# AW32207 Switch-mode Single Cell Li-ion Battery Charger With Full USB Compliance and USB-OTG Support

# **Features**

awinic

- High-Accuracy Voltage and Current Regulation

- Charge Voltage Regulation Accuracy ±0.5%(25°C), ±1%(0°C to 85°C)

- Charge Current Accuracy: ±5%

- Power Up System without Battery

- Programmable Charge Parameters through I<sup>2</sup>C<sup>™</sup> compatible Interface(100kHz/400kHz):

- -VIN DPM Threshold

- -Fast-Charge Current

- -Charge Regulation Voltage(3.5V to 4.5V)

- -Smart Charge Termination Algorithm

- 2.0A Charge Current using 51mΩ Sensing Resistor

- Specific K-DPM<sup>™</sup>: VBUS Based Dynamic Power Management

- Up to 95% Charge Efficiency

- 20V Absolute Maximum VBUS Rating

- Trickle-CC-CV Three-stage Automatic Charging Process, Automatic Recharge

- Bad Adaptor Detection and Battery Removing

Detection

- Strong Robust Protection: VBUS OVP, Minimum VBUS during Charging, Battery OVP, Reverse Leakage Protection, Thermal Shutdown

- Charge Status and Fault Indication

- 5.05V,1A Boost Mode Operation for USB OTG for 3.5V to 4.5V Battery Input

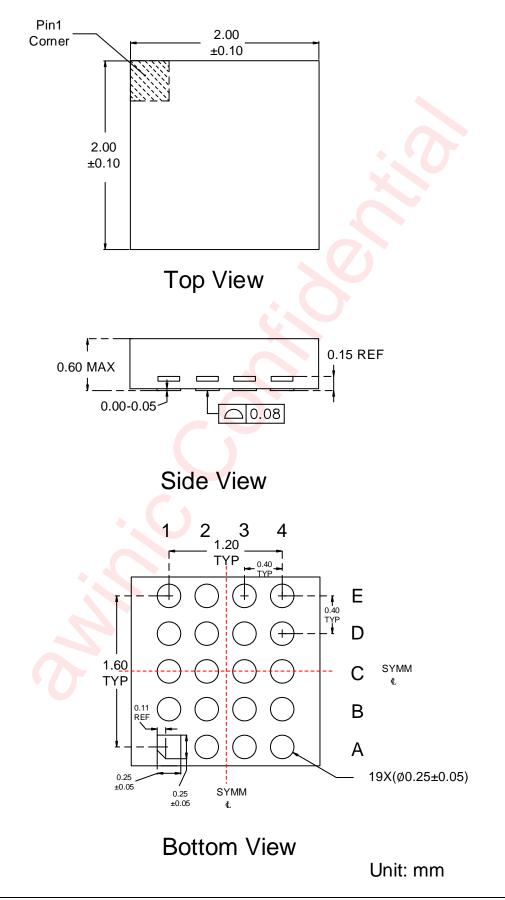

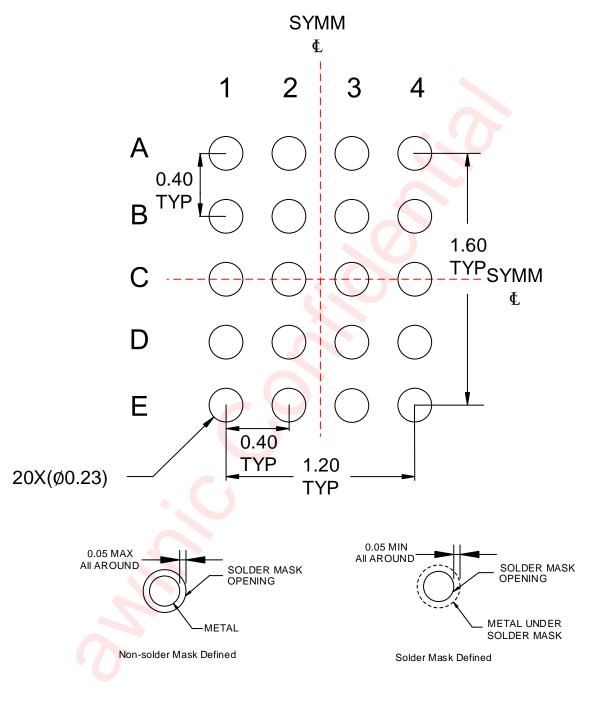

- FCQFN 2.0mm×2.0mm×0.55mm-20L Package

## **Applications**

- Mobile and Smart Phones

- Digital Camera

- Gaming Device

- Other Handheld Devices

### **General Description**

AW32207 is a high efficiency, large current, switchmode Li-lon battery charge management chip. The chip integrates 1.5 MHz synchronous Buck PWM controller, Boost PWM controller and power MOSFETs, effectively reducing the power loss.

The charge process of AW32207 includes: trickle, constant current (CC) and constant voltage (CV). The charge parameters and operating modes are programmable through I<sup>2</sup>C Interface. Also, the charge termination is determined by a programmable algorithm. The charge process runs automatically and recharging occurs when the battery voltage drops below V<sub>OREG</sub>-V<sub>RCH</sub>.

If the input source is removed, the IC enters a highimpedance mode, keeping ultra-low power loss from battery and preventing leakage from the battery to the input. Charge current is reduced when the temperature of die reaches 140°C, protecting the device and PCB from damage.

The IC can operate in boost mode to support USB OTG device on command from system. The boost regulator uses same external components with charge mode, and it supports up to 1A output current for OTG device. Meanwhile, the output voltage of boost regulator can be configured from 5.05V to 5.35V by the host.

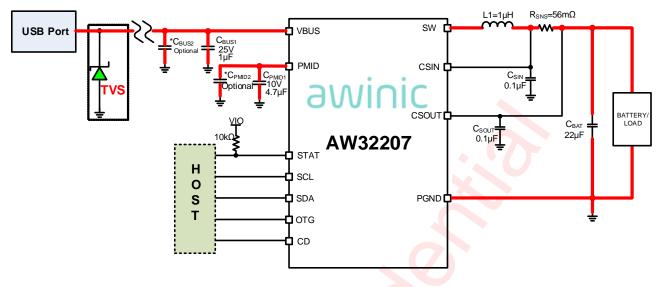

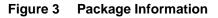

# **Application Circuit**

All trademarks are the property of their respective owners.

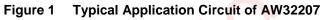

# **Pin Configuration and Top Mark**

AW32207FCR Marking (Top View)

6I6Y – AW32207FCR XXXX – Production Tracing Code

# **Pin Definition**

| Pin No.    | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2     | VBUS     | Charge input voltage and USB-OTG output voltage. Bypass with a $1\mu F$ capacitor to PGND.                                                                                                                                                                                                                                                                                                                                                 |

| A3         | NC       | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A4         | SCL      | I <sup>2</sup> C Interface Serial Clock.                                                                                                                                                                                                                                                                                                                                                                                                   |

| B1, B2, B3 | PMID     | Power input voltage. Bypass with a minimum of 4.7µF capacitor to PGND.                                                                                                                                                                                                                                                                                                                                                                     |

| B4         | SDA      | I <sup>2</sup> C Interface Serial Data.                                                                                                                                                                                                                                                                                                                                                                                                    |

| C1, C2, C3 | SW       | Switch node. Connect to output inductor.                                                                                                                                                                                                                                                                                                                                                                                                   |

| C4         | STAT     | Charge status and interrupt output pin. Open drain output indicating charge status. The charger pull the pin low when charging, and open drain for other conditions. During faults, a 128µs pulse interrupt signal is sent out.                                                                                                                                                                                                            |

| D1, D2, D3 | PGND     | Power ground.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D4         | отд      | On-The-Go. This pin sets the default charge current for charge mode. At POR while in default mode, the OTG pin is used as the input current limiting selection pin. When OTG=High, I_BUS_LIMIT<500mA and when OTG=Low, I_BUS_LIMIT<100mA. Also, the OTG pin enable the boost regulator in conjunction with OTG_EN and OTG_PL bits. The default value is pulled up to high level in the chip by a $0.3M\Omega$ (typical) internal resistor. |

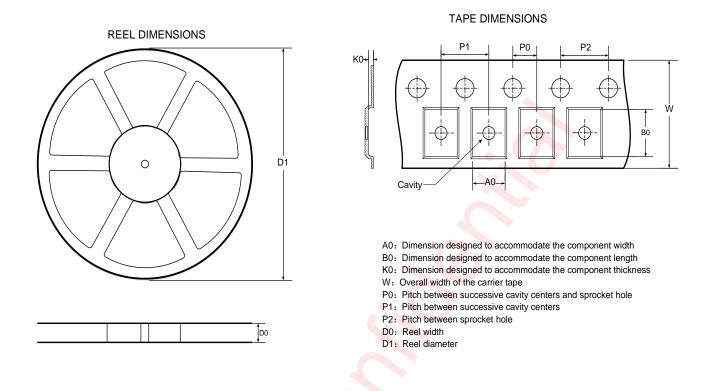

| E1         | CSIN     | Charge current-sense input. Connect to the sense resistor in series with the battery. Bypass this pin with a $0.1\mu$ F ceramic capacitor to PGND.                                                                                                                                                                                                                                                                                         |

| E2         | CD       | Charging disable. If this pin is set to high, fast charging is disabled, or if it is low, fast charging is enabled. The default value is pulled down to low level by a $1.2M\Omega(typical)$ internal resistor.                                                                                                                                                                                                                            |

| E3         | NC       | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| E4         | CSOUT    | Battery voltage and current sense input. Bypass it with a ceramic capacitor (minimum $0.1\mu$ F) to PGND.                                                                                                                                                                                                                                                                                                                                  |

# **Ordering Information**

| Part Number | Temperature | Package       | Marking | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery<br>Form             |  |

|-------------|-------------|---------------|---------|----------------------------------|------------------------------|------------------------------|--|

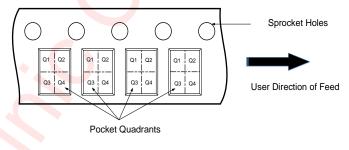

| AW32207FCR  | -40°C~85°C  | FCQFN 2×2-20L | 6I6Y    | MSL1                             | ROHS+HF                      | 3000 units/<br>Tape and Reel |  |

|             |             |               |         |                                  |                              |                              |  |

# **Typical Application Circuits**

Figure 4 AW32207 Application Circuit

Notice for typical application circuits:

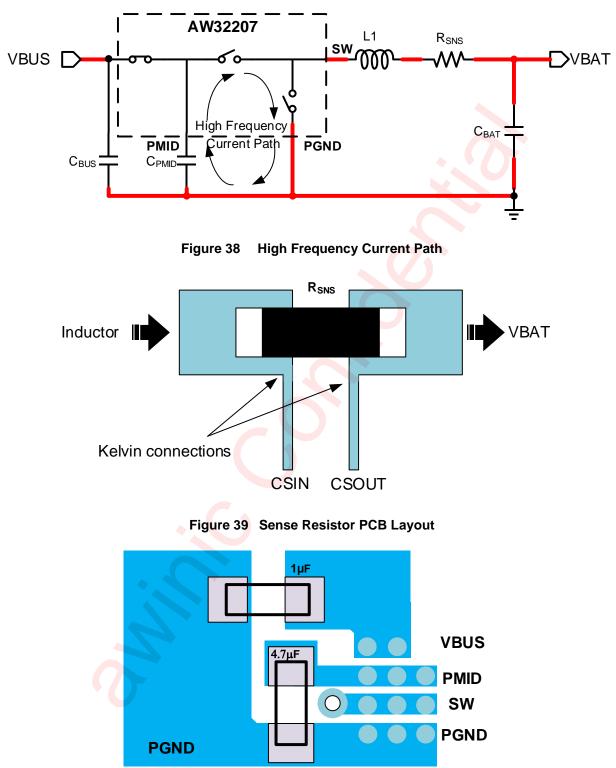

1: Please place C<sub>BUS1</sub>, C<sub>PMID1</sub>, C<sub>SIN</sub>, C<sub>SOUT</sub>, C<sub>BAT</sub> to the chip and PGND as close as possible.

2: For the sake of driving capability, the power lines, output lines, and the connection lines of L1,  $R_{SNS}$ , and BATTERY should be as short and wide as possible. The power path is marked in red as shown in the Figure 4 above, please trace according to 2A power line alignment rules.

3: Large surge voltage at VBUS may damage the chip or VBUS capacitor. In order to avoid this risk, a TVS tube can be placed in parallel with the VBUS port of USB interface.

4: C<sub>BUS2</sub> and C<sub>PMID2</sub> are optional capacitors used for FCC test.

# Absolute Maximum Ratings(NOTE1)

| PARAMETERS                                        |                                               |      | MAX | UNIT |

|---------------------------------------------------|-----------------------------------------------|------|-----|------|

| Supply voltage range $V_{\text{BUS}}$ (with respe | ect to PGND)                                  | -1.5 | 20  | V    |

| Input voltage range (with respect to PGND)        | SCL, SDA, OTG, CD                             | -0.3 | 6   | V    |

|                                                   | STAT                                          | -0.3 | 6   | V    |

| Output voltage range (with respect to PGND)       | PMID, SW <sup>(NOTE 2)</sup>                  | -0.3 | 6   | V    |

|                                                   | BAT, CSIN                                     | -0.3 | 6   | V    |

| Output sink current                               | STAT                                          |      | 10  | mA   |

| Output current(average)                           | sw                                            |      | 2   | А    |

| Operating free-air temperature                    | range                                         | -40  | 85  | °C   |

| Operating junction temperatu                      | Operating junction temperature T <sub>J</sub> |      | 150 | °C   |

| Storage temperature T <sub>STG</sub>              |                                               | -65  | 150 | °C   |

| Lead temperature (Soldering 10 s                  | seconds)                                      |      | 260 | °C   |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: The chip integrates a 100mA pull-down current at PMID and SW pin, to protect these pins from being damaged by overvoltage.

# **ESD** Rating and Latch Up

| PARAMETERS                                 | VALUE                 | UNIT |

|--------------------------------------------|-----------------------|------|

| HBM (Human Body Model) <sup>(NOTE 3)</sup> | ±2                    | kV   |

| CDM(NOTE 4)                                | ±1.5                  | kV   |

| Latch-Up <sup>(NOTE 5)</sup>               | +IT: 200<br>-IT: -200 | mA   |

NOTE3: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin. Test method: ESDA/JEDEC JS-001-2017

NOTE4: Test method: ESDA/JEDEC JS-002-2018

NOTE5: Test method: JESD78E

# **Recommended Operating Conditions**

| PARAMETERS          | DESCRIPTION                   | MIN | NORM | MAX                   | UNIT |

|---------------------|-------------------------------|-----|------|-----------------------|------|

| V <sub>BUS</sub>    | Supply voltage                | 4   |      | 6 <sup>(NOTE 6)</sup> | V    |

| V <sub>BAT</sub>    | Battery voltage               |     |      | 4.50                  | V    |

| V <sub>BUS_B</sub>  | Output voltage (Boost)        |     |      | 5.35                  | V    |

| I <sub>VBUS_B</sub> | Output current (Boost)        |     |      | 1                     | А    |

| I <sub>BAT</sub>    | Fast charging current         |     |      | 1.82                  | А    |

| T <sub>A</sub>      | Ambient temperature           | -40 |      | 85                    | °C   |

| L <sub>1</sub>      | Inductance                    |     | 1    |                       | μH   |

| Rsns                | Sense resistor                |     | 56   |                       | mΩ   |

| C <sub>BUS1</sub>   | C <sub>BUS1</sub> capacitance |     | 1    |                       | μF   |

|                     | CPMID1 capacitance            |     | 4.7  |                       | μF   |

| Сват                | CBAT capacitance              |     | 22   |                       | μF   |

| Csin                | Csin capacitance              |     | 0.1  |                       | μF   |

| Сѕоит               | Csout capacitance             |     | 0.1  |                       | μF   |

NOTE6: The inherent switching noise voltage spikes should not exceed the absolute maximum rating on either the PMID or SW pins. A tight layout minimizes switching noise.

## **Thermal Information**

| PARAMETERS                                           | VALUE | UNIT  |

|------------------------------------------------------|-------|-------|

| Junction-to-ambient thermal resistance $\theta_{JA}$ | 51    | °C /W |

# **Electrical Characteristics**

Circuit of Figure 4,  $V_{BUS}$ =5V, OPA\_MODE=0, HZ\_MODE=0, CD\_PIN=0, T\_J=25°C for typical values (unless otherwise noted)

| PARAMETER             |                                                       | TEST CONDITION                                                                                                                   | MIN  | TYP  | MAX | UNIT |

|-----------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| INPUT C               | URRENTS                                               |                                                                                                                                  |      |      |     |      |

|                       |                                                       | VBUS>VINMIN, VCSOUT>VOREG,<br>PWM Switching                                                                                      |      | 13   |     | mA   |

| I <sub>VBUS</sub>     | VBUS supply current control                           | VBUS>VINMIN, VCSOUT>VBAT_OVP,<br>PWM not switching                                                                               |      | 0.18 | ·   | mA   |

|                       |                                                       | V <sub>BUS</sub> =5V, CD=1                                                                                                       |      | 180  |     | μΑ   |

|                       |                                                       | V <sub>BUS</sub> =5V, HZ_MODE=1                                                                                                  |      | 160  |     | μΑ   |

|                       | Leakage current from battery<br>To VBUS pin           | Vcsout=4.2V, Vbus=0V                                                                                                             |      |      | 5   | μΑ   |

| I <sub>LKG</sub>      | Battery discharge current in<br>High Impedance mode   | V <sub>BAT</sub> =4.2V, High-Z mode,<br>V <sub>BUS</sub> =0V or unconnected,<br>SCL, SDA, OTG=0V,<br>0°C < T <sub>J</sub> < 85°C | 10   | 16   | 30  | μA   |

| VBUS U                | VLO & VINMIN                                          |                                                                                                                                  |      |      |     |      |

|                       | UVLO exiting threshold voltage                        | V <sub>BUS</sub> rising                                                                                                          | 3.4  | 3.6  | 3.8 | V    |

| V <sub>UVLO</sub>     | Hysteresis for UVLO                                   | V <sub>BUS</sub> falling                                                                                                         | 100  | 150  | 200 | mV   |

|                       | Deglitch time for VUVLO                               | Exits UVLO                                                                                                                       |      | 140  |     | ms   |

| Vinmin                | Input voltage lower limit for normal charging         | V <sub>BUS</sub> rising                                                                                                          | 3.8  | 4.0  | 4.2 | V    |

|                       | Hysteresis for VINMIN                                 | V <sub>BUS</sub> falling                                                                                                         | 100  | 150  | 200 | mV   |

| IDET                  | V <sub>BUS</sub> validation detection current         | V <sub>BUS</sub> rising>4V                                                                                                       | 15   | 30   | 45  | mA   |

| TDET                  | V <sub>BUS</sub> validation time                      | V <sub>BUS</sub> rising>4V                                                                                                       |      | 30   |     | ms   |

| SLEEP N               | IODE                                                  |                                                                                                                                  |      |      |     |      |

| $V_{\text{SLP}}$      | Sleep-Mode entry threshold,                           | 3.8V <v<sub>CSOUT, V<sub>BUS</sub> falling</v<sub>                                                                               | 0    | 70   | 120 | mV   |

| VSLP_EXIT             | Sleep-Mode exit hysteresis,<br>VPMID-Vcsout           | 3.8V <vcsout, rising<="" td="" vbus=""><td>80</td><td>200</td><td>280</td><td>mV</td></vcsout,>                                  | 80   | 200  | 280 | mV   |

| T <sub>SLP_EXIT</sub> | Deglitch time for VBUS rising above Vcsout +VsLP-EXIT | V <sub>BUS</sub> rising                                                                                                          |      | 30   |     | ms   |

| CHARGE                | E PROCESS                                             |                                                                                                                                  |      |      |     |      |

| M                     | Trickle to fast charge threshold                      | V <sub>CSOUT</sub> rising                                                                                                        | 2.0  | 2.1  | 2.2 | V    |

| VSHORT                | V <sub>SHORT</sub> hysteresis                         | Vcsout falling                                                                                                                   |      | 100  |     | mV   |

|                       | Weak battery voltage threshold                        | Vcsout rising                                                                                                                    |      | 3.7  |     | V    |

| M                     | Weak battery voltage accuracy                         |                                                                                                                                  | -5   |      | 5   | %    |

| VLOWV                 | Hysteresis for VLOWV                                  | Battery voltage falling                                                                                                          |      | 100  |     | mV   |

|                       | Deglitch time                                         |                                                                                                                                  |      | 30   |     | ms   |

| Vara                  | Output regulation voltage programmable range          | V <sub>BUS</sub> =5V, TE=0, operating in<br>voltage regulation,<br>programmable                                                  | 3.5  |      | 4.5 | V    |

| Voreg                 | Output regulation voltage                             | TJ=25°C                                                                                                                          | -0.5 |      | 0.5 | %    |

|                       | accuracy                                              | Tj=0°C~85°C                                                                                                                      | -1   |      | 1   | %    |

|                       | Recharge threshold voltage                            | Voreg=4.2V, below Voreg                                                                                                          | 60   | 100  | 140 | mV   |

| Vrch                  | Recharge threshold voltage programmable range         | V <sub>OREG</sub> =4.2V, TE=1, charge done<br>and V <sub>CSOUT</sub> below V <sub>OREG</sub> ,<br>programmable                   | 50   |      | 200 | mV   |

AW32207 Oct. 2021 V1.6

|                       | PARAMETER                                                        | TEST CONDITION                                                           | MIN   | TYP | MAX   | UNIT |

|-----------------------|------------------------------------------------------------------|--------------------------------------------------------------------------|-------|-----|-------|------|

|                       | Deglitch time for VRCH                                           | V <sub>CSOUT</sub> falling after charge termination                      |       | 130 |       | ms   |

|                       |                                                                  | termination                                                              |       |     |       |      |

| CHARGE                |                                                                  |                                                                          |       |     |       |      |

|                       | Output charge regulation current programmable range              | $V_{SHORT} \leq V_{CSOUT} < V_{OREG}$ ,<br>Rsense=56m $\Omega$           | 485   |     | 1821  | mA   |

| I <sub>CHG</sub>      | Default charge current<br>(OTG_PIN=1 after POR)                  | Vshort≤Vcsout <voreg ,<br="">Rsense=56mΩ</voreg>                         |       | 485 |       | mA   |

|                       | Accuracy for charge current<br>regulation                        | I <sub>CHG</sub> =1820mA, R <sub>SENSE</sub> =56m $\Omega$               | -5    |     | 5     | %    |

| IPRE_CHG              | Trickle charge current                                           | VBUS>VINMIN, VCSOUT<2.1V                                                 | 80    | 100 | 130   | mA   |

| CHARGE                | TERMINATION DETECTIO                                             | N                                                                        |       |     |       |      |

|                       | Termination charge current threshold, programmable               | Vcsout>Voreg-Vrch,<br>Rsense=56mΩ                                        | 60    |     | 485   | mA   |

| Iterm                 | Accuracy for charge termination detection                        | ITERM=121mA                                                              | -15   |     | 15    | %    |

| T <sub>DET</sub>      | Termination detecting window programmable range                  | ICHG <iterm< td=""><td>64</td><td></td><td>1024</td><td>ms</td></iterm<> | 64    |     | 1024  | ms   |

| T <sub>TERM</sub>     | Termination deglitch time programmable range                     |                                                                          | 8     |     | 256   | ms   |

| K_DPM <sup>™</sup>    | Λ                                                                |                                                                          |       |     |       |      |

|                       | K_DPM <sup>™</sup> clamps V <sub>B∪s</sub><br>programmable range |                                                                          | 4.250 |     | 4.775 | V    |

| Vk_dpm                | Accuracy for K_DPM <sup>TM</sup> clamps                          |                                                                          | -5    |     | 5     | %    |

| STAT                  |                                                                  |                                                                          | 1     |     |       |      |

| Vol(stat)             | Low-level output saturation voltage, STAT pin                    | lo=10mA, sink current                                                    |       |     | 0.3   | V    |

| I <sub>LKG_STAT</sub> | High-level leakage current for STAT                              | STAT is in High-impedance<br>status, V <sub>STAT</sub> =5V               |       |     | 2     | μA   |

| CD, OTG               | PIN LOGIC LEVEL                                                  |                                                                          |       |     |       |      |

| VIL                   | Input low threshold level                                        |                                                                          |       |     | 0.45  | V    |

| VIH                   | Input high threshold level                                       |                                                                          | 1.2   |     |       | V    |

| I <sup>2</sup> C BUS  | LOGIC LEVELS AND TIMIN                                           | G CHARACTERISITICS                                                       |       |     |       |      |

| Vol                   | Output low threshold level                                       | Io=10mA, sink current                                                    |       |     | 0.3   | V    |

| VIL                   | Input low threshold level                                        | Vpull_up=1.8V, SDA and SCL                                               |       |     | 0.45  | V    |

| VIH                   | Input high threshold level                                       | Vpull_up=1.8V, SDA and SCL                                               | 1.2   |     |       | V    |

| IBIAS                 | Input bias current                                               | Vpull_up=1.8V, SDA and SCL                                               |       |     | 1     | μA   |

| PWM                   |                                                                  |                                                                          |       |     |       |      |

| Rovp                  | Internal OVP MOSFET<br>on-resistance                             | I <sub>IN_LIMIT</sub> =500mA, measured from VBUS to PMID                 |       | 47  |       | mΩ   |

| Rpmos                 | Internal top P-channel<br>MOSFET on-resistance                   | I <sub>IN_LIMIT</sub> =500mA, measured from<br>PMID to SW                |       | 45  |       | mΩ   |

| RNMOS                 | Internal bottom N-channel<br>MOSFET on-resistance                | I <sub>IN_LIMIT</sub> =500mA, measured from SW to PGND                   |       | 60  |       | mΩ   |

|                       | Oscillator Frequency                                             |                                                                          |       | 1.5 |       | MHz  |

| fosc                  | Frequency Accuracy                                               |                                                                          | -10   | +13 | +10   | %    |

|                       | Frequency Shift                                                  |                                                                          |       | 110 |       | %    |

# **awinic** 上海艾为电子技术股份有限公司 shanghai awinic technology co., Itd.

|                      | PARAMETER                                                                         | TEST CONDITION                                                                          | MIN  | TYP        | MAX  | UNIT      |

|----------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|------------|------|-----------|

| D <sub>MAX</sub>     | Maximum Duty Cycle                                                                |                                                                                         |      |            | 100  | %         |

| CHARGE               | PROCESS PROTECTION                                                                |                                                                                         |      |            |      |           |

|                      | Input VBUS OVP threshold voltage                                                  | V <sub>BUS</sub> rising                                                                 |      | 6.4        |      | V         |

| Vovp_vbus            | Accuracy for VBUS OVP threshold                                                   |                                                                                         | -5   |            | 5    | %         |

|                      | V <sub>OVP_VBUS</sub> hysteresis                                                  | V <sub>BUS</sub> falling from above<br>V <sub>OVP_VBUS</sub>                            |      | 180        |      | mV        |

| V <sub>OVP_BAT</sub> | Output OVP threshold voltage                                                      | VCSOUT threshold over VOREG to turn off charger during charge                           |      | 117.6      | r    | - % Voreg |

| VOVP_BAI             | VovP_BAT hysteresis                                                               | Lower limit for V <sub>CSOUT</sub> falling<br>from above V <sub>OVP_BAT</sub>           |      | 12.4       |      |           |

| ILIMIT               | Cycle-by-cycle current limit for<br>charge                                        | Charge mode operation                                                                   |      | 3.88       |      | А         |

| T <sub>CF</sub>      | Charge current reduction temperature                                              | Junction temperature rising                                                             |      | 140        |      | °C        |

|                      | Thermal hysteresis for T <sub>CF</sub>                                            | Junction temperature falling                                                            |      | 30         |      | °C        |

| Тотр                 | Overheating shutdown protection temperature                                       | Junction temperature rising                                                             |      | 160        |      | °C        |

|                      | Thermal hysteresis for TOTP                                                       | Junction temperature falling                                                            |      | 30         |      | °C        |

| BATTER               | Y DETECTION                                                                       |                                                                                         |      |            |      |           |

| Idbat                | Battery detection current<br>before charge done (sink<br>current)                 | Begins after termination<br>detected and VCSOUT< VOREG                                  |      | -0.5       |      | mA        |

| Tdbat                | Battery detection time                                                            |                                                                                         |      | 262        |      | ms        |

| BOOST                | MODE                                                                              |                                                                                         |      |            |      |           |

| V <sub>BUS_B</sub>   | Boost output voltage (to VBUS pin) programmable range                             | 2.5V < Vcsout < 4.5 V                                                                   | 5.05 |            | 5.35 | V         |

|                      | Boost output voltage accuracy                                                     | 3.5 <vcsout<4.5, ibo="1A&lt;/td"><td>-3</td><td></td><td>2</td><td>%</td></vcsout<4.5,> | -3   |            | 2    | %         |

| Івотмах              | Maximum output current for<br>Boost                                               | V <sub>BUS_B</sub> =5.05V,<br>3.5V <v<sub>CSOUT&lt;4.5V</v<sub>                         |      |            | 1000 | mA        |

| I <sub>LIMIT_B</sub> | Cycle-by-cycle current limit for boost                                            | VBUS_B =5.05V,<br>3.5V <v<sub>CSOUT&lt;4.5V</v<sub>                                     |      | 2.65       |      | A         |

|                      | Overvoltage VBUS OVP<br>threshold voltage for boost                               | V <sub>BUS</sub> rising                                                                 |      | 6          |      | V         |

| VBUSOVP_B            | Accuracy for VBUS OVP<br>Threshold                                                |                                                                                         | -5   |            | 5    | %         |

|                      | VBUSOVP_B hysteresis                                                              | VBUS falling from above<br>VBUSOVP_B                                                    |      | 200        |      | mV        |

| Vuvlo_b              | Minimum battery voltage for                                                       | Before boost start                                                                      |      | 2.9        |      | V         |

| ROUT_B               | boost<br>Boost output resistance at<br>High-Impedance mode (From<br>VBUS to PGND) | Hysteresis<br>CD=1 or HZ_MODE=1                                                         |      | 400<br>304 |      | mV<br>kΩ  |

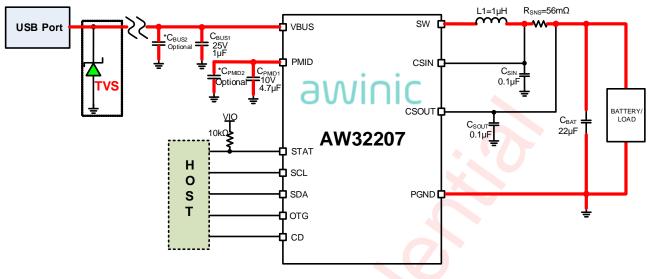

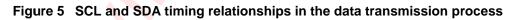

### I<sup>2</sup>C INTERFACE TIMING

| SYMBOL                | DESCRIPTION                               |     | MIN | ТҮР | МАХ | UNIT |

|-----------------------|-------------------------------------------|-----|-----|-----|-----|------|

| F <sub>SCL</sub>      | Interface Clock Frequency                 |     |     |     | 400 | kHz  |

|                       |                                           | SCL |     | 200 |     | ns   |

| t <sub>DEGLITCH</sub> | Deglitch Time                             | SDA |     | 250 |     | ns   |

| thd:sta               | (Repeat-Start) Start Condition Hold Time  |     | 0.6 |     |     | μs   |

| tLOW                  | Low Level Width of SCL                    |     | 1.3 | U   |     | μs   |

| tніgн                 | High Level Width of SCL                   |     | 0.6 |     |     | μs   |

| tsu:sta               | (Repeat-Start) Start Condition Setup Time | •   | 0.6 |     |     | μs   |

| thd:dat               | Data Hold Time                            | 0   | 0   |     |     | μs   |

| tsu:dat               | Data Setup Time                           | X   | 0.1 |     |     | μs   |

| t <sub>R</sub>        | Rising Time of SDA And SCL                |     |     |     | 0.3 | μs   |

| tF                    | Falling Time of SDA And SCL               |     |     |     | 0.3 | μs   |

| tsu:sto               | Stop Condition Setup Time                 |     | 0.6 |     |     | μs   |

| t <sub>BUF</sub>      | Time Between Start and Stop Condition     |     | 1.3 |     |     | μs   |

Figure 6 The timing relationship between START and STOP state

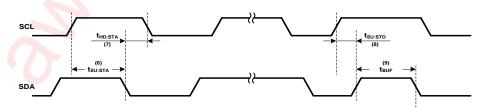

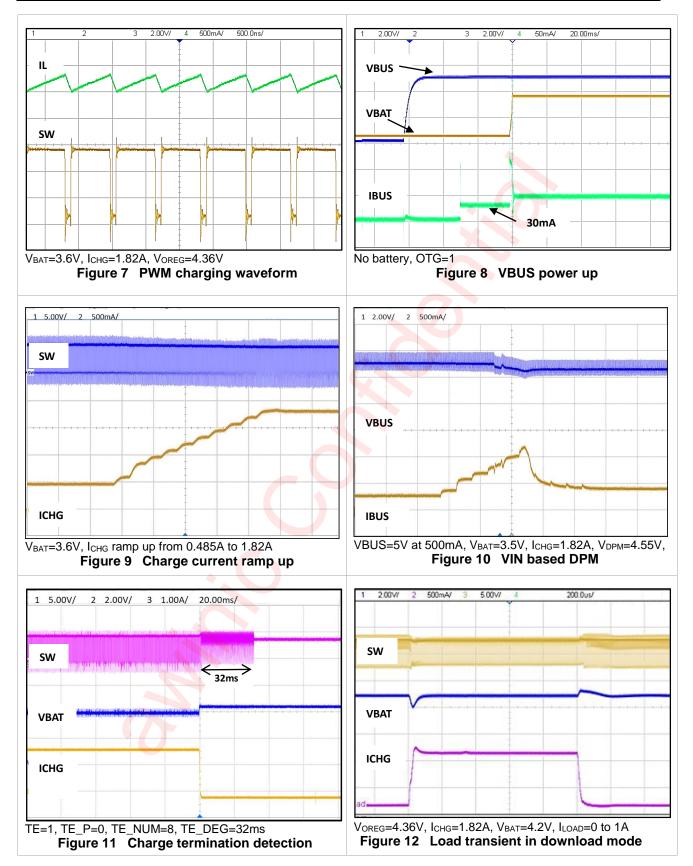

# **Typical Characteristics**

VBUS=5V, T<sub>A</sub>=25°C, Circuit of Figure 4 unless other noted.

#### Table 1 TABLE OF FIGURES

| INDEX                                                                  | FIGURE No. |

|------------------------------------------------------------------------|------------|

| PWM charging waveform                                                  | Figure 7   |

| V <sub>BUS</sub> power up and bad adaptor detection                    | Figure 8   |

| Charge current ramp up                                                 | Figure 9   |

| VIN based DPM                                                          | Figure 10  |

| Charge termination detection                                           | Figure 11  |

| Load transient in download mode:0-1A                                   | Figure 12  |

| Charge efficiency vs. VBAT                                             | Figure 13  |

| Auto-charge startup at VBUS plug-in, OTG_PIN=0, VBAT=3.0V              | Figure 14  |

| Auto-charge startup at VBUS plug-in, OTG_PIN=1, V <sub>BAT</sub> =3.0V | Figure 15  |

| Battery removal during charging, VBAT=3.9V, ICHG=1.82A, TE=1           | Figure 16  |

| Battery removal during charging, VBAT=3.9V, ICHG=1.82A, TE=0           | Figure 17  |

| BOOST waveform                                                         |            |

| Load transient 5mA-1A-5mA                                              | Figure 18  |

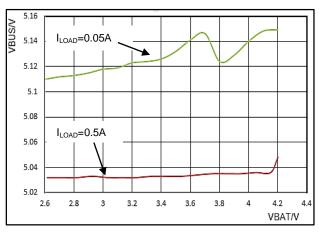

| Line regulation for BOOST                                              | Figure 19  |

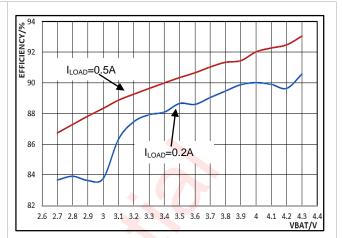

| Efficiency vs. VBAT                                                    | Figure 20  |

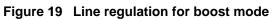

| Output regulation vs.ILOAD                                             | Figure 21  |

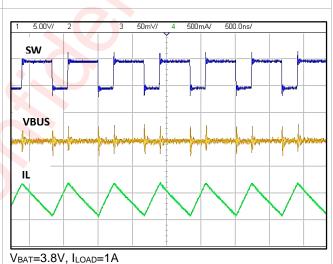

| Boost PWM waveform, VBAT=3.8V, ILOAD=1A                                | Figure 22  |

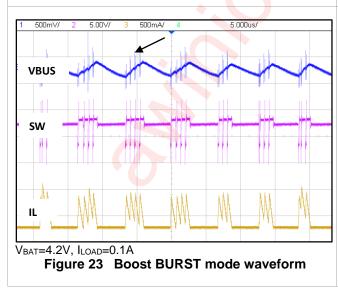

| Boost BURST mode waveform                                              | Figure 23  |

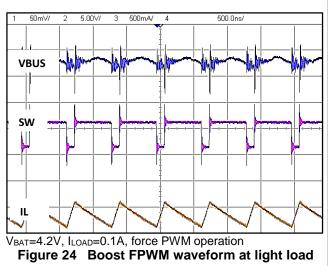

| Boost FPWM waveform at light load                                      | Figure 24  |

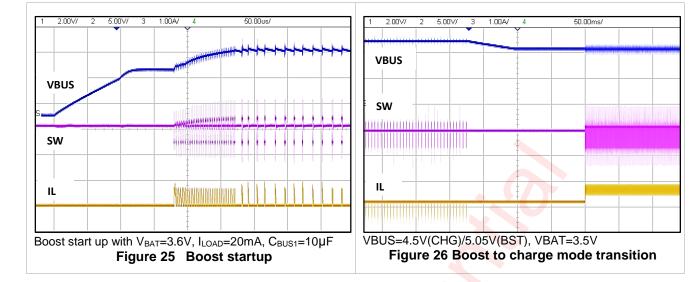

| Startup, VBAT=3.6V, ILOAD=20mA, CBUS1=10µF                             | Figure 25  |

| Boost to charge mode transition, VBUS=4.5V(CHG)/5.05V(BST), VBAT=3.5V  | Figure 26  |

# **OWINIC** 上海艾为电子技术股份有限公司 shanghai awinic technology co., ltd.

#### **awinic** 上海艾为电子技术股份有限公司 shanghai awinis technology sould shanghai awinic technology co., ltd.

# awinic

#### 上海艾为电子技术股份有限公司 shanghai awinic technology co., ltd.

AW32207 Oct. 2021 V1.6

Figure 20 Efficiency for boost mode

# awinic

www.awinic.com

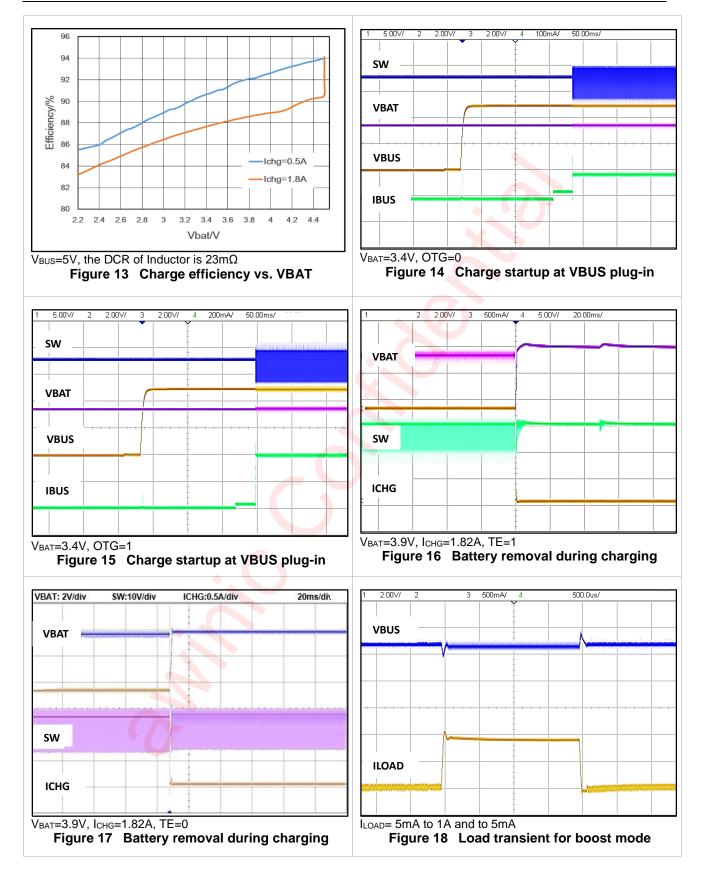

## **Functional Block Diagram**

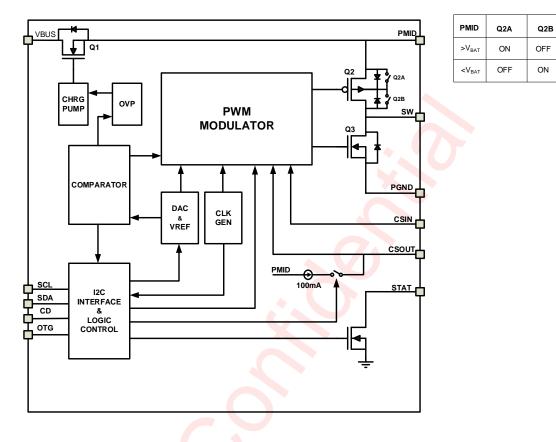

Figure 27 The AW32207 Function Block

## **Detailed Functional Description**

AW32207 is a highly efficient, highly integrated synchronous switch charger. It has a wide range of output regulation voltage and can provide maximum 2-A current for single-cell lithium ion or lithium polymer battery. Furthermore, AW32207 also supports boost mode for USB OTG applications.

The AW32207 has three operation mode:

- Charge mode: charges a single-cell battery with default or host configured value.

- Boost mode: boosts the battery voltage to 5.05V(default value) on VBUS pin for OTG applications.

- High impedance mode: stops charging or boosting and operates in a low power cost mode.

The IC starts in charge mode, which is the default mode and using each register's default value, also, it can switch smoothly among the different modes through I<sup>2</sup>C communication with the host.

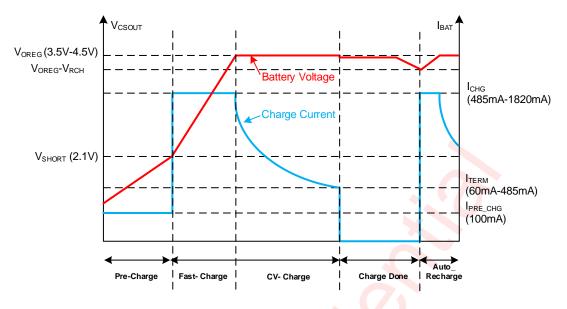

#### **Battery Charge Profile**

The AW32207 Provides three main charging phases: pre-charge, fast-charge and constant-voltage charge (see the Figure 28). If the charging parameters is not configured via I<sup>2</sup>C, the charger works under the default configuration.

Figure 28 The AW32207 Function Block

- Pre-charge: In the pre-charge process, the IC can safely pre-charge the deeply depleted battery with small current until the battery voltage rise to the pre-charge threshold (V<sub>SHORT</sub>), in which the IC enter the fast-charge process.

- Fast charge: When V<sub>BAT</sub> exceeds V<sub>SHORT</sub>, the IC enters the fast charge process. The REG04H[6:3] can be set to change the fast-charge current.

- Constant-voltage charge: The charge mode changes from CC to CV, when the V<sub>BAT</sub> rises to the batteryfull voltage (V<sub>OREG</sub>) set via REG02H[7:2]. At the same time, the charge current starts decreasing in CV charge process.

Due to multiple loop regulations, such as dynamic power management (DPM) regulation (input voltage, input current) or thermal regulation, the actual charge current may be less than the setting value.

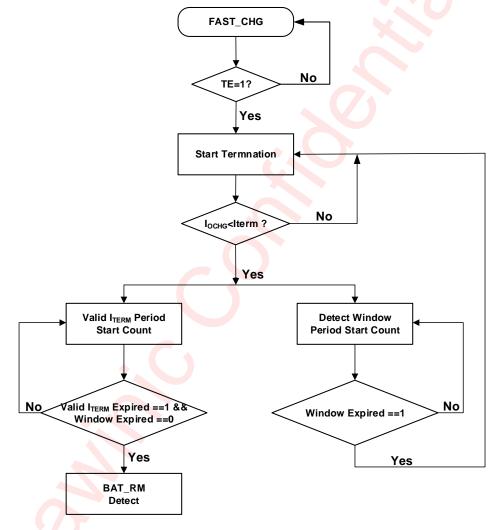

When the charge current is smaller than termination current threshold  $I_{TERM}$  in CV process and the CTA is satisfied, the charge cycle will be completed and the charge status is updated to charge done. The register REG04H[2:0] can set the termination charge current threshold  $I_{TERM}$ . The termination function can be disabled via TE=0 (REG01H[3] = 0). The termination function is show as table 2.

| TF | After Terminatio | After Termination Condition is Meet |  |  |  |

|----|------------------|-------------------------------------|--|--|--|

|    | Operation        | Charge Status                       |  |  |  |

| 0  | Keep CV Charge   | Charge                              |  |  |  |

| 1  | Charge done      | Charge done                         |  |  |  |

#### Table 2 Termination Function Selection Table

A new charge cycle starts when any of the following conditions are valid:

• Auto-recharge kicks in.

awini

- Battery charging is enabled via the I<sup>2</sup>C.

- The input power is recycled .

Under the following condition:

• No any charge fault was reported.

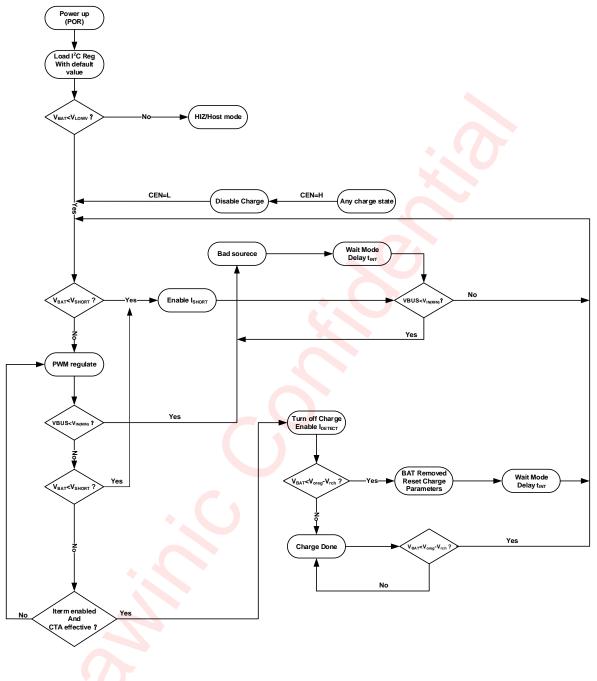

### **Operational Chart Flow**

awinic

The charge flow chart of AW32207 is showed as above. The IC loads registers value after power-onreset(POR), then detects the VBAT voltage. If  $V_{BAT}$ > $V_{LOWV}$ , the IC enters HZ MODE; otherwise, it operates in the charge mode. At the beginning of charge process, when battery voltage is lower than  $V_{SHORT}$ , the charger outputs a short-circuit current,  $I_{PRE\_CHG}$ , to pre-charge the battery. When the battery voltage reaches  $V_{SHORT}$ , the charge current increases to  $I_{CHG}$ , which is the fast charge current and can be set by the host. Once the battery voltage is near or equal to the regulation voltage,  $V_{OREG}$ , the IC enters voltage regulation phase. In this phase, the voltage of battery is stable but the charge current is decreasing. The default regulation voltage is 3.54V, meanwhile, it can be programmed from 3.5V to 4.5V through I<sup>2</sup>C interface. During the charge process, the IC monitors the charge current if termination function is enabled (REG01H[3]=1), once the Charge

#### **OWINIC** 上海艾为电子技术股份有限公司 shanghai awinic technology co., ltd.

Termination Algorithm(CTA<sup>TM</sup>) is meet, the IC turns off the PWM charge process and discharge the battery with a small current,  $I_{DET}$ , for a period of  $t_{DET}$  (262ms typical). Then the IC will check the battery voltage, if it is still above the recharge threshold after  $t_{DET}$ , the battery charging is complete, the status bit and pin are updated to indicate the charging process has completed. This strategy is used to ensure that termination do not occur when the battery is removed. If a charge process has completed, the new charge cycle will restart when the battery voltage falls below the V<sub>OREG</sub>-V<sub>RCH</sub> threshold.

Meanwhile, all the parameters of CTA are programmable, and setting the charge termination bit (REG01H[3]) to 0 can disable the charging termination detection, please refer to I<sup>2</sup>C register section for more details.

#### **VBUS** Protection

The chip sets OVP, SLEEP MODE, K-DPM<sup>™</sup>, VINMIN protection mechanisms at the VBUS input port.

#### **VBUS OVP**

AW32207 integrates input overvoltage protection to prevent the device and other downstream components from damage of the high input voltage (Voltage from VBUS to GND). If the VBUS voltage exceeds V<sub>OVP\_VBUS</sub> threshold(6.4V typical), the chip will stop charging and send out a fault pulse from STAT pin. When V<sub>BUS</sub> drops lower than the input overvoltage exit threshold (6.4V-0.18V typical), the charge process will continue.

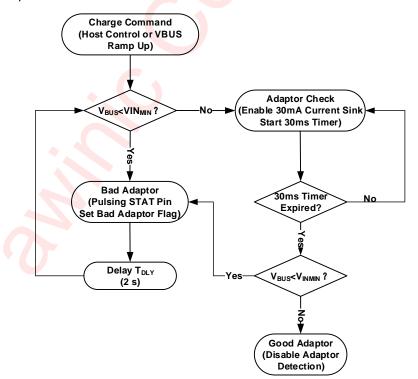

#### Bad Adaptor Detection

This detection makes sure that the adaptor has enough abilities to charge the battery. In this detection process, when VBUS rises above  $V_{INMIN}$  (4.0V typical), the IC applies a current sink to VBUS for 30ms and then detects the voltage of VBUS. If the V<sub>BUS</sub> is still higher than  $V_{INMIN}$ , the adaptor is good and the charge process begins. Otherwise, this detection does not pass and the charge process is suspended. This detection repeats every t<sub>INT</sub>, until a good adaptor is detected.

#### Figure 30 Bad Adaptor Detection Scheme Flow Chart

#### Sleep Mode

awinic

When  $V_{BUS}$  is lower than  $V_{CSOUT}+V_{SLP}$  (lasts for 1 ms), and  $V_{BUS}$  is higher than  $V_{INMIN}$ , the IC enters sleep mode. During sleep mode, PWM switching is turned off to prevent the battery from drain into VBUS.

#### VBUS Based Dynamic Power Management——K-DPM<sup>™</sup>

The K-DPM<sup>™</sup> allows AW32207 to adaptively match USB or small power adapter. During the charging process, if the input power source is unable to provide the charging current set by R<sub>SNS</sub>, the VBUS voltage will decrease. Once the VBUS drops below 4.55V(typ.), the K-DPM<sup>™</sup> loop begins to reduce charge current, preventing any further drop of VBUS, and finally balance will be achieved between them. The K-DPM<sup>™</sup> gives the IC ability to charge battery with different adapters.

#### **Battery Protection**

#### Safety Voltage and Safety Current Limit

The REG06H register is a safe output voltage and output current configuration register that needs to be set up first after power-up to prevent damage to the battery caused by excessive charger output voltage or output current. To prevent the I<sup>2</sup>C from tampering with the security register settings, the security register is locked once the other registers are read or written. Only hard reset (internal POR reset --- power-on reset) can reset the safety register.

#### Battery OVP

Overvoltage protection is integrated in the chip to protect the device against damage if the voltage at CSOUT pin goes too high. The IC will turn off the PWM converter if an overvoltage condition is detected, when the voltage of CSOUT is higher than V<sub>OVP\_BAT</sub> which is equal to 117.6%\*V<sub>OREG</sub>, and STAT pin would generate a 128µs pulse and then behave as a high impedance (open-drain). Once V<sub>CSOUT</sub> is lower than the battery overvoltage exit threshold, charge process resumes.

#### **Battery Short Protection**

During the normal charging process, when the battery voltage drops to the short-circuit threshold, V<sub>SHORT</sub>(2.1V typical), the charger operates in linear charge mode with a lower charge current of I<sub>PRE\_CHG</sub>.

#### **Battery Detection**

Once the termination bit (TE) is set 1, AW32207 can detect if the battery is absence or not for applications with removable battery packs. During normal charge process, when the voltage at the CSOUT pin is above the battery recharge threshold,  $V_{OREG}$  -  $V_{RCH}$ , and the CTA is meet, the IC turns off the PWM charge and enables a discharge current I<sub>DBAT</sub> (-0.5mA, typ.) for a period of T<sub>DBAT</sub>, (262 ms typ.). If the battery voltage is still above the recharge threshold after T<sub>DBAT</sub>, the battery is present. On the other hand, the battery is absent and the IC:

- Sets the register to their default values.

- Sets the FAULT bits (REG00H[2:0]) to 111.

- Restarts charge process with default values after tint (2s typ.).

#### **Thermal Regulation and Protection**

To avoid overheating of the chip at the charge process, the IC detects the junction temperature (T<sub>J</sub>) of the die. When T<sub>J</sub> reaches the thermal regulation threshold T<sub>CF</sub>(140°C), I<sub>CHG</sub> configuration code would reduce to "0000"(REG04H[6:3]=0000) gradually. In any state, if T<sub>J</sub> exceeds T<sub>OTP</sub>(160°C), the IC suspends charging. And charging resumes when T<sub>J</sub> falls below T<sub>OTP</sub> by approximately 30°C.

### Charge Termination Algorithm(CTA)

awinic

To end the charging process reasonably, the IC applies the unique Charge Termination Algorithm(CTA), which could adjust the termination strategies by I<sup>2</sup>C interface flexibly. If the termination is enabled, once the charge current is below the termination charge current threshold (I<sub>TERM</sub>), the termination detecting window timer will be enabled. During the termination window, if the time of I<sub>CHG</sub><I<sub>TERM</sub> is longer than configured valid I<sub>TERM</sub> deglitch time, the IC turns off the PWM charge and enables a discharge current (I<sub>DBAT</sub>) for a period of T<sub>DBAT</sub>, then checks the battery voltage. If the battery voltage is still above the recharge threshold after T<sub>DBAT</sub>, the battery charging is complete. The termination current level, the detecting window periods, the valid I<sub>TERM</sub> periods and the deglitch time of each period can be programmed by the Recharge/Charge Termination Algorithm Configure Register (REG07H).

### STAT Pin Output

awinic

The STAT pin is used to indicate operation conditions of the IC and provides a fault indicator for interrupt systems. The status of STAT pin at different operation conditions is summarized in Table 3.

| EN_STAT (REG00H[6]) | CHARGE STATE                                                                                                            | STAT                         |

|---------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 1                   | Charge in progress and EN_STAT=1                                                                                        | Low                          |

| Х                   | Other normal conditions                                                                                                 | Open-drain                   |

| x                   | Charge mode faults: Sleep mode, VBUS or battery overvoltage, poor input source, VBUS UVLO, no battery, thermal shutdown | 128µs pulse, then open-drain |

| Х                   | Boost mode faults: Over load, VBUS overvoltage, low battery voltage, thermal shutdown                                   | 128µs pulse, then open-drain |

| 0                   | X                                                                                                                       | Open-drain                   |

#### Table 3 STAT Pin Summary

#### Charge Mode Control Bits/Pin

#### CEN Bit

The CEN bit(REG01H[2]) in the control register is used to disable or enable the charge process. Writing "0" to this bit enables the charge and writing "1" to this bit disables the charge.

#### RESET Bit

The RESET bit(REG04H[7]) in the control register resets all the charge parameters. Writing '1" to the RESET bit will reset all the charge parameters to default values except the safety limit register, and it is not recommended to set the RESET bit when the IC operates in charging or boosting process. Once writing '1" to the RESET bit via I<sup>2</sup>C, it needs to wait 32ms at least before next I<sup>2</sup>C command can be accepted.

#### OPA\_Mode Bit

The OPA\_MODE bit(REG01H[0]) is the operation mode control bit. When OPA\_MODE=1 and HZ\_MODE=0, the IC operates in boost mode. Other conditions can be referred in Table 3 for details.

#### CD Pin (Charge Disable)

The CD pin controls the charging process. When the CD pin is low, fast charge is enabled. When the CD pin is high, fast charge is disabled.

| CD | OPA_MODE | HZ_MODE | OPERATION MODE                                          |  |  |  |  |

|----|----------|---------|---------------------------------------------------------|--|--|--|--|

| 0  | 0        | 0       | Charge mode (VBUS > UVLO); High impedance (VBUS < UV    |  |  |  |  |

| 1  | 0        | Х       | High impedance mode                                     |  |  |  |  |

| Х  | 1        | 0       | Boost(No faults); Any fault go to charge configure mode |  |  |  |  |

| Х  | Х        | 1       | High impedance mode                                     |  |  |  |  |

#### **Table 4 Operation Mode Summary**

#### **BOOST Mode Operation**

When the IC operates in boost mode, it delivers the power to VBUS pin from the battery and boosts the battery voltage to  $V_{BUS_B}$  (about 5.05V). Boost mode can be configured as showed as Table 4 and Table 5.

#### **OWINIC** 上海艾为电子技术股份有限公司 shanghai awinic technology co., ltd.

#### PWM Controller in Boost Mode

Similar to charge mode operation, the IC integrates an 1.5 MHz frequency peak current mode controller to regulate output voltage at VBUS pin (V<sub>BUS\_B</sub>) in boost mode. The feedback loop is internally compensated for a wide load range and battery voltage range.

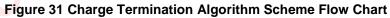

#### Boost Start Up

When the boost is enabled, if  $V_{BAT}$ > $V_{UVLO_B}$ , the regulator first attempts to bring  $V_{PMID}$  within 300mV of  $V_{BAT}$  using an internal 150mA current source from VBAT (linear startup). If the voltage of PMID pin has reached  $V_{CSOUT}$ -300mV within 3ms, the IC enters the boost soft-startup operation process. If  $V_{PMID}$  has not achieved  $V_{CSOUT}$ -300mV after 3ms, a FAULT state is indicated. And the process of boost startup is showed as below:

Figure 32 Boost Mode Start Scheme Flow Chart

#### Burst Mode at Light Load

In boost mode, under light load conditions, the IC operates in burst mode to reduce the power loss and improve the converter's efficiency. During boosting, the PWM converter is turned off once the inductor current is less than I<sub>BURST\_IN</sub>; and the PWM is turned back on when the voltage at PMID pin drops to about 101% of the rated output voltage. If the inductor current is continuously reduced, the IC will operate in Power Save Mode(PS Mode) when the inductor current is less than I<sub>PS\_IN</sub>. A pre-set circuit is used to make the smooth transition between PWM, Burst and PS mode.

#### Force PWM at Light Load

To reduce the ripple voltage under light load, AW32207 integrates Force PWM mode in boost mode, which could effectively decrease the output ripple voltage in VBUS pin. And this function can be enabled or disabled by register REG0AH[3] (default value is disabled).

#### Protection in Boost Mode

If a boost fault occurs:

• The STAT pin pulses. During normal boosting operation, the STAT pin behaves as a high impedance (opendrain) output. Under fault conditions, a 128µs pulse is sent out to notify the host. • OPA\_MODE bit is reset. If the IC operates in boost mode with OPA\_MODE=1(not in force OTG mode), it will enter charge mode because the OPA\_MODE is reset to 0.

• The fault bits (REG09H[2:0]) are set to indicate the fault type as register table.

#### Output Overvoltage Protection

The IC provides a built-in overvoltage protection to protect the device and other components against damage if the voltage (Voltage from VBUS to GND) is too high in boost mode-- exceeding 6.0V typical.

#### **Output Overload Protection**

The IC provides a built-in over-load protection to avoid the device damage when VBUS is over loaded. Once VBUS fails to achieve the voltage required to advance to the next stage during soft-start or sustained (>20µs) current limit during boost mode, the IC will enter overload protection mode.

#### Thermal Protection

To prevent overheating of the chip during the boost mode, the IC monitors the junction temperature ( $T_J$ ) of the die. If  $T_J$  exceeds  $T_{OTP}(160^{\circ}C)$ , the IC suspends boosting, and the thermal hysteresis is about 30°C.

#### Battery UVLO Protection

During boosting, when the battery voltage is below the battery under voltage threshold (VUVLO\_B), the IC turns off the PWM converter.

#### Restart After Boost Faults

If boost is enabled with the OPA\_MODE bit, boost mode can only be restarted through subsequent I<sup>2</sup>C commands since OPA\_MODE is reset on boost faults. When OTG\_PL=1/0, the OTG pin ACTIVE state is 1/0. If OTG\_EN=1 and OTG pin is still ACTIVE, the boost restarts after all faults are cleared. All the methods that can enable OTG mode are showed as Table 5.

| OTG_EN | OTG_PIN  | HZ_MODE | OPA_MODE | BOOST  |

|--------|----------|---------|----------|--------|

| 0      | X        | 0       | 1        | Enable |

| 1      | ACTIVE   | Х       | Х        | Enable |

| 1      | INACTIVE | 0       | 1        | Enable |

Table 5 Enabling Boost

#### High Impedance (HZ) Mode

In this mode, the charger stops charging and enters a low quiescent current state to conserve power. The charger enters HZ mode if

- The voltage on CD pin is logic high;

- The HZ-MODE control bit is set to "1" and OTG pin is not in active status;

- $V_{BUS} > V_{UVLO}$  and a battery with  $V_{BAT} > V_{LOWV}$  is inserted after POR;

- VBUS falls below UVLO.

In order to exit HZ mode, the CD pin must be low, VBUS must be higher than UVLO and the HOST must write a "0" to the HZ-MODE control bit.

#### General I<sup>2</sup>C Operation

The AW32207 is compatible with I<sup>2</sup>C interface. The SCL line is an input and the SDA line is a bi-directional open-drain output.

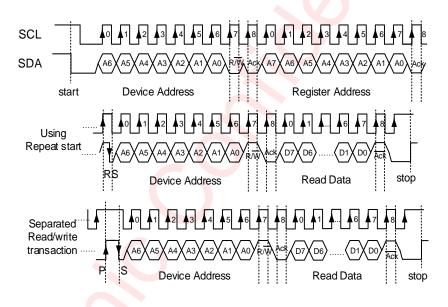

#### Device Address

AW32207 7-bit slave address (A7~A1) is 1101010 binary(0x6AH). After the START condition, the I<sup>2</sup>C master sends the 7-bit chip address followed by an eighth (A0) read or write bit (R/W). R/W= 0 indicates a WRITE function and R/W = 1 indicates a READ function.

| Table 6 | <b>Device Address</b> |  |

|---------|-----------------------|--|

|---------|-----------------------|--|

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0  |

|----|----|----|----|----|----|----|-----|

| 1  | 1  | 0  | 1  | 0  | 1  | 0  | R/W |

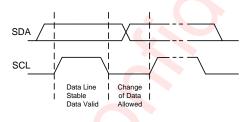

#### Data Validation

When SCL is high level, SDA level must be constant. SDA can be changed only when SCL is low level.

Figure 33 Data Validation Diagram

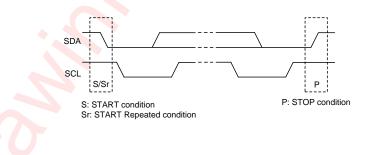

#### PC Start/Stop

I<sup>2</sup>C start: SDA changes from high level to low level when SCL is high level.

I<sup>2</sup>C stop: SDA changes from low level to high level when SCL is high level.

#### Figure 34 Start and Stop Conditions

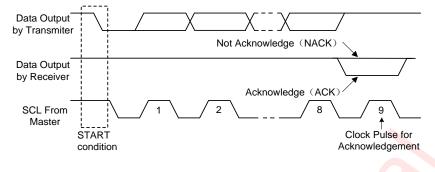

#### ACK (Acknowledgement)

ACK means the successful transfer of I<sup>2</sup>C bus data. After master sends 8bits data, SDA must be released; SDA is pulled to GND by slave device when slave acknowledges.

When master reads, slave device sends 8bit data, releases the SDA and waits for ACK from master. If ACK is send and I<sup>2</sup>C stop is not send by master, slave device sends the next data. If ACK is not send by master, slave device stops to send data and waits for I<sup>2</sup>C stop.

Figure 35 Acknowledgement Diagram

#### Write Process

awinia

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol allows a single data line to transfer both command/control information and data using the synchronous serial clock.

Each data transaction is composed of a Start Condition, a number of byte transfers (set by the software) and a Stop Condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow.

In a write process, the following steps should be followed:

- a) Master device generates START condition. The "START" signal is generated by lowering the SDA signal while the SCL signal is high.

- b) Master device sends slave address (7-bit) and the data direction bit (r/w = 0).

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master sends data byte to be written to the addressed register

- g) Slave sends acknowledge signal

- h) If master will send further data bytes the control register address will be incremented by one after acknowledge signal (repeat steps f and g)

- i) Master generates STOP condition to indicate write cycle end

#### Figure 36 I<sup>2</sup>C Write Timing

#### **Read Process**

In a read cycle, the following steps should be followed:

a) Master device generates START condition

#### **OWINC** 上海交为电子技术股份有限公司 shanghai awinic technology co., Itd.

- b) Master device sends slave address (7-bit) and the data direction bit (r/w = 0).

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master generates STOP condition followed with START condition or REPEAT START condition

- g) Master device sends slave address (7-bit) and the data direction bit (r/w = 1).

- h) Slave device sends acknowledge signal if the slave address is correct.

- i) Slave sends data byte from addressed register.

- j) If the master device sends acknowledge signal, the slave device will increase the control register address by one, then send the next data from the new addressed register.

- k) If the master device generates STOP condition, the read cycle is ended.

Figure 37 I<sup>2</sup>C Read Timing

# **Register List**

#### Status/Control Register

Address: 00H, Reset State: x1xx 0xxx.

| BIT Name  | W/R | BIT   | Function                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-----------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| OTG       | R   | B7    | Read: OTG pin status, 0-OTG pin at Low level; 1-OTG pin at High level                                                                                                                                                                                                                              |  |  |  |  |

| EN_STAT   | W/R | B6    | 0-Disable STAT pin function; 1-Enable STAT pin function (default)                                                                                                                                                                                                                                  |  |  |  |  |

| STAT      | R   | B5-B4 | HEX State HEX State<br>00 Ready; 02 Charge done;<br>01 Charge in progress; 03 Fault                                                                                                                                                                                                                |  |  |  |  |

| BOOST     | R   | B3    | 1-Boost mode; 0-Not in boost mode ( <b>default</b> )                                                                                                                                                                                                                                               |  |  |  |  |

| CHG_FAULT | R   | B2-B0 | Charge mode:       HEX       State         HEX       State       04       Output OVP;         01       VBUS OVP;       05       Thermal shutdown;         02       Sleep mode;       06       NA;         03       Bad Adaptor or V <sub>BUS</sub> <v<sub>UVLO:       07       No battery.</v<sub> |  |  |  |  |

#### **Control Register**

Address: 01H, Reset State:0011 0000.

| BIT Name | W/R | BIT   | Function                                                                            |  |  |  |  |  |

|----------|-----|-------|-------------------------------------------------------------------------------------|--|--|--|--|--|

| NA       | NA  | B7-B6 | NA                                                                                  |  |  |  |  |  |

| NA       | NA  | B5-B4 | NA                                                                                  |  |  |  |  |  |

| TE       | W/R | B3    | 1-Enable charge current termination; 0-Disable charge current termination (default) |  |  |  |  |  |

| CEN      | W/R | B2    | 1-Charger is disabled; 0-Charger is enabled (default)                               |  |  |  |  |  |

| HZ_MODE  | W/R | B1    | 1-High impedance mode; 0-Not high impedance mode ( <b>default</b> )                 |  |  |  |  |  |

| OPA_MODE | W/R | B0    | 1-B <mark>o</mark> ost mode; 0-Charger mode ( <b>default</b> )                      |  |  |  |  |  |

#### Control/Battery Voltage Register

Address: 02H, Reset State:0000 1010

| BIT Name | W/R  | BIT   | Function |                    |            |                |                   |              |              |                      |

|----------|------|-------|----------|--------------------|------------|----------------|-------------------|--------------|--------------|----------------------|

|          |      |       | Batter   | y voltage charging | g control: |                |                   |              |              |                      |

|          |      |       | HEX      | VOREG              | HEX        | VOREG          | HEX               | VOREG        | HEX          | VOREG                |

|          | •    |       | 00H      | 3.50V              | 0FH        | 3.80V          | 1EH               | 4.10V        | 2DH          | 4.40V                |

|          |      |       | 01H      | 3.52V              | 10H        | 3.82V          | 1FH               | 4.12V        | 2EH          | 4.42V                |

|          |      |       | 02H      | 3.54V(default)     | 11H        | 3.84V          | 20H               | 4.14V        | 2FH          | 4.44V                |

|          |      |       | 03H      | 3.56V              | 12H        | 3.86V          | 21H               | 4.16V        | 30H          | 4.46V                |

|          |      |       | 04H      | 3.58V              | 13H        | 3.88V          | 22H               | 4.18V        | 31H          | 4.48V                |

|          |      |       | 05H      | 3.60V              | 14H        | 3.90V          | 23H               | 4.20V        | 32H          | 4.50V                |

| VOREG    | W/R  | B7-B2 | 06H      | 3.62V              | 15H        | 3.92V          | 24H               | 4.22V        | 33H-3FH      | 4.50V                |

|          |      |       | 07H      | 3.64V              | 16H        | 3.94V          | 25H               | 4.24V        |              |                      |

|          |      |       | 08H      | 3.66V              | 17H        | 3.96V          | 26H               | 4.26V        |              |                      |

|          |      |       | 09H      | 3.68V              | 18H        | 3.98V          | 27H               | 4.28V        |              |                      |

|          |      |       | 0AH      | 3.70V              | 19H        | 4.00V          | 28H               | 4.30V        |              |                      |

|          |      |       | 0BH      | 3.72V              | 1AH        | 4.02V          | 29H               | 4.32V        |              |                      |

|          |      |       | 0CH      | 3.74V              | 1BH        | 4.04V          | 2AH               | 4.34V        |              |                      |

|          |      |       | 0DH      | 3.76V              | 1CH        | 4.06V          | 2BH               | 4.36V        |              |                      |

|          |      |       | 0EH      | 3.78V              | 1DH        | 4.08V          | 2CH               | 4.38V        |              |                      |

| OTG PL   | W/R  | B1    | 1-OT(    | Boost Enable w     | ith High l | evel (defaul   | <b>t)</b> ; 0-OTC | Boost Enal   | ole with Low | level;               |

| UIG_FL   | vv/K | ום    | not ap   | plicable to OTG p  | oin contro | l of current l | imit at PC        | OR in defaul | t mode.      |                      |

| OTG EN   | W/R  | B0    | Enabl    | e OTG Pin in H     | OST mod    | le; 0-Disable  | e OTG p           | in in HOST   | mode (de     | f <b>ault)</b> , not |

| UIG_EN   | vv/K | ы     | applic   | able to OTG pin c  | control of | current limit  | at POR i          | n default mo | de.          |                      |

#### Vender/Part/Revision Register

Address: 03H, Reset State:0100 0011.

| BIT Name | W/R | BIT   | Function                                                                                |  |  |

|----------|-----|-------|-----------------------------------------------------------------------------------------|--|--|

| Vender   | R   | B7-B5 | Vender code:010                                                                         |  |  |

| PN       | R   | B4-B3 | 6AH:00-AW32207                                                                          |  |  |

| Revision | R   | B2-B0 | 011: Revision 1.0 <b>(default)</b> ;<br>001: Revision 1.1;<br>100-111: Future Revisions |  |  |

#### Battery Termination/Fast Charge Current Register

Address: 04H, Reset State:0000 0001.

| BIT Name  | W/R | BIT   | Function     |                             |                             |                     |                                                                 |  |

|-----------|-----|-------|--------------|-----------------------------|-----------------------------|---------------------|-----------------------------------------------------------------|--|

| RESET     | W/R | B7    | reset comman |                             |                             |                     | "0", After the software<br>ns before any other I <sup>2</sup> C |  |

|           |     |       | HEX          | I <sub>CHG</sub> (mA)(68mΩ) | I <sub>CHG</sub> (mA)(56mΩ) | I <sub>CHG</sub> (m | A)(51mΩ)                                                        |  |

|           |     |       | 00           | 400                         | 485(default)                | 533                 | 3                                                               |  |

|           |     |       | 01           | 500                         | 607                         | 666                 | 3                                                               |  |

|           |     |       | 02           | 700                         | 850                         | 933                 | 3                                                               |  |

|           |     |       | 03           | 800                         | 971                         | 1066                | 6                                                               |  |

|           |     |       | 04           | 900                         | 1092                        | 120                 | )                                                               |  |

|           |     |       | 05           | 1000                        | 1214                        | 133                 | 3                                                               |  |

|           |     |       | 06           | 1100                        | 1336                        | 146                 | 6                                                               |  |

| ICHG      | W/R | B6-B3 | 07           | 1200                        | 1457                        | 160                 | 0                                                               |  |

|           |     |       | 08           | 1300                        | 1578                        | 173                 | 3                                                               |  |

|           |     |       | 09           | 1400                        | 1699                        | 186                 | 6                                                               |  |

|           |     |       | 0A           | 1500                        | 1821                        | 200                 | 0                                                               |  |

|           |     |       | 0B           | 1500                        | 1821                        | 200                 | 0                                                               |  |

|           |     |       | 0C           | 1500                        | 1821                        | 200                 | 0                                                               |  |

|           |     |       | 0D           | 1500                        | 1821                        | 200                 | 0                                                               |  |

|           |     |       | 0E           | 1500                        | 1821                        | 200                 | 0                                                               |  |

|           |     |       | OF           | 1500                        | 1821                        | 200                 | 00                                                              |  |

|           |     |       | HEX          | ITERM(mA)68m                | Ω ITERM(mA)                 | )56mΩ               | ITERM(mA)51mΩ                                                   |  |

|           |     |       | 00           | 50                          | 60                          |                     | 66                                                              |  |

|           |     |       | 01           | 100                         | 121(defau                   | ult)                | 133                                                             |  |