## BOS1211 Scalable Piezo Haptic Controller with Waveform Synthesizer

## 1 Features

- AEC-Q100 Grade 2 Qualified

- Scalable Low Power Piezo Controller

- Designed for TDK PowerHap 120 V Actuator Portfolio

- Drives up to 4 μF

- Energy Recovery

- Small Solution Footprint

- Integrated Digital Front End with SPI

- 1024-Samples Internal FIFO

- 2-kB RAM Waveform Memory

- Waveform Synthesizer

- 1.8 V to 5.0 V Digital I/O Supply

- Piezo Sensing Interface

- Multi-Actuator Synchronization

- Fast Start-Up Time of 500 μs

- Connects to 12 V Power Bus

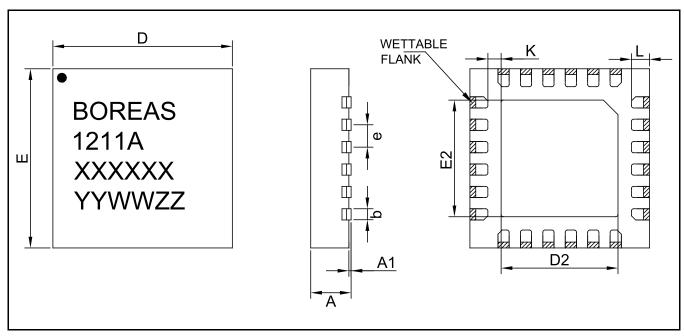

- Offered in a Wettable Flank QFN-24 Package

## 2 Applications

- Display Haptics

- Button Replacement

- Human Machine Interface

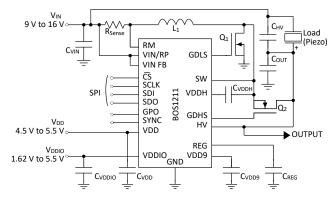

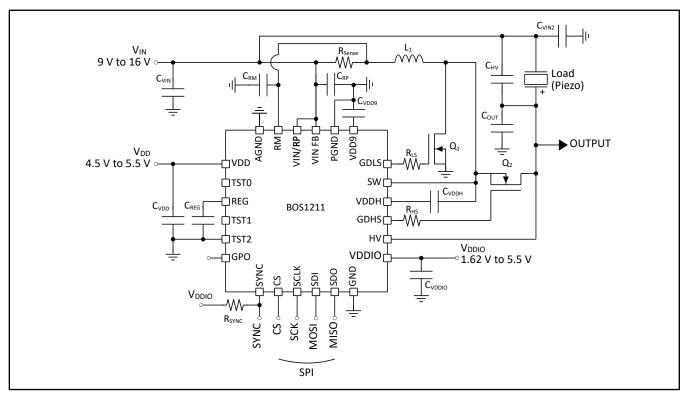

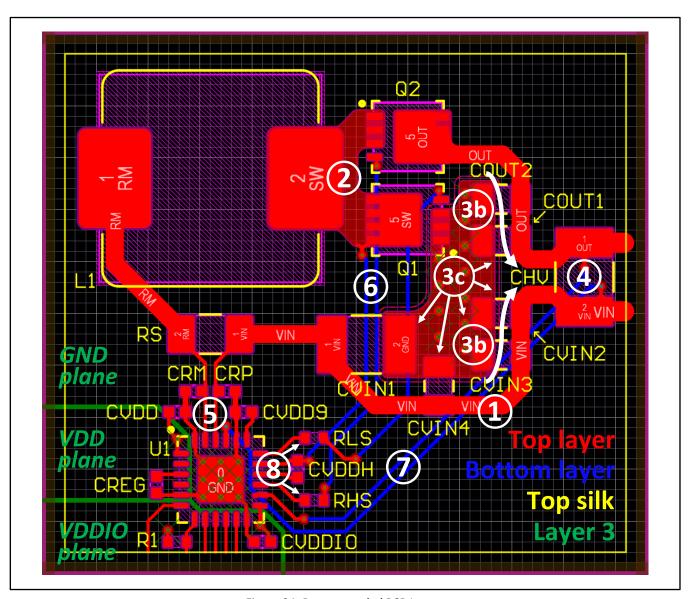

Figure 1: Simplified schematic

## 3 Description

The BOS1211 is a scalable piezo haptic controller based on our patented CapDrive™ technology. It can drive TDK's PowerHap 120 V piezo actuators or similar loads with up to 120 V HD haptic low distortion waveforms and operates from a 12 V supply voltage. The BOS1211 integrates a digital interface, low-side and high-side NMOS gate drivers for buck-boost conversion and piezo sensing capability.

The BOS1211 plays waveforms through its digital front-end and SPI interface. A flexible deep FIFO interface enables the user to continuously stream the digital waveform data for playback or to transmit burst data. The interface also integrates a waveform synthesizer and 2-kB RAM waveform memory to generate HD haptic waveforms with minimum communication bandwidth enabling two waveform generation modes: RAM playback and RAM synthesis.

The digital front-end gives access to many internal registers to optimize performance. The BOS1211 features a piezo sensing interface that can detect a pressure applied on the piezo actuator, play automatic haptic waveform feedback, and notify the host of the event.

The high-speed SPI enables the device to share a common communication bus for a multi-actuator system. The pin SYNC synchronizes multiple controllers in the same system to have waveforms phase delay within less than 2 µs.

Safety systems protect the device from damage in case of a fault.

Table 1: Product information

| PART NUMBER | DESCRIPTION           |

|-------------|-----------------------|

| BOS1211AQ   | QFN 24L 4.0mm x 4.0mm |

See section 10 for ordering information.

# **Table of Content**

| 1 FEATURES                                      | 1  |

|-------------------------------------------------|----|

| 2 APPLICATIONS                                  | 1  |

| 3 DESCRIPTION                                   |    |

| TABLE OF CONTENT                                |    |

| 4 PINS CONFIGURATION AND FUNCTIONS              |    |

| 5 SPECIFICATIONS                                |    |

|                                                 |    |

| 5.1 ABSOLUTE MAXIMUM RATINGS                    |    |

| 5.2 PACKAGE THERMAL INFORMATION                 |    |

|                                                 |    |

| 5.4 ELECTRICAL CHARACTERISTICS                  |    |

| 5.6 TYPICAL PERFORMANCE CHARACTERISTICS         |    |

|                                                 |    |

| 6 FUNCTIONAL DESCRIPTION                        | 10 |

| 6.1 Overview                                    | _  |

| 6.2 Features                                    | _  |

| 6.3 AUTOMATIC OUTPUT SHUTDOWN                   |    |

| 6.4 SPI Interface                               |    |

| 6.5 Direct Mode                                 | -  |

| 6.6 FIFO Mode                                   |    |

| 6.7 RAM PLAYBACK                                |    |

| 6.8 RAM Synthesis Mode                          |    |

| 6.9 Piezo Actuator Sensing                      |    |

| 6.10 WFS COMMAND INTERPRETER                    |    |

| 6.11 Main Register Map                          | 40 |

| 7 IMPLEMENTATION                                | 56 |

| 7.1 Typical Configuration                       | 56 |

| 7.2 External Components                         | 57 |

| 7.3 Initialization                              | 58 |

| 7.4 DESIGN METHODOLOGY: SELECTION OF COMPONENTS | 59 |

| 7.5 Design Methodology: Programming             | 61 |

| 8 LAYOUT                                        | 62 |

| 9 MECHANICAL - BOS1211AQ (QFN)                  | 64 |

| 9.1 PACKAGE DESCRIPTION                         | 64 |

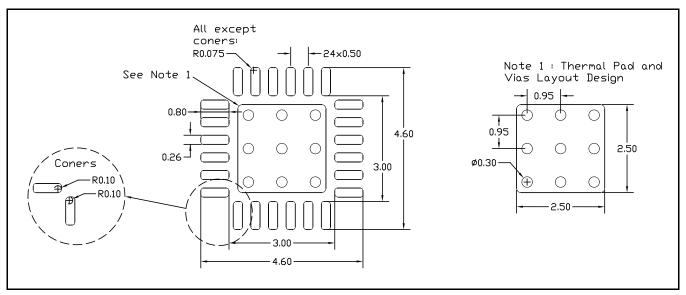

| 9.2 PACKAGE SOLDERING FOOTPRINT                 |    |

| 9.3 QFN Reflow                                  |    |

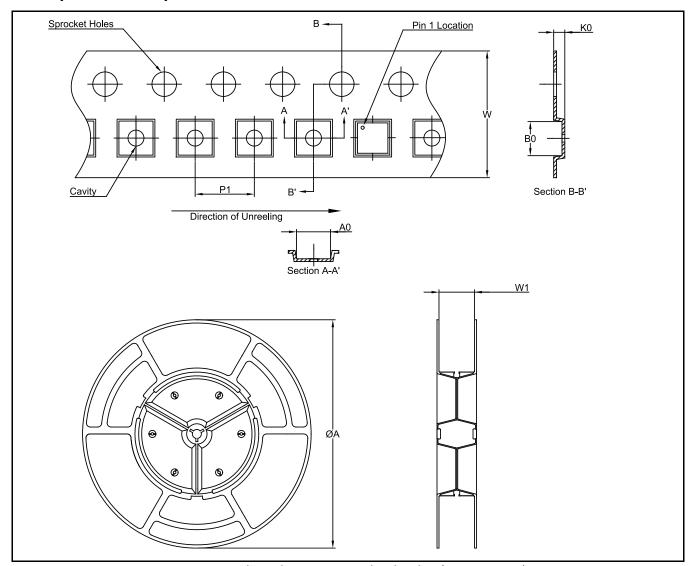

| 9.4 TAPE AND REEL SPECIFICATION                 |    |

| 10 ORDERING INFORMATION                         | 67 |

| 11 DOCUMENT HISTORY                             | 68 |

| 12 NOTICE AND WARNING                           | 69 |

# **4 Pins Configuration and Functions**

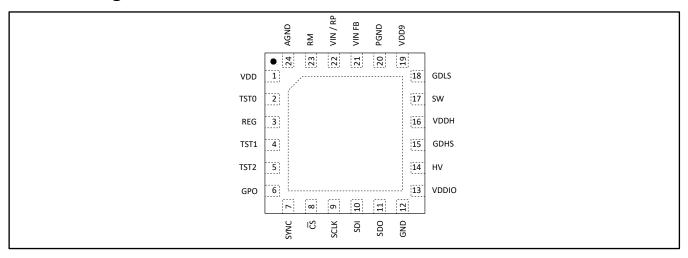

Figure 2: QFN 24L 4.0mm  $\times$  4.0 mm package with exposed thermal pad (TOP VIEW; NOT TO SCALE)

Table 2: QFN 24L 4.0mm x 4.0mm pin description

| PIN NO. | PIN NAME | TYPE         | DESCRIPTION                                                |

|---------|----------|--------------|------------------------------------------------------------|

| 1       | VDD      | Power        | Main controller supply                                     |

| 2       | TST0     | -            | Factory test pin: must be kept floating                    |

| 3       | REG      | Power        | Internal 1.8 V regulator output                            |

| 4       | TST1     | -            | Factory test pin: must be kept floating                    |

| 5       | TST2     | Input        | Factory test pin: must be connected to GND                 |

| 6       | GPO      | Output       | Configurable output                                        |

| 7       | SYNC     | Input/Output | Multi-chip synchronizing pin                               |

| 8       | CS       | Input        | SPI chip select                                            |

| 9       | SCLK     | Input        | SPI clock                                                  |

| 10      | SDI      | Input        | SPI serial data in                                         |

| 11      | SDO      | Output       | SPI serial data out                                        |

| 12      | GND      | Power        | Power supply ground                                        |

| 13      | VDDIO    | Power        | Power supply for digital IO                                |

| 14      | HV       | Input        | Voltage sense of high-voltage piezo signal                 |

| 15      | GDHS     | Output       | Gate driver output to high side NMOS switch                |

| 16      | VDDH     | Output       | Floating supply for high side gate driver                  |

| 17      | SW       | Input        | Power converter switch pin                                 |

| 18      | GDLS     | Output       | Gate driver output to low side NMOS switch                 |

| 19      | VDD9     | Power        | 9 V internal gate driver supply                            |

| 20      | PGND     | Power        | Power supply ground connection to the low-side gate driver |

| 21      | VIN FB   | Input        | Voltage sense of low voltage piezo signal                  |

| 22      | VIN/RP   | Power/Input  | 12 V Supply /Current sense positive input                  |

| 23      | RM       | Input        | Current sense negative input                               |

| 24      | AGND     | Power        | Power supply ground                                        |

## **5 Specifications**

## **5.1 Absolute Maximum Ratings**

Table 3: Absolute maximum ratings<sup>‡</sup>

|   | SYMBOL           | PARAMETER                                | MIN  | NOM | MAX | UNIT |

|---|------------------|------------------------------------------|------|-----|-----|------|

| 1 |                  | Voltage at pins HV, GDHS, GDLS, VDDH, SW | -0.3 |     | 140 | ٧    |

| 2 |                  | Voltage at pins RM, VIN/RP, VIN FB       | -0.3 |     | 28  | V    |

| 3 |                  | Voltage at all other pins                | -0.3 |     | 7   | V    |

| 4 | T <sub>stg</sub> | Storage temperature                      | -65  |     | 150 | °C   |

| 5 | Tı               | Junction temperature                     | -40  |     | 150 | °C   |

<sup>‡</sup>Exceeding these values may cause permanent damage. Functional operation under these conditions is not guaranteed.

## **5.2 Package Thermal Information**

Table 4: Package thermal information

|   | SYMBOL | PARAMETER                              | PACKAGE               | MIN | NOM  | MAX | UNIT |

|---|--------|----------------------------------------|-----------------------|-----|------|-----|------|

| 1 | Өла    | Junction-to-ambient thermal resistance | QFN 24L 4.0mm x 4.0mm |     | 28.8 |     | °C/W |

## **5.3 Recommended Operating Conditions**

Table 5: Recommended operating conditions

|   | SYMBOL                  | PARAMETER                          | TEST CONDITIONS                                     | MIN  | NOM | MAX  | UNIT |

|---|-------------------------|------------------------------------|-----------------------------------------------------|------|-----|------|------|

| 1 | TA                      | Operating Temperature              | Operating free-air temp.                            | -40  |     | 105  | °C   |

| 2 | V <sub>IN</sub>         | Actuator input supply voltage      |                                                     | 9    |     | 16   | V    |

| 3 | V <sub>DD</sub>         | Supply voltage                     |                                                     | 4.5  |     | 5.5  | V    |

| 4 | V <sub>DDIO</sub> (1)   | I/O Supply voltage                 |                                                     | 1.62 |     | 5.5  | V    |

| 5 | C <sub>ISS-Q2</sub> (2) | Gate capacitance of Q <sub>2</sub> |                                                     |      |     | 2    | nf   |

| 6 | C <sub>Load</sub>       | Load capacitance                   | f <sub>sig</sub> = 300 Hz, V <sub>OUT</sub> = 120 V |      |     | 4    | μF   |

| 7 | L <sub>1</sub>          | Inductance                         |                                                     |      | 10  |      | μН   |

| 8 | R <sub>sense</sub> (3)  | Sense resistor                     |                                                     | 30   |     | 1000 | mΩ   |

| 9 | fоит                    | Output frequency                   |                                                     | 3.9  |     | 1000 | Hz   |

<sup>(1)</sup> Digital I/O voltage (V<sub>DDIO</sub>) must match with controller SPI interface voltage (MCU).

<sup>(2)</sup> CISS-Q2 and CVDDH determine the voltage at GDHS pin. See section 7.4.5 and 7.4.6 for more information.

<sup>(3)</sup> See section 7.4.3 for R<sub>sense</sub> selection.

## **5.4 Electrical Characteristics**

Table 6: Electrical characteristics. Conditions:  $T_A = -40$  °C to 105 °C,  $V_{DD} = 5$  V,  $V_{IN} = 12$  V (unless otherwise noted)

|    | SYMBOL               | PARAMETER                                               | TEST CONDITIONS                                                                                                                                           | MIN                    | NOM            | MAX                    | UNIT |

|----|----------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|------------------------|------|

| 1  | V <sub>REG</sub>     | Voltage at REG pin                                      |                                                                                                                                                           | 1.75                   | 1.80           | 1.85                   | V    |

| 2  | $V_{DD9}$            | Voltage at VDD9 pin                                     |                                                                                                                                                           |                        | 9.6            |                        | V    |

| 3  | V <sub>IL</sub>      | Digital low-level input voltage (1)                     |                                                                                                                                                           |                        |                | 0.5                    | V    |

| 4  | V <sub>IH</sub>      | Digital high-level input voltage <sup>(1)</sup>         |                                                                                                                                                           | V <sub>DDIO</sub> ×0.7 |                | V <sub>DDIO</sub> +0.3 | V    |

| 5  | Vol                  | Digital low-level output voltage (1)                    |                                                                                                                                                           |                        |                | 0.4                    | V    |

| 6  | V <sub>OH</sub>      | Digital high-level output voltage (1)                   |                                                                                                                                                           | V <sub>DDIO</sub> ×0.8 |                |                        |      |

| 7  | V <sub>OUT(FS)</sub> | Full-scale OUTPUT voltage (at HV pin) (1)               |                                                                                                                                                           | 117.5                  | 120            | 122.5                  | V    |

| 8  | I <sub>Q_VIN</sub>   | V <sub>IN</sub> supply quiescent current                | SLEEP IDLE, OE bit = 0x0 IDLE, OE bit = 0x1                                                                                                               |                        | 6<br>14<br>350 |                        | μА   |

| 9  | IQ_VDD               | V <sub>DD</sub> supply quiescent                        | SLEEP (1)                                                                                                                                                 |                        | 1              | 10                     | μΑ   |

|    |                      | current                                                 | IDLE, OE bit = 0x0<br>IDLE, OE bit = 0x1                                                                                                                  |                        | 1 2            | 3.5<br>4               | mA   |

| 10 | I <sub>VIN,AVG</sub> | Average V <sub>IN</sub> supply current during operation | $\begin{array}{ll} f_{sig} & = DC^{\;(2)} \\ V_{OUT} & = 120 \; V \\ C_{Load} & = 4 \; \mu F \\ V_{IN} & = 12 \; V \end{array}$                           |                        | 3              |                        | mA   |

|    |                      |                                                         | $\begin{array}{ll} f_{sig} & = 300 \; \text{Hz} \\ V_{OUT} & = 120 \; \text{V} \\ C_{Load} & = 4 \; \mu\text{F} \\ V_{IN} & = 12 \; \text{V} \end{array}$ |                        | 250            |                        | mA   |

| 11 | IGATELS              | Max. peak transient current at GDLS pin                 | Source, <u>SLS</u> = 0x3<br>Sink, <u>SLS</u> = 0x3                                                                                                        |                        | 1200<br>850    |                        | mA   |

| 12 | IGATEHS              | Max. peak transient current at GDHS pin                 | Source, SHS=0x3<br>Sink, SHS=0x3                                                                                                                          |                        | 1100<br>800    |                        | mA   |

| 13 | VGATELS              | Voltage at GDLS pin activating Q <sub>1</sub>           |                                                                                                                                                           |                        | 8.6            |                        | V    |

| 14 | THD+N                | Total Harmonic Distortion<br>+ Noise <sup>(1)</sup>     | $\begin{array}{ll} f_{sig} &= 300 \ \text{Hz} \\ \text{V}_{\text{OUT}} &= 120 \ \text{V} \\ \text{C}_{\text{Load}} &= 4 \ \mu\text{F} \end{array}$        |                        |                | 1                      | %    |

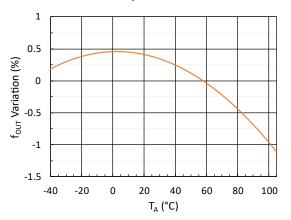

| 15 | fs                   | Sampling rate for waveform playback (3)                 | 25°C, <u>PLAY[2:0]</u> = 0x0<br>25°C, <u>PLAY[2:0]</u> = 0x7                                                                                              | 998<br>7.8             | 1024<br>8      | 1050<br>8.2            | ksps |

| 16 | DHL                  | Sensing Detection to<br>Haptic feedback latency (1)     | Time from sensing detection event to automatic playback                                                                                                   |                        |                | 100                    | μs   |

<sup>(1)</sup> Specification is assured by design and characterization data.

<sup>(2) &</sup>lt;u>PARCAP[7:0]</u> bits can be adjusted to reduce power consumption for DC output.

<sup>(3)</sup> See Figure 12 for output frequency variation as a function of temperature.

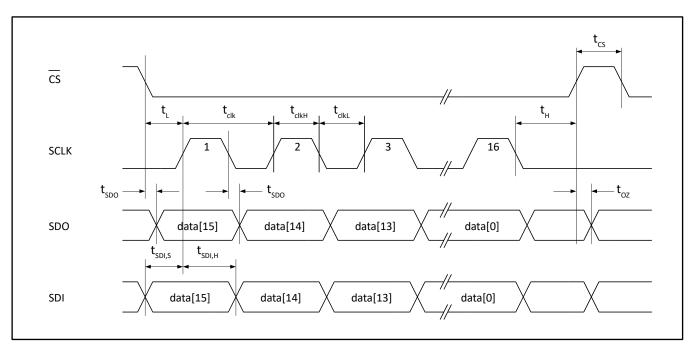

## 5.5 Timing Characteristics (SPI)

Table 7: Timing characteristics. Conditions:  $T_A = -40$ °C to 105°C,  $V_{DDIO} = 3.3$  V to 5.5 V, SDO load = 20 pF. Specifications are assured by design and characterization data.

|    | SYMBOL             | PARAMETER                                                                     | MIN | NOM | MAX | UNIT |

|----|--------------------|-------------------------------------------------------------------------------|-----|-----|-----|------|

| 1  | t <sub>clk</sub>   | Clock period (1)                                                              | 28  |     |     | ns   |

| 2  | t <sub>clkL</sub>  | Clock Low period                                                              | 15  |     |     | ns   |

| 3  | t <sub>clkH</sub>  | Clock High period                                                             | 10  |     |     | ns   |

| 4  | t∟                 | Time between $\overline{\text{CS}}$ falling edge and SCLK rising edge         | 18  |     |     | ns   |

| 5  | tн                 | Time between SCLK last falling edge and rising edge of $\overline{\text{CS}}$ | 15  |     |     | ns   |

| 6  | t <sub>CS</sub>    | CS High time between two transmissions (2)                                    | 150 |     |     | ns   |

| 7  | t <sub>SDI,S</sub> | Input data setup time                                                         | 4.5 |     |     | ns   |

| 8  | t <sub>SDI,H</sub> | Input data hold time                                                          | 3.5 |     |     | ns   |

| 9  | t <sub>SDO</sub>   | CS or SCLK falling edge to data output valid (1)                              |     |     | 14  | ns   |

| 10 | toz                | CS rising edge to SDO high impedance                                          |     |     | 14  | ns   |

<sup>(1)</sup> Specification depend on  $V_{DDIO}$  and SDO load, see Table 8.

Table 8: Maximum SPI frequency vs. V<sub>DDIO</sub> and SDO load.

|   | V <sub>DDIO</sub> | MAXIMUM SPI FREQUENCY (1/t <sub>clk</sub> ) |                  | UNIT |

|---|-------------------|---------------------------------------------|------------------|------|

|   |                   | SDO load = 20 pF                            | SDO load = 80 pF |      |

| 1 | 1.8 V             | 13                                          | 10               | MHz  |

| 2 | 2.5 V             | 28                                          | 20               | MHz  |

| 3 | 3.3 V             | 35                                          | 30               | MHz  |

| 4 | 5.5 V             | 35                                          | 30               | MHz  |

<sup>(2)</sup> A minimum delay of 400 ns is required if the fist transaction is used to set BC[4:0] bits and the second transaction is used for data reading.

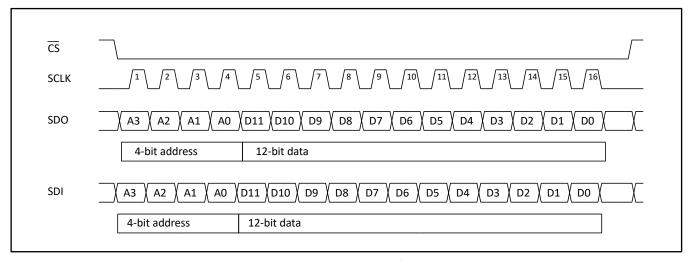

Figure 3: SPI timing diagram

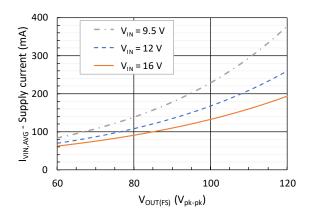

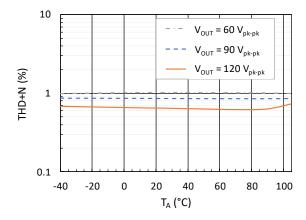

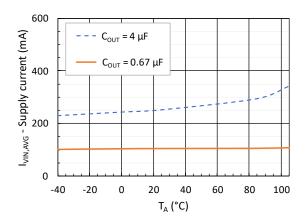

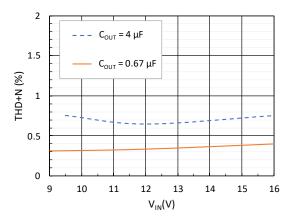

## **5.6 Typical Performance Characteristics**

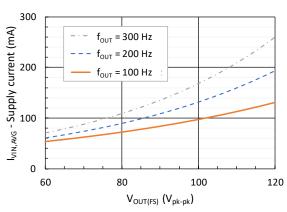

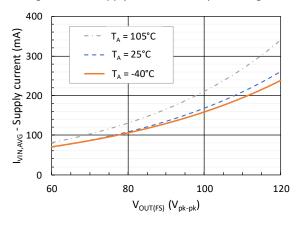

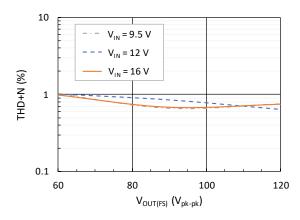

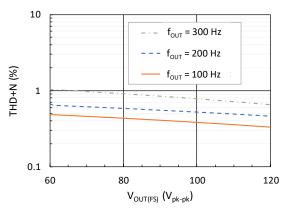

Typical performance characteristics for the following conditions:  $T_A = 25$ °C,  $V_{IN} = 12$  V,  $C_{OUT} = 4$   $\mu$ F,  $V_{OUT} = 120$  V<sub>pk-pk</sub> and  $f_{OUT} = 300$  Hz (unless otherwise noted).

Figure 4: V<sub>IN</sub> supply current vs output voltage

Figure 6: V<sub>IN</sub> supply current vs output voltage

Figure 8: V<sub>IN</sub> supply current vs operating free-air temperature

Figure 5: Total harmonic distortion + noise vs output voltage

Figure 7: Total harmonic distortion + noise vs output voltage

Figure 9: Total harmonic distortion + noise vs operating free-air temperature

Figure 10: V<sub>IN</sub> supply current vs operating free-air temperature

Figure 12: Output frequency variation vs operating free-air temperature

Figure 11: Total harmonic distortion + noise vs input voltage<sup>2</sup>

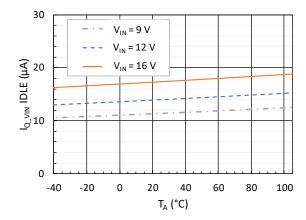

Figure 13:  $V_{IN}$  supply quiescent current in IDLE state vs operating free-air temperature

BT002DDS01.01 - Issue 5

<sup>&</sup>lt;sup>2</sup> Data for a load of 4 μF starts at a  $V_{IN}$  of 9.5 V because playing a waveform while having a  $V_{IN}$  lower than 9.5 V triggers the UVLO12 error flag.

## **6 Functional Description**

#### 6.1 Overview

The BOS1211 is a scalable haptic piezo actuator controller with integrated digital front end, including a FIFO and a Waveform Synthesizer (WFS). The BOS1211 implements a dynamic buck-boost conversion with energy recovery, based on Boreas's patented CapDrive™ Technology. The BOS1211 integrates a low-side and high-side NMOS gate drivers. The controller is compatible with 12 V systems. It can generate HD haptic waveforms with amplitude up to 120 V for a wide range of piezo actuators including TDK PowerHap 120 V portfolio. Interpolation between samples is done to smooth the haptic waveform.

The digital interface enables the user to stream the waveforms data from any MCU with an SPI port. A flexible FIFO interface enables the user to continuously stream the digital waveform data for playback or to transmit burst data. Data from the FIFO can be read at different sample rates. The digital front-end also integrates a Waveform Synthesizer (WFS) and 2-kB on-chip RAM with two waveform generation modes: RAM Playback and RAM Synthesis. These two modes allow haptic waveforms generation with minimal intervention from the host MCU.

The digital font-end gives access to many internal registers, enabling the user to optimize the performance of the device for a specific application. For instance, the voltage on the piezo actuator can be read at any time, allowing the development of advanced sensing algorithms and use a piezo actuator as a force sensor at the input of a system. Finally, the BOS1211 also includes an embedded sensing comparator enabling the controller to detect a pressure applied on a piezo actuator, automatically play a pre-programmed haptic waveform feedback and notify the MCU of an event.

The BOS1211 can use many commercial off-the-shelf (COTS) inductors. The inductor can be chosen to optimize the power, size or performance trade-off for the user application. With a start-up time of less than 500 µs from SLEEP state, the BOS1211 is ideal for low latency haptic feedback.

#### 6.2 Features

#### 6.2.1 Digital Front-End Interface

The BOS1211 uses a 35 MHz SPI target interface. This high-speed communication interface enables to share a common communication bus for multi-actuator systems. The digital front-end gives access to internal registers that control the device operation and performance, see section 7.5 for details.

#### 6.2.2 GPO

One general-purpose digital output (GPO) is available and can be used as an interruption to notify the host MCU of various events using  $\underline{\mathsf{GPO[2:0]}}$  bits such as haptic detection events or an error. The GPO is a push-pull output between  $V_{DDIO}$  and GND.

### 6.2.3 Flexible Haptic Waveform Generation

#### 6.2.3.1 Direct Mode

With MODE[1:0] bits set to 0x0, the haptic waveform samples are played as they are sent from the host MCU to RAM using REFERENCE register. The rate at which the RAM data is read to generate the haptic waveform is set by PLAY[2:0] bits. See section 6.5 for details.

#### **6.2.3.2 FIFO Mode**

A 1024-sample FIFO is available for waveform playback with MODE[1:0] bits set to 0x1. The FIFO entries are appended every time waveform samples are written in the REFERENCE register. Digital samples are represented as 12-bit unsigned values. If OE bit is set to 0x1, the FIFO entries are read automatically out of the FIFO at a rate set by PLAY[2:0] bits. See section 6.6 for more details.

#### 6.2.3.3 RAM Playback Mode

RAM Playback mode is selected with MODE[1:0] bits set to 0x2. In RAM Playback mode, the on-chip RAM of 2 kB is used to store haptic waveforms as waveform amplitude samples in 12-bit unsigned format with minimum interventions from the MCU. The waveform is sampled at a rate set by PLAY[2:0] bits. See section 6.7 for details.

### 6.2.3.4 RAM Synthesis Mode

RAM Synthesis mode is selected with MODE[1:0] bits set to 0x3. In RAM Synthesis mode, the BOS1211 uses the Waveform Synthesizer (WFS) to generate waveforms using parameters stored in the 2 kB RAM. RAM Synthesis mode allows generating sinusoidal waveforms of various amplitudes and frequencies without having to send every sample of the waveform to RAM as is the case with RAM Playback mode. This allows complex waveforms to be produced with minimal data communication. See section 6.8 for details.

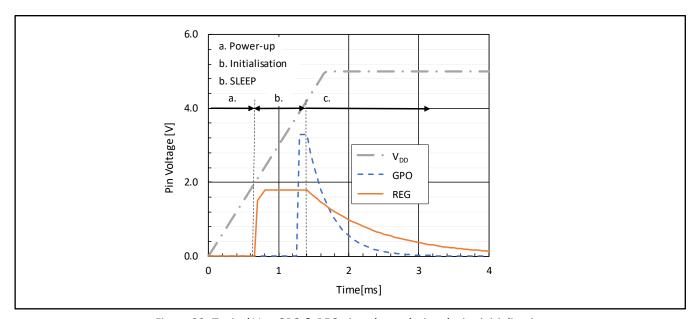

#### 6.2.4 SLEEP state

When no haptic waveform is being requested ( $\underline{OE}$  bit set to 0x0), the BOS1211 can enter in one of the two low-power modes: IDLE or SLEEP state.  $\underline{DS}$  bit sets the device power mode when no haptic waveform is requested. By default, the power mode is IDLE ( $\underline{DS}$  bit set to 0x0). SLEEP state is selected when  $\underline{DS}$  bit is set to 0x1. In SLEEP, the BOS1211 is in its lowest power state and all registers are set back to their default values as well as the RAM data is reset. The BOS1211 goes out of SLEEP state on pin  $\overline{CS}$  falling edge.

#### 6.2.5 Low Latency Startup

The BOS1211 features a fast start-up time. From IDLE or SLEEP state, the device takes approximately 500  $\mu$ s to start playing the waveform when the auto-calibration piezo zeroing is set to 500  $\mu$ s (SHORT[1:0] bits set to 0x0). That makes the BOS1211 a very small contributor to system latency.

#### 6.2.6 Piezo Actuator Sensing

The digital front-end gives access to internal registers 0xA and 0x12 that allow the use of piezo actuators as a force sensor.

The BOS1211 features an embedded sensing comparator that can be configured to detect a sensing event. The sensing comparator can adapt to a specific application by setting its voltage threshold (<a href="STHRESH[8:0]">STHRESH[8:0]</a> bits), hold time (<a href="REP[2:0]">REP[2:0]</a>) and crossing direction (<a href="SIGN">SIGN</a> bit).

It is also possible to automatically trigger an programmed waveform when a sensing event is detected by the sensing comparator. GPO output pin can be configured using <a href="GPO[2:0]">GPO[2:0]</a> bits to inform the MCU that a sensing event occurred or that the triggered waveform has finished playing. Setting <a href="BC[4:0]">BC[4:0]</a> bits to 0x12 will output sensing voltage data, which can be read at any time and is useful for MCU-based customized sensing algorithms. See section 6.9 for details.

#### 6.2.7 Device Reset

The BOS1211 device has software-based reset functionality. When <u>RST</u> bit is set, all registers are set to their default value and the BOS1211 goes to IDLE state. <u>RST</u> bit self-clears once the reset is complete.

The following sequence must be done to safely reset the device while playing a waveform in FIFO or Direct mode:

- 1. Set CONFIG.OE bit must be set to 0x0.

- 2. Wait for the device to be in IDLE by polling <a href="IC STATUS.STATE[1:0]">IC STATUS.STATE[1:0]</a> bits.

- 3. Reset the device by setting RST bit to 0x1.

### 6.2.8 Actuator Synchronization

Multiple BOS1211 devices can play haptic waveforms simultaneously using the SYNC pin. This feature allows synchronizing a waveform across several devices with a phase delay of less than 2  $\mu$ s between them.

Synchronization is achieved by connecting the SYNC pin of all devices together. A 10 k $\Omega$  pull-up resistor is needed between SYNC pin node and V<sub>DDIO</sub>. Synchronization is performed as the wave is played with a signal on the SYNC pin having a frequency that depends on the sampling rate defined by <u>PLAY[2:0]</u> bits.

The following sequence presents an example allowing synchronizing two BOS1211 devices:

- 1. On both devices perform the following configuration:

- a. In the **CONFIG** register:

- i. Set <u>CONFIG.OE</u> bit to 0x0 to disable the haptic waveform generation.

- ii. Set CONFIG.PLAY[2:0] bits to the desired sampling rate.

- iii. Set CONFIG.SYNC bit to 0x1 to enable device synchronization.

- b. Set RAM.MODE[1:0] bits to 0x2 or 0x3 to select RAM Playback or RAM Synthesis mode.

- c. Properly configure the waveform depending on the mode selected (see section 6.7 or 6.8).

- 2. Set CONFIG.OE bit to 0x1 on device 1.

- 3. Set **CONFIG.OE** bit to 0x1 on device 2 and waveform will start playing on both devices.

#### **6.2.9 Adjustable Current Limit**

The maximum current of the BOS1211 power converter must be limited to avoid damage to the inductor. Current flowing in the inductor is determined by the BOS1211 by measuring the voltage drop across  $R_{\text{sense}}$  placed between pins VIN/RP and RM. The current limit of the power converter is adjusted by selecting the proper  $R_{\text{sense}}$  value (see section 7.4.3 for more detail).

The current limit of Q<sub>1</sub> and Q<sub>2</sub> NMOS transistors should be selected based on the following:

- Ensure that the current is lower than the saturation limit of the inductor L<sub>1</sub>.

- Ensure that the current is high enough to allow sufficient energy transfer to and from the piezo actuator.

The circuit should be tested under worst-case conditions to ensure that the BOS1211 will meet the bandwidth requirement of the application (see section 7.4.5 for more detail).

#### 6.2.10 Energy Recovery

The BOS1211 implements bidirectional power transfer: input  $(V_{IN})$  to OUTPUT, and OUTPUT to input  $(V_{IN})$ , which makes the device power efficient. Such architecture enables the recovery of the energy accumulated on the capacitive load and transfers it back to the input  $(C_{VIN})$ . The internal controller determines the direction of the power flow during waveform playback.

#### 6.2.11 Adjustable Internal Clock

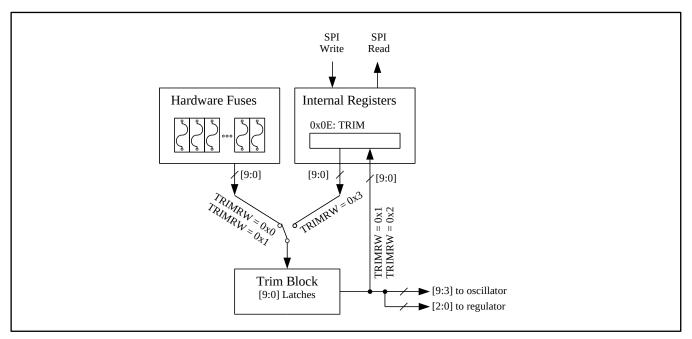

The internal BOS1211 clock oscillator frequency is trimmed during fabrication using hardware fuses. When initialized, the BOS1211 retrieves the hardware fuse values and push them to the TRIM block to adjust the oscillator frequency based on the fuse values (Figure 21). The <u>TRIM</u> register allows modifying the TRIM value to adjust oscillator frequency.

This feature can be used to match the external system clock frequency with the BOS1211 internal clock frequency, which is used to determine the FIFO read-out rate. This might be needed to minimize waveforms distortion if the user writes waveform data at a constant rate to the FIFO, without managing space available in it. To successfully adjust internal clock frequency, OE bit must be set to 0x0.

The internal oscillator can be adjusted with the following sequence:

- 1. Set OE bit to 0x0.

- 2. Set TRIM.TRIMRW[1:0] bits to either one of the following values:

- a. Set to 0x1 to latch the hardware fuses and push their value into the TRIM block and the TRIM register, or

- b. Set to 0x2 to retrieve the oscillator trim value contained in the TRIM block and push it to the TRIM register.

- 3. Wait for 1 ms.

- 4. Read TRIM.TRIM OSC[6:0] bits to get the internal oscillator trim value specific to the device.

- 5. In one transaction, set the TRIM register with the following fields:

- a. TRIM.TRIM OSC[6:0] bits set to the desired value.

- b. TRIM.TRIMRW[1:0] bits set to 0x3 to write TRIM OSC[6:0] value to TRIM block.

The same procedure can be used to adjust the internal 1.8 V regulator voltage using TRIM REG[2:0] bit instead of TRIM OSC[6:0].

#### 6.2.12 Fault Behavior

This section lists the various faults detected by the device. Note that the faults detected by the device may be caused by the following:

- Device operating outside of its safe operating conditions.

- Wrong component value (e.g., R<sub>sense</sub>, C<sub>HV</sub> or L<sub>1</sub>).

- Noise induced by improper printed circuit board layout.

If one of the following faults is detected, the device will safely ramp down the OUTPUT node voltage to  $V_{\text{IN}}$  and raise an error flag with a specific error code.

#### 6.2.12.1 Overvoltage

If an overvoltage condition at the HV pin is detected during waveform generation,  $\underline{OVV}$  bit is set, and the OUTPUT node voltage will safely ramp down to  $V_{DD}$ . A software reset ( $\underline{RST}$  bit set to 0x1) is required to clear the fault and resume normal operation.

#### 6.2.12.2 Output Short Circuit

The BOS1211 has an output short circuit protection to prevent excessive current to flow because of a short-circuit load. In case the short circuit condition is detected during waveform generation, <u>SC</u> bit is set and BOS1211 is put in IDLE state. A software reset (<u>RST</u> bit set to 0x1) is required to clear the fault and resume normal operation.

#### 6.2.12.3 Overtemperature

The BOS1211 has an internal temperature sensor that puts the device in IDLE state in case the die temperature exceeds 145 °C. In this condition, <u>OVT</u> bit is set and will clear automatically once conditions are safe for a restart.

The BOS1211 device is unlikely to reach 145  $^{\circ}$ C even during continuous operation at maximum load in the T<sub>A</sub> operating range because of its low power dissipation.

#### **6.2.12.4 Brownout**

The BOS1211 has internal brownout protections. If  $V_{REG}$  goes below 1 V, the device issues a reset signal, and all registers are set back to their default value. When  $V_{REG}$  goes back to a normal operating voltage, the BOS1211 goes to the IDLE state.

#### 6.2.12.5 Under Voltage/Over Voltage Lockout

The controller also monitors the  $V_{IN}$  and  $V_{DD}$  supplies to ensure the minimum conditions are met to operate. The controller won't start a waveform if the voltage is below or above specified limits. Table 9 presents those limits.

If an under/overvoltage condition at  $V_{IN}$  is detected during waveform generation, the following events occur:

- UVLO12/OVLO12 bit is set to 0x1.

- STATE[1:0] bits are set to 0x3 (ERROR state).

If an undervoltage condition at V<sub>DD</sub> is detected, the following events occur:

- UVLO5 bit is set to 0x1.

- STATE[1:0] bits are set to 0x3 (ERROR state).

The BOS1211 will go to IDLE state (STATE[1:0] bits to 0x0) with the following conditions:

- V<sub>IN</sub> and V<sub>DD</sub> go back to a normal operating voltage.

- OE bit is reset to 0x0.

Table 9: Under voltage / over voltage lockout limits

| Supply   | UVLO limit | OVLO limit | Unit |

|----------|------------|------------|------|

| Vin      | 8.8        | 19.9       | V    |

| $V_{DD}$ | 4.4        | N/A        | V    |

#### 6.2.12.6 Current Detection Status Fault

For proper operation, the BOS1211 monitors the current using R<sub>sense</sub> resistor connected to VIN/RP and RM pins. If no current is detected during waveform generation, the following event occurs:

- IC STATUS.IDAC fault bit is set.

- IC STATUS.STATE[1:0] bits are changed to 0x3 (ERROR state).

Typically, IDAC bit is set when R<sub>sense</sub> or L<sub>1</sub> is disconnected.

The BOS1211 will go to IDLE state (STATE[10] bits to 0x0) with the following conditions:

- V<sub>IN</sub> and V<sub>DD</sub> go back to a normal operating voltage.

- OE bit is reset to 0x0.

## 6.3 Automatic Output Shutdown

<u>TOUT</u> bit allows programming a 4 ms timeout delay after which the device will automatically go to SLEEP if it didn't receive a proper communication on its digital interface.

### 6.4 SPI Interface

A target SPI port enables communication with the BOS1211. SPI is a 4-wire synchronous serial interface that uses two control lines and two data lines: Chip Select ( $\overline{CS}$ ), Serial Clock (SCLK), Serial Data Output (SDO) and Serial Data Input (SDI). These signals are in the V<sub>DDIO</sub> voltage domain.

The SPI interface supports 16 bits per transfer. Transfer is done in full duplex: data is output on SDO at the same time data is sent on SDI.

SPI transmission starts when  $\overline{CS}$  line goes low and ends when  $\overline{CS}$  line goes high. Each SPI target device requires its own  $\overline{CS}$  line from the controller. The Figure 14 shows the correct configuration for the SPI Controller. Because different manufacturers have different definitions of SPI modes, the user should rely on Figure 14 to select the appropriate SPI mode for its MCU.

The SPI communication bus features the following:

- 1. Each transmission is 16 bits.

- 2. MSB is sent first.

- 3. Data is latched on the rising edge of SCLK.

- 4. Input Data should be transitioned on the falling edge of SCLK.

- 5. Data rates up to 35 Mbps are supported.

- 6. Single and burst read/write transmissions are supported. For burst data transmission,  $\overline{\text{CS}}$  line can be maintained low.

Figure 14: SPI typical specification

#### 6.5 Direct Mode

In Direct mode (MODE[1:0] bits set to 0x0), the haptic waveform samples are played as they are sent from the host MCU to the <u>REFERENCE</u> register. The rate at which the data is read to generate the haptic waveform is set by <u>PLAY[2:0]</u> bits.

Data management and synchronization can be facilitated by setting GPO [2:0] bits to 0x7 to allow the GPO to generate an interruption pulse that notifies the MCU when the device is ready to receive the next sample.

When MODE[1:0] bits is set to 0x0 to use Direct mode, RAM is not used and its content previously written using RAM Playback mode (section 6.7) or RAM Synthesis mode (section 6.8) is preserved.

Note that waveforms should begin and end with 0 V amplitude.

### **6.5.1 Typical Operation Sequence**

The following sequence use Direct mode to play haptic waveforms:

- 1. Set <a href="RAM.MODE[1:0]">RAM.MODE[1:0]</a> bits to 0x0 to select Direct mode.

- 2. In the CONFIG register:

- a. Set <u>CONFIG.OE</u> to 0x1.

- b. Set CONFIG.PLAY[2:0] to the desired sampling rate.

- 3. Set <u>SPI.GPO[2:0]</u> bits to 0x7 to allow the GPO pin to generate an interruption to notify the MCU when the device is ready to receive the next sample.

- 4. Write the 12-bit waveform data into the REFERENCE register.

- 5. Monitor the GPO pin and wait until the device is ready to receive the next sample.

- 6. Repeat step 4 and 5 until the desired waveform is completed.

### 6.6 FIFO Mode

In FIFO mode (MODE[1:0] bits set to 0x1), the waveform playback is set in a 1024-sample FIFO. The FIFO entries are appended every time waveform data is written in the REFERENCE register. Digital samples are represented as 12-bit unsigned values. The waveform is played when OE bit is set to 0x1 at a rate set by PLAY [2:0] bits. For waveform playback streaming, the user should ensure the FIFO never becomes empty. If the FIFO becomes empty, EMPTY bit is set and the FIFO maintains the last valid data, keeping the waveform in a steady state. FULL bit is set when the FIFO is full and cannot accept more data.

Burst data transfers can be used to minimize the communication interface usage (see section 6.4). In this use case, packets of 16-bit words can sequentially be written in the FIFO at a maximum speed of 35 Mbps. FIFO SPACE [9:0] field can be read prior writing burst data to validate the space available.

Waveforms should begin and end with 0 V amplitude. If <u>OE</u> bit is set to 0x0 during waveform playback, the voltage across the piezo actuator will be ramped down to 0 V and the remaining data in the FIFO will be preserved.

The device uses RAM to implement FIFO. Using FIFO mode overwrites any waveform data previously programmed using RAM Playback mode (section 6.7) or RAM Synthesis mode (section 6.8).

#### Note the following:

- For waveform playback streaming, the FIFO data write rate must match the readout rate of the

waveform playback set by <a href="PLAY[2:0]">PLAY[2:0]</a> bits to always keep valid data inside the FIFO. The <a href="EMPTY">EMPTY</a> bit

is set to 0x1 when the FIFO becomes empty, causing the FIFO to hold the last valid data and keep

the output waveform in a steady state.

- Waveforms should begin and end with 0 V amplitude.

- In case OE bit is set to 0x0 during waveform playback, the output will ramp down automatically to 0 V and the remaining FIFO entries will be kept and played the next time OE bit is set to 0x1 again.

### **6.6.1 Typical Operation Sequence**

The following sequence use FIFO mode to play haptic waveforms:

- 1. Set <a href="RAM.MODE">RAM.MODE</a>[1:0] bits to 0x1 to select FIFO mode.

- 2. In the CONFIG register:

- a. Set CONFIG.OE bit to 0x1 to enable the haptic waveform generation.

- b. Set CONFIG.PLAY[2:0] bits to the desired sampling rate.

- 3. Read <u>FIFO STATUS</u> register to determine how much space is available in the FIFO for new data.

- 4. Write as much 12-bit waveform data as possible according to the available space in the FIFO into the REFERENCE register.

- 5. Read FULL bit to determine if the FIFO can accept more data.

- a. If more data can be accepted, repeat steps 3, 4 and 5 until the desired waveform is completed.

- b. If the FIFO is FULL repeat step 5.

## 6.6.2 FIFO Example

In section 6.6.1, the FIFO is filled after setting  $\underline{OE}$  bit to 0x1. Table 10 is an example where the waveform data is written in the FIFO before setting  $\underline{OE}$  bit to 0x1.

Table 10: FIFO mode example

| Code                 | Description                                                        |

|----------------------|--------------------------------------------------------------------|

| Configure for FIFO m | ode:                                                               |

| 0x8001               | Select FIFO mode to RAM register.                                  |

| Write Data to FIFO:  |                                                                    |

| 0x0000               | Write waveform sample data to REFERENCE register.                  |

| 0x0066               |                                                                    |

| 0x00CC               |                                                                    |

| 0x0132               |                                                                    |

| 0x0198               |                                                                    |

| 0x01FE               |                                                                    |

| 0x0264               |                                                                    |

| 0x02CA               |                                                                    |

| 0x0330               |                                                                    |

| 0x0393               |                                                                    |

| 0x0330               |                                                                    |

| 0x02CA               |                                                                    |

| 0x0264               |                                                                    |

| 0x01FE               |                                                                    |

| 0x0198               |                                                                    |

| 0x0132               |                                                                    |

| 0x00CC               |                                                                    |

| 0x0066               |                                                                    |

| 0x0000               |                                                                    |

| Configure the Wavef  | orm Start:                                                         |

| 0x5017               | Set <u>CONFIG.OE</u> bit to 0x1 to start haptic waveform playback. |

## 6.7 RAM Playback

In RAM Playback mode ( $\underline{\text{MODE}}$  bits set to 0x2), the waveform to be played is defined by storing all the amplitude samples in sequence in RAM. The waveform is played when  $\underline{\text{OE}}$  bit is set to 0x1.

The samples are written to RAM using the <u>BURST RAM WRITE</u> WFS command. More than one waveform can be stored in RAM. The 2 kB memory can store up to 1024 samples. Each sample defines a 16-bit data word containing the 12-bit waveform amplitude in the 12 LSBs of that word and using the same format as the <u>REFERENCE</u> register. The start and end RAM address must be stored in the <u>RAM PLAYBACK</u> command, which indicates the RAM address of the samples to be fetched when the playback is initiated.

When playback starts, the data is read out sequentially at the sample rate set by <u>PLAY [2:0]</u> bits. An interpolation is done between user samples to generate the output waveform when <u>PLAY [2:0]</u> bits are 0x1 to 0x7.

The start and end RAM addresses must be written again using the <u>RAM PLAYBACK</u> command each time a waveform already programmed in RAM needs to be played again (see section 6.7.1).

Note that waveforms should begin and end with 0 V amplitude.

### **6.7.1 Typical Operation Sequence**

The following sequence shows how to use RAM Playback mode to play haptic waveforms:

- 1. In the <u>RAM</u> register:

- a. Set <a href="RAM.MODE[1:0]">RAM.MODE[1:0]</a> to 0x2 to select RAM playback mode.

- b. Set <u>RAM.RAMSEL</u> to 0x1 so that subsequent SPI communication is sent to the WFS command interpreter.

- 2. Program RAM using <u>BURST RAM WRITE</u> command. See section 6.7.2 for an example. To keep access to the WFS command interpreter, make sure the SPI transactions are sent within 4  $\mu$ s of each other to continue writing in RAM.

- 3. Write the start and end RAM address using RAM PLAYBACK WFS command.

- 4. Wait for more than 4 μs to access to the main register map.

- 5. Set BC[4:0] to 0xC to output IC STATUS register content on SDO pin.

- 6. In the CONFIG register:

- a. Set **CONFIG.OE** bit to 0x1 to start haptic waveform playback.

- b. Set CONFIG.PLAY[2:0] bits to the desired sampling rate.

- 7. Poll EMPTY bit on SDO communication port until it is set to 0x1 and waveform is completed.

- 8. Set **CONFIG.OE** bit to 0x0 to deactivate haptic waveform playback.

To start playback with sensing detection, the sensing parameters can be configured between step 4. and 5. See section 6.9 for sensing configuration details.

## 6.7.2 RAM Playback Example

An example of waveform playback is presented in Table 11 where a waveform of 9 samples is played. Table 12 is an example where a waveform already programmed in RAM is played.

Table 11: Example of playing a haptic waveform using RAM Playback mode

| Code           | Description                                                                                                                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configure RAM  | playback:                                                                                                                                                                                     |

| 0x8006         | Select RAM Playback mode and request access to the WFS command interpreter. The following SPI transactions must be sent less than 4 µs from each other to keep using WFS command interpreter. |

| 0x0014         | Use BURST RAM WRITE WFS command.                                                                                                                                                              |

| 0x0000         | Set RAM start RAM address to 0x0000.                                                                                                                                                          |

| 0x000A         | Set Data count (10 samples to be written starting at address 0x0000).                                                                                                                         |

| 0x0000         | Sample Data at RAM address 0x0000.                                                                                                                                                            |

| 0x0066         | Sample Data at RAM address 0x0001.                                                                                                                                                            |

| 0x00CC         | Sample Data at RAM address 0x0002.                                                                                                                                                            |

| 0x0132         | Sample Data at RAM address 0x0003.                                                                                                                                                            |

| 0x0198         | Sample Data at RAM address 0x0004.                                                                                                                                                            |

| 0x0198         | Sample Data at RAM address 0x0005.                                                                                                                                                            |

| 0x0132         | Sample Data at RAM address 0x0006.                                                                                                                                                            |

| 0x00CC         | Sample Data at RAM address 0x0007.                                                                                                                                                            |

| 0x0066         | Sample Data at RAM address 0x0008.                                                                                                                                                            |

| 0x0000         | Sample Data at RAM address 0x0009.                                                                                                                                                            |

| 0x0013         | Use RAM Playback WFS command.                                                                                                                                                                 |

| 0x0000         | Set RAM Playback start address to 0x0000.                                                                                                                                                     |

| 0x0009         | Set RAM Playback end address to 0x0008.                                                                                                                                                       |

| Wait for more  | than 4 μs to access to the main registers.                                                                                                                                                    |

| Start and stop | waveform playback:                                                                                                                                                                            |

| 0x9628         | Set BC[4:0] to 0xC to output IC STATUS register content on SDO pin.                                                                                                                           |

| 0x5017         | Set OE bit to 0x1 to start haptic waveform playback.                                                                                                                                          |

| 0x0000         | Poll EMPTY bit on SDO communication port until it is set to 0x1 and waveform is completed.                                                                                                    |

| 0x5007         | Set OE bit to 0x0 to deactivate haptic waveform playback.                                                                                                                                     |

Table 12: Example of playing a haptic waveform already programmed in RAM using RAM Playback mode

| Code             | Description                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set start and en | d RAM addresses:                                                                                                                                                                                   |

| 0x8006           | Select RAM Playback mode and request access to the WFS command interpreter. The following SPI transactions must be sent less than 4 $\mu$ s from each other to keep using WFS command interpreter. |

| 0x0013           | Use RAM Playback WFS command.                                                                                                                                                                      |

| 0x0000           | Set RAM Playback start address to 0x0000.                                                                                                                                                          |

| 0x0009           | Set RAM Playback end address to 0x0008.                                                                                                                                                            |

| Wait for more th | nan 4 μs to access to the main registers.                                                                                                                                                          |

| Start and stop w | vaveform playback:                                                                                                                                                                                 |

| 0x9628           | Set BC[4:0] to 0xC to output IC STATUS register content on SDO pin.                                                                                                                                |

| 0x5017           | Set OE bit to 0x1 to start haptic waveform playback and PLAY[2:0] to set sample rate to 8 ksps.                                                                                                    |

| 0x0000           | Poll <u>EMPTY</u> bit on SDO communication port until it is set to 0x1 and waveform is completed.                                                                                                  |

| 0x5007           | Set OE bit to 0x0 to deactivate haptic waveform playback.                                                                                                                                          |

## 6.8 RAM Synthesis Mode

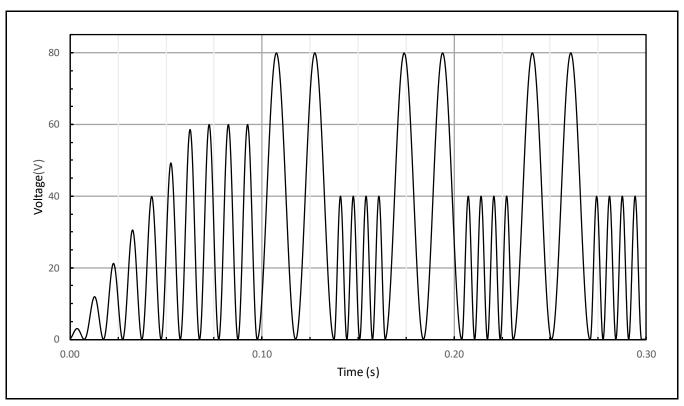

In RAM Synthesis mode ( $\underline{MODE}$  bits set to 0x3), RAM stores sine wave parameters to generate simple and complex waveforms using the following:

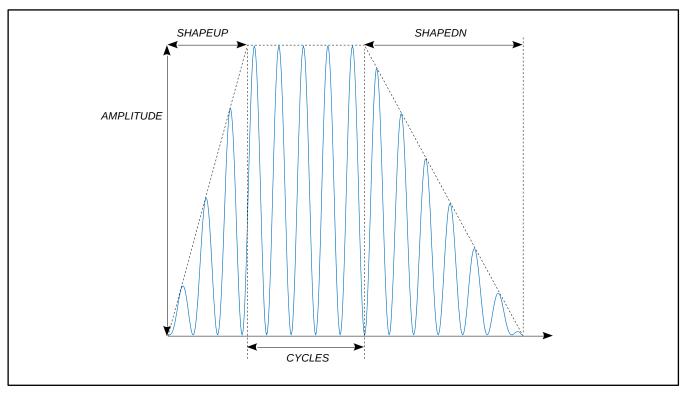

- 1) SLICEs, written in RAM using the <u>RAM SYNTHESIS WRITE</u> command. Each SLICE contains a group of parameters used to produce a sine wave of defined amplitude, frequency, and number of cycles. It may also be ramped up and down (as shown in Figure 17). See section 6.8.1.1 for more details.

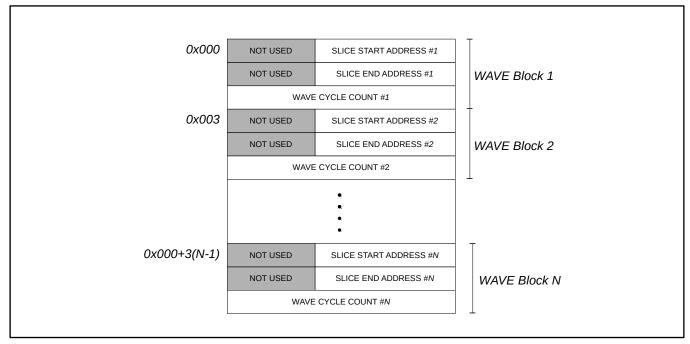

- 2) WAVEs, written in RAM using the <u>RAM SYNTHESIS WRITE</u> WFS command. A WAVE defines a series of SLICEs to be played successively. All SLICEs of a WAVE must be written in order and contiguously in RAM. See section 6.8.1.2. for more details.

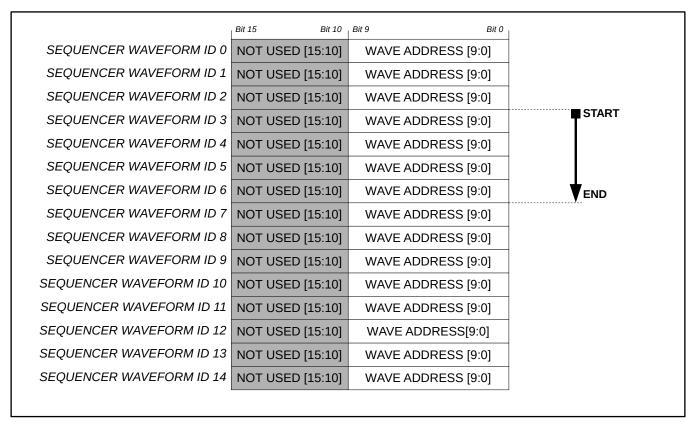

- 3) SEQUENCEs, written using the <u>SEQUENCER</u> WFS command. The <u>SEQUENCER</u> command is used to store up to 15 WAVE addresses in RAM (called WAVEFORM\_IDs). The WAVEs may all be played sequentially, or in any contiguous subsets, down to a single WAVEFORM\_ID. See section 6.8.1.3 for more details.

The <u>SEQUENCE START/STOP</u> WFS command defines the start and end WAVEFORM\_IDs from the WAVEFORM\_IDs list stored using the <u>SEQUENCER</u> command.

The start and end WAVEFORM\_IDs must be written again using the <u>SEQUENCE START/STOP</u> WFS command each time a waveform already programmed in RAM needs to be played again (see section 6.8.3).

#### 6.8.1 RAM Programming

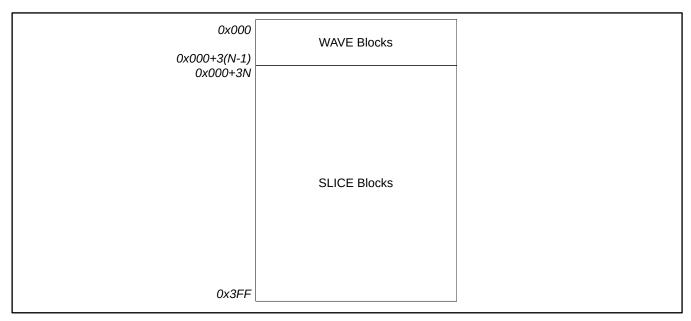

WAVE and SLICE data are stored in RAM. RAM is divided in two sections as shown in Figure 15. The first section stores the WAVE blocks, and the second section stores the SLICEs.

Figure 15: Example of N WAVE blocks followed with SLICEs organized in RAM (1024 × 16-Bit)

## 6.8.1.1 SLICE Blocks

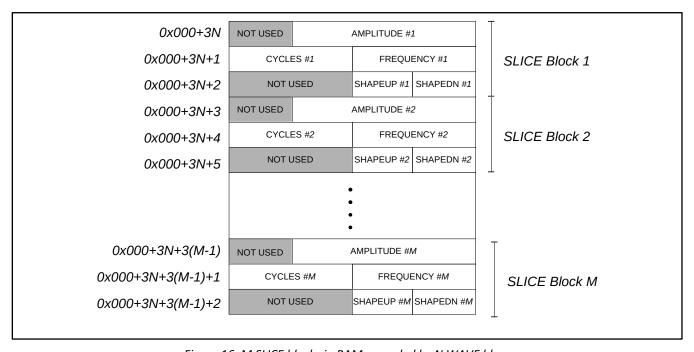

SLICE blocks in RAM contains the parameters used to synthesize sine waveforms. Each SLICE block contains three words grouping five parameters as described in Figure 16 and Table 13. The Figure 17 illustrates how SLICE parameters shape a SLICE waveform. Many SLICEs may be successively played to form complex waveforms.

Figure 16: M SLICE blocks in RAM preceded by N WAVE blocs

## Table 13: Sine wave SLICE parameters

| 15   |         | 13     | 12     | 11     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9        | 8        | 7                                                             | 6     | 5       | 4       | 3      | 2        | 1       | 0  |  |  |  |

|------|---------|--------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|---------------------------------------------------------------|-------|---------|---------|--------|----------|---------|----|--|--|--|

|      | NOT USE | D: 0x0 |        |        | AMPLITUDE[11:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |          |                                                               |       |         |         |        |          |         |    |  |  |  |

|      |         |        |        | S[7:0] |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |          |                                                               |       |         |         | NCY[7: | NCY[7:0] |         |    |  |  |  |

|      |         |        | NOT US |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |          |                                                               | SHAPE | UP[3:0] |         |        | SHAP     | EDN[3:0 | D] |  |  |  |

| WORD | BITS    | NAN    |        |        | CRIPTIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |          |                                                               |       | 11. 1   | <i></i> | \ C II |          |         |    |  |  |  |

| 1    | 11:0    | AMP    | LITUDE | Sets   | s the ou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | tput wav |          |                                                               | _     | -       |         |        | ows:     |         |    |  |  |  |

|      |         |        |        |        | $AMPLITUDE[11:0] = \frac{4095 \times V_{OUT-pk}}{120}$ This AMPLITUDE solves as keelesting in which are part of the PAMS with a six and a MARPLITUDE (1) bits and the six                                                     |          |          |                                                               |       |         |         |        |          |         |    |  |  |  |

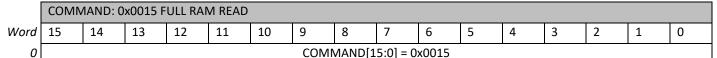

|      |         |        |        |        | AMPLI<br>to 0x3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | lue calc | culation is valid only for RAM Synthesis mode (MODE[1:0] bits |       |         |         |        |          |         |    |  |  |  |