Data sheet

# **BMA222E**Digital, triaxial acceleration sensor

**Bosch Sensortec**

#### BMA222E: Data sheet

Document revision 1.3

Document release date 28 April 2015

Document number BST-BMA222E-DS004-06

Technical reference code(s) 0 273 141 168 0 273 141 218

Notes Data in this document are subject to change without notice.

Product photos and pictures are for illustration purposes only and

may differ from the real product's appearance.

Not intended for publishing

#### **BMA222E**

# 8 BIT, DIGITAL, TRIAXIAL ACCELERATION SENSOR WITH INTELLIGENT ON-CHIP MOTION-TRIGGERED INTERRUPT CONTROLLER

#### **Key features**

Ultra-Small package

• Digital interface

Programmable functionality

On-chip FIFO

On-chip interrupt controller

LGA package (12 pins), footprint 2mm x 2mm, height 0.95mm

SPI (4-wire, 3-wire), I2C, 2 interrupt pins

V<sub>DDIO</sub> voltage range: 1.2V to 3.6V

Acceleration ranges ±2g/±4g/±8g/±16g

Low-pass filter bandwidths 1kHz - <8Hz Integrated FIFO with a depth of 32 frames Motion-triggered interrupt-signal generation for

- new data

- any-motion (slope) detection

- tap sensing (single tap / double tap)

- orientation recognition

- flat detection

- low-g/high-g detection

- no-motion / inactivity detection

Low current consumption, short wake-up time, advanced features for system power management

- Ultra-low power

- Temperature sensor

- RoHS compliant, halogen-free

#### **Typical applications**

- Display profile switching

- Menu scrolling, tap / double tap sensing

- Gaming

- Pedometer / step counting

- Free-fall detection

- E-compass tilt compensation

- Drop detection for warranty logging

- Advanced system power management for mobile applications

#### **General description**

The BMA222E is a triaxial, low-g acceleration sensor with digital output for consumer applications. It allows measurements of acceleration in three perpendicular axes. An evaluation circuitry (ASIC) converts the output of a micromechanical acceleration-sensing structure (MEMS) that works according to the differential capacitance principle.

Package and interfaces of the BMA222E have been defined to match a multitude of hardware requirements. Since the sensor features an ultra-small footprint and a flat package it is ingeniously suited for mobile applications.

The BMA222E offers a variable  $V_{DDIO}$  voltage range from 1.2V to 3.6V and can be programmed to optimize functionality, performance and power consumption in customer specific applications.

Page 3

In addition it features an on-chip interrupt controller enabling motion-based applications without use of a microcontroller.

The BMA222E senses tilt, motion, inactivity and shock vibration in cell phones, handhelds, computer peripherals, man-machine interfaces, virtual reality features and game controllers.

#### **Index of Contents**

| 1. SPECIFICATION                                                                      | 8        |

|---------------------------------------------------------------------------------------|----------|

| 2. ABSOLUTE MAXIMUM RATINGS                                                           | 11       |

| 3. BLOCK DIAGRAM                                                                      | 12       |

| 4. FUNCTIONAL DESCRIPTION                                                             | 13       |

| 4.1 SUPPLY VOLTAGE AND POWER MANAGEMENT                                               | 13       |

| 4.2 Power modes                                                                       | 14       |

| 4.3 SENSOR DATA                                                                       | 18       |

| 4.3.1 Acceleration data4.3.2 Temperature sensor                                       |          |

| 4.4 SELF-TEST                                                                         | 20       |

| 4.5 Offset compensation                                                               | 21       |

| 4.5.1 SLOW COMPENSATION                                                               | 23<br>24 |

| 4.6 Non-volatile memory                                                               | 25       |

| 4.7 Interrupt controller                                                              | 26       |

| 4.7.1 GENERAL FEATURES 4.7.2 MAPPING TO PHYSICAL INTERRUPT PINS (INTTYPE TO INT PIN#) |          |

| 4.8 SOFTRESET                                                                         | 44       |

| 5. FIFO OPERATION                                                                     | 45       |

| 5.1 FIFO OPERATING MODES                                                              | 45       |

| 5.2 FIFO DATA READOUT                                                                 | 46       |

| 5.3 FIFO FRAME COUNTER AND OVERRUN FLAG                                               | 46       |

| 5.4 FIFO INTERRUPTS                                                                   |          |

|                                                                                       |          |

| 6. | REGISTER DESCRIPTION          | .48  |

|----|-------------------------------|------|

|    | 6.1 GENERAL REMARKS           | .48  |

|    | 6.2 REGISTER MAP              | 49   |

|    | REGISTER 0x00 (BGW_CHIPID)    | .50  |

|    | REGISTER 0x02 (ACCD_X_LSB)    | .50  |

|    | REGISTER 0x03 (ACCD_X_MSB)    | .51  |

|    | REGISTER 0x04 (ACCD_Y_LSB)    | .52  |

|    | REGISTER 0x05 (ACCD_Y_MSB)    | . 53 |

|    | REGISTER 0x06 (ACCD_Z_LSB)    | . 54 |

|    | REGISTER 0x07 (ACCD_Z_MSB)    | . 55 |

|    | REGISTER 0x08 (ACCD_TEMP)     | .56  |

|    | REGISTER 0x09 (INT_STATUS_0)  | . 57 |

|    | REGISTER 0x0A (INT_STATUS_1)  | .58  |

|    | REGISTER 0x0B (INT_STATUS_2)  | . 59 |

|    | REGISTER 0x0C (INT_STATUS_3)  | 60   |

|    | REGISTER 0x0E (FIFO_STATUS)   | 61   |

|    | REGISTER 0x0F (PMU_RANGE)     | 62   |

|    | REGISTER 0x10 (PMU_BW)        | 62   |

|    | REGISTER 0x11 (PMU_LPW)       | 63   |

|    | REGISTER 0x12 (PMU_LOW_NOISE) | 64   |

|    | REGISTER 0x13 (ACCD_HBW)      | 65   |

|    | REGISTER 0x14 (BGW_SOFTRESET) | 66   |

|    | REGISTER 0x16 (INT_EN_0)      | 66   |

|    | REGISTER 0x17 (INT_EN_1)      | 67   |

|    | REGISTER 0x18 (INT_EN_2)      | 68   |

|    | REGISTER 0x19 (INT_MAP_0)     | 69   |

|    | REGISTER 0x1A (INT_MAP_1)     | . 70 |

|    | REGISTER 0x1B (INT_MAP_2)     | . 71 |

|    | REGISTER 0x1E (INT_SRC)       | . 72 |

|    | REGISTER 0x20 (INT_OUT_CTRL)  | . 73 |

|    | REGISTER 0x21 (INT_RST_LATCH) | . 74 |

|    | REGISTER 0x22 (INT_0)         | . 74 |

|    | REGISTER 0x23 (INT_1)         | . 75 |

|    | REGISTER 0x24 (INT_2)         | . 75 |

Page 6

|    | REGISTER 0x25 (INT_3)                              | 76  |

|----|----------------------------------------------------|-----|

|    | REGISTER 0x26 (INT_4)                              | 76  |

|    | REGISTER 0x27 (INT_5)                              | 77  |

|    | REGISTER 0x28 (INT_6)                              | 78  |

|    | REGISTER 0x29 (INT_7)                              | 78  |

|    | REGISTER 0x2A (INT_8)                              | 79  |

|    | REGISTER 0x2B (INT_9)                              | 80  |

|    | REGISTER 0x2C (INT_A)                              | 81  |

|    | REGISTER 0x2D (INT_B)                              | 82  |

|    | REGISTER 0x2E (INT_C)                              | 82  |

|    | REGISTER 0x2F (INT_D)                              | 83  |

|    | REGISTER 0x30 (FIFO_CONFIG_0)                      | 84  |

|    | REGISTER 0x32 (PMU_SELF_TEST)                      | 85  |

|    | REGISTER 0x33 (TRIM_NVM_CTRL)                      | 86  |

|    | REGISTER 0x34 (BGW_SPI3_WDT)                       | 87  |

|    | REGISTER 0x36 (OFC_CTRL)                           | 88  |

|    | REGISTER 0x37 (OFC_SETTING)                        | 89  |

|    | REGISTER 0x38 (OFC_OFFSET_X)                       | 90  |

|    | REGISTER 0x39 (OFC_OFFSET_Y)                       |     |

|    | REGISTER 0x3A (OFC_OFFSET_Z)                       |     |

|    | REGISTER 0x3B (TRIM_GP0)                           |     |

|    | REGISTER 0x3C (TRIM_GP1)                           | 93  |

|    | REGISTER 0x3E (FIFO_CONFIG_1)                      | 94  |

|    | REGISTER 0x3F (FIFO_DATA)                          | 95  |

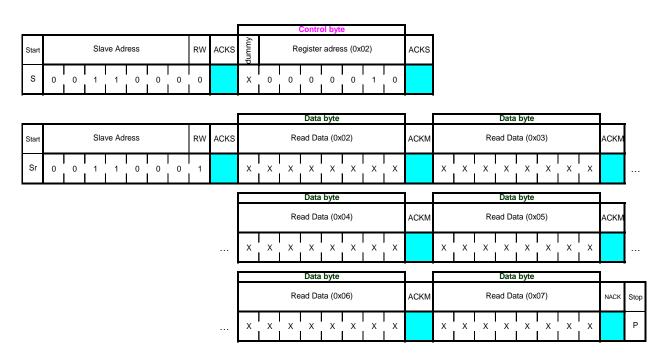

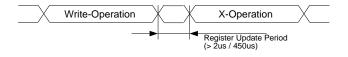

| 7  | . DIGITAL INTERFACES                               | 96  |

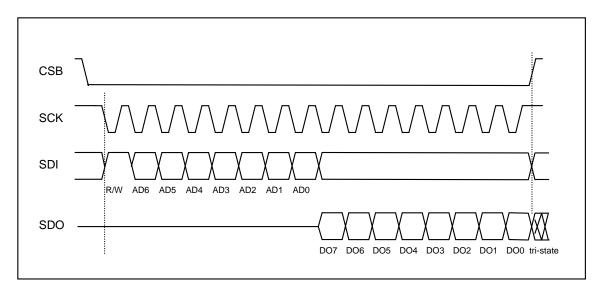

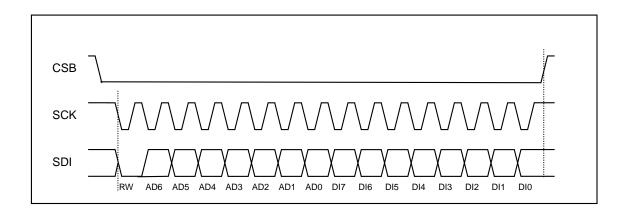

| •  | 7.1 SERIAL PERIPHERAL INTERFACE (SPI)              |     |

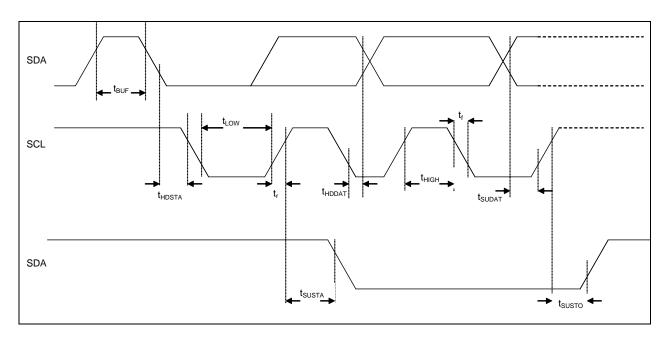

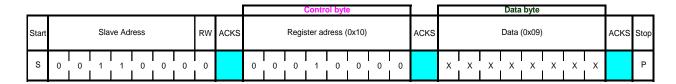

|    | 7.2 INTER-INTEGRATED CIRCUIT (I <sup>2</sup> C)    |     |

|    | 7.2.1 SPI and I <sup>2</sup> C Access Restrictions |     |

|    | 71 <u>212</u>                                      |     |

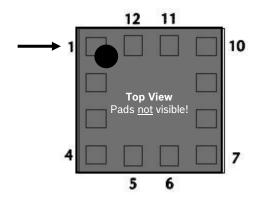

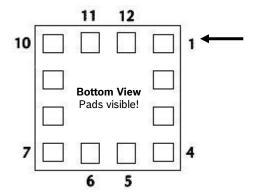

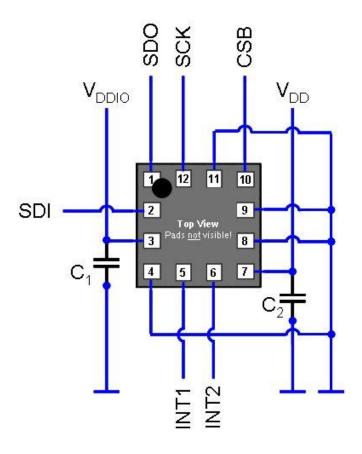

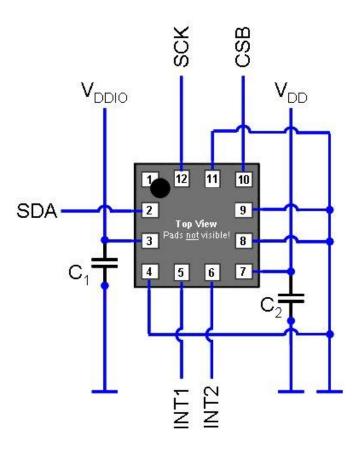

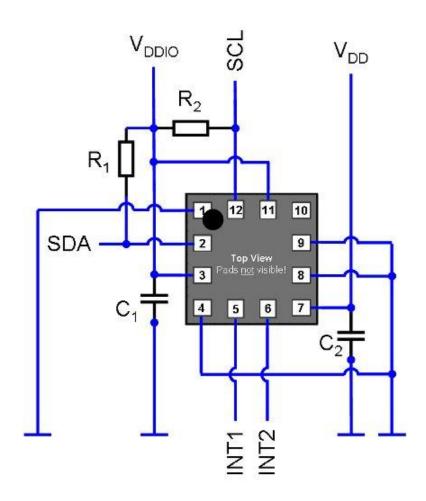

| 8. | . PIN-OUT AND CONNECTION DIAGRAM                   | 105 |

|    | 8.1 PIN-OUT                                        |     |

|    | 8.2 CONNECTION DIAGRAM 4-WIRE SPI                  | 106 |

|    | 8.3 CONNECTION DIAGRAM 3-WIRE SPI                  | 107 |

|    | 8.4 CONNECTION DIAGRAM I <sup>2</sup> C            | 108 |

Page 7

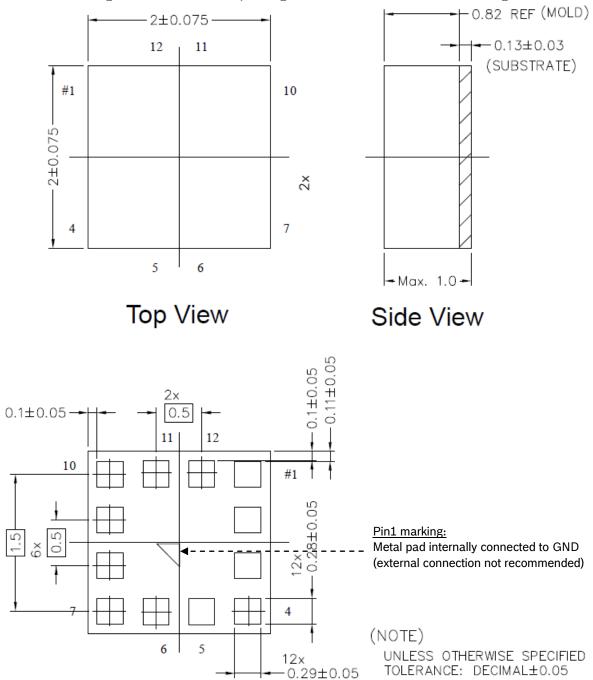

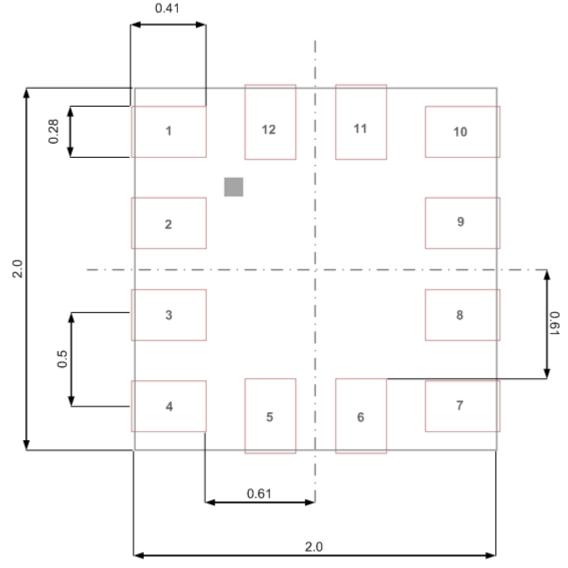

| 9. PACKAGE                                            | 109 |

|-------------------------------------------------------|-----|

| 9.1 OUTLINE DIMENSIONS                                | 109 |

| 9.2 SENSING AXES ORIENTATION                          |     |

| 9.3 LANDING PATTERN RECOMMENDATION                    |     |

| 9.4 Marking                                           |     |

| 9.4.1 Mass production devices                         |     |

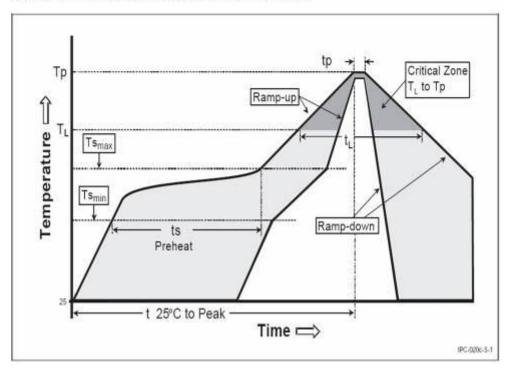

| 9.5 SOLDERING GUIDELINES                              |     |

| 9.6 HANDLING INSTRUCTIONS                             |     |

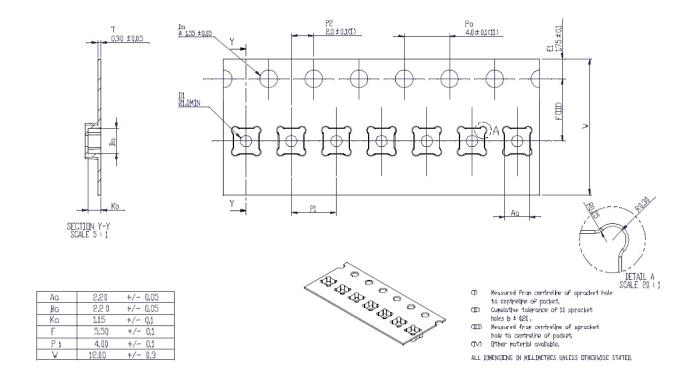

| 9.7 TAPE AND REEL SPECIFICATION                       |     |

| 9.7.1 ORIENTATION WITHIN THE REEL                     |     |

| 9.8 ENVIRONMENTAL SAFETY                              | 117 |

| 9.8.1 HALOGEN CONTENT9.8.2 INTERNAL PACKAGE STRUCTURE |     |

| 10. LEGAL DISCLAIMER                                  | 118 |

| 10.1 ENGINEERING SAMPLES                              | 118 |

| 10.2 PRODUCT USE                                      | 118 |

| 10.3 APPLICATION EXAMPLES AND HINTS                   | 118 |

| 11 DOCUMENT HISTORY AND MODIFICATION                  | 119 |

## 1. Specification

Unless stated otherwise, the given values are over lifetime, operating temperature and voltage ranges. Minimum/maximum values are  $\pm 3\sigma$ .

Table 1: Parameter specification

| OPERATING CONDITIONS                               |                                   |                                                                                 |                      |                       |                      |             |

|----------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------|----------------------|-----------------------|----------------------|-------------|

| Parameter                                          | Symbol                            | Condition                                                                       | Min                  | Тур                   | Max                  | Units       |

| Acceleration<br>Range                              | gFS2g<br>gFS4g<br>gFS8g<br>gFS16g | Selectable<br>via serial digital<br>interface                                   |                      | ±2<br>±4<br>±8<br>±16 |                      | g<br>g<br>g |

| Supply Voltage<br>Internal Domains                 | $V_{DD}$                          |                                                                                 | 1.62                 | 2.4                   | 3.6                  | V           |

| Supply Voltage<br>I/O Domain                       | $V_{\text{DDIO}}$                 |                                                                                 | 1.2                  | 2.4                   | 3.6                  | V           |

| Voltage Input<br>Low Level                         | V <sub>IL</sub>                   | SPI & I <sup>2</sup> C                                                          |                      |                       | 0.3V <sub>DDIO</sub> | -           |

| Voltage Input<br>High Level                        | $V_{IH}$                          | SPI & I <sup>2</sup> C                                                          | $0.7V_{DDIO}$        |                       |                      | -           |

| Voltage Output<br>Low Level                        | $V_{OL}$                          | I <sub>OL</sub> = 3mA, SPI & I <sup>2</sup> C                                   |                      |                       | 0.2V <sub>DDIO</sub> | -           |

| Voltage Output<br>High Level                       | $V_{OH}$                          | I <sub>OH</sub> = 3mA, SPI                                                      | 0.8V <sub>DDIO</sub> |                       |                      | -           |

| Total Supply<br>Current in<br>Normal Mode          | I <sub>DD</sub>                   | $T_A=25$ °C, bw = 1kHz<br>$V_{DD}=V_{DDIO}=2.4V$                                |                      | 130                   |                      | μΑ          |

| Total Supply<br>Current in<br>Suspend Mode         | I <sub>DDsum</sub>                | $T_A=25^{\circ}C$ $V_{DD}=V_{DDIO}=2.4V$                                        |                      | 2.1                   |                      | μΑ          |

| Total Supply<br>Current in<br>Deep Suspend<br>Mode | I <sub>DDdsum</sub>               | $T_A=25^{\circ}C$ $V_{DD}=V_{DDIO}=2.4V$                                        |                      | 1                     |                      | μΑ          |

| Total Supply<br>Current in<br>Low-power Mode<br>1  | I <sub>DDlp1</sub>                | $T_A$ =25°C, bw = 1kHz<br>$V_{DD}$ = $V_{DDIO}$ = 2.4V<br>sleep duration = 25ms |                      | 6.5                   |                      | μΑ          |

| Total Supply<br>Current in<br>Low-power Mode<br>2  | I <sub>DDlp2</sub>                | $T_A$ =25°C, bw = 1kHz<br>$V_{DD}$ = $V_{DDIO}$ = 2.4V<br>sleep duration = 25ms |                      | 66                    |                      | μΑ          |

Page 9

| Total Supply<br>Current in<br>Standby Mode   | I <sub>DDsbm</sub> | $T_A=25^{\circ}C$ $V_{DD}=V_{DDIO}=2.4V$                                      |     | 62  |     | μΑ     |

|----------------------------------------------|--------------------|-------------------------------------------------------------------------------|-----|-----|-----|--------|

| Wake-Up Time 1                               | $t_{w,up1}$        | from Low-power Mode<br>1 or Suspend Mode or<br>Deep Suspend Mode<br>bw = 1kHz |     | 1.3 | 1.8 | ms     |

| Wake-Up Time 2                               | $t_{w,up2}$        | from Low-power Mode<br>2 or Stand-by Mode<br>bw = 1kHz                        |     | 1   | 1.2 | ms     |

| Start-Up Time                                | $t_{s,up}$         | POR, bw = 1kHz                                                                |     |     | 3   | ms     |

| Non-volatile<br>memory (NVM)<br>write-cycles | n <sub>NVM</sub>   |                                                                               |     |     | 15  | cycles |

| Operating<br>Temperature                     | T <sub>A</sub>     |                                                                               | -40 |     | +85 | °C     |

#### **OUTPUT SIGNAL**

| Parameter                          | Symbol             | Condition                                                                                   | Min | Тур   | Max | Units  |

|------------------------------------|--------------------|---------------------------------------------------------------------------------------------|-----|-------|-----|--------|

|                                    | S <sub>2g</sub>    | $g_{FS2g}$ , $T_A=25$ °C                                                                    |     | 64    |     | LSB/g  |

| Sensitivity                        | $S_{4g}$           | $g_{FS4g}$ , $T_A = 25$ °C                                                                  |     | 32    |     | LSB/g  |

| Sensitivity                        | S <sub>8g</sub>    | $g_{FS8g}$ , $T_A=25$ °C                                                                    |     | 16    |     | LSB/g  |

|                                    | S <sub>16g</sub>   | $g_{FS16g}$ , $T_A=25$ °C                                                                   |     | 8     |     | LSB/g  |

| Sensitivity<br>Temperature Drift   | TCS                | $g_{FS2g}$ , Nominal $V_{DD}$ supplies                                                      |     | ±0.02 |     | %/K    |

| Zero-g Offset                      | Off                | $g_{FS2g}$ , $T_A$ =25°C,<br>nominal $V_{DD}$ supplies,<br>over life-time                   |     | ±100  |     | mg     |

| Zero-g Offset<br>Temperature Drift | TCO                | $g_{FS2g}$ , Nominal $V_{DD}$ supplies                                                      |     | ±1    |     | mg/K   |

|                                    | bw <sub>8</sub>    | 2 <sup>nd</sup> order filter,<br>bandwidth                                                  |     | 8     |     | Hz     |

|                                    | bw <sub>16</sub>   |                                                                                             |     | 16    |     | Hz     |

|                                    | bw <sub>31</sub>   |                                                                                             |     | 31    |     | Hz     |

| Bandwidth                          | bw <sub>63</sub>   |                                                                                             |     | 63    |     | Hz     |

| Danawiatii                         | bw <sub>125</sub>  | programmable                                                                                |     | 125   |     | Hz     |

|                                    | bw <sub>250</sub>  | , ,                                                                                         |     | 250   |     | Hz     |

|                                    | bw <sub>500</sub>  |                                                                                             |     | 500   |     | Hz     |

|                                    | bw <sub>1000</sub> |                                                                                             |     | 1,000 |     | Hz     |

| Nonlinearity                       | NL                 | best fit straight line,<br>g <sub>FS2g</sub>                                                |     | ±0.5  |     | %FS    |

| Output Noise<br>Density            | n <sub>rms</sub>   | g <sub>FS2g</sub> , T <sub>A</sub> =25°C<br>Nominal V <sub>DD</sub> supplies<br>Normal mode |     | 600   |     | µg/√Hz |

BST-BMA222E-DS004-06 | Revision 1.3 | April 2015

Bosch Sensortec

| Temperature<br>Sensor<br>Measurement<br>Range | Ts     |                                                               | -40      |      | 85  | °C    |

|-----------------------------------------------|--------|---------------------------------------------------------------|----------|------|-----|-------|

| Temperature<br>Sensor Slope                   | dTs    |                                                               |          | 0.5  |     | K/LSB |

| Temperature<br>Sensor Offset                  | OTs    |                                                               |          | ±2   |     | K     |

|                                               |        |                                                               |          |      |     |       |

|                                               |        | MECHANICAL CHARACT                                            | ERISTICS |      |     |       |

| Parameter                                     | Symbol | Condition                                                     | Min      | Тур  | Max | Units |

| Cross Axis<br>Sensitivity                     | S      | relative contribution<br>between any two of<br>the three axes |          | 1    |     | %     |

| Alignment Error                               | $E_A$  | relative to package<br>outline                                |          | ±0.5 |     | o     |

# 2. Absolute maximum ratings

Table 2: Absolute maximum ratings

| Parameter                                  | Condition                    | Min  | Max             | Units |

|--------------------------------------------|------------------------------|------|-----------------|-------|

| Voltago at Supply Din                      | $V_{DD}$ Pin                 | -0.3 | 4.25            | V     |

| Voltage at Supply Pin                      | $V_{DDIO}$ Pin               | -0.3 | 4.25            | V     |

| Voltage at any Logic Pin                   | Non-Supply Pin               | -0.3 | $V_{DDIO}$ +0.3 | V     |

| Passive Storage Temp. Range                | ≤ 65% rel. H.                | -50  | +150            | °C    |

| None-volatile memory (NVM)  Data Retention | T = 85°C,<br>after 15 cycles | 10   |                 | у     |

|                                            | Duration ≤ 200µs             |      | 10,000          | g     |

| Mechanical Shock                           | Duration ≤ 1.0ms             |      | 2,000           | g     |

|                                            | Free fall onto hard surfaces |      | 1.8             | m     |

|                                            | HBM, at any Pin              |      | 2               | kV    |

| ESD                                        | CDM                          |      | 500             | V     |

|                                            | MM                           |      | 200             | V     |

#### Note:

Stress above these limits may cause damage to the device. Exceeding the specified electrical limits may affect the device reliability or cause malfunction.

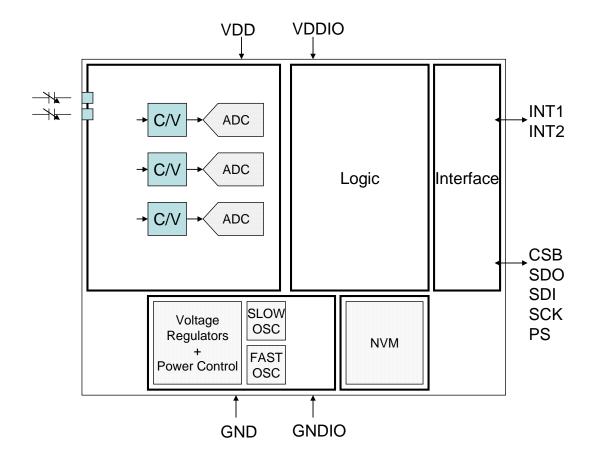

## 3. Block diagram

Figure 1 shows the basic building blocks of the BMA222E:

Figure 1: Block diagram of BMA222E

Page 13

#### 4. Functional description

Note: Default values for registers can be found in chapter 6.

#### 4.1 Supply voltage and power management

The BMA222E has two distinct power supply pins:

- $\bullet$   $V_{DD}$  is the main power supply for the internal blocks

- V<sub>DDIO</sub> is a separate power supply pin used for supplying power for the interface

There are no limitations on the voltage levels of both pins relative to each other, as long as each of them lies within its operating range. Furthermore, the device can be completely switched off ( $V_{DD} = 0V$ ) while keeping the  $V_{DDIO}$  supply on ( $V_{DDIO} > 0V$ ) or vice versa.

When the  $V_{DDIO}$  supply is switched off, all interface pins (CSB, SDI, SCK, PS) must be kept close to  $GND_{IO}$  potential.

The device contains a power-on reset (POR) generator. It resets the logic part and the register values after powering-on  $V_{DD}$  and  $V_{DDIO}$ . Please note, that all application specific settings which are not equal to the default settings (refer to 6.2 register map), must be re-set to its designated values after POR.

There are no constraints on the switching sequence of both supply voltages. In case the  $I^2C$  interface shall be used, a direct electrical connection between  $V_{DDIO}$  supply and the PS pin is needed in order to ensure reliable protocol selection. For SPI interface mode the PS pin must be directly connected to  $GND_{IO}$ .

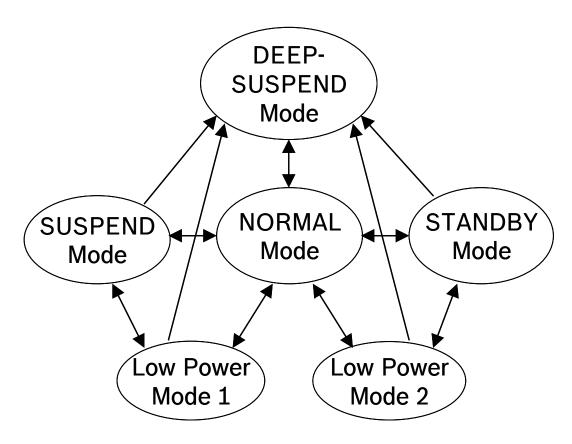

#### 4.2 Power modes

The BMA222E has six different power modes. Besides normal mode, which represents the fully operational state of the device, there are five energy saving modes: deep-suspend mode, suspend mode, standby mode, low-power mode 1 and low-power mode 2.

The possible transitions between the power modes are illustrated in figure 2:

Figure 2: Power mode transition diagram

After power-up BMA222E is in normal mode so that all parts of the device are held powered-up and data acquisition is performed continuously.

In **deep-suspend** mode the device reaches the lowest possible power consumption. Only the interface section is kept alive. No data acquisition is performed and the content of the configuration registers is lost. Deep suspend mode is entered (left) by writing '1' ('0') to the (0x11) deep\_suspend bit while (0x11) suspend bit is set to '0'. The I<sup>2</sup>C watchdog timer remains functional. The (0x11) deep\_ suspend bit, the (0x34) spi3 bit, (0x34) i2c\_wdt\_en bit and the (0x34) i2c\_wdt\_sel bit are functional in deep-suspend mode. Equally the interrupt level and driver configuration registers (0x20) int1\_lvl, (0x20) int1\_od, (0x20) int2\_lvl, and (0x20) int2\_od are accessible. Still it is possible to enter normal mode by performing a softreset as described in chapter 4.8. Please note, that all application specific settings which are not equal to the default settings (refer to 6.2 register map), must be re-set to its designated values after leaving deep-suspend mode.

Page 15

In **suspend mode** the whole analog part is powered down. No data acquisition is performed. While in suspend mode the latest acceleration data and the content of all configuration registers are kept. Writing to and reading from registers is supported except from the (0x3E) fifo\_config\_1, (0x30) fifo\_config\_0 and (0x3F) fifo\_data register. It is possible to enter normal mode by performing a softreset as described in chapter 4.8.

Suspend mode is entered (left) by writing '1' ('0') to the (0x11) suspend bit after bit (0x12) lowpower\_mode has been set to '0'. Although write access to registers is supported at the full interface clock speed (SCL or SCK), a waiting period must be inserted between two consecutive write cycles (please refer also to section 7.2.1).

In **standby mode** the analog part is powered down, while the digital part remains largely operational. No data acquisition is performed. Reading and writing registers is supported without any restrictions. The latest acceleration data and the content of all configuration registers are kept. Standby mode is entered (left) by writing '1' ('0') to the (0x11) suspend bit after bit (0x12) lowpower\_mode has been set to '1'. It is also possible to enter normal mode by performing a softreset as described in chapter 4.8.

In **low-power mode 1**, the device is periodically switching between a sleep phase and a wake-up phase. The wake-up phase essentially corresponds to operation in normal mode with complete power-up of the circuitry. The sleep phase essentially corresponds to operation in suspend mode. Low-power mode is entered (left) by writing '1' ('0') to the (0x11) lowpower\_en bit with bit (0x12) lowpower\_mode set to '0'. Read access to registers is possible except from the (0x3F) fifo\_data register. However, unless the register access is synchronised with the wake-up phase, the restrictions of the suspend mode apply.

**Low-power mode 2** is very similar to low-power mode 1, but register access is possible at any time without restrictions. It consumes more power than low-power mode 1. In low-power mode 2 the device is periodically switching between a sleep phase and a wake-up phase. The wake-up phase essentially corresponds to operation in normal mode with complete power-up of the circuitry. The sleep phase essentially corresponds to operation in standby mode. Low-power mode is entered (left) by writing '1' ('0') to the (0x11) lowpower\_en bit with bit (0x12) lowpower\_mode set to '1'.

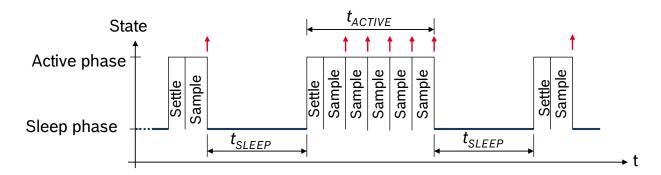

The timing behaviour of the low-power modes 1 and 2 depends on the setting of the (0x12) sleeptimer\_mode bit. When (0x12) sleeptimer\_mode is set to '0', the event-driven time-base mode (EDT) is selected. In EDT the duration of the wake-up phase depends on the number of samples required by the enabled interrupt engines. If an interrupt is detected, the device stays in the wake-up phase as long as the interrupt condition endures (non-latched interrupt), or until the latch time expires (temporary interrupt), or until the interrupt is reset (latched interrupt). If no interrupt is detected, the device enters the sleep phase immediately after the required number of acceleration samples have been taken and an active interface access cycle has ended. The EDT mode is recommended for power-critical applications which do not use the FIFO. Also, EDT mode is compatible with legacy BST sensors. Figure 3 shows the timing diagram for low-power modes 1 and 2 when EDT is selected.

Figure 3: Timing Diagram for low-power mode 1/2, EDT

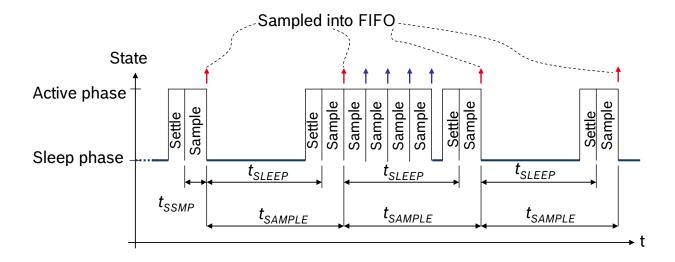

When (0x12) sleeptimer\_mode is set to '1', the equidistant-sampling mode (EST) is selected. The use of the EST mode is recommended when the FIFO is used since it ensures that equidistant samples are sampled into the FIFO regardless of whether the active phase is extended by active interrupt engines or interface activity. In EST mode the sleep time  $t_{SLEEP}$  is defined as shown in Figure 4. The FIFO sampling time  $t_{SAMPLE}$  is the sum of the sleep time  $t_{SLEEP}$  and the sensor data sampling time  $t_{SSMP}$ . Since interrupt engines can extend the active phase to exceed the sleep time  $t_{SLEEP}$ , equidistant sampling is only guaranteed if the bandwidth has been chosen such that  $1/(2 * bw) = n * t_{SLEEP}$  where n is an integer. If this condition is infringed, equidistant sampling is not possible. Once the sleep time has elapsed the device will store the next available sample in the FIFO. This set-up condition is not recommended as it may result in timing jitter.

Figure 4: Timing Diagram for low-power mode 1/2, EST

The sleep time for lower-power mode 1 and 2 is set by the (0x11) sleep\_dur bits as shown in the following table:

Table 3: Sleep phase duration settings

| (0x11)<br>sleep_dur | Sleep Phase<br>Duration<br>t <sub>sleep</sub> |

|---------------------|-----------------------------------------------|

| 0000b               | 0.5ms                                         |

| 0001b               | 0.5ms                                         |

| 0010b               | 0.5ms                                         |

| 0011b               | 0.5ms                                         |

| 0100b               | 0.5ms                                         |

| 0101b               | 0.5ms                                         |

| 0110b               | 1ms                                           |

| 0111b               | 2ms                                           |

| 1000b               | 4ms                                           |

| 1001b               | 6ms                                           |

| 1010b               | 10ms                                          |

| 1011b               | 25ms                                          |

| 1100b               | 50ms                                          |

| 1101b               | 100ms                                         |

| 1110b               | 500ms                                         |

| 1111b               | 1s                                            |

The current consumption of the BMA222E in low-power mode 1 ( $I_{DDlp2}$ ) and low-power mode 2 ( $I_{DDlp2}$ ) can be estimated with the following formulae:

$$I_{DDlp1} \approx \frac{t_{sleep} \cdot I_{DDsum} + t_{active} \cdot I_{DD}}{t_{sleep} + t_{active}} \,.$$

$$I_{DDlp2} \approx \frac{t_{sleep} \cdot I_{DDsbm} + t_{active} \cdot I_{DD}}{t_{sleep} + t_{active}}$$

When estimating the length of the wake-up phase  $t_{active}$ , the corresponding typical wake-up time,  $t_{w,up1}$  or  $t_{w,up2}$  and  $t_{ut}$  (given in Table 4) have to be considered:

If bandwidth is >=31.25 Hz:

$$t_{active} = t_{ut} + t_{w,up1} - 0.9 \text{ ms}$$

(or  $t_{active} = t_{ut} + t_{w,up2} - 0.9 \text{ ms}$ ) else:  $t_{active} = 4 t_{ut} + t_{w,up1} - 0.9 \text{ ms}$  (or  $t_{active} = 4 t_{ut} + t_{w,up2} - 0.9 \text{ ms}$ )

During the wake-up phase all analog modules are held powered-up, while during the sleep phase most analog modules are powered down. Consequently, a wake-up time of at least  $t_{w,up1}$  ( $t_{w,up2}$ ) is needed to settle the analog modules so that reliable acceleration data are generated.

#### 4.3 Sensor data

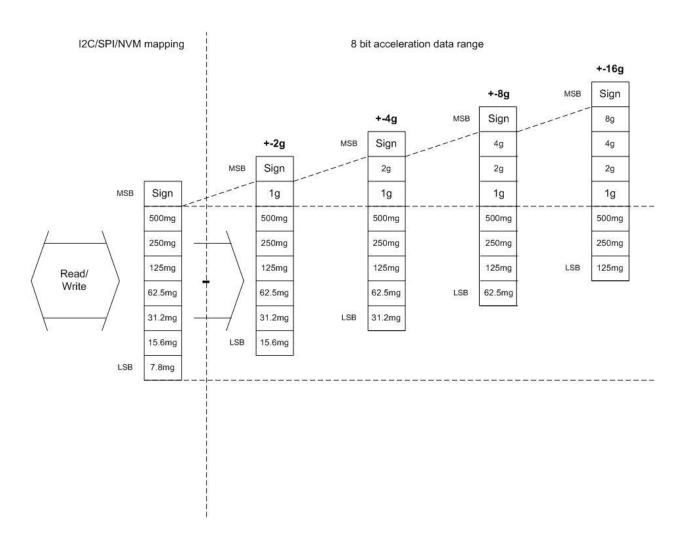

#### 4.3.1 Acceleration data

The width of acceleration data is 8 bits given in two's complement representation. The 8 bit data word for each axis is contained the MSB of the acceleration data output registers 0x03, 0x05, 0x07. The LSB of the acceleration data output registers contain a (0x02, 0x04, 0x06) new\_data flag. Reading the acceleration data registers shall always start with the LSB part. In order to ensure the integrity of the acceleration data, the content of an MSB register is locked by reading the corresponding LSB register (shadowing procedure). When shadowing is enabled, the MSB must always be read in order to remove the data lock. The shadowing procedure can be disabled (enabled) by writing '1' ('0') to the bit shadow\_dis. With shadowing disabled, the content of both MSB and LSB registers is updated by a new value immediately. Unused bits of the LSB registers may have any value and should be ignored. The (0x02, 0x04, 0x06) new\_data flag of each LSB register is set if the data registers have been updated. The flag is reset if either the corresponding MSB or LSB part is read.

Two different streams of acceleration data are available, unfiltered and filtered. The unfiltered data is sampled with 2kHz. The sampling rate of the filtered data depends on the selected filter bandwidth and is always twice the selected bandwidth (BW = ODR/2). Which kind of data is stored in the acceleration data registers depends on bit (0x13)  $data_high_bw$  is '0' ('1'), then filtered (unfiltered) data is stored in the registers. Both data streams are offset-compensated.

The bandwidth of filtered acceleration data is determined by setting the (0x10) bw bit as followed:

| bw    | Bandwidth | Update Time t <sub>ut</sub> |

|-------|-----------|-----------------------------|

| 00xxx | *)        | -                           |

| 01000 | 7.81Hz    | 64ms                        |

| 01001 | 15.63Hz   | 32ms                        |

| 01010 | 31.25Hz   | 16ms                        |

| 01011 | 62.5Hz    | 8ms                         |

| 01100 | 125Hz     | 4ms                         |

| 01101 | 250Hz     | 2ms                         |

| 01110 | 500Hz     | 1ms                         |

| 01111 | 1000Hz    | 0.5ms                       |

| 1xxxx | *)        | -                           |

Table 4: Bandwidth configuration

<sup>\*)</sup> Note: Settings 00xxx result in a bandwidth of 7.81 Hz; settings 1xxxx result in a bandwidth of 1000 Hz. It is recommended to actively set an application specific and an appropriate bandwidth and to use the range from '01000b' to '01111b' only in order to be compatible with future products.

Page 19

The BMA222E supports four different acceleration measurement ranges. A measurement range is selected by setting the (0x0F) range bits as follows:

Table 5: Range selection

| Range  | Acceleration<br>measurement<br>range | Resolution   |

|--------|--------------------------------------|--------------|

| 0011   | ±2g                                  | 15.63 mg/LSB |

| 0101   | ±4g                                  | 31.25 mg/LSB |

| 1000   | ±8g                                  | 62.5 mg/LSB  |

| 1100   | ±16g                                 | 125 mg/LSB   |

| others | reserved                             | -            |

#### 4.3.2 Temperature sensor

The width of temperature data is 8 bits given in two's complement representation. Temperature values are available in the (0x08) temp register.

The slope of the temperature sensor is 0.5 K/LSB, its center temperature is  $23^{\circ}\text{C}$  [(0x08) temp = 0x00].

Page 20

#### 4.4 Self-test

This feature permits to check the sensor functionality by applying electrostatic forces to the sensor core instead of external accelerations. By actually deflecting the seismic mass, the entire signal path of the sensor can be tested. Activating the self-test results in a static offset of the acceleration data; any external acceleration or gravitational force applied to the sensor during active self-test will be observed in the output as a superposition of both acceleration and self-test signal.

Before the self-test is enabled the g-range should be set to 8 g.The self-test is activated individually for each axis by writing the proper value to the (0x32) self\_test\_axis bits ('01b' for x-axis, '10b' for y-axis, '11b' for z-axis, '00b' to deactivate self-test). It is possible to control the direction of the deflection through bit (0x32) self\_test\_sign. The excitation occurs in negative (positive) direction if (0x32) self\_test\_sign = '0b' ('1b'). The amplitude of the deflection has to be set high by writing (0x32) self\_test\_amp='1b'. After the self-test is enabled, the user should wait 50ms before interpreting the acceleration data.

In order to ensure a proper interpretation of the self-test signal it is recommended to perform the self-test for both (positive and negative) directions and then to calculate the difference of the resulting acceleration values. Table 6 shows the minimum differences for each axis. The actually measured signal differences can be significantly larger.

Table 6: Self-test difference values

|                                     | x-axis signal | y-axis signal | z-axis signal |

|-------------------------------------|---------------|---------------|---------------|

| resulting minimum difference signal | 800 mg        | 800 mg        | 400 mg        |

It is recommended to perform a reset of the device after a self-test has been performed. If the reset cannot be performed, the following sequence must be kept to prevent unwanted interrupt generation: disable interrupts, change parameters of interrupts, wait for at least 50ms, enable desired interrupts.

#### 4.5 Offset compensation

Offsets in measured signals can have several causes but they are always unwanted and disturbing in many cases. Therefore, the BMA222E offers an advanced set of four digital offset compensation methods which are closely matched to each other. These are slow, fast, and manual compensation as well as inline calibration.

The compensation is performed with unfiltered data, and is then applied to both, unfiltered and filtered data. If necessary the result of this computation is saturated to prevent any overflow errors (the smallest or biggest possible value is set, depending on the sign). However, the registers used to read and write compensation values have only a width of 8 bits.

An overview of the offset compensation principle is given in figure 5:

Figure 5: Principle of offset compensation

Page 22

The public offset compensation registers (0x38) offset\_x, (0x39) offset\_y, (0x3A) offset\_z are images of the corresponding registers in the NVM. With each image update (see section 4.6 Non-volatile memory for details) the contents of the NVM registers are written to the public registers. The public registers can be over-written by the user at any time.

Figure 5 illustrates how the offset compensation value scales with the range setting. The scaled offset compensation value is subsequently subtracted from the raw acceleration value.

By writing '1' to the (0x36) offset\_reset bit, all offset compensation registers are reset to zero.

#### 4.5.1 Slow compensation

Slow compensation is based on a  $1^{st}$  order high-pass filter, which continuously drives the average value of the output data stream of each axis to zero. The bandwidth of the high-pass filter is configured with bit (0x37) cut\_off according to Table 7Fehler! Verweisquelle konnte nicht gefunden werden..

Table 7: Compensation period settings

| (0x37)<br>cut_off | high-pass filter<br>bandwidth      | Example<br><i>bw</i> = 500 Hz                   |

|-------------------|------------------------------------|-------------------------------------------------|

| 0b                | $\frac{1Hz \times bw *}{1000 Hz}$  | $\frac{1Hz \times 500  Hz}{1000  Hz} = 0.5  Hz$ |

| 1b                | $\frac{10Hz \times bw *}{1000 Hz}$ | $\frac{10Hz \times 500  Hz}{1000  Hz} = 5  Hz$  |

<sup>\*</sup>bw: please insert selected decimal data bandwidth value [Hz] from table 4

The slow compensation can be enabled (disabled) for each axis independently by setting the bits  $(0x36) hp_xen, hp_yen, hp_zen$  to '1' ('0'), respectively.

Slow compensation should not be used in combination with low-power mode. In low-power mode the conditions (availability of necessary data) for proper function of slow compensation are not fulfilled.

#### 4.5.2 Fast compensation

Fast compensation is a one-shot process by which the compensation value is set in such a way that when added to the raw acceleration, the resulting acceleration value of each axis approaches the target value. This is best suited for "end-of-line trimming" with the customer's device positioned in a well-defined orientation. For fast compensation the g-range has to be switched to 2g.

The algorithm in detail: An average of 16 consecutive acceleration values is computed and the difference between target value and computed value is written to (0x38, 0x39, 0x34) offset\_filt\_x/y/z. The public registers (0x38, 0x39, 0x34) offset\_filt\_x/y/z are updated with the contents of the internal registers (using saturation if necessary) and can be read by the user.

Fast compensation is triggered for each axis individually by setting the (0x36) cal\_trigger bits as shown in Table 8:

Table 8: Fast compensation axis selection

| (0x36)<br>cal_trigger | Selected Axis |

|-----------------------|---------------|

| 00b                   | none          |

| 01b                   | X             |

| 10b                   | у             |

| 11b                   | Z             |

Page 24

Register (0x36) cal\_trigger is a write-only register. Once triggered, the status of the fast correction process is reflected in the status bit (0x36) cal\_rdy. Bit (0x36) cal\_rdy is '0' while the correction is in progress. Otherwise it is '1'. Bit (0x36) cal\_rdy is '0' when (0x36) cal\_trigger is not '00'.

For the fast offset compensation, the compensation target can be chosen by setting the bits (0x37) offset\_target\_x, (0x37) offset\_target\_y, and (0x37) offset\_target\_z according to Table 9:

(0x37)

Target value

00b

0g

01b

+1g

10b

-1g

11b

0g

Table 9: Offset target settings

Fast compensation should not be used in combination with any of the low-power modes. In low-power mode the conditions (availability of necessary data) for proper function of fast compensation are not fulfilled.

#### 4.5.3 Manual compensation

The contents of the public compensation registers (0x38, 0x39, 0x3A) offset\_filt\_x/y/z can be set manually via the digital interface. It is recommended to write into these registers directly after a new data interrupt has occurred in order not to disturb running offset computations.

Writing to the offset compensation registers is not allowed while the fast compensation procedure is running.

#### 4.5.4 Inline calibration

For certain applications, it is often desirable to calibrate the offset once and to store the compensation values permanently. This can be achieved by using one of the aforementioned offset compensation methods to determine the proper compensation values and then storing these values permanently in the NVM. See section 4.6 Non-volatile memory for details of the storing procedure.

Each time the device is reset, the compensation values are loaded from the non-volatile memory into the image registers and used for offset compensation until they are possibly overwritten using one of the other compensation methods.

Page 25

#### 4.6 Non-volatile memory

The entire memory of the BMA222E consists of three different kinds of registers: hard-wired, volatile, and non-volatile. Part of it can be both read and written by the user. Access to non-volatile memory is only possible through (volatile) image registers.

Altogether, there are eight registers (octets) with NVM backup which are accessible by the user. The addresses of the image registers range from 0x38 to 0x3C. While the addresses up to 0x3A are used for offset compensation (see 4.4 Offset Compensation), addresses 0x3B and 0x3C are general purpose registers not linked to any sensor-specific functionality.

The content of the NVM is loaded to the image registers after a reset (either POR or softreset) or after a user request which is performed by writing '1' to the write-only bit (0x33)  $nvm_load$ . As long as the image update is in progress, bit (0x33)  $nvm_rdy$  is '0', otherwise it is '1'.

The image registers can be read and written like any other register.

Writing to the NVM is a three-step procedure:

- 1. Write the new contents to the image registers.

- 2. Write '1' to bit (0x33) nvm\_prog\_mode in order to unlock the NVM.

- 3. Write '1' to bit (0x33) nvm\_prog\_trig and keep '1' in bit (0x33) nvm\_prog\_mode in order to trigger the write process.

Writing to the NVM always renews the entire NVM contents. It is possible to check the write status by reading bit  $(0x33) \ nvm_rdy$ . While  $(0x33) \ nvm_rdy = '0'$ , the write process is still in progress; if  $(0x33) \ nvm_rdy = '1'$ , then writing is completed. As long as the write process is ongoing, no change of power mode and image registers is allowed. Also, the NVM write cycle must not be initiated while image registers are updated, in low-power mode, and in suspend mode.

Please note that the number of permitted NVM write-cycles is limited as specified in Table 1. The number of remaining write-cycles can be obtained by reading bits (0x33)  $nvm_remain$ .

#### 4.7 Interrupt controller

The BMA222E is equipped with eight programmable interrupt engines. Each interrupt can be independently enabled and configured. If the trigger condition of an enabled interrupt is fulfilled, the corresponding status bit is set to '1' and the selected interrupt pin is activated. The BMA222E provides two interrupt pins, INT1 and INT2; interrupts can be freely mapped to any of these pins. The state of a specific interrupt pin is derived from a logic 'or' combination of all interrupts mapped to it.

The interrupt status registers are updated when a new data word is written into the acceleration data registers. If an interrupt is disabled, all active status bits associated with it are immediately reset.

#### 4.7.1 General features

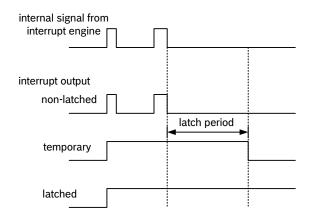

An interrupt is cleared depending on the selected interrupt mode, which is common to all interrupts. There are three different interrupt modes: non-latched, latched, and temporary. The mode is selected by the (0x21) latch\_int bits according to Table 10.

(0x21)Interrupt mode latch\_int 0000b non-latched 0001b temporary, 250ms 0010b temporary, 500ms 0011b temporary, 1s 0100b temporary, 2s 0101b temporary, 4s 0110b temporary, 8s 0111b latched 1000b non-latched 1001b temporary, 250µs 1010b temporary, 500µs 1011b temporary, 1ms 1100b temporary, 12.5ms 1101b temporary, 25ms 1110b temporary, 50ms

Table 10: Interrupt mode selection

An interrupt is generated if its activation condition is met. It can not be cleared as long as the activation condition is fulfilled. In the non-latched mode the interrupt status bit and the selected pin (the contribution to the 'or' condition for INT1 and/or INT2) are cleared as soon as the activation condition is no more valid. Exceptions to this behavior are the new data, orientation, and flat interrupts, which are automatically reset after a fixed time.

latched

1111b

Page 27

In latched mode an asserted interrupt status and the selected pin are cleared by writing '1' to bit (0x21) reset\_int. If the activation condition still holds when it is cleared, the interrupt status is asserted again with the next change of the acceleration registers.

In the temporary mode an asserted interrupt and selected pin are cleared after a defined period of time. The behaviour of the different interrupt modes is shown graphically in figure 6. The timings in this mode are subject to the same tolerances as the bandwidths (see Table 1).

Figure 6: Interrupt modes

Several interrupt engines can use either unfiltered or filtered acceleration data as their input. For these interrupts, the source can be selected with the bits in register (0x1E). These are (0x1E)  $int\_src\_data$ , (0x1E)  $int\_src\_tap$ , (0x1E)  $int\_src\_slo\_no\_mot$ , (0x1E)  $int\_src\_slope$ , (0x1E)  $int\_src\_lope$ , (0x1E)  $int\_src\_lop$

It is strongly recommended to set interrupt parameters prior to enabling the interrupt. Changing parameters of an already enabled interrupt may cause unwanted interrupt generation and generation of a false interrupt history. A safe way to change parameters of an enabled interrupt is to keep the following sequence: disable the desired interrupt, change parameters, wait for at least 10ms, and then re-enable the desired interrupt.

#### 4.7.2 Mapping to physical interrupt pins (inttype to INT Pin#)

Registers (0x19) to (0x1B) are dedicated to mapping of interrupts to the interrupt pins "INT1" or "INT2". Setting (0x19) int1\_"inttype" to '1' ('0') maps (unmaps) "inttype" to pin "INT1". Correspondingly setting (0x1B) int2\_"inttype" to '1' ('0') maps (unmaps) "inttype" to pin "INT2".

Note: "inttype" to be replaced with the precise notation, given in the memory map in chapter 6.

Example: For flat interrupt (int1 flat): Setting (0x19) int1 flat to '1' maps int1 flat to pin "INT1".

Page 28

#### 4.7.3 Electrical behaviour (INT pin# to open-drive or push-pull)

Both interrupt pins can be configured to show the desired electrical behaviour. The 'active' level of each interrupt pin is determined by the (0x20) int1\_lvl and (0x20) int2\_lvl bits.

If (0x20)  $int1_lvl = '1'$  ('0') / (0x20)  $int2_lvl = '1'$  ('0'), then pin "INT1" / pin "INT2" is active '1' ('0'). The characteristic of the output driver of the interrupt pins may be configured with bits (0x20)  $int1_lod$  and (0x20)  $int2_lod$ . By setting bits (0x20)  $int1_lod$  / (0x20)  $int2_lod$  to '1', the output driver shows open-drive characteristic, by setting the configuration bits to '0', the output driver shows push-pull characteristic. When open-drive characteristic is selected in the design, external pull-up or pull-down resistor should be applied according the int\_lvl configuration.

#### 4.7.4 New data interrupt

This interrupt serves for synchronous reading of acceleration data. It is generated after storing a new value of z-axis acceleration data in the data register. The interrupt is cleared automatically when the next data acquisition cycle starts. The interrupt status is '0' for at least 50µs.

The interrupt mode of the new data interrupt is fixed to non-latched.

It is enabled (disabled) by writing '1' ('0') to bit (0x17) data\_en. The interrupt status is stored in bit (0x0A) data\_int.

Due to the settling time of the filter, the first interrupt after wake-up from suspend or standby mode will take longer than the update time.

#### 4.7.5 Slope / any-motion detection

Slope / any-motion detection uses the slope between successive acceleration signals to detect changes in motion. An interrupt is generated when the slope (absolute value of acceleration difference) exceeds a preset threshold. It is cleared as soon as the slope falls below the threshold. The principle is made clear in figure 7.

Figure 7: Principle of any-motion detection

The threshold is defined through register (0x28) slope\_th. In terms of scaling 1 LSB of (0x28) slope\_th corresponds to 15.6mg in 2g-range (31.3mg in 4g-range, 62.5mg in 8g-range and 125mg in 16g-range).

The time difference between the successive acceleration signals depends on the selected bandwidth and equates to 1/(2\*bandwidth) ()t=1/(2\*bw)). In order to suppress false triggers, the interrupt is only generated (cleared) if a certain number N of consecutive slope data points is larger (smaller) than the slope threshold given by (0x28) slope\_th. This number is set by the (0x27) slope\_dur bits. It is N = (0x27) slope\_dur + 1 for (0x27).

Example: (0x27) slope dur = 00b, ..., 11b = 1decimal, ..., 4decimal.

Page 30

#### 4.7.5.1 Enabling (disabling) for each axis

Any-motion detection can be enabled (disabled) for each axis separately by writing '1' ('0') to bits (0x16)  $slope\_en\_x$ , (0x16)  $slope\_en\_y$ , (0x16)  $slope\_en\_z$ . The criteria for any-motion detection are fulfilled and the slope interrupt is generated if the slope of any of the enabled axes exceeds the threshold (0x28)  $slope\_th$  for [(0x27)  $slope\_dur +1]$  consecutive times. As soon as the slopes of all enabled axes fall or stay below this threshold for [(0x27)  $slope\_dur +1]$  consecutive times the interrupt is cleared unless interrupt signal is latched.

#### 4.7.5.2 Axis and sign information of slope / any motion interrupt

The interrupt status is stored in bit (0x09)  $slope_int$ . The any-motion interrupt supplies additional information about the detected slope. The axis which triggered the interrupt is given by that one of bits (0x0B)  $slope_first_x$ , (0x0B)  $slope_first_y$ , (0x0B)  $slope_first_z$  that contains a value of '1'. The sign of the triggering slope is held in bit (0x0B)  $slope_sign$  until the interrupt is retriggered. If (0x0B)  $slope_sign = '0'$  ('1'), the sign is positive (negative).

#### 4.7.6 Tap sensing

Tap sensing has a functional similarity with a common laptop touch-pad or clicking keys of a computer mouse. A tap event is detected if a pre-defined slope of the acceleration of at least one axis is exceeded. Two different tap events are distinguished: A 'single tap' is a single event within a certain time, followed by a certain quiet time. A 'double tap' consists of a first such event followed by a second event within a defined time frame.

Single tap interrupt is enabled (disabled) by writing '1' ('0') to bit (0x16) s\_tap\_en. Double tap interrupt is enabled (disabled) by writing '1' ('0') to bit (0x16) d\_tap\_en.

While temporary latching is used do not simultaneously enable single tap interrupt and double tap interrupt.

The status of the single tap interrupt is stored in bit (0x09) s\_tap\_int, the status of the double tap interrupt is stored in bit (0x09) d\_tap\_int.

The slope threshold for detecting a tap event is set by bits (0x2B) tap\_th. The meaning of (0x2B) tap\_th depends on the range setting. 1 LSB of (0x2B) tap\_th corresponds to a slope of 62.5mg in 2g-range, 125mg in 4g-range, 250mg in 8g-range, and 500mg in 16g-range.

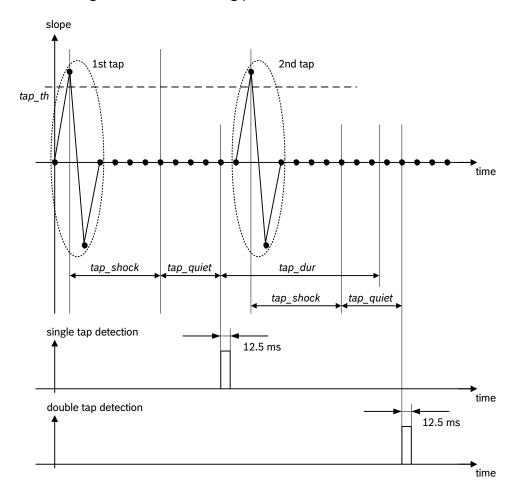

In figure 8 the meaning of the different timing parameters is visualized:

Figure 8: Timing of tap detection

The parameters (0x2A)  $tap\_shock$  and (0x2A)  $tap\_quiet$  apply to both single tap and double tap detection, while (0x2A)  $tap\_dur$  applies to double tap detection only. Within the duration of (0x2A)  $tap\_shock$  any slope exceeding (0x2B)  $tap\_th$  after the first event is ignored. Contrary to this, within the duration of (0x2A)  $tap\_quiet$  no slope exceeding (0x2B)  $tap\_th$  must occur, otherwise the first event will be cancelled.

#### 4.7.6.1 Single tap detection

A single tap is detected and the single tap interrupt is generated after the combined durations of (0x2A)  $tap\_shock$  and (0x2A)  $tap\_quiet$ , if the corresponding slope conditions are fulfilled. The interrupt is cleared after a delay of 12.5 ms.

Do not map single-tap to any INT pin if you do not want to use it.

#### 4.7.6.2 Double tap detection

A double tap interrupt is generated if an event fulfilling the conditions for a single tap occurs within the set duration in (0x2A)  $tap\_dur$  after the completion of the first tap event. The interrupt is automatically cleared after a delay of 12.5 ms.

#### 4.7.6.3 Selecting the timing of tap detection

For each of parameters (0x2A)  $tap\_shock$  and (0x2A)  $tap\_quiet$  two values are selectable. By writing '0' ('1') to bit (0x2A)  $tap\_shock$  the duration of (0x2A)  $tap\_shock$  is set to 50 ms (75 ms). By writing '0' ('1') to bit (0x2A)  $tap\_quiet$  the duration of (0x2A)  $tap\_quiet$  is set to 30 ms (20 ms).

The length of (0x2A)  $tap\_dur$  can be selected by setting the (0x2A)  $tap\_dur$  bits according to Table 11:

(0x2A)length of tap\_dur tap\_dur 000b 50 ms 001b 100 ms 010b 150 ms 011b 200 ms 100b 250 ms 101b 375 ms 110b 500 ms 111b 700 ms

Table 11: Selection of tap dur

Page 33

#### 4.7.6.4 Axis and sign information of tap sensing

The sign of the slope of the first tap which triggered the interrupt is stored in bit (0x0B) tap\_sign ('0' means positive sign, '1' means negative sign). The value of this bit persists after clearing the interrupt.

The axis which triggered the interrupt is indicated by bits (0x0B) tap\_first\_x, (0x0B) tap\_first\_y, and (0x0B) tap\_first\_z.

The bit corresponding to the triggering axis contains a '1' while the other bits hold a '0'. These bits are cleared together with clearing the interrupt status.

#### 4.7.6.5 Tap sensing in low power mode

In low-power mode, a limited number of samples is processed after wake-up to decide whether an interrupt condition is fulfilled. The number of samples is selected by bits (0x2B) tap\_samp according to Table 12.

Table 12: Meaning of (0x2B) tap\_samp

| (0x2B)<br>tap_samp | Number of Samples |

|--------------------|-------------------|

| 00b                | 2                 |

| 01b                | 4                 |

| 10b                | 8                 |

| 11b                | 16                |

#### 4.7.7 Orientation recognition

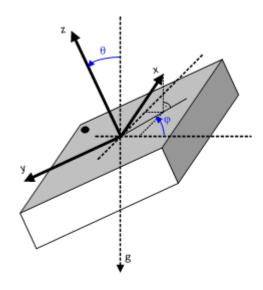

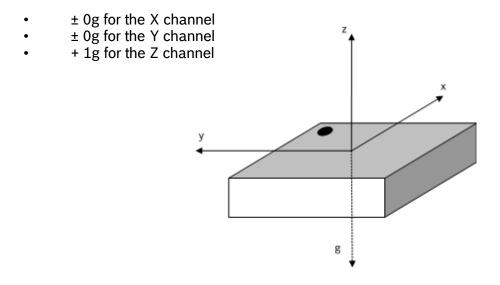

The orientation recognition feature informs on an orientation change of the sensor with respect to the gravitational field vector 'g'. The measured acceleration vector components with respect to the gravitational field are defined as shown in figure 9.

Figure 9: Definition of vector components

Therefore, the magnitudes of the acceleration vectors are calculated as follows:

$$acc_x = 1g x sin\theta x cos\phi$$

$acc_y = -1g x sin\theta x sin\phi$

$acc_z = 1g x cos\theta$

$acc_y/acc_x = -tan\phi$

Depending on the magnitudes of the acceleration vectors the orientation of the device in the space is determined and stored in the three (0x0C) orient bits. These bits may not be reset in the sleep phase of low-power mode. There are three orientation calculation modes with different thresholds for switching between different orientations: symmetrical, high-asymmetrical, and low-asymmetrical. The mode is selected by setting the (0x2C) orient\_mode bits as given in Table 13.

Table 13: Orientation mode settings

| (0x2C)<br>orient_mode | Orientation Mode  |  |

|-----------------------|-------------------|--|

| 00b                   | symmetrical       |  |

| 01b                   | high-asymmetrical |  |

| 10b                   | low-asymmetrical  |  |

| 11b                   | symmetrical       |  |

For each orientation mode the (0x0C) orient bits have a different meaning as shown in Table 14 to Table 16:

Table 14: Meaning of the (0x0C) orient bits in symmetrical mode

| (0x0C)<br>orient | Name                 | Angle           | Condition                                           |

|------------------|----------------------|-----------------|-----------------------------------------------------|

| x00              | portrait upright     | 315° < φ < 45°  | acc_y  <  acc_x  - 'hyst'<br>and acc_x - 'hyst' ≥ 0 |

| x01              | portrait upside down | 135° < φ < 225° | acc_y  <  acc_x  - 'hyst'<br>and acc_x + 'hyst' < 0 |

| x10              | landscape left       | 45° < φ < 135°  | $ acc_y  \ge  acc_x  + 'hyst'$<br>and $acc_y < 0$   |

| x11              | landscape right      | 225° < φ < 315° | $ acc_y  \ge  acc_x  + 'hyst'$<br>and $acc_y \ge 0$ |

Table 15: Meaning of the (0x0C) orient bits in high-asymmetrical mode

| (0x0C)<br>orient | Name                 | Angle           | Condition                                                          |

|------------------|----------------------|-----------------|--------------------------------------------------------------------|

| x00              | portrait upright     | 297° < φ < 63°  | $ acc_y  < 2 \cdot  acc_x  - 'hyst'$<br>and $acc_x - 'hyst' \ge 0$ |

| x01              | portrait upside down | 117° < φ < 243° | $ acc_y  < 2 \cdot  acc_x  - 'hyst'$<br>and $acc_x + 'hyst' < 0$   |

| x10              | landscape left       | 63° < φ < 117°  | $ acc_y  \ge 2 \cdot  acc_x  + 'hyst'$<br>and $acc_y < 0$          |

| x11              | landscape right      | 243° < φ < 297° | $ acc_y  \ge 2 \cdot  acc_x  + 'hyst'$<br>and acc $y \ge 0$        |

Table 16: Meaning of the (0x0C) orient bits in low-asymmetrical mode

| (0x0C)<br>orient | Name                 | Angle           | Condition                                                     |

|------------------|----------------------|-----------------|---------------------------------------------------------------|

| x00              | portrait upright     | 333° < φ < 27°  | acc_y  < 0.5 ·  acc_x  - 'hyst'<br>and acc_x - 'hyst' ≥ 0     |

| x01              | portrait upside down | 153° < φ < 207° | acc_y  < 0.5 ·  acc_x  - 'hyst'<br>and acc_x + 'hyst' < 0     |

| x10              | landscape left       | 27° < φ < 153°  | $ acc_y  \ge 0.5 \cdot  acc_x  + 'hyst'$<br>and $acc_y < 0$   |

| x11              | landscape right      | 207° < φ < 333° | $ acc_y  \ge 0.5 \cdot  acc_x  + 'hyst'$<br>and $acc_y \ge 0$ |

In the preceding tables, the parameter 'hyst' stands for a hysteresis, which can be selected by setting the (0x2C) orient\_hyst bits. 1 LSB of (0x2C) orient\_hyst always corresponds to 62.5 mg, in any g-range (i.e. increment is independent from g-range setting). It is important to note that by using a hysteresis  $\neq$  0 the actual switching angles become different from the angles given in the tables since there is an overlap between the different orientations.

The most significant bit of the *(0x0C)* orient bits (which is displayed as an 'x' in the above given tables) contains information about the direction of the z-axis. It is set to '0' ('1') if  $acc_z \ge 0$  ( $acc_z < 0$ ).

Page 36

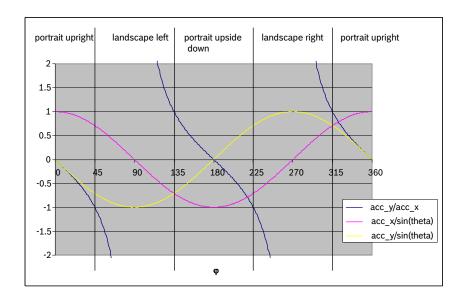

Figure 10 shows the typical switching conditions between the four different orientations for the symmetrical mode i.e. without hysteresis:

Figure 10: Typical orientation switching conditions w/o hysteresis

The orientation interrupt is enabled (disabled) by writing '1' ('0') to bit (0x16) orient\_en. The interrupt is generated if the value of (0x0C) orient has changed. It is automatically cleared after one stable period of the (0x0C) orient value. The interrupt status is stored in the (0x09) orient\_int bit. The register (0x0C) orient always reflects the current orientation of the device, irrespective of which interrupt mode has been selected. Bit (0x0C) orient<2> reflects the device orientation with respect to the z-axis. The bits (0x0C) orient<1:0> reflect the device orientation in the x-y-plane. The conventions associated with register (0x0C) orient are detailed in chapter 6.

#### 4.7.7.1 Orientation blocking

The change of the (0x0C) orient value and – as a consequence – the generation of the interrupt can be blocked according to conditions selected by setting the value of the (0x2C) orient\_blocking bits as described by Table 17

(0x2C) **Conditions** orient\_blocking 00b no blocking theta blocking 01b or acceleration in any axis > 1.5g theta blocking 10b acceleration slope in any axis > 0.2 g acceleration in any axis > 1.5g theta blocking acceleration slope in any axis > 0.4 g 11b acceleration in any axis > 1.5g and value of orient is not stable for at least 100 ms

Table 17: Blocking conditions for orientation recognition

The theta blocking is defined by the following inequality:

$$|\tan \theta| < \frac{\sqrt{blocking \_theta}}{8}$$

The parameter *blocking\_theta* of the above given equation stands for the contents of the (0x2D) orient\_theta bits. It is possible to define a blocking angle between 0° and 44.8°. The internal blocking algorithm saturates the acceleration values before further processing. As a consequence, the blocking angles are strictly valid only for a device at rest; they can be different if the device is moved.

#### Example:

To get a maximum blocking angle of 19° the parameter *blocking\_theta* is determined in the following way:  $(8 * tan(19°))^2 = 7.588$ , therefore, *blocking\_value* = 8dec = 001000b has to be chosen.

In order to avoid unwanted generation of the orientation interrupt in a nearly flat position ( $z \sim 0$ , sign change due to small movements or noise), a hysteresis of 0.2 g is implemented for the z-axis, i. e. a after a sign change the interrupt is only generated after |z| > 0.2 g.

#### 4.7.7.2 Up-Down Interrupt Suppression Flag

Per default an orientation interrupt is triggered when any of the bits in register (0x0C) orient

Page 38

changes state. The BMA222E can be configured to trigger orientation interrupts only when the device position changes in the x-y-plane while orientation changes with respect to the z-axis are ignored. A change of the orientation of the z-axis, and hence a state change of bit (0x0C) orient<2> is ignored (considered) when bit (0x2D) orient\_ud\_en is set to '0' ('1').

#### 4.7.8 Flat detection

The flat detection feature gives information about the orientation of the devices' z-axis relative to the g-vector, i. e. it recognizes whether the device is in a flat position or not.

The flat angle  $\Theta$  is adjustable by (0x2E) flat\_theta from 0° to 44.8°. The flat angle can be set according to following formula:

$$\Theta = \operatorname{atan}\left(\frac{1}{8}\sqrt{\operatorname{flat\_theta}}\right)$$

A hysteresis of the flat detection can be enabled by (0x2F) flat\_hy bits. In this case the flat position is set if the angle drops below following threshold:

$$\Theta_{hyst,ll} = \operatorname{atan}\left(\frac{1}{8}\sqrt{\operatorname{flat\_theta}\cdot\left(1 - \frac{\operatorname{flat\_hy}}{1024}\right) - \frac{\operatorname{flat\_hy}}{16}}\right)$$

The flat position is reset if the angle exceeds the following threshold:

$$\Theta_{hyst,ul} = \operatorname{atan}\left(\frac{1}{8}\sqrt{\operatorname{flat\_theta}\cdot\left(1 + \frac{flat\_hy}{1024}\right) + \frac{flat\_hy}{16}}\right)$$

The flat interrupt is enabled (disabled) by writing '1' ('0') to bit (0x16) flat\_en. The flat value is stored in the (0x0C) flat bit if the interrupt is enabled. This value is '1' if the device is in the flat position, it is '0' otherwise. The flat interrupt is generated if the flat value has changed and the new value is stable for at least the time given by the (0x2F) flat\_hold\_time bits. A flat interrupt may be also generated if the flat interrupt is enabled. The actual status of the interrupt is stored in the (0x09) flat\_int bit. The flat orientation of the sensor can always be determined from reading the (0x0C) flat bit after interrupt generation. If unlatched interrupt mode is used, the (0x09) flat\_int value and hence the interrupt is automatically cleared after one sample period. If temporary or latched interrupt mode is used, the (0x09) flat\_int value is kept fixed until the latch time expires or the interrupt is reset.

The meaning of the (0x2F) flat\_hold\_time bits can be seen from Table 18.

Table 18: Meaning of flat hold time

| (0x2F)<br>flat_hold_time | Time    |

|--------------------------|---------|

| 00b                      | 0       |

| 01b                      | 512 ms  |

| 10b                      | 1024 ms |

| 11b                      | 2048 ms |

Page 40

#### 4.7.9 Low-g interrupt

This interrupt is based on the comparison of acceleration data against a low-g threshold, which is most useful for free-fall detection.

The interrupt is enabled (disabled) by writing '1' ('0') to the (0x17) low\_en bit. There are two modes available, 'single' mode and 'sum' mode. In 'single' mode, the acceleration of each axis is compared with the threshold; in 'sum' mode, the sum of absolute values of all accelerations  $|acc_x| + |acc_y| + |acc_z|$  is compared with the threshold. The mode is selected by the contents of the (0x24) low\_mode bit: '0' means 'single' mode, '1' means 'sum' mode.

The low-g threshold is set through the (0x23) low\_th register. 1 LSB of (0x23) low\_th always corresponds to an acceleration of 7.81 mg (i.e. increment is independent from g-range setting).

A hysteresis can be selected by setting the (0x24) low\_hy bits. 1 LSB of (0x24) low\_hy always corresponds to an acceleration difference of 125 mg in any g-range (as well, increment is independent from g-range setting).

The low-g interrupt is generated if the absolute values of the acceleration of all axes ('and' relation, in case of single mode) or their sum (in case of sum mode) are lower than the threshold for at least the time defined by the  $(0x22) low_dur$  register. The interrupt is reset if the absolute value of the acceleration of at least one axis ('or' relation, in case of single mode) or the sum of absolute values (in case of sum mode) is higher than the threshold plus the hysteresis for at least one data acquisition. In bit  $(0x09) low_int$  the interrupt status is stored.

The relation between the content of (0x22)  $low_dur$  and the actual delay of the interrupt generation is: delay [ms] = [(0x22)  $low_dur + 1] \cdot 2$  ms. Therefore, possible delay times range from 2 ms to 512 ms.

Page 41

#### 4.7.10 High-g interrupt

This interrupt is based on the comparison of acceleration data against a high-g threshold for the detection of shock or other high-acceleration events.

The high-g interrupt is enabled (disabled) per axis by writing '1' ('0') to bits (0x17) high\_en\_x, (0x17) high\_en\_y, and (0x17) high\_en\_z, respectively. The high-g threshold is set through the (0x26) high\_th register. The meaning of an LSB of (0x26) high\_th depends on the selected grange: it corresponds to 7.81 mg in 2g-range, 15.63 mg in 4g-range, 31.25 mg in 8g-range, and 62.5 mg in 16g-range (i.e. increment depends from g-range setting).

A hysteresis can be selected by setting the (0x24) high\_hy bits. Analogously to (0x26) high\_th, the meaning of an LSB of (0x24) high\_hy is g-range dependent: It corresponds to an acceleration difference of 125 mg in 2g-range, 250 mg in 4g-range, 500 mg in 8g-range, and 1000mg in 16g-range (as well, increment depends from g-range setting).

The high-g interrupt is generated if the absolute value of the acceleration of at least one of the enabled axes ('or' relation) is higher than the threshold for at least the time defined by the (0x25) high\_dur register. The interrupt is reset if the absolute value of the acceleration of all enabled axes ('and' relation) is lower than the threshold minus the hysteresis for at least the time defined by the (0x25) high\_dur register. In bit (0x09) high\_int the interrupt status is stored. The relation between the content of (0x25) high\_dur and the actual delay of the interrupt generation is delay [ms] = [(0x22) low\_dur + 1] • 2 ms. Therefore, possible delay times range from 2 ms to 512 ms. The interrupt will be cleared immediately once acceleration is lower than threshold.

#### 4.7.10.1 Axis and sign information of high-g interrupt

The axis which triggered the interrupt is indicated by bits (0x0C) high\_first\_x, (0x0C) high\_first\_y, and (0x0C) high\_first\_z. The bit corresponding to the triggering axis contains a '1' while the other bits hold a '0'. These bits are cleared together with clearing the interrupt status. The sign of the triggering acceleration is stored in bit (0x0C) high\_sign. If (0x0C) high\_sign = '0' ('1'), the sign is positive (negative).

#### 4.7.11 No-motion / slow motion detection

The slow-motion/no-motion interrupt engine can be configured in two modes.

In slow-motion mode an interrupt is triggered when the measured slope of at least one enabled axis exceeds the programmable slope threshold for a programmable number of samples. Hence the engine behaves similar to the any-motion interrupt, but with a different set of parameters. In order to suppress false triggers, the interrupt is only generated (cleared) if a certain number N of consecutive slope data points is larger (smaller) than the slope threshold given by (0x27) slo\_no\_mot\_dur<1:0> . The number is N = (0x27) slo\_no\_mot\_dur<1:0> + 1.

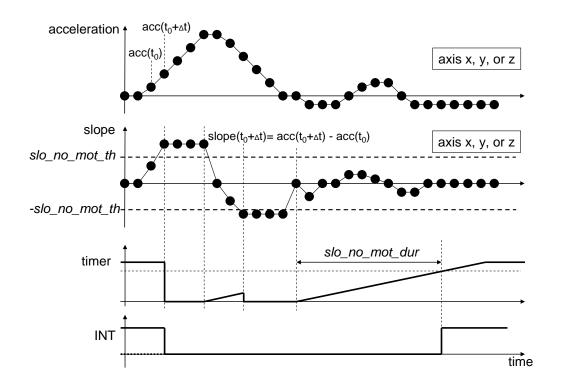

In no-motion mode an interrupt is generated if the slope on all selected axes remains smaller than a programmable threshold for a programmable delay time. Figure 11 shows the timing diagram for the no-motion interrupt. The scaling of the threshold value is identical to that of the slow-motion interrupt. However, in no-motion mode register (0x27) slo\_no\_mot\_dur defines the delay time before the no-motion interrupt is triggered. Table 19 lists the delay times adjustable with register (0x27) slo\_no\_mot\_dur. The timer tick period is 1 second. Hence using short delay times can result in considerable timing uncertainty.

If bit (0x18)  $slo_no_mot_sel$  is set to '1' ('0') the no-motion/slow-motion interrupt engine is configured in the no-motion (slow-motion) mode. Common to both modes, the engine monitors the slopes of the axes that have been enabled with bits (0x18)  $slo_no_mot_en_x$ , (0x18)  $slo_no_mot_en_y$ , and (0x18)  $slo_no_mot_en_z$  for the x-axis, y-axis and z-axis, respectively. The measured slope values are continuously compared against the threshold value defined in register (0x29)  $slo_no_mot_th$ . The scaling is such that 1 LSB of (0x29)  $slo_no_mot_th$  corresponds to 3.91 mg in 2g-range (7.81 mg in 4g-range, 15.6 mg in 8g-range and 31.3 mg in 16g-range). Therefore the maximum value is 996 mg in 2g-range (1.99g in 4g-range, 3.98g in 8g-range and 7.97g in 16g-range). The time difference between the successive acceleration samples depends on the selected bandwidth and equates to 1/(2\*bw).

Table 19: No-motion time-out periods

| (0x27)<br>slo_no_mot_dur | Delay<br>time | (0x27)<br>slo_no_mot_dur | Delay<br>time | (0x27)<br>slo_no_mot_dur | Delay<br>Time |

|--------------------------|---------------|--------------------------|---------------|--------------------------|---------------|

| 0                        | 1 s           | 16                       | 40 s          | 32                       | 88 s          |

| 1                        | 2 s           | 17                       | 48 s          | 33                       | 96 s          |

| 2                        | 3 s           | 18                       | 56 s          | 34                       | 104 s         |

| •••                      | •••           | 19                       | 64 s.         | •••                      |               |

| 14                       | 15 s          | 20                       | 72 s          | 62                       | 328 s         |

| 15                       | 16 s          | 21                       | 80 s          | 63                       | 336 s         |

Note: slo\_no\_mot\_dur values 22 to 31 are not specified

Figure 11: Timing of No-motion interrupt

Page 44

### 4.8 Softreset

A softreset causes all user configuration settings to be overwritten with their default value and the sensor to enter normal mode.

A softreset is initiated by means of writing value 0xB6 to register (0x14) softreset. Subsequently a waiting time of  $t_{w,up1}$  (max.) is required prior to accessing any configuration registers.

# 5. FIFO Operation

#### **5.1 FIFO Operating Modes**

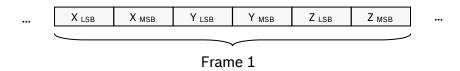

The BMA222E features an integrated FIFO memory capable of storing up to 32 frames. Conceptually each frame consists of three 16 bit words corresponding to the x, y and z- axis, which are sampled at the same point in time. At the core of the FIFO is a buffer memory, which can be configured to operate in the following modes:

- FIFO Mode: In FIFO mode the acceleration data of the selected axes are stored in the

buffer memory. If enabled, a watermark interrupt is triggered when the buffer has filled

up to a configurable level. The buffer will be continuously filled until the fill level reaches

32 frames. When it is full the data collection is stopped, and all additional samples are

ignored. Once the buffer is full, a FIFO-full interrupt is generated if it has been enabled.