# ACPL-33JT

Automotive 2.5 Amp Gate Drive Optocoupler with Integrated Flyback Controller for Isolated DC-DC Converter, Integrated IGBT Desat Over Current Sensing, Miller Current Clamping and UVLO Feedback

# **Data Sheet**

## Description

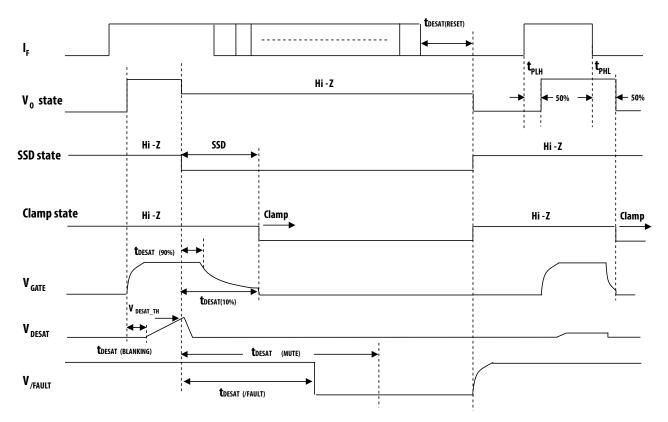

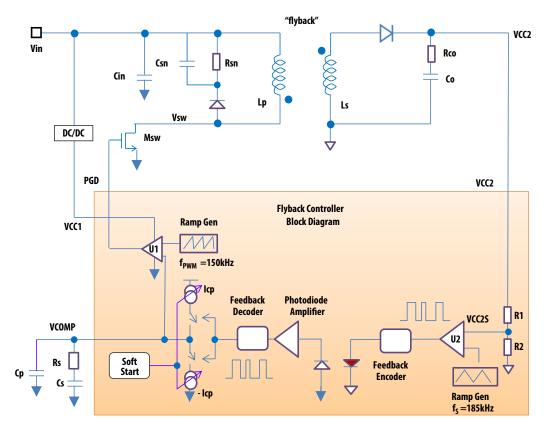

The ACPL-33JT Automotive 2.5 Amp Gate Drive Optocoupler features integrated flyback controller for isolated DC-DC converter, IGBT desaturation sensing and fault feedback, Under-Voltage LockOut (UVLO) with soft-shutdown and fault feedback and active Miller current clamping. The fast propagation delay with excellent timing skew performance enables excellent timing control and efficiency. This full feature optocoupler comes in a compact, surface-mountable SO-16 package for space-savings, is suitable for traction power train inverter, power converter, battery charger, air-conditioner and oil pump motor drives in HEV and EV applications.

Avago R2Coupler<sup>®</sup> isolation products provide reinforced insulation and reliability that delivers safe signal isolation critical in automotive and high temperature industrial applications.

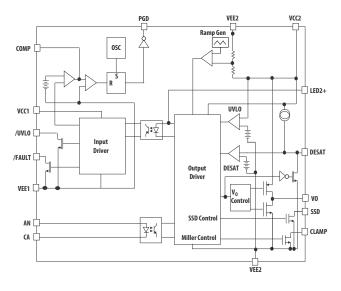

# **Functional Diagram**

## Figure 1 ACPL-33JT Functional Diagram

## Features

- Qualified to AEC-Q100 Grade 1 Test Guidelines

- Automotive temperature range: -40°C to +125°C

- Integrated flyback controller for isolated DC-DC converter

- Regulated output voltage: 16V

- Peak output current: 2.5A max.

- Miller clamp sinking current: 2A

- Input supply voltage range: 4.5V to 5.5V

- Common mode rejection (CMR): > 50 kV/µs at V<sub>CM</sub> = 1500V

- Propagation delay: 250 ns max.

- Integrated fail-safe IGBT protection

- Desat sensing, "soft" IGBT turn-off and fault feedback

- Under voltage lock-out (UVLO) protection with feedback

- High noise immunity

- Miller current clamping

- Direct LED input with low input impedance and low noise sensitivity

- SO-16 package with 8-mm clearance and creepage

- Regulatory approvals:

- UL1577, CSA

- IEC/EN/DIN EN 60747-5-5

## **Applications**

- Automotive isolated IGBT/MOSFET inverter gate drive

- Automotive DC-DC converter

- AC and brushless DC motor drives

- Hybrid and plug-in hybrid power train inverter

- Uninterruptible power supplies (UPSs)

**CAUTION** Take normal static precautions in handling and assembly of this component to prevent damage, degradation, or both, that might be induced by ESD. The components featured in this data sheet are not to be used in military or aerospace applications or environments.

#### Table 1 Ordering Information

| Part Number | Option (RoHS Compliant) | Package | Surface Mount | Tape and Reel | IEC/EN/DIN EN<br>60747-5-5 | Quantity     |

|-------------|-------------------------|---------|---------------|---------------|----------------------------|--------------|

| ACPL-33JT   | -500E                   | SO-16   | х             | Х             | Х                          | 850 per reel |

To order, choose a part number from the Part Number column and combine with the desired option from the Option column to form an order entry.

Example:

ACPL-33JT-500E to order product of SO-16 Surface Mount package in Tape and Reel packaging with IEC/EN/DIN EN 60747-5-5 Safety Approval in RoHS compliant.

Option data sheets are available. Contact your Broadcom sales representative or authorized distributor for information.

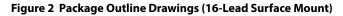

Dimensions in millimeters (inches).

#### NOTE

- Lead coplanarity = 0.10 mm (0.004 inches) max

- Floating lead protrusion = 0.254 mm ([0.010 inches) max

- Mold flash on each side = 0.254 mm (0.010 inches) max

## **Recommended Lead-free IR Profile**

Recommended reflow condition as per JEDEC Standard, J-STD-020 (latest revision).

Non-halide flux should be used.

## **Product Overview Description**

The ACPL-33JT (shown in Figure 1) is a highly integrated power control device that incorporates all the necessary components for a complete, reliable, isolated IGBT gate drive circuit. It features a flyback controller for isolated DC-DC converter, a high current gate driver, Miller current clamping, IGBT desaturation sensing, IGBT soft shutdown (SSD), fault feeback and under voltage lock-out (UVLO) protection and feedback in a SO-16 package. Direct LED input allows flexible logic configuration and differential current mode driving with low input impedance, greatly increases its noise immunity.

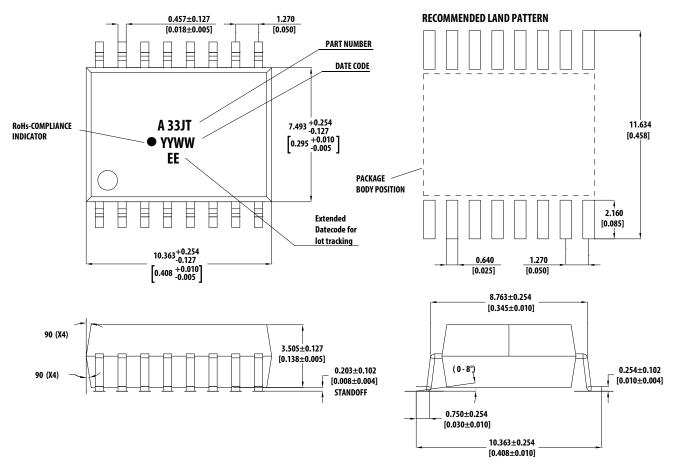

## Package Pinout

Figure 3 Pin out of ACPL-33JT

|          | VEE2 16  |

|----------|----------|

| 2 PGD    | LED2+ 15 |

| 3 VCC1   | DESAT 14 |

| 4 COMP   | SSD 13   |

| 5 /UVLO  | VCC2 12  |

| 6 /FAULT | V0 11    |

| 7 AN     | CLAMP 10 |

| 8 CA     | VEE2 9   |

|          |          |

#### Table 2 Pin Description

| Pin No. | Pin Name | Function                                    | Pin No. | Pin Name | Function                                    |

|---------|----------|---------------------------------------------|---------|----------|---------------------------------------------|

| 1       | VEE1     | Input IC common                             | 16      | VEE2     | Output IC common and IGBT emitter reference |

| 2       | PGD      | Primary gate drive for MOSFET               | 15      | LED2+    | No connection, for testing only             |

| 3       | VCC1     | Input power supply                          | 14      | DESAT    | Desaturation over current sensing           |

| 4       | COMP     | Compensation network for Flyback Controller | 13      | SSD      | Soft Shutdown                               |

| 5       | /UVLO    | VCC2 Under Voltage Lock-Out feedback        | 12      | VCC2     | Output power supply                         |

| 6       | /FAULT   | Over current fault feedback                 | 11      | VO       | Driver output to IGBT gate                  |

| 7       | AN       | Input LED anode                             | 10      | CLAMP    | Miller current clamping output              |

| 8       | CA       | Input LED cathode                           | 9       | VEE2     | Output IC common and IGBT emitter reference |

## **Regulatory Information**

The ACPL-33JT is approved by the following organizations:

#### **Table 3 Regulatory Information**

| UL                      | Approved under UL 1577, component recognition program up to VISO = 5000 VRMS.         |

|-------------------------|---------------------------------------------------------------------------------------|

| CSA                     | Approved under CSA Component Acceptance Notice #5, File CA 88324.                     |

| IEC/EN/DIN EN 60747-5-5 | Approved under: IEC 60747-5-5, EN 60747-5-5, DIN EN 60747-5-5, IEC/EN/DIN EN60747-5-5 |

#### Table 4 IEC/EN/DIN EN 60747-5-5 Insulation Characteristics

| Description                                                                                                                                             | Symbol                                                          | Characterist<br>ic | Unit              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------|-------------------|

| Insulation Classification per DIN VDE 0110/1.89, Table 1<br>for rated mains voltage ≤ 150 V <sub>rms</sub>                                              |                                                                 | I – IV             |                   |

| for rated mains voltage $\leq$ 300 V <sub>rm</sub> s<br>for rated mains voltage $\leq$ 600 V <sub>rms</sub>                                             |                                                                 | I – IV<br>I – IV   |                   |

| for rated mains voltage $\leq 1000 V_{rms}$                                                                                                             |                                                                 | I – III            |                   |

| Climatic Classification <sup>a</sup>                                                                                                                    |                                                                 | 40/125/21          |                   |

| Pollution Degree (DIN VDE 0110/1.89)                                                                                                                    |                                                                 | 2                  |                   |

| Maximum Working Insulation Voltage                                                                                                                      | V <sub>IORM</sub>                                               | 1230               | V <sub>PEAK</sub> |

| Input to Output Test Voltage, Method b<br>$V_{IORM} \times 1.875 = V_{PR}$ , 100% Production Test with t <sub>m</sub> = 1 sec, Partial discharge < 5 pC | V <sub>PR</sub>                                                 | 2306               | V <sub>PEAK</sub> |

| Input to Output Test Voltage, Method a $V_{IORM} 	imes 1.6 = V_{PR}$ , Type and Sample Test, t <sub>m</sub> = 10 sec, Partial Discharge < 5 pC          | V <sub>PR</sub>                                                 | 1968               | V <sub>PEAK</sub> |

| Highest Allowable Overvoltage (Transient Overvoltage t <sub>ini</sub> = 60 sec)                                                                         | V <sub>IOTM</sub>                                               | 8000               | V <sub>PEAK</sub> |

| Safety-limiting values – maximum values allowed in the event of a failure<br>Case Temperature<br>Input Power<br>Output Power                            | T <sub>s</sub><br>P <sub>s,input</sub><br>P <sub>s,output</sub> | 175<br>400<br>1200 | °C<br>mW<br>mW    |

| Insulation Resistance at T <sub>S</sub> , VIO = 500V                                                                                                    | R <sub>S</sub>                                                  | > 10 <sup>9</sup>  | Ohm               |

a. Climatic classification denotes minimum operating temperature/ maximum operating temperature/ humidity test duration.

#### NOTE

- 1. Isolation characteristics are guaranteed only within the safety maximum ratings which must be ensured by protective circuits in application. Surface mount classification is class A in accordance with CECCO0802.

- 2. Refer to the optocoupler section of the Isolation and Control Components Designer's Catalog, under Product Safety Regulation section IEC 60747-5-5, EN/DIN EN 60747-5-5, for a detailed description of Method a and Method b partial discharge test profiles.

#### Table 5 Insulation and Safety Related Specifications

| Parameter                                            | Symbol | Value | Units | Conditions                                                                                                                         |

|------------------------------------------------------|--------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| Minimum External Air Gap<br>(Clearance)              | L(101) | 8.3   | mm    | Measured from input terminals to output terminals, shortest distance through air.                                                  |

| Minimum External Tracking<br>(Creepage)              | L(102) | 8.3   | mm    | Measured from input terminals to output terminals, shortest distance path along body.                                              |

| Minimum Internal Plastic Gap<br>(Internal Clearance) |        | 0.5   | mm    | Through insulation distance conductor to conductor, usually the straight line distance thickness between the emitter and detector. |

| Tracking Resistance<br>(Comparative Tracking Index)  | СТІ    | >175  | Volts | DIN IEC 112/VDE 0303 Part 1                                                                                                        |

| Isolation Group                                      |        | Illa  |       | Material Group (DIN VDE 0110)                                                                                                      |

#### **Table 6 Absolute Maximum Ratings**

| Parameter                                                   | Symbol                                  | Min. | Max.                  | Units | Note |

|-------------------------------------------------------------|-----------------------------------------|------|-----------------------|-------|------|

| Storage Temperature                                         | prage Temperature T <sub>S</sub>        |      | 150                   | °C    |      |

| Operating Temperature                                       | T <sub>A</sub>                          | -40  | 125                   | °C    |      |

| Output IC Junction Temperature                              | Tj                                      |      | 150                   | °C    | a    |

| Average Input Current                                       | I <sub>F(AVG)</sub>                     |      | 20                    | mA    |      |

| Peak Transient Input Current (<1 μs<br>pulse width, 300pps) | I <sub>F(TRAN)</sub>                    |      | 1                     | A     |      |

| Reverse Input Voltage                                       | V <sub>R</sub>                          |      | 6.0                   | V     |      |

| Input Supply Voltage <sup>b</sup>                           | V <sub>CC1</sub> – V <sub>EE1</sub>     | -0.5 | 6.0                   | V     |      |

| Primary Gate Drive Voltage <sup>b</sup>                     | V <sub>PGD</sub> – V <sub>EE1</sub>     | -0.5 | V <sub>CC1</sub>      | V     |      |

| COMP Pin Voltage <sup>b</sup>                               | V <sub>COMP</sub> – V <sub>EE1</sub>    | -0.5 | V <sub>CC1</sub>      | V     |      |

| /UVLO Output Current <sup>c</sup>                           | I/UVLO                                  |      | 10                    | mA    |      |

| /UVLO Pin Voltage <sup>b</sup>                              | V/UVLO – V <sub>EE1</sub>               | -0.5 | 6.0                   | V     | d    |

| /Fault Output Current <sup>c</sup>                          | I/FAULT                                 |      | 10                    | mA    |      |

| /Fault Pin Voltage <sup>b</sup>                             | V/FAULT – V <sub>EE1</sub>              | -0.5 | 6.0                   | V     | d    |

| Output Supply Voltage <sup>b</sup>                          | V <sub>CC2</sub> – V <sub>EE2</sub>     | -0.5 | 25                    | V     |      |

| Peak Output Current <sup>c</sup>                            | I <sub>O(peak)</sub>                    |      | 2.5                   | A     | e    |

| Gate Drive Output Voltage <sup>b</sup>                      | V <sub>O(peak)</sub> – V <sub>EE2</sub> | -0.5 | V <sub>CC2</sub> +0.5 | V     |      |

| Miller Clamping Pin Voltage <sup>b</sup>                    | V <sub>CLAMP</sub> – V <sub>EE2</sub>   | -0.5 | V <sub>CC2</sub> +0.5 | V     | f    |

| Desat Voltage <sup>b</sup>                                  | V <sub>DESAT</sub> – V <sub>EE2</sub>   | -0.5 | V <sub>CC2</sub> +0.5 | V     | g    |

| Soft Shutdown Pin Voltage <sup>b</sup>                      | V <sub>SSD</sub> – V <sub>EE2</sub>     | -0.5 | V <sub>CC2</sub> +0.5 | V     |      |

| Output IC Power Dissipation                                 | Po                                      |      | 600                   | mW    | а    |

| Input IC Power Dissipation                                  | P <sub>I</sub>                          |      | 150                   | mW    | а    |

a. Input IC power dissipation is derated linearly above 10 0°C from 15 0mW to 100 mW at 125 °C for high effective thermal conductivity board. Output IC power dissipation is derated linearly above 100 °C from 600 mW to 350 mW at 125 °C for high effective thermal conductivity board; see Figure 6. For power derating with low effective thermal conductivity board, see Figure 5.

b. Absolute maximum voltage ratings imply transistor off state.

c. Absolute maximum current ratings imply transistor on state.

d. Duration of absolute maximum voltage applied to /UVLO or /Fault pin during the internal MOS turns ON is limited to maximum 10 µs with maximum 5% duty cycle.

- e. Maximum pulse width=1 µs, maximum duty cycle=1%.

- f. When CLAMP pin is turned on, maximum pulse width is limited to 1 µs, maximum duty cycle=2%.

g. Maximum pulse width=5 µs, maximum duty cycle=10%.

#### **Table 7 Recommended Operating Conditions**

| Parameter                            | Symbol               | Min. | Max. | Units | Notes |

|--------------------------------------|----------------------|------|------|-------|-------|

| Operating Temperature                | Τ <sub>Α</sub>       | -40  | 125  | °C    |       |

| Input IC Supply Voltage              | V <sub>CC1</sub>     | 4.5  | 5.5  | V     | а     |

| Total Output IC Supply Voltage       | $V_{CC2} - V_{EE2}$  | 15.2 | 16.8 | V     | b     |

| Input LED Turn on Current            | I <sub>F(ON)</sub>   | 10   | 16   | mA    |       |

| Input LED Turn off Voltage (VAN–VCA) | V <sub>F(OFF)</sub>  | -5.5 | 0.8  | V     |       |

| Maximum PWM Duty Cycle               | D <sub>MAX</sub>     |      | 50   | %     |       |

| Input Pulse Width                    | t <sub>ON(LED)</sub> | 500  |      | ns    |       |

a. In most applications,  $V_{CC1}$  will be powered up first (before  $V_{CC2}$ ) and powered down last (after  $V_{CC2}$ ). This is desirable for maintaining control of the IGBT gate. In applications where  $V_{CC2}$  is powered up first, it is important to ensure that the input remains low until  $V_{CC1}$  reaches the proper operating voltage to avoid any momentary instability at the output during  $V_{CC1}$  ramp-up or ramp-down).

b. 15.2V is the recommended minimum operating supply voltage (V<sub>CC2</sub> - V<sub>EE2</sub>) to ensure adequate margin in excess of the maximum V<sub>UVLO+</sub> threshold of 14.5V.

## **Electrical Specifications**

Unless otherwise specified, all Minimum/Maximum specifications are at recommended operating conditions, all voltages at input IC are referenced to  $V_{EE1}$ , all voltages at output IC are referenced to  $V_{EE2}$ . All typical values at  $T_A = 25$  °C,  $V_{CC1} = 5$  V,  $V_{CC2} - V_{EE2} = 16$  V.

| Parameter                                            | Symbol                              | Min.     | Тур.     | Max.  | Units | Test Conditions             | Fig. | Note |

|------------------------------------------------------|-------------------------------------|----------|----------|-------|-------|-----------------------------|------|------|

| DCDC Flyback Converter                               |                                     |          |          | ł     |       |                             |      |      |

| VCC1 MOS Threshold                                   | V <sub>CC1_MOSTH</sub>              | 0.4      | 1.2      | 1.7   | V     | I <sub>FAULT</sub> = 2.0 mA |      |      |

| VCC1 Turn on Threshold                               | V <sub>CC1_TH</sub>                 | 3.7      | 4.0      | 4.3   | V     |                             |      |      |

| VCC1 Turn on Threshold Hysteresis                    | V <sub>CC1_TH_HYS</sub>             | 0.05     | 0.3      | 0.5   | V     |                             |      |      |

| PWM Switching Frequency                              | f <sub>PWM</sub>                    | 100      | 150      | 190   | kHz   |                             |      | а    |

| Primary Gate Drive Rise Time                         | t <sub>rPGD</sub>                   | 3        | 16       | 40    | ns    | C <sub>PGD</sub> = 1 nF     |      |      |

| Primary Gate Drive Fall Time                         | t <sub>fPGD</sub>                   | 3        | 14       | 40    | ns    | C <sub>PGD</sub> = 1 nF     |      |      |

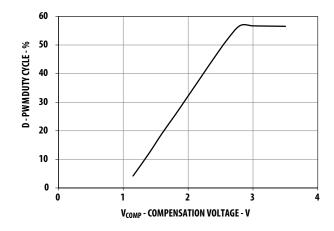

| Maximum PWM Duty Cycle                               | D <sub>MAX</sub>                    | 50       | 55       | 60    | %     |                             | 8    |      |

| Regulated VCC2 Voltage                               | V <sub>CC2</sub> – V <sub>EE2</sub> | 15.2     | 16.0     | 16.8  | V     |                             |      |      |

| VCC2 Over Voltage Protection<br>Threshold            | V <sub>OV_TH</sub>                  | 18.0     | 20.5     | 22.0  | V     |                             |      |      |

| VCC2 Over Voltage Protection<br>Threshold Hysteresis | V <sub>OV_TH_HYS</sub>              | 0.4      | 0.8      | 1.2   | V     |                             |      |      |

| IC Supply Current                                    |                                     |          |          |       |       | 1                           |      |      |

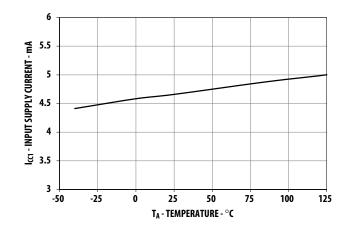

| Input Supply Current                                 | I <sub>CC1</sub>                    |          | 4.7      | 6.2   | mA    | $V_{COMP} = 0V$             | 10   |      |

| Output Supply Current                                | I <sub>CC2</sub>                    | 6.5      | 10.30    | 14.20 | mA    | I <sub>F</sub> =0 mA        | 11   |      |

| Logic Input and Output                               |                                     | <b> </b> | <b>I</b> | !     |       | 4                           | Į    |      |

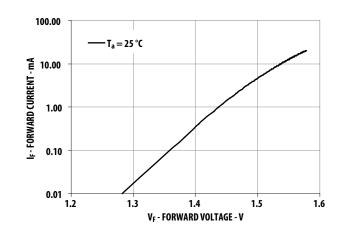

| LED Forward Voltage                                  | V <sub>F</sub>                      | 1.25     | 1.55     | 1.85  | V     | I <sub>F</sub> = 10 mA      | 12   |      |

| LED Reverse Breakdown Voltage                        | V <sub>BR</sub>                     | 6.0      | 11       |       | V     | $I_F = 10 \ \mu A$          |      |      |

| Input Capacitance                                    | C <sub>IN</sub>                     |          | 90       |       | pF    |                             |      | b    |

#### **Table 8 Electrical Specifications**

#### Table 8 Electrical Specifications (Continued)

| Parameter                                           | Symbol                | Min.                  | Тур.                  | Max. | Units | Test Conditions                                                            | Fig.   | Note |

|-----------------------------------------------------|-----------------------|-----------------------|-----------------------|------|-------|----------------------------------------------------------------------------|--------|------|

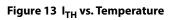

| LED Turn on Current Threshold<br>Low-to-High        | I <sub>TH+</sub>      | 0.5                   | 2.7                   | 7.5  | mA    | V <sub>O</sub> = 5V                                                        | 13     |      |

| LED Turn on Current Threshold<br>High-to-Low        | I <sub>TH-</sub>      | 0.3                   | 2.3                   | 7.0  | mA    | V <sub>O</sub> = 5V                                                        | 13     |      |

| LED Turn on Current Hysteresis                      | I <sub>TH_HYS</sub>   |                       | 0.4                   |      | mA    |                                                                            |        |      |

| /FAULT Logic Low Output Current                     | I <sub>FAULT_L</sub>  | 4                     | 10                    | 20   | mA    | V <sub>FAULT</sub> = 0.4V                                                  |        |      |

| /FAULT Logic High Output Current                    | I <sub>FAULT_H</sub>  |                       | 0.01                  | 2    | μΑ    | V <sub>FAULT</sub> = 5V                                                    |        |      |

| /UVLO Logic Low Output Current                      | I <sub>UVLO_L</sub>   | 4                     | 10                    | 20   | mA    | $V_{UVLO} = 0.4V$                                                          |        |      |

| /UVLO Logic High Output Current                     | IUVLO_H               |                       | 0.01                  | 2    | μΑ    | $V_{UVLO} = 5V$                                                            |        |      |

| Gate Driver                                         |                       |                       |                       |      |       | 1                                                                          |        |      |

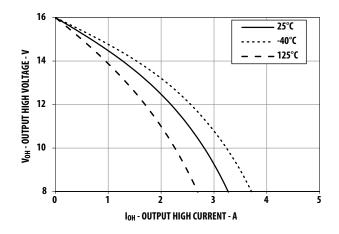

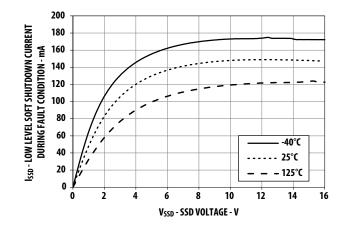

| High Level Output Current                           | I <sub>OH</sub>       |                       | -1.7                  | -0.5 | А     | $V_{O} = V_{CC2} - 3 V$                                                    | 14     |      |

| Low Level Output Current                            | I <sub>OL</sub>       | 0.5                   | 2.4                   |      | A     | $V_0 = V_{EE2} + 2.5V$                                                     | 15     |      |

| High Level Peak Output Current                      | I <sub>OH_PEAK</sub>  |                       |                       | -2   | A     | $V_0 = V_{CC2} - 14V$                                                      |        | c    |

| Low Level Peak Output Current                       | I <sub>OL_PEAK</sub>  | 2                     |                       |      | A     | $V_{O} = V_{EE2} + 14V$                                                    |        | с    |

| High Level Output Voltage                           | V <sub>OH</sub>       | V <sub>CC2</sub> -0.5 | V <sub>CC2</sub> -0.2 |      | V     | I <sub>O</sub> = -100 mA                                                   |        | d, e |

| Low Level Output Voltage                            | V <sub>OL</sub>       |                       | 0.1                   | 0.5  | V     | I <sub>O</sub> = 100 mA                                                    |        |      |

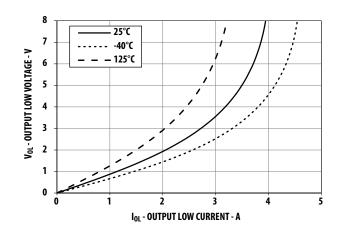

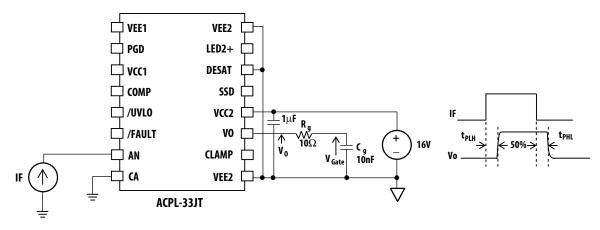

| IF to High Level Output Propagation<br>Delay Time   | t <sub>PLH</sub>      | 50                    | 115                   | 250  | ns    | $Rg = 10\Omega$<br>Cg = 10 nF                                              | 16, 21 | f    |

| IF to Low Level Output Propagation<br>Delay Time    | t <sub>PHL</sub>      | 50                    | 150                   | 300  | ns    | f = 10 kHz<br>Duty Cycle = 50%                                             | 16, 21 | g    |

| Pulse Width Distortion                              | PWD                   | -175                  | 35                    | 230  | ns    | -                                                                          |        | h,i  |

| Dead Time Distortion                                | DTD                   | -230                  | -35                   | 175  | ns    | -                                                                          |        | i j  |

| VO 10% to 90% Rise Time                             | t <sub>R</sub>        | 10                    | 76                    | 280  | ns    | -                                                                          |        |      |

| VO 90% to 10% Fall Time                             | t <sub>F</sub>        | 10                    | 41                    | 280  | ns    | -                                                                          |        |      |

| Output High Level Common Mode<br>Transient Immunity | CM <sub>H</sub>       | 30                    | >50                   |      | kV/s  | T <sub>A</sub> =25°C,<br>I <sub>F</sub> =10 mA,<br>V <sub>CM</sub> = 1500V | 23     | k    |

| Output Low Level Common Mode<br>Transient Immunity  | CM <sub>L</sub>       | 30                    | >50                   |      | kV/s  | $T_A = 25^{\circ}C,$<br>$I_F = 0 \text{ mA},$<br>$V_{CM} = 1500 \text{V}$  | 24     | I    |

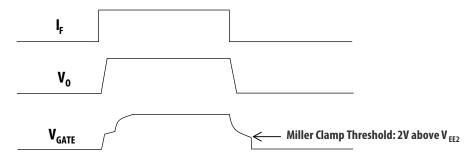

| Active Miller Clamp and Soft Shutdo                 | wn                    |                       |                       |      |       |                                                                            | •      | •    |

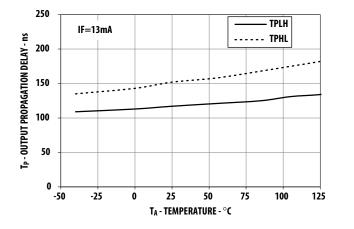

| Low Level SSD Current During Fault<br>Condition     | I <sub>SSDLF</sub>    | 90                    | 150                   | 210  | mA    | $V_{SSD} = 14V$                                                            | 17     |      |

| Clamp Threshold Voltage                             | V <sub>TH_CLAMP</sub> | 1                     | 2.1                   | 3    | V     |                                                                            |        |      |

| Clamp Low Level Sinking Current                     | I <sub>CLAMP</sub>    | 0.5                   | 2                     |      | A     | $V_{CLAMP} = V_{EE2} + 2.5V$                                               |        |      |

| V <sub>CC2</sub> UVLO Protection                    | 1                     | <b>I</b>              | 1                     | 1    |       | 1                                                                          | 1      | 1    |

| V <sub>CC2</sub> UVLO Threshold Low to High         | V <sub>UVLO+</sub>    | 12                    | 13.4                  | 14.5 | V     | V <sub>O</sub> > 5V                                                        |        | e, m |

| V <sub>CC2</sub> UVLO Threshold High to Low         | V <sub>UVLO-</sub>    | 10                    | 11.3                  | 12.5 | V     | V <sub>O</sub> < 5V                                                        |        | e n  |

| V <sub>CC2</sub> UVLO Hysteresis                    | V <sub>UVLO_HYS</sub> | 1.6                   | 2.1                   | 2.4  | V     |                                                                            |        |      |

#### Table 8 Electrical Specifications (Continued)

| Parameter                                         | Symbol                       | Min. | Тур. | Max. | Units | Test Conditions                                    | Fig.   | Note |

|---------------------------------------------------|------------------------------|------|------|------|-------|----------------------------------------------------|--------|------|

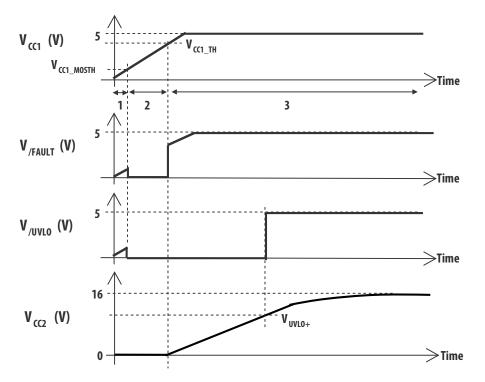

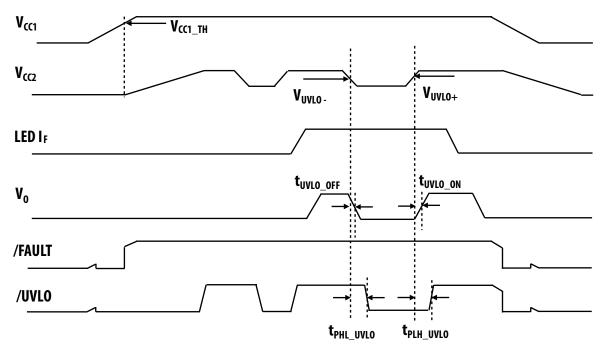

| V <sub>CC2</sub> to UVLO High Delay               | t <sub>PLH_UVLO</sub>        |      | 9    | 20   | μs    |                                                    | 30     | 0    |

| V <sub>CC2</sub> to UVLO Low Delay                | t <sub>PHL_UVLO</sub>        |      | 7    | 20   | μs    |                                                    | 30     | р    |

| V <sub>CC2</sub> UVLO to VOUT High Delay          | t <sub>UVLO_ON</sub>         |      | 5    | 6.5  | μs    |                                                    | 30     | q    |

| V <sub>CC2</sub> UVLO to VOUT Low Delay           | t <sub>UVLO_OFF</sub>        |      | 1.1  | 2    | μs    |                                                    | 30     | r    |

| Desaturation Protection                           | 1                            |      |      |      |       |                                                    |        |      |

| Desat Sensing Threshold                           | V <sub>DESAT</sub>           | 6.65 | 7.0  | 7.35 | V     |                                                    | 18     |      |

| Desat Charging Current                            | I <sub>СНG</sub>             | 0.8  | 1.0  | 1.2  | mA    | V <sub>DESAT</sub> = 0V,<br>V <sub>DESAT</sub> =6V | 19     |      |

| Desat Discharging Current                         | I <sub>DSCHG</sub>           | 19   | 60   | 106  | mA    | V <sub>DESAT</sub> = 7.5V                          | 20     |      |

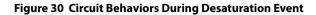

| Desat Blanking Time                               | t <sub>DESAT(BLANKING)</sub> | 0.3  | 0.6  | 0.9  | μs    | RSSD = 0 $\Omega$<br>Cg= 10 nF                     | 30     | s    |

| Desat Sense to 90% VGATE Delay                    | t <sub>DESAT(90%)</sub>      | 0.05 | 0.2  | 0.5  | μs    |                                                    | 22, 30 | t    |

| Desat Sense to 10% VGATE Delay                    | t <sub>DESAT(10%)</sub>      | 0.5  | 1.2  | 2    | μs    |                                                    | 22, 30 | u    |

| Desat to Low Level FAULT Signal Delay             | t <sub>DESAT(FAULT)</sub>    |      | 4.4  | 8    | μs    |                                                    |        | v    |

| Output Mute Time due to Desaturation              | t <sub>DESAT(MUTE)</sub>     | 3    | 7.5  | 12   | ms    |                                                    | 30     | w    |

| Time Input Kept Low Before Fault Reset<br>to High | t <sub>DESAT(RESET)</sub>    | 3    | 7.5  | 12   | ms    |                                                    | 30     | x    |

a. PWM switching frequency of primary gate drive (PGD) is dithered in a range of  $\pm 6\%$  typically over 3.3 ms.

b. C<sub>IN</sub> is measured between pin 7 and pin 8 of the IC.

- c. Maximum pulse width=1 µs, maximum duty cycle=1%.

- d. Maximum pulse width = 1.0 ms, maximum duty cycle = 1%.

- e. Once V<sub>OH</sub> of ACPL-33JT is allowed to go high (V<sub>CC2</sub> V<sub>EE2</sub> > V<sub>UVLO</sub>), the DESAT detection features of the ACPL-33JT will be the primary source of IGBT protection. Once V<sub>CC2</sub> exceeds V<sub>UVLO+</sub> threshold, DESAT will remain functional until V<sub>CC2</sub> is below V<sub>UVLO-</sub> threshold. Thus, the DESAT detection and UVLO features of the ACPL-33JT work in conjunction to ensure constant IGBT protection.

- f. t<sub>PLH</sub> is defined as propagation delay from 50% of LED input I<sub>F</sub> to 50% of High level output.

- g.  $t_{PHL}$  is defined as propagation delay from 50% of LED input I<sub>F</sub> to 50% of Low level output.

- h. Pulse Width Distortion (PWD) is defined as (t<sub>PHL</sub> t<sub>PLH</sub>) of any given unit.

- i. As measured from  $I_F$  to  $V_O$ .

- j. Dead Time Distortion (DTD) is defined as (t<sub>PLH</sub> t<sub>PHL</sub>) between any two ACPL-33JT under the same test conditions.

- k. Common mode transient immunity in the output high state is the maximum tolerable  $dV_{CM}/dt$  of the common mode pulse,  $V_{CM}$ , to ensure that the output remains in the high state (that is,  $V_O > 14V$ ).  $CM_H$  specification is guaranteed by design and not subjected to production test.

- I. Common mode transient immunity in the output low state is the maximum tolerable  $dV_{CM}/dt$  of the common mode pulse,  $V_{CM}$ , to ensure that the output remains in the low state (that is,  $V_O < 2.0V$ ).  $CM_L$  specification is guaranteed by design and not subjected to production test.

- m. This is the "increasing" (that is, turn-on or "positive going" direction) of  $V_{CC2} V_{EE2}$ .

- n. This is the "decreasing" (that is, turn-off or "negative going" direction) of  $V_{CC2} V_{EE2}$ .

- o. The delay time when V<sub>CC2</sub> exceeded UVLO+ threshold to 50% of /UVLO positive going edge.

- p. The delay time when  $V_{CC2}$  exceeded UVLO- threshold to 50% of /UVLO negative going edge.

- q. The delay time when  $V_{CC2}$  exceeded UVLO+ threshold to 50% of High level output.

- r. The delay time when V<sub>CC2</sub> exceeded UVLO- threshold to 50% of Low level output.

- s. The delay time for ACPL-33JT to respond to a DESAT fault condition without any external DESAT capacitor.

- t. The amount of time from when DESAT threshold is exceeded to 90% of V<sub>GATE</sub> at mentioned test conditions.

- u. The amount of time from when DESAT threshold is exceeded to 10% of  $V_{GATE}$  at mentioned test conditions.

- v. The amount of time from when DESAT threshold is exceeded to /Fault output Low 50% of  $V_{CC1}$  voltage.

- w. The amount of time when DESAT threshold is exceeded, Output is mute to LED input.

- x. The amount of time when DESAT Mute time is expired, LED input must be kept Low for Fault status to return to High.

#### **Table 9 Package Characteristics**

| Parameter                  | Symbol           | Min.            | Тур.             | Max. | Units            | Test Conditions                             |

|----------------------------|------------------|-----------------|------------------|------|------------------|---------------------------------------------|

| Input-Output Momentary     |                  |                 |                  |      |                  |                                             |

| Withstand Voltage          | V <sub>ISO</sub> | 5000            |                  |      | V <sub>RMS</sub> | RH < 50%, t = 1 min., T <sub>A</sub> = 25°C |

| Resistance (Input-Output)  | R <sub>I-O</sub> | 10 <sup>9</sup> | 10 <sup>14</sup> |      | Ω                | V <sub>I-O</sub> = 500 Vdc                  |

| Capacitance (Input-Output) | C <sub>I-O</sub> |                 | 0.8              |      | pF               | f = 1 MHz                                   |

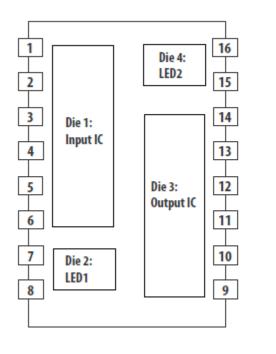

## **Thermal Resistance Model for ACPL-33JT**

The diagram for measurement is shown in Figure 4. This is a multi chip package with four heat sources, the effect of heating of one die due to the adjacent dice are considered by applying the theory of linear superposition. Here, one die is heated first and the temperatures of all the dice are recorded after thermal equilibrium is reached. Then, the second die is heated and all the dice temperatures are recorded and so on until the 4th die is heated. With the known ambient temperature, the die junction temperature and power dissipation, the thermal resistance can be calculated. The thermal resistance calculation can be cast in matrix form. This yields a 4 by 4 matrix for our case of four heat sources.

#### Figure 4 Diagram of ACPL-33JT for Measurement

| R11 | R12 | R13 | R14 |   | P1 |   | ∆T1                      |  |

|-----|-----|-----|-----|---|----|---|--------------------------|--|

| R21 | R22 | R23 | R24 |   | P2 |   | ∆T2                      |  |

| R31 | R32 | R33 | R34 | • | P3 | = | ∆T3                      |  |

| R41 | R42 | R43 | R44 |   | P4 |   | ΔT1<br>ΔT2<br>ΔT3<br>ΔT4 |  |

R<sub>11</sub>: Thermal Resistance of Die1 due to heating of Die1 (C/W) R<sub>12</sub>: Thermal Resistance of Die1 due to heating of Die2 (C/W)) R<sub>13</sub>: Thermal Resistance of Die1 due to heating of Die3 (C/W)) R<sub>14</sub>: Thermal Resistance of Die1 due to heating of Die4 (C/W)) R<sub>21</sub>: Thermal Resistance of Die2 due to heating of Die1 (C/W) R<sub>22</sub>: Thermal Resistance of Die2 due to heating of Die2 (C/W) R<sub>23</sub>: Thermal Resistance of Die2 due to heating of Die3 (C/W) R<sub>24</sub>: Thermal Resistance of Die2 due to heating of Die4 (C/W) R<sub>31</sub>: Thermal Resistance of Die3 due to heating of Die1 (C/W) R<sub>32</sub>: Thermal Resistance of Die3 due to heating of Die2 (C/W) R<sub>33</sub>: Thermal Resistance of Die3 due to heating of Die3 (C/W) R<sub>34</sub>: Thermal Resistance of Die3 due to heating of Die4 (C/W) R<sub>41</sub>: Thermal Resistance of Die4 due to heating of Die1 (C/W) R<sub>42</sub>: Thermal Resistance of Die4 due to heating of Die2 (C/W) R<sub>43</sub>: Thermal Resistance of Die4 due to heating of Die3 (C/W) R<sub>44</sub>: Thermal Resistance of Die4 due to heating of Die4 (C/W)

$\Delta T_1$ : Temperature difference between Die1 junction and ambient (°C)  $\Delta T_2$ : Temperature deference between Die2 junction and ambient (°C)  $\Delta T_3$ : Temperature difference between Die3 junction and ambient (°C)  $\Delta T_4$ : Temperature deference between Die4 junction and ambient (°C)

| $T_1 = (R_{11} \times P_1 + R_{12} \times P_2 + R_{13} \times P_3 + R_{14} \times P_4) + Ta$ (1)             |

|--------------------------------------------------------------------------------------------------------------|

| $T_2 = (R_{21} \times P_1 + R_{22} \times P_2 + R_{23} \times P_3 + R_{24} \times P_4) + Ta$ (2)             |

| $T_{3} = (R_{31} \times P_{1} + R_{32} \times P_{2} + R_{33} \times P_{3} + R_{34} \times P_{4}) + Ta - (3)$ |

| $T_4 = (R_{41} \times P_1 + R_{42} \times P_2 + R_{43} \times P_3 + R_{44} \times P_4) + Ta$ (4)             |

P<sub>1</sub>: Power dissipation of Die1 (W)

P<sub>2</sub>: Power dissipation of Die2 (W)

P3: Power dissipation of Die3 (W)

P<sub>4</sub>: Power dissipation of Die4 (W)

T<sub>1</sub>: Junction temperature of Die1 due to heat from all dice (0 °C) T<sub>2</sub>: Junction temperature of Die2 due to heat from all dice (0 °C) T<sub>3</sub>: Junction temperature of Die3 due to heat from all dice (0 °C) T<sub>4</sub>: Junction temperature of Die4 due to heat from all dice (0 °C)

Ta: Ambient temperature (°C)

Measurement is done on low effective thermal conductivity board according to JEDEC Standard 51-3 and on high effective thermal conductivity board according to JEDEC Standard 51-7.

#### Table 10 Test Boards

| Test Board                                | Test Board<br>Conditions                                                                                                                                                       | Thermal Resistance                                                                                                                                                                                                                                             | Power Dissipation Derating Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low effective thermal conductivity board  | Single layer board for<br>signal<br>Outer layer: 2 oz.<br>copper thickness                                                                                                     | R11 = 138°C/W<br>R12 = 87°C/W<br>R13 = 67°C/W<br>R14 = 87°C/W<br>R21 = 89°C/W<br>R22 = 241°C/W<br>R23 = 81°C/W<br>R34 = 95°C/W<br>R32 = 92°C/W<br>R35 = 117°C/W<br>R41 = 86°C/W<br>R42 = 96°C/W<br>R43 = 111°C/W<br>R44 = 225°C/W                              | Figure 5 PowerDerating Chart Using Low Effective Thermal<br>Conductivity Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| High effective thermal conductivity board | 4-layer board that<br>embodies two signal<br>layers, a power plane<br>and a ground plane<br>Outer layers: 2 oz.<br>copper thickness<br>Inner layers: 1 oz.<br>copper thickness | R11 = 78°C/W<br>R12 = 34°C/W<br>R13 = 23°C/W<br>R14 = 29°C/W<br>R21 = 37°C/W<br>R22 = 165°C/W<br>R23 = 32°C/W<br>R31 = 24°C/W<br>R31 = 24°C/W<br>R33 = 59°C/W<br>R33 = 59°C/W<br>R41 = 32°C/W<br>R41 = 32°C/W<br>R42 = 34°C/W<br>R43 = 51°C/WR<br>A4 = 136°C/W | <ul> <li>NOTE</li> <li>Input IC power dissipation is derated linearly above 65°C from 150 mW to 60 mW at 125°C.</li> <li>Output IC power dissipation is derated linearly above 65°C from 600 mW to 150 mW at 125°C.</li> <li>Figure 6 Power Derating Chart Using High Effective Thermal Conductivity Board</li> <li>700</li> <li>600</li> <li>90</li> <li>90<!--</td--></li></ul> |

## **Notes on Thermal Calculation**

Application and environmental design for ACPL-33JT needs to ensure that the junction temperature of the internal ICs and LED within the gate driver optocoupler do not exceed 150°C. The following equations calculate the maximum power dissipation and corresponding effect on junction temperatures and can only be used as a reference for thermal performance comparison under specified PCB layout as shown above. The thermal resistance model shown here is not meant to and will not predict the performance of a package in an application-specific environment.

## Calculation of Input IC Power Dissipation, P<sub>1</sub>

Input IC Power Dissipation  $(P_1) = P_{I(Static)} + P_{I(PGD)}$

where

$P_{I(Static)}$  – Static power dissipated by the input IC =  $I_{CC1} \times V_{CC1}$

$P_{I(PGD)} - Switching power dissipated in the PGD pin = (V_{CC1} \times Q_{G\_ExtMOS} \times f_{PWM\_DCDC)} \times R_{O(MAX)} / (R_{O(MAX)} + R_{G\_PGD}) \times R_{O(MAX)} / (R_{O(MAX)} + R_{O(MAX)} + R_{O(MAX)} / (R_{O(MAX)} + R_{O(MAX)} + R_{O(MAX)} )$

$Q_{G\_ExtMOS}$  – Gate charge of external MOSFET connected to PGD pin at supply voltage

f<sub>PWM DCDC</sub> – DC-DC switching frequency

$R_{O(MAX)}$  – Maximum PGD pin output impedance = 0.3V / 50 mA = 6

$R_{G\ PGD}$  – Gate resistance connected to PGD pin

Example:

$$\begin{split} & \mathsf{P}_{\mathsf{I}(\mathsf{Static})} = 6 \text{ mA} \times 5.5 \text{ V} = 33 \text{ mW} \\ & \mathsf{PI}_{(\mathsf{PGD})} = (5.5 \text{V} \times 5 \text{ nC} \times 190 \text{ kHz}) \times 6\Omega \text{ / } (6\Omega + 10\Omega) = 1.96 \text{ mW} \\ & \mathsf{P}_1 = 33 \text{ mW} + 1.96 \text{ mW} = 34.96 \text{ mW} \end{split}$$

## Calculation of Input LED Power Dissipation, P<sub>2</sub>

Input LED Power Dissipation (P<sub>2</sub>) = IF(LED) (Recommended Max.) ×  $V_{F(LED)}$  (at 125°C) × Duty Cycle

Example:

$P_2 = 16 \text{ mA} \times 1.25 \text{V} \times 50\% \text{ duty cycle} = 10 \text{ mW}$

## Calculation of Output IC Power Dissipation, P<sub>3</sub>

Output IC Power Dissipation  $(P_3) = P_{O(Static)} + P_{HS} + P_{LS}$

where

$P_{O(Static)}$  – Static power dissipated by the output IC =  $I_{CC2} \times V_{CC2}$

$P_{HS}$  – High side switching power dissipation at  $V_O$  pin = ( $V_{CC2} \times Q_G \times f_{PWM}$ ) ×  $R_{OH(MAX)}$  / ( $R_{OH(MAX)}$  +  $R_{GH}$ ) / 2

$P_{LS}$  - Low side switching power dissipation at  $V_O$  pin = ( $V_{CC2} \times Q_G \times f_{PWM}$ ) ×  $R_{OL(MAX)}$  / ( $R_{OL(MAX)}$  +  $R_{GL}$ ) / 2

Q<sub>G</sub> – IGBT gate charge at supply voltage

f<sub>PWM</sub> – Input LED switching frequency

$R_{OH(MAX)}$  – Maximum high side output impedance – ( $V_{CC2}$  –  $V_{OH(MIN)}$ ) /  $I_{OH(MIN)}$

R<sub>GH</sub> – Gate charging resistance

$R_{OL(MAX)}$  – Maximum low side output impedance –  $V_{OL(MAX)}$  /  $I_{OL(MIN)}$

R<sub>GL</sub> – Gate discharging resistance

Example:

$$\begin{split} &\mathsf{R}_{OH(MAX)} = (\mathsf{V}_{CC2} - \mathsf{V}_{OH(MIN)}) \ / \ \mathsf{I}_{OH(MIN)} = 3.0 \mathsf{V} \ / \ 0.5 \mathsf{A} = 6.0 \Omega \\ &\mathsf{R}_{OL(MAX)} = \mathsf{V}_{OL(MAX)} \ / \ \mathsf{I}_{OH(MIN)} = 2.5 \mathsf{V} \ / \ 0.5 \mathsf{A} = 5.0 \Omega \\ &\mathsf{P}_{HS} = (16\mathsf{V} \times 1\mu\mathsf{C} \times 10 \ \mathsf{kHz}) \times 6.0 \Omega \ / \ (6.0 \Omega + 10 \Omega) \ / \ 2 = 30 \ \mathsf{mW} \\ &\mathsf{P}_{LS} = (16\mathsf{V} \times 1\ \mu\mathsf{C} \times 10 \ \mathsf{kHz}) \times 5.0 \Omega \ / \ (5.0 \Omega + 10 \Omega) \ / \ 2 = 26.7 \ \mathsf{mW} \\ &\mathsf{P}_3 = 14.2 \ \mathsf{mA} \times 16\mathsf{V} + 30 \ \mathsf{mW} + 26.7 \ \mathsf{mW} = 283.9 \ \mathsf{mW} \end{split}$$

## Calculation of LED2 Power Dissipation, P<sub>4</sub>

LED2 Power Dissipation (P<sub>4</sub>) = I<sub>F(LED2)</sub> (Design Max.) × V<sub>F(LED2)</sub> (at 125°C) × Duty Cycle

Example:

$P_4 = 16 \text{ mA} \times 1.25 \text{V} \times 50\% \text{ duty cycle} = 10 \text{ mW}$

Calculation of Junction Temperature for High Effective Thermal Conductivity Board:

Input IC Junction Temperature =  $(78^{\circ}C/W \times P_1 + 34^{\circ}C/W \times P_2 + 23^{\circ}C/W \times P_3 + 29^{\circ}C/W \times P_4) + Ta$ Input LED Junction Temperature =  $(37^{\circ}C/W \times P_1 + 165^{\circ}C/W \times P_2 + 32^{\circ}C/W \times P_3 + 31^{\circ}C/W \times P_4) + Ta$ Output IC Junction Temperature =  $(24^{\circ}C/W \times P_1 + 33^{\circ}C/W \times P_2 + 59^{\circ}C/W \times P_3 + 48^{\circ}C/W \times P_4) + Ta$ LED2 Junction Temperature =  $(32^{\circ}C/W \times P_1 + 34^{\circ}C/W \times P_2 + 51^{\circ}C/W \times P_3 + 136^{\circ}C/W \times P_4) + Ta$

## **Printed Circuit Board Layout Considerations**

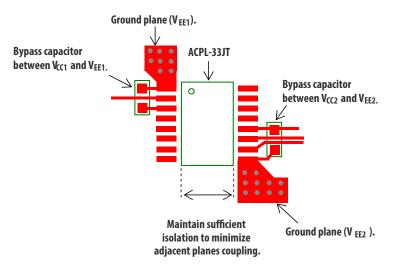

Care must be taken while designing the layout of printed circuit board (PCB) for optimum performance.

Adequate spacing should always be maintained between the high voltage isolated circuitry and any input referenced circuitry. The same minimum spacing between two adjacent high-side isolated regions of the printed circuit board must be maintained as well. Insufficient spacing will reduce the effective isolation and increase parasitic coupling that will degrade CMR performance.

The placement and routing of supply bypass capacitors requires special attention. During switching transients, the majority of the gate charge is supplied by the bypass capacitors. Maintaining short bypass capacitor trace lengths will ensure low supply ripple and clean switching waveforms.

Bypass capacitors should be placed closely in between these pins:  $V_{CC1}$  (pin 3) to  $V_{EE1}$  (pin 1) and  $V_{CC2}$  (pin 12) to  $V_{EE2}$  (pin 9). Ground plane connections are necessary for  $V_{EE1}$  and  $V_{EE2}$  in order to achieve maximum power as the ACPL-33JT is designed to dissipate the majority of heat generated through these pins. Actual power dissipation will depend on the application environment (PCB layout, airflow, part placement, and so on).

#### Figure 7 PCB Layout Considerations

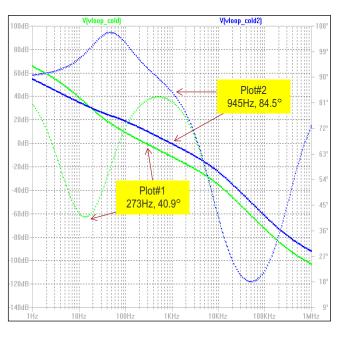

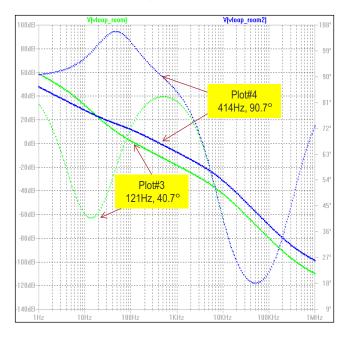

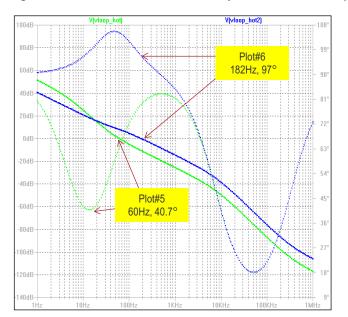

# **Typical Performance Plots** Figure 8 PWM Duty Cycle vs. V<sub>COMP</sub>

Figure 10 I<sub>CC1</sub> vs. Temperature

Figure 12 I<sub>F</sub> vs. V<sub>F</sub>

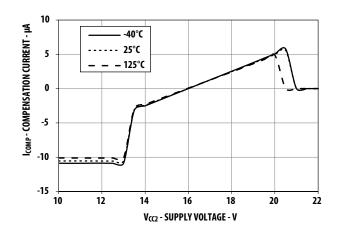

Figure 9 I<sub>COMP</sub> vs. Supply Voltage

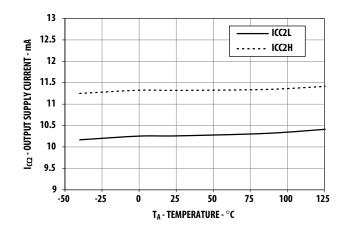

Figure 11 I<sub>CC2</sub> vs. Temperature

## Figure 14 V<sub>OH</sub> vs. I<sub>OH</sub>

Figure 15 V<sub>OL</sub> vs. I<sub>OL</sub>

Figure 16 T<sub>P</sub> vs. Temperature

Figure 17 I<sub>SSD</sub> vs. V<sub>SSD</sub>

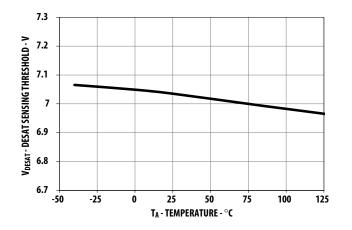

#### Figure 18 V<sub>DESAT</sub> Threshold vs. Temperature

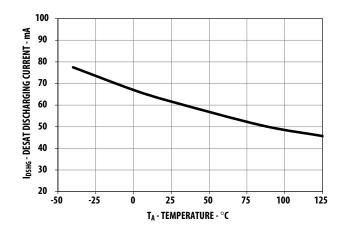

Figure 20 I<sub>DSCHG</sub> vs. Temperature

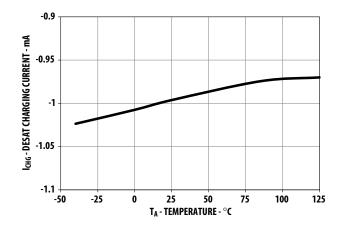

Figure 19 I<sub>CHG</sub> vs. Temperature

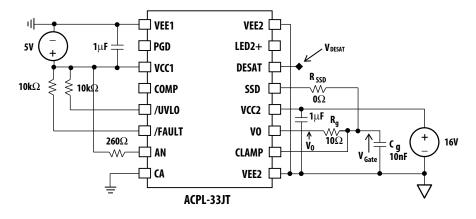

#### Figure 21 Propagation Delay Test Circuit

Figure 22  $t_{DESAT}(90\%)$  and  $t_{DESAT}(10\%)$  Test Circuit

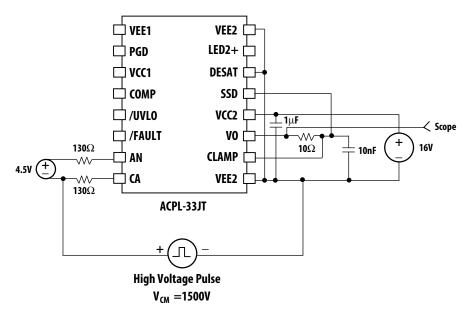

#### Figure 23 CMR V<sub>O</sub> High Test Circuit

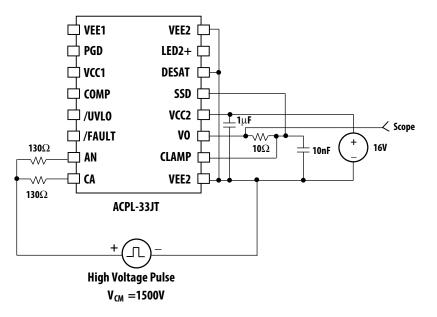

Figure 24 CMR V<sub>O</sub> Low Test Circuit

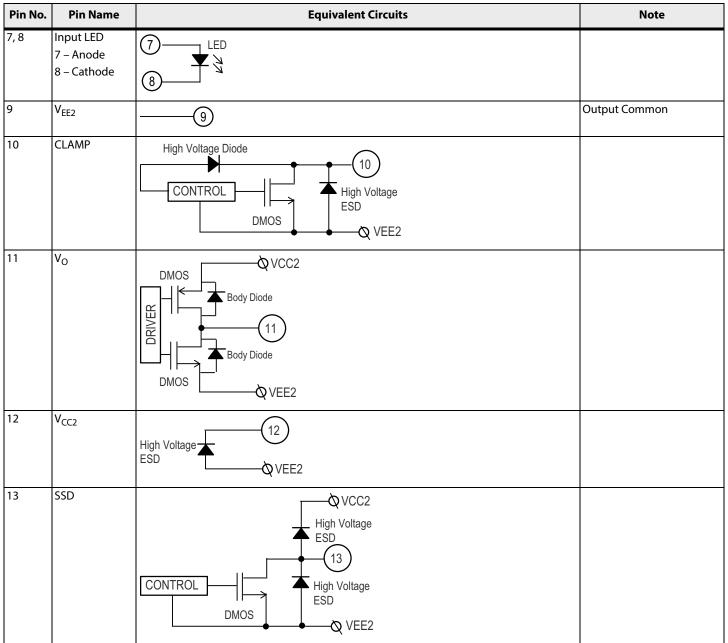

#### Table 11 Internal Connection Equivalent Circuits

| Pin No. | Pin Name         | Equivalent Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Note             |

|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 1       | V <sub>EE1</sub> | ①▶                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Input Common/GND |

| 2       | PGD              | VCC1<br>5V ESD<br>5V MOS<br>5V ESD<br>5V MOS<br>5V MOS<br>5V MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |

| 3       | V <sub>CC1</sub> | 3<br>5V ESD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |

| 4       | COMP             | Image: style | 5                |

| 5       | /UVLO            | 5V ESD 5V MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |

| 6       | /FAULT           | SV ESD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |

#### Table 11 Internal Connection Equivalent Circuits (Continued)

| Pin No. | Pin Name         | Equivalent Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Note          |

|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 14      | DESAT            | VBIAS - CONTROL - High Voltage<br>VBIAS - CONTROL - High Voltage<br>ESD<br>High Voltage<br>ESD<br>WBIAS - CONTROL - High Voltage<br>ESD<br>WBIAS - CONTROL - CON |               |

| 15      | LED2+            | VBIAS DMOS<br>VBIAS DMOS<br>RES<br>15<br>LED<br>5V MOS<br>SV MOS<br>SV ESD<br>Ø VEE2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |

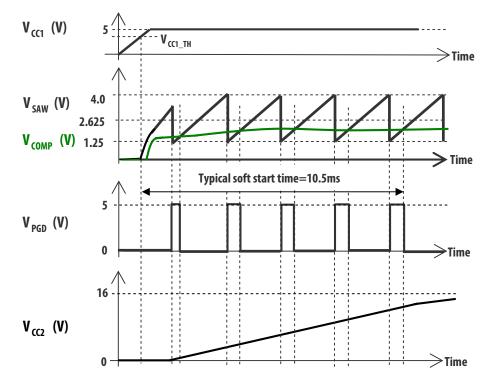

| 16      | V <sub>EE2</sub> | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output Common |