# ACPL-C87AT/ACPL-C87BT Automotive High Precision DC Voltage Isolation Sensor

### Description

The Broadcom<sup>®</sup> ACPL-C87AT/C87BT isolation sensors utilize superior optical coupling technology, with sigma-delta  $(\Sigma - \Delta)$  analog-to-digital converter, chopper stabilized amplifiers, and a fully differential circuit topology to provide unequaled isolation-mode noise rejection, low offset, high gain accuracy and stability.

ACPL-C87AT (±1% gain tolerance) and ACPL-C87BT (±0.5% gain tolerance) are designed for high precision DC voltage sensing in electronic motor drives, DC/DC and AC/DC converter and battery monitoring system. The ACPL-C87AT/C87BT features high input impedance and operate with full span of analog input voltage up to 2.46V. The shutdown feature provides power saving and can be controlled from external source, such as microprocessor.

The high common-mode transient immunity (15 kV/ $\mu$ s) of the ACPL-C87AT/C87BT maintains the precision and stability needed to accurately monitor DC rail voltage in high noise motor control environments. This galvanic safe isolation solution is delivered in a compact, surface mount stretched SO-8 (SSO-8) package that meets worldwide regulatory safety standards.

Broadcom R<sup>2</sup>Coupler<sup>®</sup> isolation products provide the reinforced insulation and reliability needed for critical automotive and high temperature industrial applications.

### Features

- Unity gain

- ± 0.5% (ACPL-C87BT) and ± 1% (ACPL-C87AT) gain tolerance @ 25°C

- –0.3 mV Input offset voltage

- 0.05% non linearity

- 25 ppm/°C gain drift vs. temperature

- 100 kHz bandwidth

- 0 to 2V nominal input range

- Qualified to AEC-Q100 Grade 1 test guidelines

- Operating temperature: -40°C to +125°C

- Shutdown feature (active high)

- 15 kV/µs common-mode rejection at V<sub>CM</sub> = 1 kV

- Working voltage, V<sub>IORM</sub> = 1414 V<sub>peak</sub>

- Compact, surface mount stretched SO8 package

- Worldwide safety approval:

- UL 1577 (5000 V<sub>RMS</sub>/1 minute)

- CSA

- IEC/EN/DIN EN 60747-5-5

### **Applications**

- Automotive BMS battery pack voltage sensing

- Automotive DC/DC converter voltage sensing

- Automotive motor inverter DC bus voltage sensing

- Automotive AC/DC (charger) DC output voltage sensing

- Isolation interface for temperature sensing

- General-purpose voltage sensing and monitoring

**CAUTION!** Take normal static precautions in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

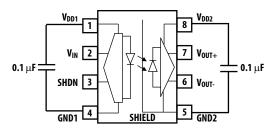

## **Functional Diagram**

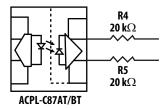

Figure 1: Functional Diagram

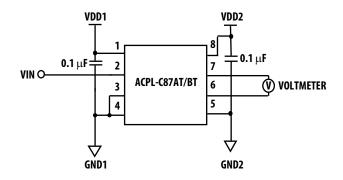

A 0.1-µF bypass capacitor must be connected between pin 1 and pin 4, and pin 5 and pin 8 as shown.

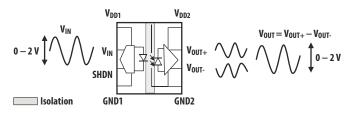

### Figure 2: Functional Diagram 2

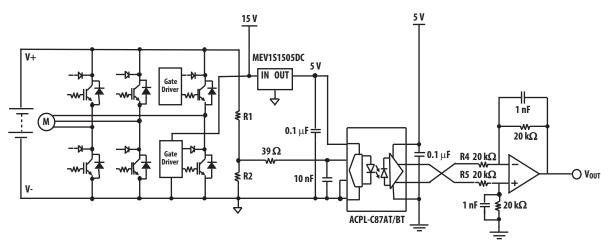

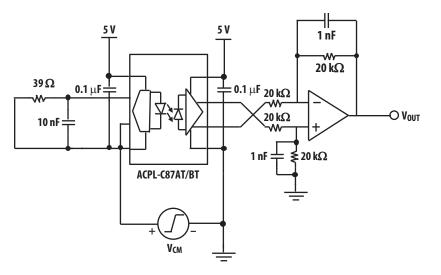

Figure 3: Typical Voltage Sensing Circuit

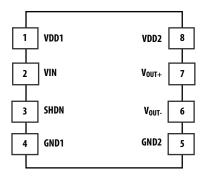

#### Figure 4: Package Pinout

## **Pin Description**

| Pin Number | Pin Name        | Description                                                                                  | Pin Number | Pin Name          | Description             |

|------------|-----------------|----------------------------------------------------------------------------------------------|------------|-------------------|-------------------------|

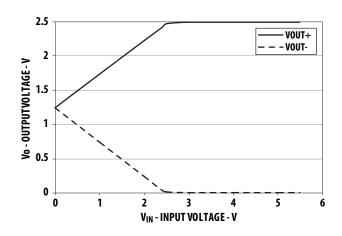

| 1          | DDT             | Input power supply<br>When $V_{DD1} = 0$ , then $V_{OUT+} = 0V$ , $V_{OUT-} = 2.6V$          | 8          | $V_{DD2}$         | Output power supply     |

| 2          | V <sub>IN</sub> | Voltage input, full scale range = 2.46V                                                      | 7          | V <sub>OUT+</sub> | Positive output voltage |

| 3          |                 | Shutdown (active high)<br>When active, then V <sub>OUT+</sub> = 0V, V <sub>OUT-</sub> = 2.6V | 6          | V <sub>OUT-</sub> | Negative output voltage |

| 4          | GND1            | Input side ground                                                                            | 5          | GND2              | Output side ground      |

## **Ordering Information**

|             | Option              |           |                  |               |                                               |                            |               |

|-------------|---------------------|-----------|------------------|---------------|-----------------------------------------------|----------------------------|---------------|

| Part Number | (RoHS<br>Compliant) | Package   | Surface<br>Mount | Tape and Reel | UL 5000 V <sub>rms</sub> /<br>1 Minute rating | IEC/EN/DIN<br>EN 60747-5-5 | Quantity      |

| ACPL-C87AT  | -000E               | Stretched | Х                |               | Х                                             | Х                          | 80 per tube   |

| ACPL-C87BT  | -500E               | SO-8      | Х                | Х             | Х                                             | Х                          | 1000 per reel |

To order, choose a part number from the part number column and combine with the desired option from the option column to form an order entry.

### Example:

ACPL-C87AT-500E to order product of SSO-8 Surface Mount package in Tape and Reel packaging with RoHS compliant. Contact your Broadcom sales representative or authorized distributor for information.

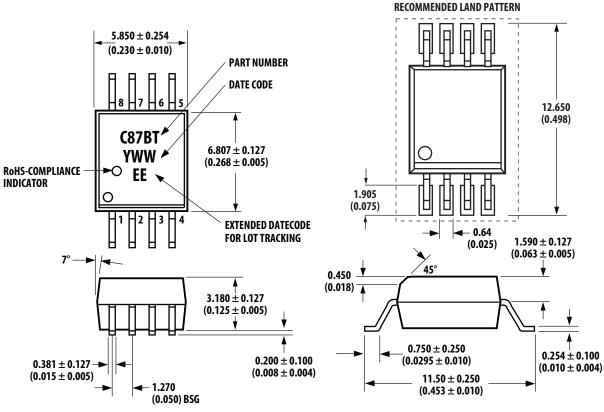

# Package Outline Drawing (Stretched SO8)

### Figure 5: Package Outline Drawing

Dimensions in millimeters and (inches).

Note: Lead coplanarity = 0.1 mm (0.004 inches). Floating lead protrusion = 0.25mm (10mils) max.

## **Recommended Pb-Free IR Profile**

Recommended reflow condition as per JEDEC Standard, J-STD-020 (latest revision).

NOTE: Use non-halide flux.

# **Regulatory Information**

The ACPL-C87AT and ACPL-C87BT are approved by the following organizations.

| UL                                        | CSA                          | IEC/EN/DIN EN 60747-5-5 |

|-------------------------------------------|------------------------------|-------------------------|

| UL 1577, component recognition program up | Approved under CSA Component | IEC 60747-5-5           |

| to V <sub>ISO</sub> = 5kV <sub>RMS</sub>  | Acceptance Notice #5.        | EN 60747-5-5            |

|                                           |                              | DIN EN 60747-5-5        |

# **IEC/EN/DIN EN 60747-5-5 Insulation Characteristics**

| Description                                                                                                             | Symbol                |                   | Units             |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------|-------------------|

| Installation classification per DIN VDE 0110/1.89, Table 1                                                              |                       |                   |                   |

| for rated mains voltage ≤ 150 V <sub>rms</sub>                                                                          |                       | I – IV            |                   |

| for rated mains voltage ≤ 300 V <sub>rms</sub>                                                                          |                       | I – IV            |                   |

| for rated mains voltage ≤ 450 V <sub>rms</sub>                                                                          |                       | I – IV            |                   |

| for rated mains voltage ≤ 600 V <sub>rms</sub>                                                                          |                       | I – IV            |                   |

| for rated mains voltage ≤ 1000 V <sub>rms</sub>                                                                         |                       | I — III           |                   |

| Climatic Classification                                                                                                 |                       | 40/125/21         |                   |

| Pollution Degree (DIN VDE 0110/1.89)                                                                                    |                       | 2                 |                   |

| Maximum Working Insulation Voltage                                                                                      | V <sub>IORM</sub>     | 1414              | V <sub>peak</sub> |

| Input to Output Test Voltage, Method b                                                                                  | V <sub>PR</sub>       | 2651              | V <sub>peak</sub> |

| $V_{\rm IORM}$ × 1.875 = $V_{\rm PR},$ 100% Production Test with $t_{\rm m}$ = 1 sec, Partial discharge < 5 pC          |                       |                   |                   |

| Input to Output Test Voltage, Method a                                                                                  | V <sub>PR</sub>       | 2262              | V <sub>peak</sub> |

| V <sub>IORM</sub> × 1.6 = V <sub>PR</sub> , Type and Sample Test with t <sub>m</sub> = 10 sec, Partial discharge < 5 pC |                       |                   |                   |

| Highest Allowable Overvoltage (Transient Overvoltage t <sub>ini</sub> = 60 sec)                                         | V <sub>IOTM</sub>     | 8000              | V <sub>peak</sub> |

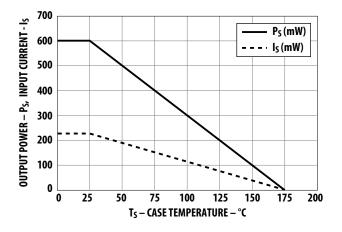

| Safety-limiting values – maximum values allowed in the event of a failure, also see Figure 6.                           |                       |                   |                   |

| Case Temperature                                                                                                        | Τ <sub>S</sub>        | 175               | °C                |

| Input Current                                                                                                           | I <sub>S,INPUT</sub>  | 230               | mA                |

| Output Power                                                                                                            | P <sub>S,OUTPUT</sub> | 600               | mW                |

| Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500V                                                        | R <sub>S</sub>        | > 10 <sup>9</sup> | Ω                 |

#### Figure 6: Dependence of Safety-Limiting Values on Temperature

# Insulation and Safety-Related Specifications

| Parameter                                            | Symbol | Value | Units | Conditions                                                                                                                               |

|------------------------------------------------------|--------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| Minimum External Air Gap<br>(External Clearance)     | L(101) | 8.0   | mm    | Measured from input terminals to output terminals, shortest distance through air.                                                        |

| Minimum External Tracking<br>(External Creepage)     | L(102) | 8.0   | mm    | Measured from input terminals to output terminals, shortest distance path along body.                                                    |

| Minimum Internal Plastic Gap<br>(Internal Clearance) |        | 0.5   | mm    | Through insulation distance conductor to conductor,<br>usually the straight line distance thickness between the<br>emitter and detector. |

| Tracking Resistance<br>(Comparative Tracking Index)  | CTI    | > 175 | Volts | DIN IEC 112/VDE 0303 Part 1                                                                                                              |

| Isolation Group (DIN BDE0109)                        |        | Illa  |       | Material Group (DIN VDE 0110)                                                                                                            |

## **Absolute Maximum Ratings**

| Parameter                     | Symbol                                | Min. | Max.                   | Units | Note |

|-------------------------------|---------------------------------------|------|------------------------|-------|------|

| Storage Temperature           | T <sub>S</sub>                        | -55  | 150                    | °C    |      |

| Ambient Operating Temperature | T <sub>A</sub>                        | -40  | 125                    | °C    |      |

| Supply Voltages               | V <sub>DD1</sub> , V <sub>DD2</sub>   | -0.5 | 6.0                    | Volts |      |

| Input Voltage                 | V <sub>IN</sub>                       | -2.0 | V <sub>DD1</sub> + 0.5 | Volts |      |

| Shutdown Voltage              | V <sub>SD</sub>                       | -0.5 | V <sub>DD1</sub> + 0.5 | Volts |      |

| Output Voltages               | V <sub>OUT+</sub> , V <sub>OUT-</sub> | -0.5 | V <sub>DD2</sub> + 0.5 | Volts |      |

# **Recommended Operating Conditions**

| Parameter                     | Symbol           | Min.                   | Max.             | Units | Notes |

|-------------------------------|------------------|------------------------|------------------|-------|-------|

| Ambient Operating Temperature | T <sub>A</sub>   | -40                    | 125              | °C    |       |

| Input Supply Voltage          | V <sub>DD1</sub> | 4.5                    | 5.5              | Volts |       |

| Output Supply Voltage         | V <sub>DD2</sub> | 3.0                    | 5.5              | Volts |       |

| Input Voltage                 | V <sub>IN</sub>  | 0                      | 2.0              | Volts |       |

| Shutdown Voltage              | V <sub>SD</sub>  | V <sub>DD1</sub> - 0.5 | V <sub>DD1</sub> | Volts |       |

## **Electrical Specifications**

Unless otherwise noted, all typical values at  $T_A = 25^{\circ}$ C,  $V_{DD1} = V_{DD2} = 5$ V,  $V_{IN} = 0$  to 2V,  $V_{SD} = 0$ V; all Minimum/Maximum specifications are at recommended voltage supply conditions: 4.5V  $\leq V_{DD1} \leq 5.5$ V, 4.5V  $\leq V_{DD2} \leq 5.5$ V.

| Parameter                                        | Symbol                            | Min.  | Тур.                    | Max.  | Units  | Test Conditions                                                                                | Figure   | Note |

|--------------------------------------------------|-----------------------------------|-------|-------------------------|-------|--------|------------------------------------------------------------------------------------------------|----------|------|

| Power Supplies                                   | L                                 | I     |                         |       | 1      |                                                                                                | 1        |      |

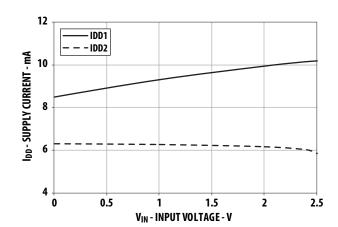

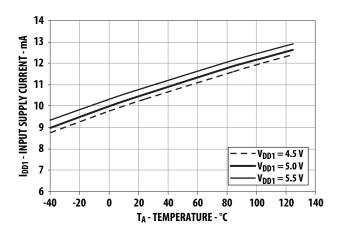

| Input Supply Current                             | I <sub>DD1</sub>                  | _     | 10.5                    | 15    | mA     | V <sub>SD</sub> = 0V                                                                           | 18, 19   |      |

| Input Supply Current<br>(Shutdown Mode)          | I <sub>DD1(SD)</sub>              | _     | 20                      | —     | μA     | V <sub>SD</sub> = 5V                                                                           |          |      |

| Output Supply Current                            | I <sub>DD2</sub>                  | _     | 6.5                     | 12    | mA     |                                                                                                | 18, 20   |      |

| DC Characteristics                               | L                                 | I     |                         |       | 4      |                                                                                                | 1 1      |      |

| Gain (ACPL-C87BT, ± 0.5%)                        | G0                                | 0.995 | 1                       | 1.005 | V/V    | $T_A = 25^{\circ}C, V_{IN} = 0 \text{ to } 2 \text{ V},$<br>$V_{DD1} = V_{DD2} = 5.0 \text{V}$ | 8        | а    |

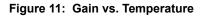

| Gain (ACPL-C87AT, ± 1%)                          | G1                                | 0.99  | 1                       | 1.01  | V/V    | $T_A = 25^{\circ}C, V_{IN} = 0 \text{ to } 2 \text{ V},$<br>$V_{DD1} = V_{DD2} = 5.0 \text{V}$ | 8, 11    | а    |

| Magnitude of Gain Change vs.<br>Temperature      | dG/dT <sub>A</sub>                | _     | 25                      | —     | ppm/°C | $T_A = -40^{\circ}C$ to $+125^{\circ}C$                                                        | 11       |      |

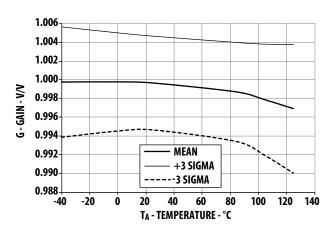

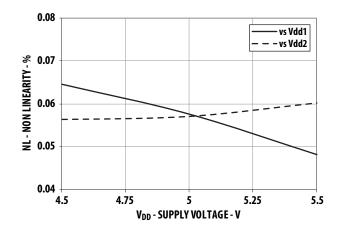

| Magnitude of Gain Change vs.<br>V <sub>DD1</sub> | dG/dV <sub>DD1</sub>              |       | 0.05                    | _     | %/V    | T <sub>A</sub> = 25°C                                                                          | 12       |      |

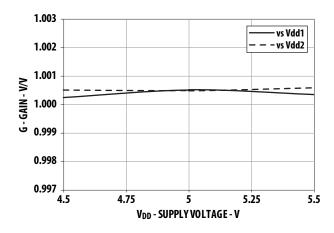

| Magnitude of Gain Change vs.<br>V <sub>DD2</sub> | dG/dV <sub>DD2</sub>              | _     | 0.02                    | _     | %/V    | T <sub>A</sub> = 25 °C                                                                         | 12, 13   |      |

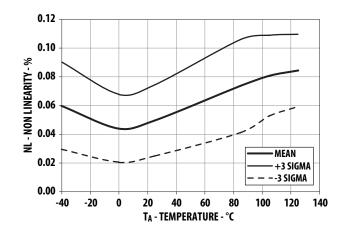

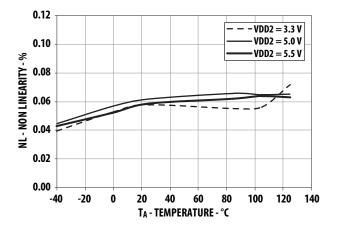

| Nonlinearity                                     | NL                                |       | 0.05                    | 0.12  | %      | V <sub>IN</sub> = 0 to 2V,<br>T <sub>A</sub> = –40°C to +125°C                                 | 15, 16   |      |

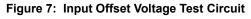

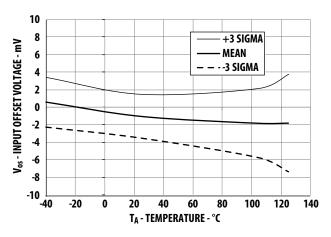

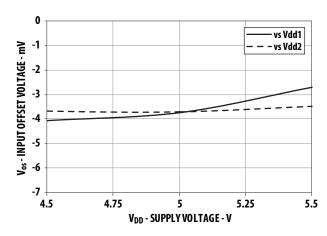

| Input Offset Voltage                             | V <sub>OS</sub>                   | -10   | -0.3                    | 10    | mV     | V <sub>IN</sub> is shorted to GND1,<br>T <sub>A</sub> = 25°C                                   | 7, 9, 10 |      |

| Magnitude of Input Offset Change vs. Temperature | dV <sub>OS</sub> /dT <sub>A</sub> |       | 21                      | —     | µV/°C  | V <sub>IN</sub> is shorted to GND1,<br>T <sub>A</sub> = –40°C to +125°C                        | 7, 9     |      |

| Inputs and Outputs                               | L                                 | I     |                         |       | 1      |                                                                                                | 1        |      |

| Full-Scale Differential Voltage Input Range      | FSR                               |       | 2.46                    | _     | V      | Referenced to GND1                                                                             |          |      |

| Input Bias Current                               | I <sub>IN</sub>                   | -0.1  | -0.001                  | 0.1   | μA     | V <sub>IN</sub> = 0V                                                                           | 22       |      |

| Equivalent Input Impedance                       | R <sub>IN</sub>                   | —     | 1000                    | —     | MΩ     |                                                                                                | 22       |      |

| Output Common-Mode Voltage                       | V <sub>OCM</sub>                  |       | 1.23                    | —     | V      | V <sub>IN</sub> = 0V, V <sub>SD</sub> = 0V                                                     |          |      |

| VOUT+ Range                                      | V <sub>OUT+</sub>                 | _     | V <sub>OCM</sub> +1.23  | —     | V      | V <sub>IN</sub> = 2.5V                                                                         |          |      |

| VOUT - Range                                     | V <sub>OUT-</sub>                 | _     | V <sub>OCM</sub> – 1.23 |       | V      | V <sub>IN</sub> = 2.5V                                                                         |          |      |

| Output Short-Circuit Current                     | I <sub>OSC</sub>                  |       | 30                      | _     | mA     | V <sub>OUT+</sub> or V <sub>OUT-</sub> ,<br>shorted to GND2 or V <sub>DD2</sub>                |          |      |

| Output Resistance                                | R <sub>OUT</sub>                  |       | 36                      | _     | Ω      | V <sub>IN</sub> = 0V                                                                           |          |      |

a. Gain is defined as the slope of the best-fit line of differential output voltage (V<sub>OUT+</sub> – V<sub>OUT-</sub>) versus input voltage over the nominal range, with offset error adjusted. A 0.5% gain tolerance for ACPL-C87BT, and a 1% tolerance for ACPL-C87AT.

# **Electrical Specifications (Continued)**

Unless otherwise noted, all typical values at  $T_A = 25$ °C,  $V_{DD1} = V_{DD2} = 5$ V,  $V_{IN} = 0$  to 2V,  $V_{SD} = 0$ V; all Minimum/Maximum specifications are at recommended voltage supply conditions: 4.5V  $\leq V_{DD1} \leq 5.5$ V, 4.5V  $\leq V_{DD2} \leq 5.5$ V.

| Parameter                                      | Symbol             | Min. | Тур. | Max. | Unit              | Test Conditions                                                                | Figure | Note |

|------------------------------------------------|--------------------|------|------|------|-------------------|--------------------------------------------------------------------------------|--------|------|

| AC Characteristics                             |                    |      |      |      |                   |                                                                                |        |      |

| Small-Signal Bandwidth (–3 dB)                 | f <sub>–3 dB</sub> | _    | 100  |      | kHz               |                                                                                |        |      |

| V <sub>OUT</sub> Noise                         | N <sub>OUT</sub>   | —    | 1.3  | _    | mV <sub>RMS</sub> | V <sub>IN</sub> = 2V; BW = 1 kHz                                               | 23     | а    |

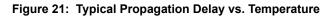

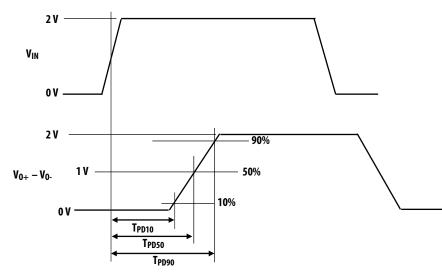

| Input to Output Propagation Delay (10% to 10%) | t <sub>PD10</sub>  | —    | 2.2  | 3.5  | μs                | V <sub>IN</sub> = 0 to 2V Step                                                 | 21, 26 |      |

| Input to Output Propagation Delay (50% to 50%) | t <sub>PD50</sub>  | —    | 3.7  | 6.0  | μs                | V <sub>IN</sub> = 0 to 2V Step                                                 | 21, 26 |      |

| Input to Output Propagation Delay (90% to 90%) | t <sub>PD90</sub>  | —    | 5.3  | 7.0  | μs                | V <sub>IN</sub> = 0 to 2V Step                                                 | 21, 26 |      |

| Output Rise/Fall Time<br>(10% to 90%)          | t <sub>R/F</sub>   | —    | 2.7  | 4.0  | μs                | Step Input                                                                     |        |      |

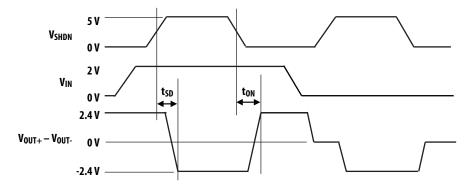

| Shutdown Time                                  | t <sub>SD</sub>    | _    | 25   | _    | μs                |                                                                                | 25     |      |

| Shutdown Recovery Time                         | t <sub>ON</sub>    | _    | 150  | _    | μs                |                                                                                | 25     |      |

| Power Supply Rejection                         | PSR                | _    | -78  | _    | dB                | 1 Vp-p, 1 kHz sine wave<br>ripple on V <sub>DD1</sub> , differential<br>output |        |      |

| Common Mode Transient Immunity                 | CMTI               | 10   | 15   | _    | kV/μs             | V <sub>CM</sub> = 1 kV, T <sub>A</sub> = 25°C                                  | 24     | b    |

a. Noise is measured at the output of the differential to single ended post amplifier.

b. Common mode transient immunity (CMTI) is tested by applying a fast rising/falling voltage pulse across GND1 (pin 4) and GND2 (pin 5). The output glitch observed is less than 0.2V from the average output voltage for less than 1 μs.

# **Package Characteristics**

Unless otherwise noted, all typical values are at  $T_A = 25^{\circ}C$ ; all Minimum/Maximum specifications are at Recommended Operating Conditions.

| Parameter                                             | Symbol           | Min. | Тур.             | Max. | Units            | Test Conditions                                  | Figure | Note |

|-------------------------------------------------------|------------------|------|------------------|------|------------------|--------------------------------------------------|--------|------|

| Input-Output Momentary Withstand Voltage <sup>a</sup> | V <sub>ISO</sub> | 5000 | _                | —    | V <sub>RMS</sub> | RH < 50%, t = 1 minute,<br>T <sub>A</sub> = 25°C |        | b, c |

| Input-Output Resistance                               | R <sub>I-O</sub> | _    | 10 <sup>14</sup> |      | Ω                | V <sub>I-O</sub> = 500 V <sub>DC</sub>           |        | b    |

| Input-Output Capacitance                              | C <sub>I-O</sub> | —    | 0.5              | _    | pF               | f =1 MHz                                         |        | b    |

a. The Input-Output Momentary Withstand Voltage is a dielectric voltage rating that should not be interpreted as an input-output continuous voltage rating.

b. Device considered a two terminal device: pins 1, 2, 3, and 4 shorted together, and pins 5, 6, 7, and 8 shorted together.

c. In accordance with UL 1577, each optocoupler is proof tested by applying an insulation test voltage  $\ge$  6000 V<sub>RMS</sub> for 1 second.

# **Typical Characteristic Plots and Test Conditions**

All  $\pm 3\sigma$  plots are based on characterization test result at the point of product release. For guaranteed specification, refer to the respective Electrical Specifications section.

Figure 9: Input Offset Voltage vs. Temperature

### Figure 8: Gain and Nonlinearity Test Circuit

Figure 12: Gain vs. Supply Voltage

Figure 13: Gain vs Temperature at Different V<sub>DD2</sub>

Figure 15: Nonlinearity vs. Temperature

Figure 14: Nonlinearity vs. Supply Voltage

Figure 16: Nonlinearity vs. Temperature at Different V<sub>DD2</sub>

Figure 18: Typical Supply Current vs. Input Voltage

# Figure 19: Typical Input Supply Current vs. Temperature at Different $V_{\text{DD1}}$

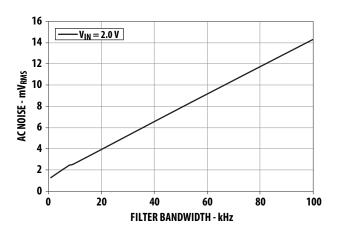

Figure 23: AC Noise vs. Filter Bandwidth

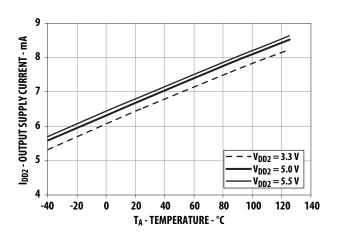

Figure 20: Typical Output Supply Current vs. Temperature at Different  $V_{DD2}$

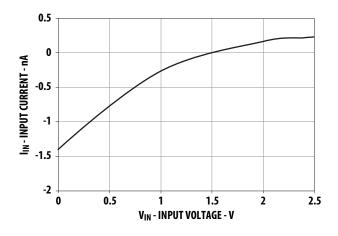

Figure 22: Input Current vs. Input Voltage

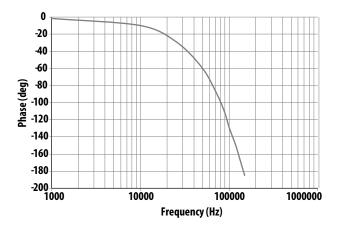

Figure 24: Phase vs. Frequency

#### Figure 25: Common Mode Transient Immunity Test Circuit

### Figure 26: Shutdown Timing Diagram

## **Application Information**

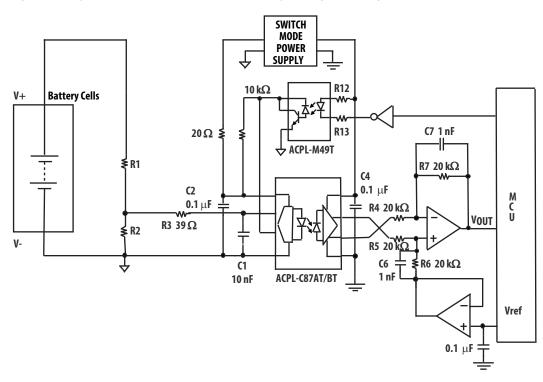

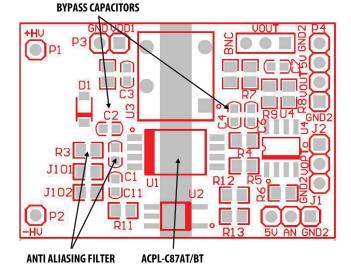

The circuit shown in the Figure 28 is a high voltage sensing application using ACPL-C87AT/BT (isolation amplifier) and ACPL-M49T (optocoupler). The high voltage input is sensed by the precision voltage divider resistors R1 and sensing resistor R2. The ratio of the voltage divider is determined by the allowable input range of the isolation amplifier (0 to 2 V). This small analog input goes through a  $39\Omega$  and 10 nF anti aliasing filter (ACPL-C87AT/BT use  $\Sigma$ - $\Delta$  modulation).

Inside the isolation amplifier: the analog input signal is digitized and optically transmitted to the output side of the amplifier. The detector will then decode the signal and converted back to analog signal. The output differential signals of ACPL-C87AT/BT go through an op-amp to convert the differential signals to a single ended output.

Figure 28: Typical Application Circuit for Battery Voltage Sensing

## **Bypass Capacitor**

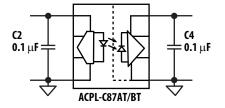

A 0.1-µF bypass capacitor must be connected as near as possible between V<sub>DD1</sub> to GND1 and V<sub>DD2</sub> to GND2 (Figure 29).

Figure 29: Bypass Capacitors C2, C4

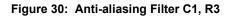

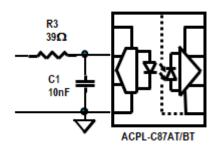

## **Anti-aliasing Filter**

A 39 $\Omega$  resistor and a 10-nF capacitor are recommended to be connected to the input (V<sub>IN</sub>) as anti-aliasing filter because ACPL-C87AT/BT uses sigma data modulation (Figure 30). The value of the capacitor must be greater than 1 nF and bandwidth must be less than 410 kHz.

Figure 31: Loading Resistors R4, F5

## **Designing the Input Resistor Divider**

- 1. Choose the sensing current (Isense) for bus voltage; for example, 1 mA.

- 2. Determine R2,

$R_2 = \frac{Voltage input range}{I_{SENSE}} = \frac{2 V}{1 mA} = 2 k\Omega$

3. Determine R1 using voltage divider formula:

$$(V + - V -) \bullet \frac{R_2}{R_1 + R_2} = Voltage input range, or$$

$$R_1 = \frac{(V + - V -) \bullet R_2}{Voltage input range} - R_2$$

where (V + - V -) is the high voltage input; for example, 0 to 600V,

$$R_{1} = \frac{(600 \text{ V} - 0 \text{ V}) \bullet 2 \text{ k}\Omega}{2 \text{ V}} - 2 \text{ k}\Omega = 598 \text{ k}\Omega$$

To reduce the voltage stress of a sole resistor, R1 can be a series of several resistors.

## **Post Amplifier Circuit**

The output of ACPL-C87AT/BT is a differential output  $(V_{OUT+} \text{ and } V_{OUT-} \text{ pins})$ . A post amplifier circuit is needed to convert the differential output to single ended output with a reference ground. The post amplifier circuit can also be configured to establish a desired gain if needed. It also functions as filter to high frequency chopper noise. The bandwidth can be adjusted by changing the feedback resistor and capacitor (R7 and C7). Adjusting this bandwidth to a minimum level helps minimize the output noise.

Post op-amp resistive loading (R4, R5) should be equal or greater than 20 k $\Omega$  (Figure 31). Resistor values lower than this can affect the overall system error due to output impedance of isolation amplifier.

The application circuit in Figure 28 features two op-amps to improve the linearity at voltage near 0V caused by the limited headroom of the amplifier. The second op-amp can set the reference voltage to above 0V.

## **Shutdown Function**

ACPL-C87AT/BT has a shutdown function to disable the device and make the output ( $V_{OUT+} - V_{OUT-}$ ) low. A voltage of 5V on SHDN pin will shutdown the device producing an output ( $V_{OUT+} - V_{OUT-}$ ) of –2.6V. To be able to control the SHDN function (example, from microprocessor), an optocoupler (ACPL-M49T) is used.

## **Total System Error**

Total system error is the sum of the resistor divider error, isolation amplifier error and post amplifier error. The resistor divider error is due to the accuracy of the resistors used. It is recommended to use high accuracy resistor of 0.1%. Post amplifier error is due to the resistor matching and the voltage offset characteristic which can be found on the supplier data sheet.

Isolation Amplifier Error is shown in the following table.

### **Isolation Amplifier Error Calculation**

|   |                                                        |         | 3σ Distribution or<br>Specification <sup>a</sup> |            |                                                        |        |

|---|--------------------------------------------------------|---------|--------------------------------------------------|------------|--------------------------------------------------------|--------|

|   |                                                        | Typical | ACPL-C87AT                                       | ACPL-C87BT |                                                        | Figure |

| A | Error due to offset voltage (25°C)                     | 0.015%  | 0.5%                                             | 0.5%       | Offset Voltage /Recommended input voltage range (2.0V) | specs  |

| В | Error due to offset voltage drift (across temperature) | 0.1%    | 0.4%                                             | 0.4%       | Offset Voltage /Recommended input voltage range (2.0V) |        |

| С | Error due to gain tolerance (25°C)                     | 0%      | 1%                                               | 0.5%       |                                                        | specs  |

| D | Error due to gain drift (across temperature)           | 0.25%   | 0.8%                                             | 0.8%       |                                                        |        |

| Е | Error due to Nonlinearity (across temperature)         | 0.05%   | 0.12%                                            | 0.12%      |                                                        |        |

| F | Total uncalibrated error (A+B+C+D+E)                   | 0.415%  | 2.82%                                            | 2.32%      |                                                        | specs  |

| G | Total offset calibrated error (F – A)                  | 0.4%    | 2.32%                                            | 1.82%      |                                                        |        |

| Н | Total gain and offset calibrated error (G – C)         | 0.4%    | 1.32%                                            | 1.32%      |                                                        |        |

a.  $3\sigma$  distribution is based on corner wafers.

## **PCB Layout Recommendations**

Bypass capacitor C2 and C4 must be located close to ACPL-C87xT Pins 1 and Pin 8 respectively. Grounded pins of C4 and C5 can be connected by vias through the respective ground layers. If the design has multiple layers, a dedicated layer for ground is recommended for flexibility in component placement.

Anti aliasing filters R3 and C1 also need to be connected as close as possible to Pin 2 of ACPL-C87AT/BT. See Figure 32 for actual component placement of the anti-aliasing filter and bypass capacitors.

#### Figure 32: Component Placement Recommendation

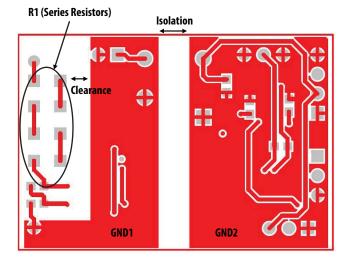

GND1 and GND2 must be totally isolated in the PCB layout (Figure 33). Distance of separation depends on the high voltage level of the equipment. The higher the voltage level, the larger the distance of separation needed. Designers can refer to specific IEC standard of their equipment for the creepage/clearance requirements.

R1, which is directly connected to the high voltage input, must have sufficient clearance with the low voltage components. Clearance depends on the high voltage level of the input. Designers can refer to specific IEC standards of their equipment for the clearance requirements.

#### Figure 33: Bottom Layer Layout Recommendation

Broadcom, the pulse logo, Connecting everything, Avago Technologies, Avago, the A logo, and R<sup>2</sup>Coupler are among the trademarks of Broadcom and/or its affiliates in the United States, certain other countries, and/or the EU.

Copyright © 2013–2018 Broadcom. All Rights Reserved.

The term "Broadcom" refers to Broadcom Inc. and/or its subsidiaries. For more information, please visit www.broadcom.com.

Broadcom reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design. Information furnished by Broadcom is believed to be accurate and reliable. However, Broadcom does not assume any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Optically Isolated Amplifiers category:

Click to view products by Broadcom manufacturer:

Other Similar products are found below :

TLP7920

LIA130S

ACPL-C79A-500E

ACPL-C797-500E

TLP7930(D4-TP1,F

TLP7920(D4-A,F

TLP7920(B.F(O

LIA130

ACPL-C790

500E

ACPL-782T-500E

ACPL-790B-000E

ACPL-C78A-000E

ACPL-C87BT-500E

HCPL-7510-300E

HCPL-7520-300E

HCPL-7520-500E

HCPL-788J-500E

ACPL-7970-000E

ACPL-C784-500E

ACPL-C79B-500E

ACPL-C79A-000E

ACPL-C87A-500E

ACPL-C87B-500E

HCPL-7520-000E

HCPL-7800-000E

HCPL-7800A-000E

HCPL-7840-000E

HCPL-7800-300E

HCPL-7800A-300E

HCPL-7800A-500E

HCPL-7800-500E

ACPL-7970-500E

HCPL-7840-300E

HCPL-7840-300E

HCPL-7800A-500E

HCPL-7800-500E

ACPL-7970-500E

HCPL-7840-300E

HCPL-7840-300E

C87H-500E

TLP7920(D4,F

TLP7830(TP4,E

ACPL-C780-000E

ACPL-C78A-500E

HCPL-78A-500E