### **AEIC-7272-S16**

Quad Differential Line Driver Separate Logic Bias and Driver Bias With Tri-State Outputs

# AVAGO

## **Data Sheet**

#### **Description**

These line drivers are pin compatible with 26LS31 in applications where pin 4 = 5V and pin 12 = GND. Internal clamp diodes allow trouble-free operation when driving cable lengths exceeding 100m. Split supplies are provided to minimize standby power dissipation in high voltage applications. The logic should be powered from a regulated 5V supply at the VccBias pin. The output stages may then be powered by a separate supply at VccDrivers, up to 30V. Output voltage swings of 0.3V to VCC-1.9V are typical. The outputs are protected against shorts to ground, shorts to Vcc and to other outputs, by a two-fold scheme of current limiting and thermal shutdown. This assures highly reliable operation in harsh environments.

This part is available in 16L SOIC (Pb-free) package.

## **Applications**

- Encoders

- Industrial controls

#### **Features**

- Supply (Bias) Voltage Range 3.5 V to 30 V

- Operation to 800 KHz

- CMOS and TTL Compatible Inputs

- Separate logic bias and driver supply pins

- Optional single supply operation for moderate power applications

- High Impedance Buffered Inputs with hysteresis

- Tri-State outputs

- 80 mA peak SINK/SOURCE current

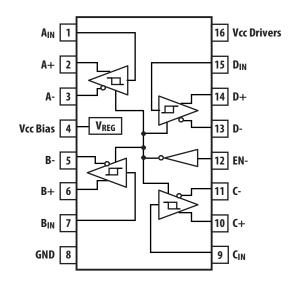

#### **Pin Assignment**

**Table 1. Absolute Maximum Ratings**

| Parameters                    | Symbol         | Min. | Max. | Units | Test Conditions |

|-------------------------------|----------------|------|------|-------|-----------------|

| Operating Temperature Range   | T <sub>A</sub> | -55  | 125  | °C    |                 |

| Supply (Driver) Voltage Range | $V_{CCD}$      | 4.5  | 30   | V     |                 |

#### **Table 2. Electrical Characteristics**

Unless otherwise specified,  $T_A = 25^{\circ}$  C and EN- < 0.8 V.

| Parameters                                 | Symbol            | Min. | Тур. | Max. | Units | Test Conditions                                           |

|--------------------------------------------|-------------------|------|------|------|-------|-----------------------------------------------------------|

| Overtemp Operate Point (junction)          | T <sub>JOP</sub>  | -    | 172  | -    | °C    | Note 1                                                    |

| Overtemp Release Point (junction)          | $T_{JRP}$         | -    | 136  | -    | °C    | Note 1                                                    |

| Vcc Bias Voltage Range                     | V <sub>CCB</sub>  | 3.5  | 5    | 30   | V     |                                                           |

| Vcc Drivers Voltage Range                  | V <sub>CCD</sub>  | 4.5  | 5    | 30   | V     |                                                           |

| Supply Current V <sub>CCB1</sub> (BIAS)    | I <sub>CCB1</sub> | -    | 11.9 | 16.0 | mA    | $V_{CCB}$ and $V_{CCD} = 5 V$                             |

| Supply Current V <sub>CCD1</sub> (DRIVERS) | I <sub>CCD1</sub> | -    | 2.4  | 3.3  | mA    | $V_{CCB}$ and $V_{CCD} = 5 V$                             |

| Supply Current V <sub>CCB2</sub>           | I <sub>CCB2</sub> | -    | 2.5  | 3.4  | mA    | $V_{CCB}$ and $V_{CCD} = 5 \text{ V, EN-} > 2 \text{ V}$  |

| Supply Current V <sub>CCD2</sub>           | I <sub>CCD2</sub> | -    | 0.0  | 0.1  | mA    | $V_{CCB}$ and $V_{CCD} = 5 \text{ V, EN-} > 2 \text{ V}$  |

| Supply Current V <sub>CCB3</sub>           | I <sub>CCB3</sub> | -    | 12.1 | 18.5 | mA    | $V_{CCB}$ and $V_{CCD} = 30 \text{ V}$                    |

| Supply Current V <sub>CCD3</sub>           | I <sub>CCD3</sub> | -    | 2.4  | 3.3  | mA    | $V_{CCB}$ and $V_{CCD} = 30 \text{ V}$                    |

| Supply Current V <sub>CCB4</sub>           | I <sub>CCB4</sub> | -    | 2.6  | 3.5  | mA    | $V_{CCB}$ and $V_{CCD} = 30 \text{ V, EN-} > 2 \text{ V}$ |

| Supply Current V <sub>CCD4</sub>           | I <sub>CCD4</sub> | -    | 0.0  | 0.1  | mA    | $V_{CCB}$ and $V_{CCD} = 30 \text{ V, EN-} > 2 \text{ V}$ |

| Enable Input Threshold                     | V <sub>THE</sub>  | 0.8  | 1.5  | 2    | V     |                                                           |

| Enable Low Level Input Current             | I <sub>ILE</sub>  | -10  | 0    | 10   | μΑ    | $V_{IN} = 0 \text{ V}, V_{CCB} = 5 \text{ V}$             |

| Enable High Level Input Current            | I <sub>IHE</sub>  | _    | 108  | 150  | μΑ    | $V_{IN} = 5 \text{ V}, V_{CCB} = 5 \text{ V}$             |

| High Impedance Output Leakage              | I <sub>OZ</sub>   | -4.0 | 0.0  | 4.0  | μΑ    | V <sub>CCD</sub> = 30 V, EN- > 2 V,<br>Output at 15 V     |

| Input Positive-Going Threshold             | V <sub>T+</sub>   | 1.05 | 1.25 | 1.45 | V     | $V_{CCB} = 5 V$                                           |

| Input Negative-Going Threshold             | V <sub>T</sub> -  | 0.75 | 0.95 | 1.15 | V     | $V_{CCB} = 5 V$                                           |

| Input Hysteresis                           | V <sub>H</sub>    | _    | 0.3  | -    | V     | $V_{CCB} = 5 V$                                           |

| Low Level Input Current                    | I <sub>IL</sub>   | -4.0 | -0.1 | -    | μΑ    | $V_{IN} = 0 \text{ V}, V_{CCB} = 5 \text{ V}$             |

| High Level Input Current                   | I <sub>IH</sub>   | -    | 0    | 4.0  | μΑ    | $V_{IN} = 5 \text{ V}, V_{CCB} = 5 \text{ V}$             |

| Low Level Output1                          | V <sub>OL1</sub>  | -    | 375  | 500  | mV    | $I_{OL} = 20 \text{ mA}, V_{CCD} = 5 \text{ V}$           |

| Low Level Output2                          | V <sub>OL2</sub>  | -    | 370  | 500  | mV    | $I_{OL} = 20 \text{ mA}, V_{CCD} = 30 \text{ V}$          |

| High Level Output1                         | V <sub>OH1</sub>  | 2.4  | 2.8  | -    | V     | $I_{OH} = -20 \text{ mA}, V_{CCD} = 5 \text{ V}$          |

| High Level Output2                         | V <sub>OH2</sub>  | 27.7 | 28.1 | -    | V     | $I_{OH} = -20 \text{ mA}, V_{CCD} = 30 \text{ V}$         |

Note:

## **Table 3. AC Switching Characteristics**

Values given at  $V_{CCD} = 5 \text{ V}$ ,  $V_{CCD} = 24 \text{ V}$ ,  $T_A = 25^{\circ} \text{ C}$ ,  $C_L = 1000 \text{ pF}$  on all outputs, and EN- < 0.8 V.

| Parameters                                                                          | Symbol           | Min. | Тур. | Max. | Units | <b>Test Conditions</b> |

|-------------------------------------------------------------------------------------|------------------|------|------|------|-------|------------------------|

| Propagation delay, rising input 50% point to zero crossing of differential outputs  | T <sub>PLH</sub> | -    | 450  | 630  | ns    | See above.             |

| Propagation delay, falling input 50% point to zero crossing of differential outputs | T <sub>PHL</sub> | -    | 450  | 630  | ns    | See above.             |

| Output Rise Time                                                                    | T <sub>R</sub>   | -    | 700  | 980  | ns    | See above.             |

| Output Fall Time                                                                    | T <sub>F</sub>   | -    | 700  | 980  | ns    | See above.             |

<sup>1.</sup> This is not a test parameter, but for information only.

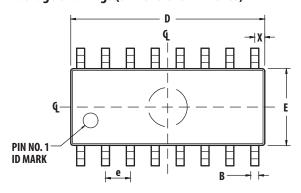

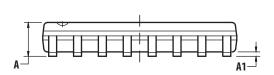

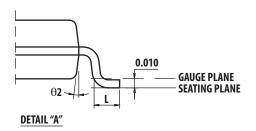

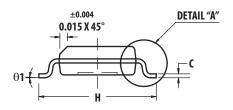

## **Package Drawings (Dimensions in Inches)**

|        | 16 SOIC   |        |  |  |  |

|--------|-----------|--------|--|--|--|

| Symbol | Min       | Max    |  |  |  |

| Α      | 0.054     | 0.068  |  |  |  |

| A1     | 0.004     | 0.0098 |  |  |  |

| В      | 0.014     | 0.019  |  |  |  |

| D      | 0.386     | 0.393  |  |  |  |

| Е      | 0.150     | 0.157  |  |  |  |

| Н      | 0.229     | 0.244  |  |  |  |

| е      | 0.050 BSC |        |  |  |  |

| С      | 0.0075    | 0.0098 |  |  |  |

| L      | 0.016     | 0.034  |  |  |  |

| Х      | 0.020 REF |        |  |  |  |

| θ1     | 0°        | 8°     |  |  |  |

| θ2     | 7° BSC    |        |  |  |  |

#### Notes:

- 1. Lead coplanarity should be o to 0.004" max.

- Package surface finishing: VD1 24~27 (Dual).

Package surface finishing: VD1 13~15 (16L Soic(NB) Matrix).

- 3. All dimension excluding mold flashes.

- 4. The lead width, B to be determined at 0.0075" from the lead tip.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Buffers & Line Drivers category:

Click to view products by Broadcom manufacturer:

Other Similar products are found below:

Le87401NQC Le87402MQC 028192B 042140C 051117G 070519XB NL17SZ07P5T5G NLU1GT126AMUTCG 74AUP1G17FW5-7

74LVC2G17FW4-7 CD4502BE 5962-8982101PA 5962-9052201PA 74LVC1G125FW4-7 NL17SH17P5T5G NL17SH125P5T5G

NLV37WZ07USG RHRXH162244K1 74AUP1G34FW5-7 74AUP1G07FW5-7 74LVC2G126RA3-7 NLX2G17CMUTCG

74LVCE1G125FZ4-7 Le87501NQC 74AUP1G126FW5-7 TC74HC4050AP(F) 74LVCE1G07FZ4-7 NLX3G16DMUTCG

NLX2G06AMUTCG NLVVHC1G50DFT2G NLU2G17AMUTCG LE87100NQC LE87290YQC LE87290YQCT LE87511NQC

LE87511NQCT LE87557NQC LE87557NQCT LE87614MQC LE87614MQCT 74AUP1G125FW5-7 NLU2G16CMUTCG

MC74LCX244MN2TWG