#

# BCM53134S

# **Multiport Ultra Low-Power Gigabit Ethernet Switch**

### **General Description**

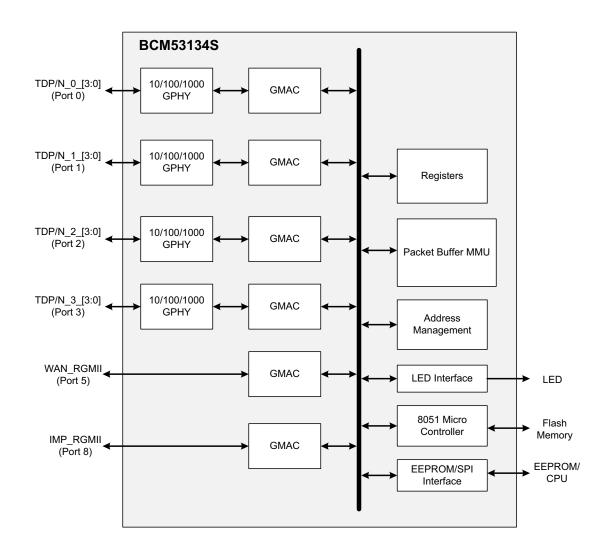

The Broadcom<sup>®</sup> BCM53134S is an ultra low-power, highly integrated, cost-effective smart Gigabit switch. The switch design is based on the field-proven, industry-leading ROBO architecture. This device combines all the functions of a high-speed switch system including packet buffers, PHY transceivers, media access controllers (MACs), address management, port-based rate control, and a nonblocking switch fabric into a single 28 nm CMOS device. Designed to be fully compliant with the IEEE 802.3 and IEEE 802.3x specifications, including the MAC-control PAUSE frame, the BCM53134S provides compatibility with all industry-standard Ethernet, Fast Ethernet, and Gigabit Ethernet (GbE) devices.

The BCM53134S has a rich feature set suitable for not only standard GbE connectivity for broadband home gateways, desktop, and laptop PCs, but also for next-generation gaming consoles, set-top boxes, networked DVD players, and home theater receivers. It is also specifically designed for next generation SOHO/SMB routers and gateways.

The BCM53134S contains four full-duplex 10/100/ 1000BASE-T Ethernet transceivers. In addition, the BCM53134S has two PHY-less interfaces for the CPU or a router chip, providing flexible 10/100/1000 Mb/s connectivity. One RGMII interface can be connected to a CPU entity and configured as an IMP (In-Band Management port).

The second RGMII interface is available for another PHY, modem, or CPU connection.

The BCM53134S provides 70+ on-chip MIB counters to collect receive and transmit statistics for each port.

#### Features

- Six 10/100/1000 media access controllers

- Four-port 10/100/1000 transceivers for TX

- One RGMII interface for an IMP for connection to a CPU/management entity without PHY

- One RGMII interface for a connection to another PHY, CPU, or modem

- IEEE 802.1p, MAC Port, TOS, and DiffServ QoS for six queues, plus two time-sensitive queues

- Port-based VLAN

- IEEE 802.1Q-based VLAN with 4K entries

- MAC-based trunking with automatic link failover

- Port-based rate control

- Port mirroring (Ingress/Egress)

- Supports IPv4 and IPv6

- Priority modification on egress

- BroadSync<sup>®</sup> HD for IEEE 802.1AS support

- Timestamp tagging at MAC interface

- Time-aware egress scheduler

- DOS attack prevention

- IGMP Snooping, MLD snooping support

- Spanning tree support (multiple spanning trees-up to eight)

- Embedded CPU (8051) processor for cable diagnostics

- CableChecker<sup>™</sup> with unmanaged mode support

- Double tagging/QinQ

- IEEE 802.az Energy Efficient Ethernet (EEE) support

- IEEE 802.3x programmable per-port flow control and backpressure, with IEEE 802.1X support for secure user authentication

- EEPROM, MDC/MDIO, and SPI Interface.

- Serial Flash Interface for accessing embedded CPU (8051)

- 4K entry MAC address table with automatic learning and aging

- 128 KB packet buffer (1 KB = 1024 bytes)

- 128 multicast group support

### **Features (Continued)**

- Jumbo frame support up to 9720 bytes

- 1.0V for core and 3.3V for I/O

#### Figure 1: Functional Block Diagram

- RGMII with option of 3.3V/2.5V or 1.8V/1.5V

- JTAG support

- 212-pin FBGA package

# **Table of Contents**

| Chap | pter 1: Introduction                               | 8  |

|------|----------------------------------------------------|----|

| 1.1  | 1 Overview                                         | 8  |

| 1.2  | 2 Audience                                         | 9  |

| 1.3  | 3 Data Sheet Information                           | 9  |

| Chap | pter 2: Features and Operation                     |    |

| 2.1  | 1 Overview                                         |    |

| 2.2  | 2 Quality of Service and Scheduling                |    |

|      | 2.2.1 CoS Mapping                                  |    |

|      | 2.2.2 SF3 Egress Queues and Scheduler              | 14 |

|      | 2.2.2.1 Egress Transmit Queues                     | 14 |

|      | 2.2.2.2 Scheduler                                  |    |

|      | 2.2.3 Scheduling                                   |    |

|      | 2.2.4 Leaky Bucket Shaper                          |    |

| 2.3  | 3 Port-Based VLAN                                  |    |

| 2.4  | 4 IEEE 802.1Q VLAN                                 | 19 |

|      | 2.4.1 IEEE 802.1Q VLAN Table Organization          | 20 |

| 2.5  | 5 Double-Tagging                                   | 20 |

|      | 2.5.1 ISP Port                                     | 21 |

|      | 2.5.2 Customer Port                                |    |

|      | 2.5.3 Uplink Traffic (from Customer Port to ISP)   |    |

|      | 2.5.4 Downlink Traffic (from ISP to Customer Port) |    |

| 2.6  | 6 Jumbo Frame Support                              |    |

|      | 7 Port Trunking/Aggregation                        |    |

|      | 3 WAN Port                                         |    |

| 2.9  | 9 Rate Control                                     |    |

|      | 2.9.1 Ingress Rate Control                         |    |

|      | 2.9.2 Two-Bucket System                            |    |

|      | 2.9.3 Egress Rate Control                          |    |

|      | 2.9.4 Bucket Bit Rate                              |    |

|      | 10 Protected Ports                                 |    |

| 2.1  | 11 Port Mirroring                                  |    |

|      | 2.11.1 Enabling Port Mirroring                     |    |

|      | 2.11.2 Capture Port                                |    |

|      | 2.11.3 Mirror Filtering Rules                      |    |

|      | 2.11.3.1 Port Mask Filter                          |    |

|      | 2.11.3.2 Packet Address Filter                     |    |

|      | 2.11.3.3 Packet Divider Filter                     |    |

| 2.12 IGMP Snooping                             |    |

|------------------------------------------------|----|

| 2.13 MLD Snooping                              |    |

| 2.14 IEEE 802.1X Port-Based Security           |    |

| 2.15 DoS Attack Prevention                     | 29 |

| 2.16 Multiple Spanning Tree Protocol           | 29 |

| 2.17 Software Reset                            |    |

| 2.18 BroadSync HD                              | 30 |

| 2.18.1 Time Base and Slot Generation           | 30 |

| 2.18.2 Transmission Shaping and Scheduling     | 31 |

| 2.18.2.1 BroadSync HD Class5 Media Traffic     | 31 |

| 2.18.2.2 BroadSync HD Class4 Media Traffic     | 31 |

| 2.19 CableChecker                              | 32 |

| 2.20 Egress PCP Remarking                      | 33 |

| 2.21 Address Management                        | 34 |

| 2.21.1 Address Table Organization              | 34 |

| 2.21.2 Address Learning                        | 35 |

| 2.21.3 Address Resolution and Frame Forwarding | 35 |

| 2.21.3.1 Unicast Addresses                     | 36 |

| 2.21.3.2 Multicast Addresses                   | 36 |

| 2.21.3.3 Reserved Multicast Addresses          |    |

| 2.21.4 Static Address Entries                  |    |

| 2.21.5 Accessing the ARL Table Entries         |    |

| 2.21.5.1 Searching the ARL Table               |    |

| 2.21.6 Address Aging                           |    |

| 2.21.6.1 Normal Aging                          |    |

| 2.21.6.2 Fast Aging                            |    |

| 2.22 Power Savings Modes                       | 40 |

| 2.22.1 Auto Power-Down Mode                    | 40 |

| 2.22.2 Energy Efficient Ethernet Mode          |    |

| 2.22.3 Deep Green Mode                         |    |

| 2.23 Interrupt                                 | 41 |

| Chapter 3: System Functional Blocks            |    |

| 3.1 Overview                                   | 42 |

| 3.2 Media Access Controller                    | 42 |

| 3.2.1 Receive Function                         | 42 |

| 3.2.2 Transmit Function                        | 43 |

| 3.2.3 Flow Control                             | 43 |

| 3.2.3.1 10/100 Mb/s Half-Duplex                | 43 |

| 3.2.3.2 10/100/1000 Mb/s Full-Duplex           |    |

| 3.3 Integrated 10/100/1000 PHY                 | 43 |

|      | 3.3.1 Encoder                                         | 44 |

|------|-------------------------------------------------------|----|

|      | 3.3.2 Decoder                                         | 44 |

|      | 3.3.3 Link Monitor                                    | 45 |

|      | 3.3.4 Digital Adaptive Equalizer                      | 45 |

|      | 3.3.5 Echo Canceler                                   | 45 |

|      | 3.3.6 Crosstalk Canceler                              | 45 |

|      | 3.3.7 Analog-to-Digital Converter                     | 45 |

|      | 3.3.8 Clock Recovery/Generator                        | 46 |

|      | 3.3.9 Baseline Wander Correction                      | 46 |

|      | 3.3.10 Multimode TX Digital-to-Analog Converter       | 46 |

|      | 3.3.11 Stream Cipher                                  | 46 |

|      | 3.3.12 Wire Map and Pair Skew Correction              | 47 |

|      | 3.3.13 Automatic MDI Crossover                        | 47 |

|      | 3.3.14 10/100BASE-TX Forced Mode Auto-MDIX            | 48 |

|      | 3.3.15 Resetting the PHY                              |    |

|      | 3.3.16 PHY Address                                    | -  |

|      | 3.3.17 Super Isolate Mode                             |    |

|      | 3.3.18 Standby Power-Down Mode                        |    |

|      | 3.3.19 Auto Power-Down Mode                           |    |

|      | 3.3.20 External Loopback Mode                         |    |

|      | 3.3.21 Full-Duplex Mode                               | 50 |

|      | 3.3.21.1 Copper Mode                                  | 50 |

|      | 3.3.22 Master/Slave Configuration                     | 51 |

|      | 3.3.23 Next Page Exchange                             |    |

| 3.4  | Frame Management                                      |    |

|      | 3.4.1 In-Band Management Port                         |    |

|      | 3.4.2 Broadcom Tag Format for Egress Packet Transfer  |    |

|      | 3.4.3 Broadcom Tag Format for Ingress Packet Transfer |    |

| 3.5  | MIB Engine                                            |    |

|      | 3.5.1 MIB Counters Per Port                           |    |

|      | Integrated High-Performance Memory                    |    |

| 3.7  | Switch Controller                                     |    |

|      | 3.7.1 Buffer Management                               |    |

|      | 3.7.2 Memory Arbitration                              |    |

|      | 3.7.3 Transmit Output Port Queues                     |    |

| Chap | oter 4: System Interfaces                             | 63 |

|      | Overview                                              |    |

| 4.2  | Copper Interface                                      |    |

|      | 4.2.1 Auto-Negotiation                                |    |

|      | 4.2.2 Line-side (Remote) Loopback Mode                | 63 |

| 4.3  | Frame Management Port Interface                           | 63 |

|------|-----------------------------------------------------------|----|

|      | 4.3.1 RGMII Interface                                     | 64 |

| 4.4  | WAN Interface                                             | 64 |

| 4.5  | Configuration Pins                                        | 64 |

| 4.6  | Programming Interfaces                                    | 64 |

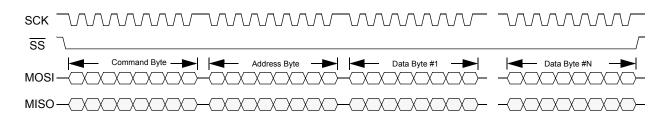

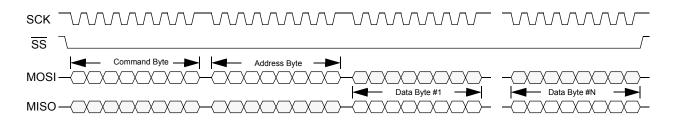

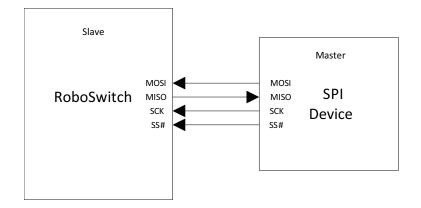

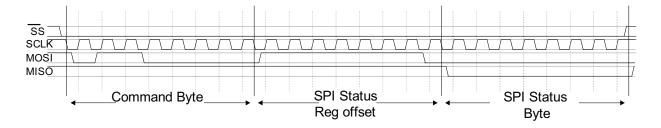

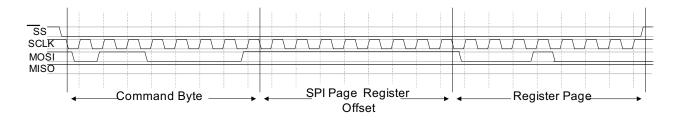

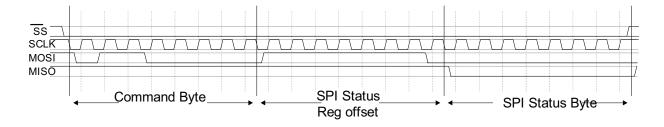

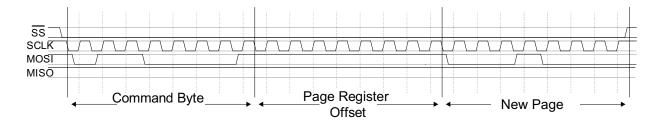

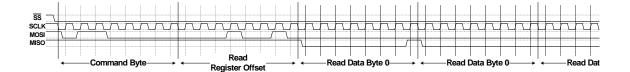

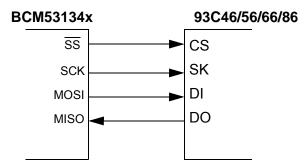

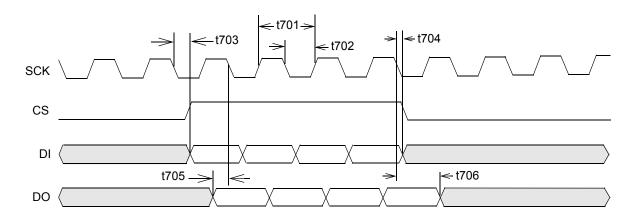

|      | 4.6.1 SPI-Compatible Programming Interface                | 65 |

|      | 4.6.1.1 SS: Slave Select                                  | 65 |

|      | 4.6.1.2 SCK: Serial Clock                                 | 65 |

|      | 4.6.1.3 MOSI: Master Output Slave Input                   | 65 |

|      | 4.6.1.4 MISO: Master Input Slave Output                   | 65 |

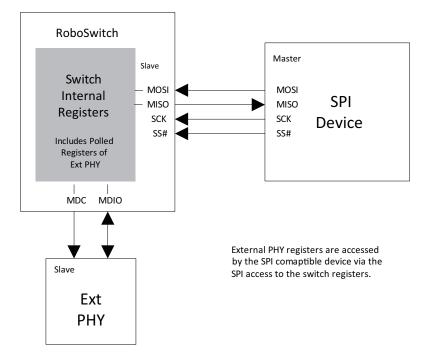

|      | 4.6.1.5 External PHY Registers                            | 67 |

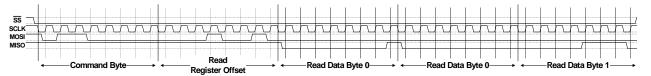

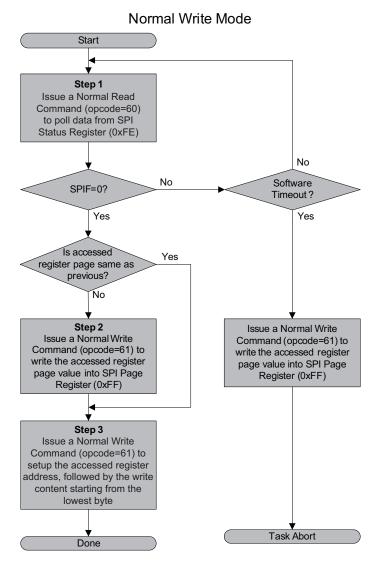

|      | 4.6.1.6 Reading and Writing BCM53134S Registers Using SPI | 68 |

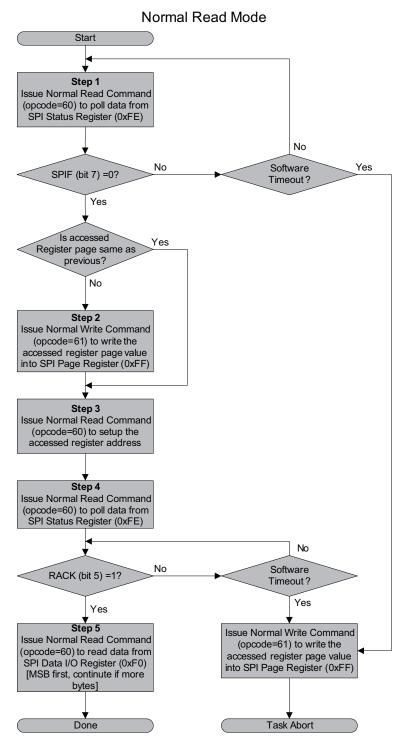

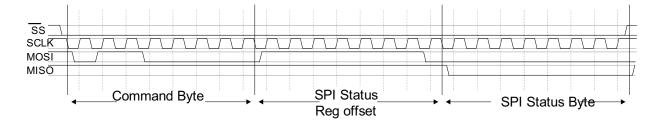

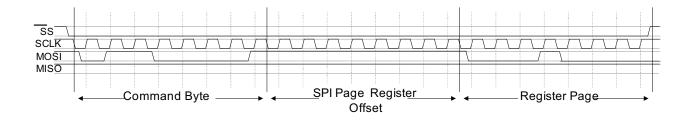

|      | 4.6.1.7 Normal Read Operation                             | 69 |

|      | 4.6.1.8 Fast Read Operation                               | 73 |

|      | 4.6.1.9 Normal Write Operation                            | 76 |

|      | 4.6.2 EEPROM Interface                                    | 79 |

|      | 4.6.2.1 EEPROM Format                                     | 79 |

|      | 4.6.3 Serial Flash Interface                              | 81 |

|      | 4.6.4 MDC/MDIO Interface                                  | 81 |

|      | 4.6.4.1 MDC/MDIO Interface Register Programming           | 82 |

|      | 4.6.4.2 Pseudo-PHY                                        | 83 |

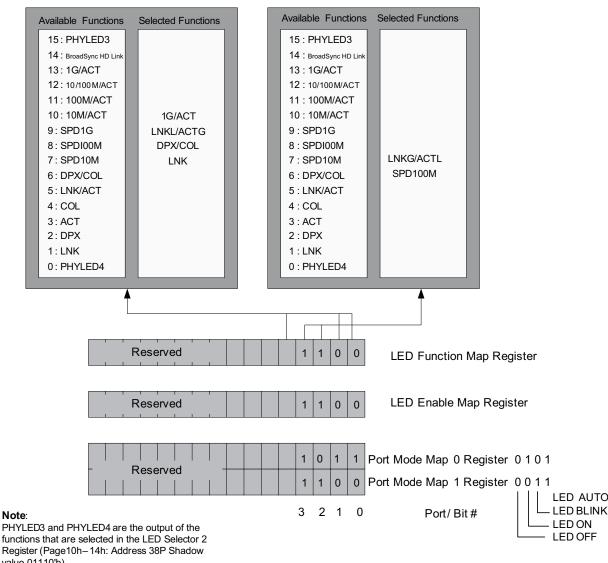

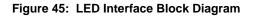

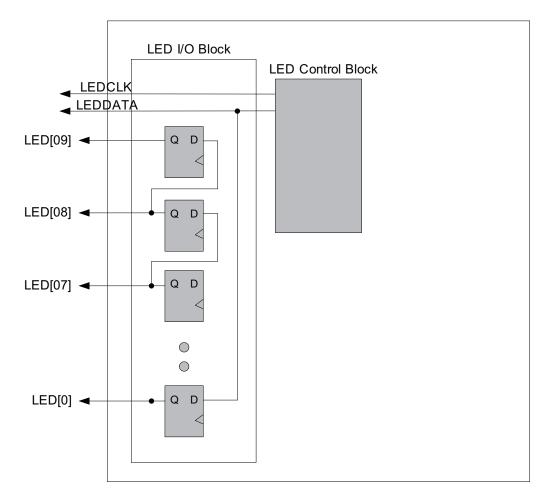

| 4.7  | ' LED Interfaces                                          |    |

|      | 4.7.1 Dual Input Configuration/LED Output Function        |    |

| 4.8  | Digital Voltage Regulator (LDO)                           | 94 |

| Chap | pter 5: Hardware Signal Definitions                       |    |

| 5.1  | I/O Signal Types                                          | 95 |

| 5.2  | Signal Descriptions                                       | 96 |

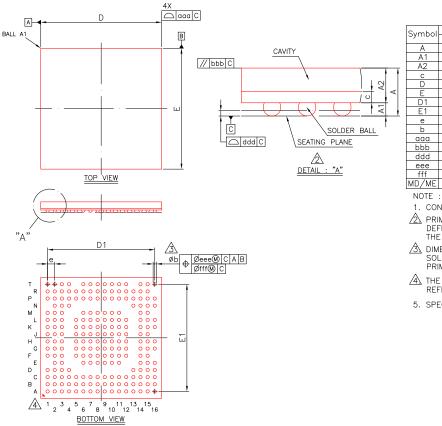

| Chap | pter 6: Pin Assignment                                    |    |

| 6.1  | Pin List by Pin Number                                    |    |

| 6.2  | Pin List by Pin Name                                      |    |

| Char | pter 7: Electrical Characteristics                        |    |

|      | Absolute Maximum Ratings                                  |    |

|      | Recommended Operating Conditions                          |    |

|      | Electrical Characteristics                                |    |

| Char | pter 8: Timing Characteristics                            |    |

|      | Reset and Clock Timing                                    |    |

|      | RGMII Interface Timing                                    |    |

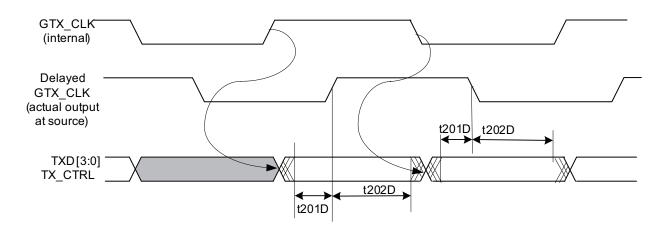

|      | 8.2.1 RGMII Output Timing (Normal Mode)                   |    |

|      | 8.2.2 RGMII Output Timing (Delayed Mode)                  |    |

|      |                                                           |    |

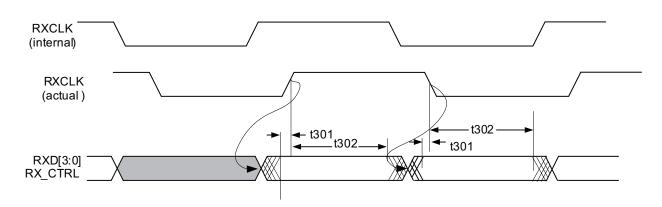

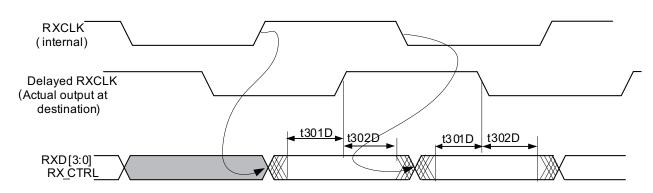

|      | 8.2.3 RGMII Input Timing (Normal Mode)         |  |

|------|------------------------------------------------|--|

|      | 8.2.4 RGMII Input Timing (Delayed Mode)        |  |

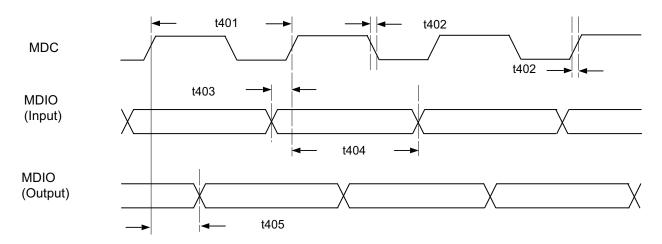

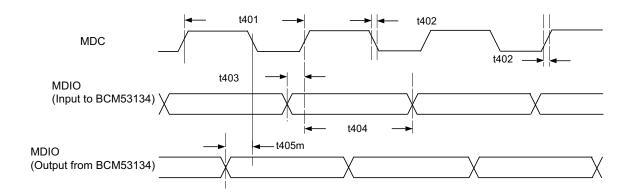

| 8.3  | MDC/MDIO Timing                                |  |

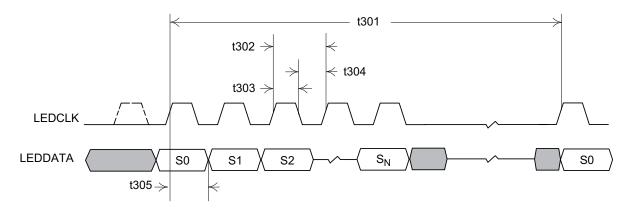

| 8.4  | Serial LED Interface Timing                    |  |

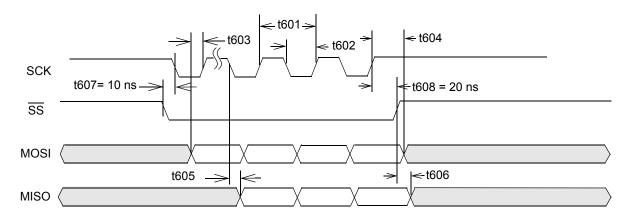

| 8.5  | SPI Timings                                    |  |

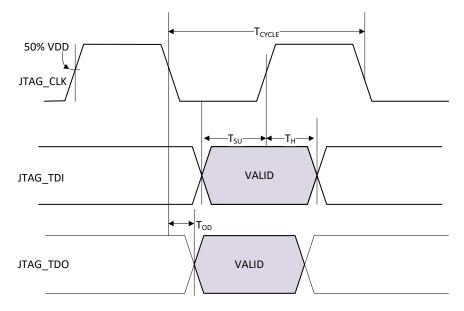

|      | JTAG Interface                                 |  |

| 8.7  | EEPROM Timing                                  |  |

| Chap | oter 9: Thermal Characteristics                |  |

| 9.1  | Package Only                                   |  |

|      | Package Only with Heat Sink (50 x 50 x 35 mm3) |  |

| 9.3  | Package Only                                   |  |

| 9.4  | Package Only with Heat Sink (19 x 19 x 5 mm3)  |  |

| Chap | oter 10: Mechanical Information                |  |

| Chap | oter 11: Ordering Information                  |  |

# **Chapter 1: Introduction**

### 1.1 Overview

The BCM53134S is a single-chip, six-port Gigabit Ethernet (GbE) switch device. It provides the following:

- A six-port nonblocking 10/100/1000 Mb/s switch controller.

- Four ports with 10/100/1000BASE-T compatible transceivers.

- Six integrated Gigabit MACs (GMACs).

- Two RGMII ports for PHY-less connection to the management agent (available only in full-duplex mode).

- An integrated Motorola SPI-compatible interface.

- High-performance, integrated packet buffer memory.

- An address resolution engine.

- A set of management information base (MIB) statistics registers.

The GMACs support full-duplex and half-duplex modes for 10 Mb/s and 100 Mb/s, and full-duplex for 1000 Mb/s. Flow control is supported in half-duplex mode with backpressure. In full-duplex mode, IEEE 802.3x frame-based flow control is supported. The GMACs are IEEE 802.3-compliant and support a maximum frame size of 9720 bytes.

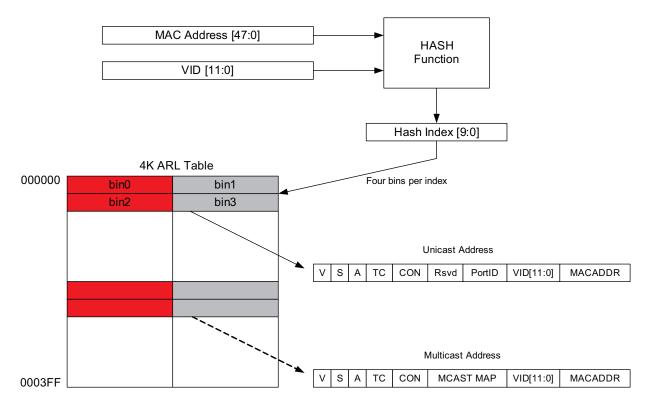

An integrated address management engine provides address learning and recognition functions at maximum frame rates. The address table provides capacity for learning up to 4K unicast addresses. Addresses are added to the table after receiving an error-free packet.

The MIB statistics registers collect receive and transmit statistics for each port and provide direct hardware support for the Ether-like MIB, MIB II (interfaces), and the first four groups of the RMON MIB. All nine groups of RMON can be supported by using additional capabilities, such as port mirroring/snooping, together with an external microcontroller to process some MIB attributes. The MIB registers can be accessed through the Serial Peripheral Interface Port by an external microcontroller.

# 1.2 Audience

This document is for designers interested in integrating the BCM53134S switches into their hardware designs and for others who need specific data about the physical characteristics and operation of the BCM53134S switches.

# 1.3 Data Sheet Information

The following notational conventions are used in this document:

- Signal names are shown in uppercase letters (such as DATA).

- A bar over a signal name indicates that it is active low (such as CE).

- In register and signal descriptions, [n:m] indicates a range from bit n to bit m (such as [7:0] indicates bits 7 through 0, inclusive).

- The use of R or Reserved indicates that a bit or a field is reserved by Broadcom for future use. Typically, R is used for individual bits and Reserved is used for fields.

- Numerical modifiers such as K or M follow traditional usage (for example, 1 KB means 1,024 bytes, 100 Mb/s [referring to fast Ethernet speed] means 100,000,000 b/s, and 133 MHz means 133,000,000 Hz).

# **Chapter 2: Features and Operation**

### 2.1 Overview

The BCM53134S switches include the following features:

- "Quality of Service and Scheduling" on page 11

- "Port-Based VLAN" on page 19

- "IEEE 802.1Q VLAN" on page 19

- "Double-Tagging" on page 20

- "Jumbo Frame Support" on page 22

- "Port Trunking/Aggregation" on page 22

- "WAN Port" on page 24

- "Rate Control" on page 24

- "Protected Ports" on page 26

- "Port Mirroring" on page 26

- "IGMP Snooping" on page 28

- "MLD Snooping" on page 28

- "IEEE 802.1X Port-Based Security" on page 28

- "DoS Attack Prevention" on page 29

- "Multiple Spanning Tree Protocol" on page 29

- "Software Reset" on page 30

- "BroadSync HD" on page 30

- "CableChecker" on page 32

- "Egress PCP Remarking" on page 33

- "Address Management" on page 34

- "Power Savings Modes" on page 40

The following sections discuss each feature in detail.

# 2.2 Quality of Service and Scheduling

The Quality of Service (QoS) feature provides up to eight internal queues per port to support eight different traffic classes (TCs). Traffic class is an internal representation of the priority of an incoming packet inside the device. The traffic class assignment can be programmed so that the user can assign incoming packets to higher/lower TC priorities through TC Mapping. Then, each TC is mapped to one of eight internal class-of-service (CoS) egress queues through TC-to-CoS process. Packets assigned (mapped) to a higher priority output queue in the switch experience less delay than packets with a lower priority under congested conditions. This can be important in minimizing latency for delay-sensitive traffic.

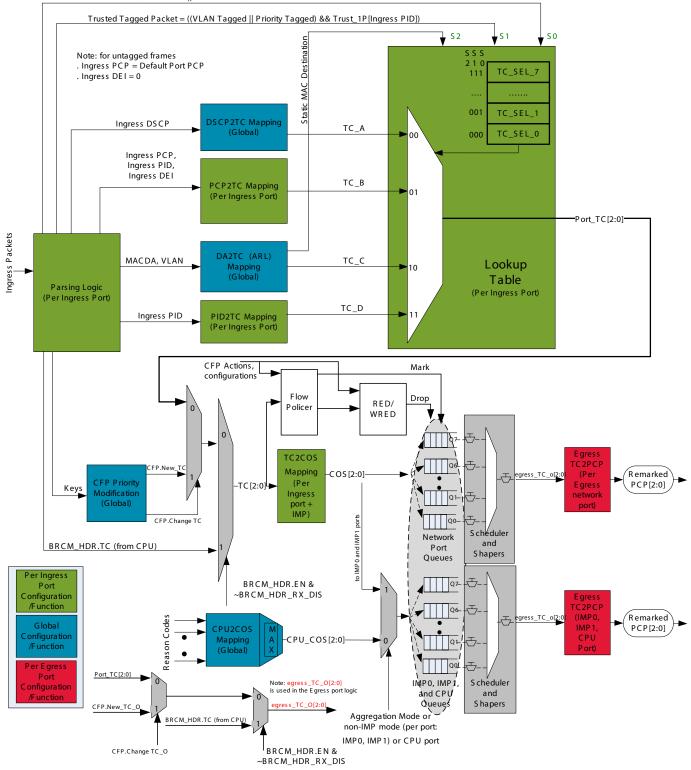

Figure 2 on page 12 shows how the BCM53134S determines the CoS and performs Priority Code Point (PCP) remarking in packets.

#### Figure 2: CoS and Egress Remarking Flow

The TC is selected from one of the following sources based on software configuration of an eight-entry lookup table corresponding to the ingress port on which the packet was received.

- DSCP-to-TC mapping table (DSCP2TC) (global function)

- The TC of a packet received from an Ethernet (or IMP) port is assigned the TC configured for the corresponding IP TOS/DSCP. When DSCP is disabled, or when the incoming packet is not of IPv4/v6 type, the TC that results from this mapping is 000.

- IEEE 802.1p PCP-to-TC mapping table (PCP2TC) (per ingress port function)

- The TC of a packet received from an Ethernet (or IMP) port is assigned the TC configured for the corresponding IEEE 802.1p priority code point (PCP). When IEEE 802.1p tagging is disabled or when the incoming packet is not tagged, the TC that results from this mapping is 000. The PCP of an ingress-tagged or priority-tagged packet is the same as the PCP field in the outermost VLAN header in the packet. The PCP of an untagged packet is the same as the default PCP register value corresponding to the port on which the packet was received.

- TC from ARL table (DA2TC) (global function)

When using MACDA-based QoS, destination addresses and VLAN IDs are used to index the ARL table, as described in "Address Management" on page 34. The matching ARL entry contains a 3-bit TC field, as shown. These bits set the MACDA-based TC for the frame and TC can also be looked up from ARL table static entries. The MACDA-based TC is assigned to the TC bits depending upon the result. The TC bits for a learned ARL entry default to 0.

Port-to-TC mapping table (PID2TC) (per ingress port function)

The TC of a packet received from an Ethernet (or IMP) port is assigned the TC configured for the corresponding port. The mapping mechanism is enabled and disabled using Port ID to TC Mapping Register (Page 30h: Address 48h–4Bh) programming. When disabled, the TC that results from this mapping is 000.

The Lookup Table is configured by software for each port separately.

The Lookup Table is indexed by the following internal flags:

- IP Packet. The flag indicates that the packet is either an IPv4 or IPv6 packet.

- Trusted Tagged Packet. The flag indicates that the packet is either VLAN-tagged or priority-tagged, and was received on a port that is configured as a trusted port.

- Static MAC Destination. The flag indicates that the MAC destination address matched a static entry in the ARL table.

The TC\_SEL\_X is an 8-entry x 2-bits-per-entry table for every ingress port. One of the 8 entries (TC\_SEL\_7..TC\_SEL\_0) is selected by a 3-bit address {S2, S1, S0}, where:

- S2 = Static MAC Destination

- S1 = Trusted Tagged Packet

- S0 = IP Packet

The two bits (which are configurable by user) that are stored at the indexed entry in the table are then used to select one of the following sources of TC (before it is optionally overridden by the TC field in the Broadcom header):

- 00: TC\_A

- 01: TC\_B

- 10: TC C

- 11: TC\_D

### 2.2.1 CoS Mapping

All packets should be configured to be mapped to appropriate TCs and those TCs should be mapped to appropriate egress queues through the TC2COS table.

A packet may be sent to the CPU through the IMP0. An additional CPU2COS mapping table may be used for the packet in nonaggregation mode to determine the CoS of those packets. The index to the mapping table entry is determined by a MAX function that selects the maximum value of reason codes. A reason code indicates the reason why a packet is sent to the CPU.

**NOTE:** In addition to determining the CPU queue in nonaggregation mode, the reason code may also help software process the packet in all modes. In aggregation mode, however, the CoS is determined by the same TC2COS hardware mapping function that is used for network ports.

### 2.2.2 SF3 Egress Queues and Scheduler

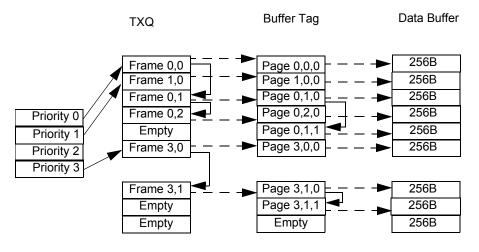

#### 2.2.2.1 Egress Transmit Queues

Each Ethernet egress port has eight transmit queues (CoS0–CoS7). Each CoS queue has its own dedicated counter to measure the buffer occupancy of the queue for congestion management purposes. Every Ethernet (ingress) port has its own set of counters to measure the buffer occupancy and the arrival rate related to the traffic received from the port.

The IMP (egress) port and port 5 also serve eight transmit queues. When the IMP port (or port 5) is set in non-aggregation mode (for example, IMP port is configured as a management port to CPU), the CoS (output queue) is decided based on the reasons for forwarding the packets to the CPU. When the IMP port (port 5) is set in aggregation mode (for example, IMP port is configured as a regular data uplink port), the CoS is decided from the TC based the normal packet classification flow.

For the rest of Ethernet egress ports, all incoming frames are assigned to an egress transmit queue depending on their assigned TC. Each egress transmit queue is a list that specifies an order for packet transmission. The corresponding egress port transmits packets from each of the queues according to a programmable algorithm, with the higher TC queues being given greater access than the lower TC queues. Queue 0 is the lowest-TC queue.

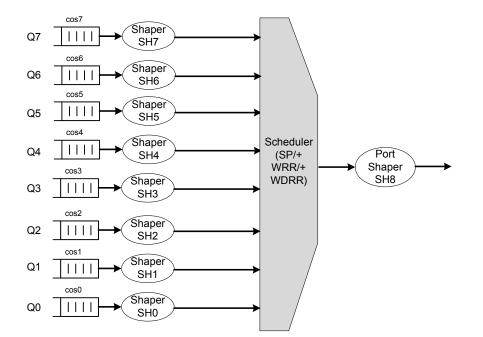

The queues and scheduler/shaper for each port are shown in the Figure 3 on page 14.

#### Figure 3: Queues and Scheduler/Shaper Diagram

#### 2.2.2.2 Scheduler

The scheduling element can be configured to be one of the following operating modes:

- 1. Strict Priority.

- 2. Weighted Round Robin (WRR): packet-based scheduling.

- 3. Weighted Deficit Round Robin (WDRR): byte-based scheduling.

- 4. Or a mix of SP, WRR, and WDRR.

Table 1 lists various configuration options of the scheduler.

Table 1: Scheduler Configuration Selections

|          | CoS7     | CoS6     | CoS5     | CoS4     | CoS3     | CoS2     | CoS1     | CoS0     |

|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Option 1 | SP       |

| Option 2 | SP       | WDRR/WRR |

| Option 3 | SP       | SP       | WDRR/WRR | WDRR/WRR | WDRR/WRR | WDRR/WRR | WDRR/WRR | WDRR/WRR |

| Option 4 | SP       | SP       | SP       | WDRR/WRR | WDRR/WRR | WDRR/WRR | WDRR/WRR | WDRR/WRR |

| Option 5 | SP       | SP       | SP       | SP       | WDRR/WRR | WDRR/WRR | WDRR/WRR | WDRR/WRR |

| Option 6 | WDRR/WRR |

The operating mode of a scheduling queue/port can be configured independent of the operating mode of any other scheduling queue/port in the device. One of the two round robin scheduling algorithms (WRR or WDRR) is selected through a per-port configuration register.

Within the SP group, the precedence takes the ascending order of the CoS number. The higher the CoS number, the higher the precedence for scheduling.

Within the WDRR group, the queues are selected based on the following round-robin rules:

- The share can be weighted by assigning each queue its corresponding Weight in granularity of 1/256. If CoS2 is assigned a weight of x/256, CoS1 is assigned a weight of y/256, and CoS0 is assigned a weight of z/256, the ratio of transmitted packet bytes between Cos2:CoS1:CoS0 should be x:y:z in each Scheduling Round, if there is always a packet waiting during the round.

- A Scheduling Round is defined as a period within which each queue gets its fair share of packet transmission resource in granularity of number of packets or number of sets of 256 bytes transmitted.

- At the beginning of each scheduling round:

- Every queue's share is added to its respective accumulated credit, and

- Empty queues are noted and are not considered for scheduling in the scheduling round.

- During each scheduling round, queues with positive credits in respective queue shaper are serviced in order of CoS (CoS7, CoS6, CoS5,....CoS0):

- Empty queues as well as queues that do not have positive credits in the respective queue shaper are skipped.

- When a queue is serviced, the number of packets transmitted from the queue depends on one of the two modes of operations configured by software:

Burst Mode: one or more packets are transmitted from the queue when its fair share of packet transmission resources is used up (credit becomes negative), or the queue becomes empty before the current scheduling round for the queue ends. End of current scheduling round for a queue means the queue will not be serviced again in the current scheduling round.

Non-Burst Mode: one packet is transmitted from each queue in the CoS order (CoS7...0), until the fair share of packet transmission resources of a queue is used up (credit becomes negative), or the queue becomes empty before the current scheduling round for the queue ends. End of current scheduling round for a queue means the queue will not be serviced again in the current scheduling round.

- Also, the negative accumulated credit of a non-empty queue from the current round is carried forward from the current round to the beginning of the next round.

- If a queue becomes empty before its fair share is used up, the current scheduling round for the queue ends will mean that the queue will not be serviced again in the current scheduling round. Also, its left-over credit is not carried over to the next scheduling round, which means the deficit counter of an empty queue is set to zero (to avoid carrying over accumulated credit history of empty queues). The action of setting the accumulated credit to zero is independent of whether the queue became negative after serving the last packet in the queue, or it was still positive after it served the last packet in the queue.

- The scheduler algorithm goes back to Step "At the beginning of each scheduling round" to start the next round.

The weights of a WRR/WDRR scheduler can be configured independent of weights of any other WRR/WDRR scheduler in the device.

The scheduler works by first servicing the SP queues. Queues have an intrinsic priority from high to low. That is, CoS7 has higher priority than CoS6. The second scheduling option utilizes WRR/WDRR. The WRR/WDRR scheduling discipline interleaves packets from queues based on a configured weight for the queues. That is, when a queue is selected for service the depth of the queue is sampled. Packets are transmitted from the queue in the scheduling round until either the queue becomes empty or the credit counter runs out of credits. Once these numbers of packets are serviced, then the next queue is serviced. Queues are serviced in a round-robin fashion (WRR/WDRR) until this process is completed. Queues that do not have packets to send in a round (either empty or do not have positive credits in respective queue shapers), are skipped and not serviced. A queue is serviced only once in a round. If a packet arrives in a queue just after the scheduler decided to skip a queue (because it was empty, became empty) in the current round, the packet will not be serviced in the current round by the scheduler.

For example, assume the queue weights for CoS3–CoS0 are 4, 3, 2, 1 (or 1024, 768, 512, and 256 bytes) respectively, and the scheduler is configured in burst mode of operation. Note that small weights have been used in this example for simplification. In real applications, the minimum (WDRR weight \* 256) should be  $\geq$  MTU for correct behavior of the WDRR scheduler. Because of programming error, if the weight of any DRR queue is configured such that (WDRR weight \* 256) < MTU, the behavior of the DRR scheduler is not predictable.

Assume an example of a scheduling round is similar to Figure 3 on page 14 where the frames are queued only in CoS3, CoS1, and CoS0. CoS2 is empty through the entire round in this example. The egress packet stream created by the WDRR scheduler is depicted where the number in a rectangle indicates the length of the packet in bytes. In the example, the WDRR scheduler creates an egress packet stream by interleaving packets from CoS3, CoS1, and CoS0 (the non-empty queues with accumulated weight > 0) in a fashion that depends on the WDRR weights assigned to the respective CoS.

In the example, assume a scheduling round started with zero accumulated credit for each of the four CoS queues. The WDRR scheme will add credits to the four queues at the beginning of the round. Hence, there will be 1024 bytes accumulated credits for CoS3, 0 for CoS2, 512 for CoS1, and 256 for CoS0. CoS2 accumulated credits at the beginning of the round is 0 since it was either empty, or its shaper was blocked, or the shaper was enabled but did not have positive credits. In the current round, the WDRR scheduler will service the queues in the following order:

The scheduler will service CoS3 first because it is the highest order CoS queue that has positive credits in the current round. In the example, CoS3 has 494 bytes in four packets whereas its accumulated credits are 1024 bytes. Hence, it became empty when it still had 530 positive accumulated credits. However, since the queue became empty before it could use up all its credits, the WDRR scheme will carry forward 0 accumulated credits for CoS3 to the next round. The scheduler will not service CoS3 any more in the current round even if a new packet is stored in the queue while it is servicing any remaining queues in the current round.

- It will skip CoS2 next because it has 0 accumulated credits. The scheduler will carry forward 0 accumulated credits to the next round for CoS2. The scheduler will not service CoS2 any more in the current round even if a new packet is stored in the queue while it is servicing the remaining queues in the current round.

- 3. It will service CoS1 next because it has the next highest order CoS queue. CoS1 has 780 bytes in four packets, which is more than 512 bytes of accumulated credits. Hence, the WDRR scheduler will stop servicing the queue and carry forward -278 accumulated credits for CoS1 to the next round after the first three packets from the queue are transmitted. The scheduler will not service CoS1 any more in the current round even if a new packet is stored in the queue while it is servicing the remaining queues in the current round.

- 4. Finally, it will serve CoS0 and then end the current round. CoS0 has 204 bytes in two packets, which is a little less than 256 bytes of accumulated credits for CoS1. Since the queue will become empty before its positive credits are used up, the WDRR scheduler will carry forward 0 credits for CoS0 to the next round. The scheduler will not service CoS0 any more in the current round even if a packet arrives before the next round starts.

### 2.2.3 Scheduling

There are three shapers, SH2, SH1, and SH0, and they can be separately configured to be either a credit-based AVB shaper that is compliant with the IEEE 802.1qav standard, or a standard Leaky Bucket rate limiter.

### 2.2.4 Leaky Bucket Shaper

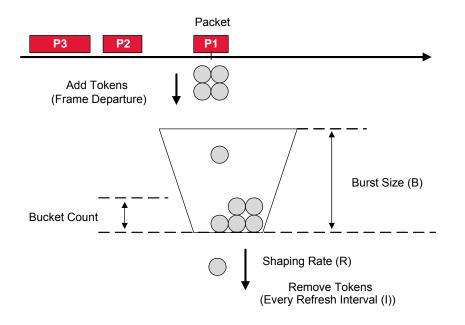

Initially, the bucket is filled with tokens with a burst size (B). In every refresh interval, certain amounts of tokens are removed from the bucket, which effectively determines the shaping rate. The scheduler services a packet based on the state information of the shaper. If the bucket count is less than or equal to the burst size, the packet is in-profile. Otherwise, the packet is out-of-profile. After servicing a packet, tokens are added into the bucket by an amount of tokens equivalent to the size of the packet. In the BroadSync HD (AVB) shaping mode, the following additional token updates are required to reduce the burst size (B), reset the bucket counter to be equal to burst size (B). See Figure 4.

#### Figure 4: Leaky Bucket Shaper

The leaky bucket shaper has the following parameters:

- Refresh Interval (I): Defines the how often the tokens are removed from the buckets.

- Shaping Rate (R): The rate at which the shaper limits service.

- Burst Size (B): The maximum number of tokens that can be added into the bucket.

- AVB Shaping Mode: Used to select AVB versus Normal shaping mode.

In every refresh interval, T tokens are removed from the bucket. T is the number of tokens. Associated with a token is a token size (S). The shaper operates in byte-based mode, and the token size (S) is the number of bytes per token.

The relation between Shaping Rate (R), Refresh Interval (I) and Token Size (S) can be represented by formula:

R = T x (S/I)

NOTE: The refresh interval is fixed at 7.8125 µs.

It is recommended that software configure the two shapers in the following way when applicable:

- SH2 should be configured as:

- An AVB shaper for an AVB port with Class A traffic.

- A non-AVB shaper in all other applications.

- SH1 should be configured as:

- An AVB shaper for an AVB port with Class B traffic.

- A non-AVB shaper in all other applications.

- SH0 should be configured as a non-AVB shaper in all applications.

The Leaky Bucket threshold of a shaper can be configured in the range of 64 bytes–16 MB, with a resolution of 64 bytes. When the shaper operates as an AVB shaper, the number of tokens in the shaper is saturated by hardware (made equal to the configured threshold) when there is no packet at the shaper input. For example, if SH2 is configured as an AVB shaper and Q5 is empty, then hardware forces the accumulated credits in SH2 to be the same as the threshold. Each shaper output rate can be configured in the range of 64 Kb/s–1 Gb/s, with a resolution of 64 Kb/s.

# 2.3 Port-Based VLAN

The port-based virtual LAN (VLAN) feature partitions the switching ports into virtual private domains designated on a perport basis. Data switching outside of the port's private domain is not allowed. The BCM53134S provide flexible VLAN configuration for each ingress (receiving) port.

The port-based VLAN feature works as a filter, filtering out traffic destined to nonprivate domain ports. For each received packet, the ARL resolves the DA and obtains a forwarding vector (list of ports to which the frame will be forwarded). The ARL then applies the VLAN filter to the forwarding vector, effectively masking out the nonprivate domain ports. The frame is forwarded only to those ports that meet the ARL table criteria, as well as the port-based VLAN criteria.

# 2.4 IEEE 802.1Q VLAN

The BCM53134S support IEEE 802.1Q VLAN and up to approximately 4096 VLAN table entries that reside in the internal embedded memory. Once the VLAN table is programmed and maintained by the microcontroller, the BCM53134S autonomously handle all operations of the protocol. These actions include the stripping or adding of the IEEE 802.1Q tag, depending on the requirements of the individual transmitting port. It also performs all the necessary VLAN lookups in addition to MAC L2 lookups.

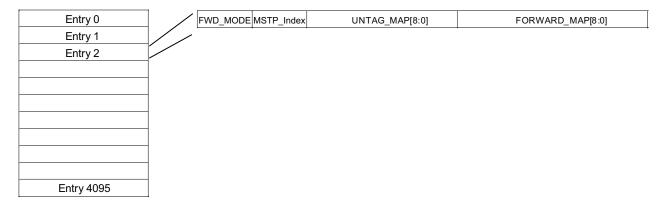

### 2.4.1 IEEE 802.1Q VLAN Table Organization

Each VLAN table entry, also referred to as a VLAN ID, an untag map, and a forward map:

- The untag map controls whether the egress packet is tagged or untagged.

- The forward map defines the membership within a VLAN domain.

- The FWD\_MODE indicates whether the packet forwarding should be based on VLAN membership or on ARL flow.

The untag map and forward map include bit-wise representation of all the ports.

#### Figure 5: VLAN Table Organization

NOTE: If the MII port is configured as a management port, then the tag is not stripped even if the untag bit is set.

# 2.5 Double-Tagging

The BCM53134S provide the double tagging feature, which is useful for ISP applications. When the ISP aggregates incoming traffic from each individual customer, the extra tag (double tag) can provide an additional layer of tagging to the existing IEEE 802.1Q VLAN. The ISP tag (extra tag) is a way of separating individual customers from other customers. Using the IEEE 802.1Q VLAN tag, the individual customer's traffic can be identified on a per-port basis.

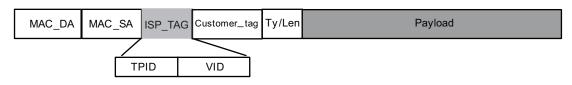

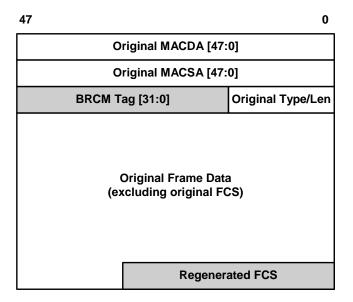

When the double-tagging feature is enabled (register Page 34h, Address 05h, bit[3:2]) and the Enable IEEE 802.1Q (register Page 34h, Address 00h, bit 7), users can expect two VLAN tags in a frame: the tag close to MAC\_SA is the ISP tag, and the one following is the customer tag as shown in Figure 6.

#### Figure 6: ISP Tag Diagram

The switch uses the ISP tag for ARL and VLAN table accesses and the customer tag as an IEEE 802.1Q tag. There is a perchip programmable register Double Tagging TPID register for ISP tag (default = 9100'h). All ISP tags will be qualified by this Tag Protocol ID (TPID) value. When the double-tagging feature is enabled, all switch ports are separated into two groups: ISP ports and customer ports. The BCM53134S performs the normalization process for all ingress frames for both Intelligent Double Tag (IDT) and Double Tag (DT) modes, whether from the ISP port or customer port. The normalization process is to insert an ISP tag, customer tag, or ISP + customer tag (depending on whether the ingress frame is without tags or with one tag) to allow all ingress frames with double tags. However, if the ingress frames are with double tags (ISP + customer tag), and the ISP tag TPID matches the TPID specified in the Double Tagging TPID register, it does not perform the normalization process. The ISP ports are defined in the ISP Port Selection Portmap register. When the port(s) corresponding bit(s) are set, those port(s) should be connected to the ISP, and otherwise connected to customers. Each switch device can have multiple ports assigned as ISP ports, and each ISP is uniquely identified using different VLAN forward maps or the port-based VLAN feature.

### 2.5.1 ISP Port

It is possible for the ISP port to receive three different types of frames: untagged, ISP-tagged, and ISP+Customer-tagged frames.

When the double-tagging feature is enabled and the received frame is untagged (or the TPID does not match with ISP TPID specified in Double Tagging TPID register, the default ISP tag and customer tag are added, and VLAN ID of ISP tag receives it from the port default VID. The frames are forwarded according to the VLAN table. However, if the Port-Based VLAN Control register is enabled, the egress ports specified in the port-VLAN control register override the VLAN table settings. If the received frame is ISP tagged (TPID matches with the ISP tag VLAN ID specified in the double-tagging TPID register), the default customer tag (8100 + default PVID) is added, the ISP VID is used to access the ARL table, and the ISP tag can be stripped on the way out according to the untagged bit setting in the VLAN table. In addition, ISP port frame can forward to the destination port directly based on forward port map of VLAN table by setting FWD\_MODE bit to 1 of VLAN Table Entry register.

The VLAN ID is generated from the ISP tag, and TC is generated from the ingress frame outer tag.

### 2.5.2 Customer Port

It is also possible for the Customer port to receive two different types of frames: untagged and Customer-tagged frames.

When the double-tagging feature is enabled, all the ingress frames preform the normalization process to insert an ISP tag or ISP + Customer tag (depending whether the ingress frame is without tags or with one tag) to allow all ingress frames with double tags. The VLAN ID of ISP tag receives it from the port default VID.

The VLAN ID is generated from the ISP tag, and the TC is generated from the ingress frame outer tag.

- **NOTE:** It is illegal to strip out the ISP tag on the ISP egress port by using the untagged bit setting in the VLAN table.

- **NOTE:** Only the VLAN tagged or untagged packets are expected for the ingress of the customer ports. The customer does not add the ISP tags.

There are two possible traffic scenarios:

- One scenario is from a customer port to an ISP port.

- The second scenario is from an ISP port to a customer port.

### 2.5.3 Uplink Traffic (from Customer Port to ISP)

Data traffic is traffic received from the customer port without tags or a customer tag, and the frame is destined for an ISP port. The customer ingress port performs a normalization process to allow ingress frames with double tags (ISP + Customer tag), and the ISP tag VID is based on the port default VID tag.

However, if the ingress frame is with an IEEE 802.1p tag, the VID of IEEE 802.1p tag is changed by the VID of the port default VID tag after the customer port normalization process. The TC do not change.

Control traffic frames can be forwarded to the CPU first and then the CPU forwards to the ISP port if the switch management mode is enabled and if the RESV\_MCAST\_FLOOD bit=0 in the Global VLAN Control 4 register. In this case, the control frame adds an ISP tag by ingress port and forwards to the CPU. The CPU can then forward it to the ISP port with or without the ISP tag by using the egress-direct feature.

### 2.5.4 Downlink Traffic (from ISP to Customer Port)

Data traffic frame received from the ISP port may or may not have an ISP tag attached. When the received frame does not have an ISP tag and customer tag, the ISP ingress port does a normalization process to insert double tags (ISP + Customer tag), and the ISP tag VID is based on the port default VID tag. All ARL and VID table access should be based on the new tag. The traffic is then forwarded to the customer port through proper VLAN configuration. Usually, the software configures so the customer Egress port continuously removes the ISP tag. However, it is based on how the untagged map is configured.

Moreover, if the ingress frame is with an IEEE 802.1p tag, the VID of the IEEE 802.1p tag is changed by the VID of the port default VID tag after the ISP port normalization process. The TC will not change.

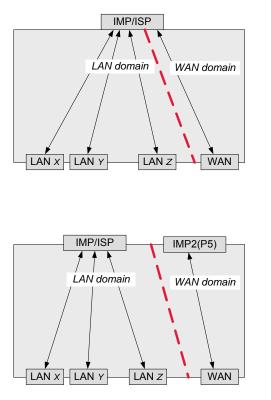

The Control traffic is forwarded to the CPU when the switch management mode is enabled and if RESV\_MCAST\_FLOOD bit=0 in the Global VLAN Control 4 register. The BCM53134S can also support multiple ISP port configurations by enabling the FWD\_MODE bit of the VLAN Table Entry register.

There are also two ways to separate traffic that belongs to two different ISP customers:

- 1. Each group (ISP and customer) is assigned to the same VLAN group, so that traffic does not leak to other ISP.

- 2. Use the Port-based VLAN to separate traffic that belongs to a different ISP.

# 2.6 Jumbo Frame Support

The BCM53134S can receive and transmit frames of extended length on ports linked at gigabit speed. Referred to as jumbo frames, these packets are longer than the standard maximum size, but shorter than 9720 bytes. Jumbo packets can be received or forwarded only to 1000BASE-T–linked ports that are jumbo-frame enabled. Up to 38 buffer memory pages are required for storing the longest allowed jumbo frame. While there is no physical limitation to the number of ports that can be jumbo enabled, it is recommended that no more than two be enabled simultaneously to ensure system performance. There is no performance penalty for enabling additional jumbo ports beyond the potential strain on memory resources that can occur due to accumulated jumbo packets at multiple ports.

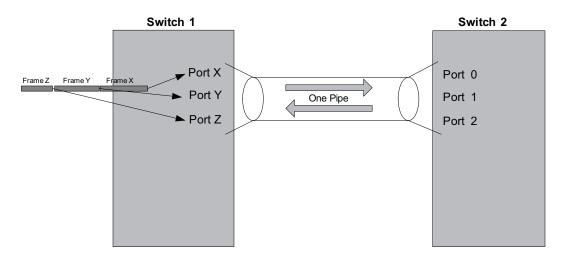

# 2.7 Port Trunking/Aggregation

The BCM53134S supports MAC-based trunking. The trunking feature allows up to four ports to be grouped together as a single-link connection between two switch devices. This increases the effective bandwidth through a link and provides redundancy. The BCM53134S allow up to two trunk groups. Trunks are composed of predetermined ports and can be enabled using the Trunking Group 0 register. Ports within a trunk group must be of the same linked speed. By performing a

dynamic hashing algorithm on the MAC address, each packet destined for the trunk is forwarded to one of the valid ports within the trunk group. This method has several key advantages. By dynamically performing this function, the traffic patterns can be more balanced across the ports within a trunk. In addition, the MAC-based algorithm provides dynamic failover. If a port within a trunking group fails, the other port within the trunk automatically assumes all traffic designated for the trunk. It allows for a seamless, automatic redundancy scheme. This hashing function can be performed on the DA, SA, or DA/SA.

#### Figure 7: Trunking

# 2.8 WAN Port

The BCM53134S offers a programmable WAN port feature: a WAN Port Select register (page 00h, address 26h). Select a port as a WAN port to forward all of that port's traffic to only the CPU port. The non-WAN port traffic from all other local ports does not flood to the WAN port.

Figure 8 shows the WAN and LAN domain separation when the WAN port is selected.

# 2.9 Rate Control

### 2.9.1 Ingress Rate Control

Forwarding broadcast traffic consumes switch resources, which can negatively impact the forwarding of other traffic. The rate-based broadcast storm suppression mechanism is used to protect regular traffic from an overabundance of broadcast or multicast traffic. This feature monitors the rate of ingressed traffic of programmable packet types. If the rates of these packet types exceed the programmable maximum rate, the packets are dropped.

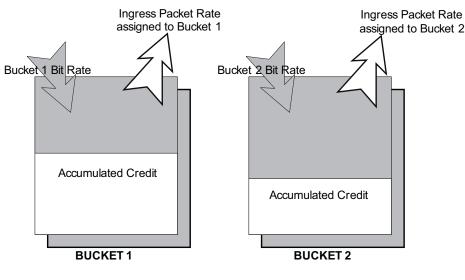

The broadcast storm suppression mechanism works on a credit-based rate system that figuratively uses a bucket to track the bandwidth of each port (see Figure 9). Credit is continually added to the bucket at a programmable bucket bit rate. Credit is decremented from the bucket whenever one of the programmable packet types is ingressed at the port. If no packets are ingressed for a considerable length of time, the bucket credit continues to increase up to a programmable-maximum bucket size. If a heavy burst of traffic is suddenly ingressed at the port, the bucket credit becomes drained. When the bucket is emptied, incoming traffic is constrained to the bucket bit rate (the rate at which credit is added to the bucket). At this point, excess packets either are dropped or deterred using flow control, depending upon the Suppression Drop mode.

#### Figure 9: Bucket Flow

If there is no accumulated credit available, the switch does not accept input packets.

### 2.9.2 Two-Bucket System

For added flexibility, the BCM53134S employs two buckets to track the rate of ingressed packets. Each of the two buckets (Bucket 0 and Bucket 1) can be programmed to monitor different packet types. For example, Bucket 0 could monitor broadcast packets, while Bucket 1 monitors multicast packets. Multiple packet types can be monitored by each bucket, and a packet type can be monitored by both buckets.

The rates of each bucket can be individually programmed. For example, the broadcast packets of Bucket 0 could have a maximum rate of 3 Mb/s, whereas the multicast packets of Bucket 1 could be allowed up to 80 Mb/s. The size of each bucket can be programmed. This determines the maximum credit that can accumulate in each bucket. The rate count and bucket size can be individually programmed for each port, providing another level of flexibility. Suppression control can be enabled or disabled on a per-port basis. This system allows the user to control dual packet-type rates on a per-port basis.

### 2.9.3 Egress Rate Control

The BCM53134S monitors the rate of egress traffic per port. Unlike the ingress traffic rate control, the egress rate control provides only the per-port rate control regardless of traffic types. This feature uses only one bucket to track the rate of egressed packets. The egress rate control feature supports only absolute bit rate mode (Bit Rate Mode = 0), and the bucket bit rate calculation is shown in Table 2.

### 2.9.4 Bucket Bit Rate

The relative ingress rates of each bucket can be programmed on a per-port basis. Each port has a programmable rate count value for Bucket 0 and Bucket 1. Additionally, the bit rate mode is programmed on a chip basis. If this bit is 1, the packet rate is automatically scaled according to the port link speed. Ports operating at 1000 Mb/s would be allotted a 100 times higher ingress rate than ports linked at 10 Mb/s. Together, the rate count value and the bit rate mode determine the bucket bit rate, which is a reflection of how quickly data can be ingressed (Kb/s) at the given port for a given bucket. The rate count values are specified in Table 2. Values outside these ranges are not valid entries.

| Rate Count (RC)                           | Bit Rate<br>Mode | Link Speed | Bucket Bit Rate<br>Equation | Approximate Computed<br>Bucket Bit Rate<br>Values (as a function of RC) |

|-------------------------------------------|------------------|------------|-----------------------------|-------------------------------------------------------------------------|

| 1–28                                      | 0                | Any        | (RC × 8 × 1M)/125           | 64 KB, 128 KB, 192 KB,, 1.792 MB                                        |

| 29–127                                    | 0                | Any        | (RC – 27) × 1M              | 2 MB, 3 MB, 4 MB,, 100 MB                                               |

| 128–240                                   | 0                | Any        | (RC – 115) × 1M × 8         | 104 MB, 112 MB, 120 MB,, 1000 MB                                        |

| 1–125                                     | 1                | 10 Mb/s    | (RC × 8 × 1M)/100           | 0.08 MB, 0.16 MB, 0.24 MB,, 10 MB                                       |

| 1–125                                     | 1                | 100 Mb/s   | (RC × 8 × 1M)/10            | 0.8 MB, 1.6 MB, 2.4 MB,, 100 MB                                         |

| 1–125                                     | 1                | 1000 Mb/s  | RC × 8 × 1M                 | 8 MB, 16 MB, 24 MB,, 1000 MB                                            |

| NOTE: 1M represents 1 × 10 <sup>6</sup> . |                  |            |                             |                                                                         |

#### Table 2: Bucket Bit Rate

2.10 Protected Ports

The Protected Ports feature allows certain ports to be designated as protected. All other ports are unprotected. Traffic between protected port group members is blocked. However, protected ports are able to send traffic to unprotected ports. Unprotected ports can send traffic to any port. Several applications that can benefit from protected ports:

- Aggregator: For example, all the available ports are designated as protected ports except a single aggregator port. No

traffic incoming to the protected ports is sent within the protected ports group. Any flooded traffic is forwarded only to

the aggregator port.

- To prevent nonsecured ports from monitoring important information on a server port, the server port and nonsecured ports are designated as protected. The nonsecured ports will not be able to receive traffic from the server port.

# 2.11 Port Mirroring

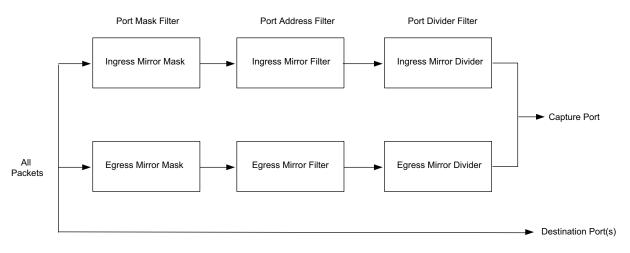

The BCM53134S support Port Mirroring, allowing ingress and/or egress traffic to be monitored by a single port designated as the mirror capture port. The BCM53134S can be configured to mirror the ingress traffic and/or egress traffic of any other port (s). Mirroring multiple ports is possible, but can create congestion at the mirror capture port. Several filters are used to decrease congestion.

### 2.11.1 Enabling Port Mirroring

Port Mirroring is enabled by setting the Mirror Enable bit.

#### Figure 10: Mirror Filter Flow

### 2.11.2 Capture Port

The capture port is capable of monitoring other specified ports. Frames transmitted and received at the other ports are forwarded to the Capture port according to the mirror filtering rules discussed below.

### 2.11.3 Mirror Filtering Rules

Mirror filtering rules consist of a set of three filter operations (Port Mask, Packet Address, and Packet Divider) that are applied to traffic ingressed and/or egressed at a switch port.

#### 2.11.3.1 Port Mask Filter

The IN\_MIRROR\_MASK bits define the receive ports that are monitored. The OUT\_MIRROR\_MASK bits define the transmit ports that are monitored.

Any number of ingress/egress ports can be programmed to be mirrored, but bandwidth restrictions on the one-mirror capture port should be taken into account to avoid congestion or packet loss.

#### 2.11.3.2 Packet Address Filter

The type of filtering that is applied to frames received on the mirrored ports is configurable. The IN\_MIRROR\_FILTER bits select among the following where x is the 48-bit MAC address. Likewise, the type of filtering that is applied to frames transmitted on the egressed mirrored ports:

- Mirror all received frames

- Mirror received frames with DA = x

- Mirror received frames with SA = x

#### 2.11.3.3 Packet Divider Filter

The IN\_DIV\_EN bit allows further statistical sampling. When IN\_DIV\_EN = 1, the receive frames passing the initial filter are divided by the value IN\_MIRROR\_DIV, which is a 10-bit value. Only one out of every n frames is forwarded to the mirror capture port, where  $n = IN_MIRROR_DIV + 1$ . This allows the following additional capabilities:

Mirror every n<sup>th</sup> received frame

- Mirror every n<sup>th</sup> received frame with DA = x

- Mirror every n<sup>th</sup> received frame with SA = x

- **NOTE:** When multiple ingress ports have been enabled in the IN\_MIRROR\_MASK, the cumulative total packet count received from all ingress ports is divided by the value of IN\_MIRROR\_DIV to deliver the nth receive frame to the mirror capture port. Egressed frames are governed by the OUT\_MIRROR\_MASK bit and the OUT\_MIRROR\_DIV bit.

# 2.12 IGMP Snooping

The BCM53134S supports IP layer IGMP Snooping, which includes IGMP unknown, query, report, and leave message.

A frame with a value of 2 in the IP header protocol field and IGMP frames are forwarded to the CPU port. The management CPU can then determine, from the IGMP control packets which port should participate in the multigroup session. The management CPU proactively programs the multicast address in the ARL table or the multiport address entries. If the IGMP\_UKN\_FWD\_EN, IGMP\_QRY\_FWD\_EN, IGMP\_RPTLVE\_FWD\_EN is enabled, IGMP frames will be trapped to the CPU port only.

# 2.13 MLD Snooping

The BCM53134S supports IP layer MLD Snooping, which includes MLD query, report, and done message. For of the query and report/done message types, there are four options available: discard, forward normally, forward to CPU, or forward normally and copy to CPU. The CPU is then expected to interpret these messages and configure the address table accordingly.

# 2.14 IEEE 802.1X Port-Based Security

IEEE 802.1X is a port-based authentication protocol. By receiving and extracting special frames, the CPU can control whether the ingress and egress ports should forward packets or not. If a user port wants service from another port (authenticator), it must get approved by the authenticator. EAPOL is the protocol used by the authentication process. The BCM53134S detects EAPOL frames by checking the destination address of the frame. The Destination addresses should be either a multicast address as defined in IEEE 802.1X (01-80-C2-00-00-03) or a user-predefined MAC (unicast or multicast) address. Once EAPOL frames are detected, the frames are forwarded to the CPU so it can send the frames to the authenticator server. Eventually, the CPU determines whether the requestor is qualified or not based on its MAC\_Source addresses, and frames are either accepted or dropped. The per-port EAP can be programmed in the register.

BCM53134S provides three modes for implementing the IEEE 802.1X feature. Each mode can be selected by setting the appropriate bits in the register.

- The Basic Mode (when EAP Mode = 00'b) is the standard mode. The EAP\_BLK\_MODE bit is set before authentication to block all of the incoming packets. Upon authentication, the EAP\_BLK\_MODE bit is cleared to allow all the incoming packets. In this mode, the Source Address of incoming packets is not checked.

- The second mode is Extended Mode (when EAP Mode = 10'b), where an extra filtering mechanism is implemented after the port is authenticated. If the Source MAC address is unknown, the incoming packets would be dropped and the unknown SA is not learned. However if the incoming packet is IEEE 802.1X packet, or special frames, the incoming packets is forwarded. The definition of the Unknown SA in this case is when the switch cannot match the incoming Source MAC address to any of the addresses in ARL table, or the incoming Source MAC address matches the address in ARL table, but the port number is mismatched.

- The third mode is Simplified Mode (when EAP Mode = 11'b). In this mode, the unknown Source MAC address packets would be forwarded to CPU rather than dropped. Otherwise, it is same as the Extended Mode operation.

- **NOTE:** The BCM53134S checks only the destination addresses to qualify EAPOL frames. Ethernet type fields, packet type fields, or non-IEEE 802.1Q frames are not checked.

# 2.15 DoS Attack Prevention

The BCM53134S supports the detection of the following DoS (Denial of Service) attack types based on register setting, which can be programmed drop or not to drop each type of DoS packets respectively.

| DoS Attack Type | Description                                                                                                                                                                                |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IP_LAND         | IPDA = IPSA in an IPv4/IPv6 datagram                                                                                                                                                       |  |

| TCP_BLAT        | DPort = SPort in a TCP header carried in an unfragmented IP datagram or in the first fragment of a<br>fragmented IP datagram                                                               |  |

| UDP_BLAT        | DPort = SPort in a UDP header carried in an unfragmented IP datagram or in the first fragment of a<br>fragmented IP datagram                                                               |  |

| TCP_NULLScan    | Seq_Num = 0 and all TCP_FLAGs = 0 in a TCP header carried in an unfragmented IP datagram or in the first fragment of a fragmented IP datagram                                              |  |

| TCP_XMASScan    | Seq_Num = 0, FIN = 1, URG = 1, and PSH = 1 in a TCP header carried in an unfragmented IP datagram or in the first fragment of a fragmented IP datagram                                     |  |

| TCP_SYNFINScan  | SYN = 1 and FIN = 1 in a TCP header carried in an unfragmented IP datagram or in the first fragment of a fragmented IP datagram                                                            |  |

| TCP_SYNError    | SYN = 1, ACK = 0, and SRC_Port<1024 in a TCP header carried in an unfragmented IP datagram or in the first fragment of a fragmented IP datagram                                            |  |

| TCP_ShortHDR    | The length of a TCP header carried in an unfragmented IP datagram or the first fragment of a fragmented IP datagram is less than MIN_TCP_Header_Size                                       |  |

| TCP_FragError   | The Fragment_Offset = 1 in any fragment of a fragmented IP datagram carrying part of TCP data                                                                                              |  |

| ICMPv4_Fragment | The ICMPv4 protocol data unit carried in a fragmented IPv4 datagram                                                                                                                        |  |

| ICMPv6_Fragment | The ICMPv6 protocol data unit carried in a fragmented IPv6 datagram                                                                                                                        |  |

| ICMPv4_LongPing | The ICMPv4 ping (echo request) protocol data unit carried in an unfragmented IPv4 datagram with its Total Length indicating a value greater than the MAX_ICMPv4_Size + size of IPv4 header |  |

| ICMPv6_LongPing | The ICMPv6 ping (echo request) protocol data unit carried in an unfragmented IPv6 datagram with its payload length indicating a value greater than the MAX_ICMPv6_Size                     |  |

#### Table 3: DoS Attacks Detected by BCM53134S

MIN\_TCP\_Header\_Size is programmable between 0 and 255 bytes, inclusive. The default value is set to 20 bytes (TCP header without options).

- MAX\_ICMPv4\_Size is programmable between 0 and 9.6 KB, inclusive. The default value is set to 512 bytes.

- MIN\_TCP\_Header\_Size is programmable between 0 and 9.6 KB, inclusive. The default value is set to 512 bytes.

- The default control setting for all types of DoS attacks is not to drop the DoS attack packet.

- It is globally configurable whether to perform the SA learning operation with the received packets of the DoS attack type defined in the registers, regardless of the individual DoS attack types.

- Once a packet is detected as a DOS attack type that must be dropped, the packet is dropped regardless of ARL forwarding decisions, but its forwarding based on mirroring function is not affected.

# 2.16 Multiple Spanning Tree Protocol

The BCM53134S support up to eight multiple spanning trees. When the EN\_RX\_BPDU bit = 1, the BCM53134S forwards BPDU packets to the management port only.

# 2.17 Software Reset

The BCM53134S provides Software Resets. Software Resets can be triggered by setting the register (page 00h, address 79h).

**NOTE:** Software Reset sets all the register and the table (ARL, VLAN) contents to the default values. Software Reset will not latch in the strap pin values, but the previous latched strap pin values are retained.

# 2.18 BroadSync HD

BroadSync HD is the enhancement to IEEE 802.3 MAC and IEEE 802.1D bridges to support the kind of low-latency isochronous services and guaranteed QoS that is required for many consumer electronics applications.

BCM53134S provides the BroadSync HD feature. BCM53134S always forwards BPDU, MRP packets to CPU for BroadSync HD applications, and handle IEEE 802.1 Time Sync Protocol.

The BCM53134S can identify a packet as a BroadSync HD packet if MAC DA matches with the programmed (registered and configured based on MRP protocols) MAC address. A MAC address can be a multicast or unicast address. The PCP of the incoming BroadSync HD packet can be any value that is programmed. The default values are 4 and 5. There are two dedicated queues for BroadSync HD Class 5 and Class 4 traffic per egress port. The BCM53134S enhances shaping and scheduling for BroadSync HD operation.

### 2.18.1 Time Base and Slot Generation

For BroadSync HD applications, the BCM53134S maintains a time base (32-bit counter) running at a granularity of 1 ns, which can be adjusted by CPU for synchronization with the BroadSync HD time master unit (Switch or Host) through the IEEE 802.1 Time Synchronized (TS) protocol (to be standardized). The TS protocol is implemented by the CPU, which requires the BCM53134S to perform the following operations.

- A received TS protocol packet is timestamped at the ingress port when the first byte (of MACDA) arrives, and is transferred along with the receiving timestamp to the CPU.

- A TS protocol packet initiated by the CPU (to be transmitted at an egress port) is timestamped at the egress port when the first byte (of MACDA) is transmitted, and the transmit timestamp recorded at the egress port is reported back to CPU.

It is required that the time synchronization point peers over an Ethernet link is chosen such that the link delay is perceived as constant, and the protocol exchange occurs at least every 10 ms over every link.

The CPU may be required to speed up or slow down the timebase maintained in BCM53134S based on the TS protocol execution. The BCM53134S provides the time base adjustment mechanism for graceful time changes based on CPU instructions.

In addition, the BCM53134S maintains counter mechanism to generate time slot for BroadSync HD traffic scheduling.

- A Slot is defined as 125 μs, it is used to pace the BroadSync HD Class 5 traffic which has tight jitter requirements;

- A MacroSlot is configurable as 1 ms, 2 ms, or 4 ms (binary number of Slots). It is used to pace the BroadSync HD Class4 traffic, which has relaxed jitter requirements.

The CPU may be required to make the slot wider or narrower based on the TS protocol execution. The BCM53134S provides the slot adjustment mechanism for graceful Slot width changes based on CPU instructions.

# 2.18.2 Transmission Shaping and Scheduling

#### 2.18.2.1 BroadSync HD Class5 Media Traffic

The CoS5 queue is dedicated for BroadSync HD Class 5 traffic only, and a CoS5 packet is always the highest priority to be scheduled for transmission. It is allowed by the Shaper A that operates as follows.

- The Shaper A is an emulation of fixed-bandwidth pipe for Class 5 BroadSync HD traffic with tight jitter-to-handle interference from non-BroadSync HD or Class 4 BroadSync HD traffic, adaptively. Note that the preamble and IPG transmission are not taken into account for the pipe operation.

- Tunable parameters for the Shaper A are listed as follows.

- MaxAVPacketSize indicates the maximum packet size allowed on an AV-Enabled port. It is a global setting using BroadSync HD Max Packet Size register.

- Class5\_BW indicates the reserved bandwidth for Class 5 BroadSync HD traffic at granularity of Byte (per slot, 125 µs). It is a per-port setting.

- Class5\_Window indicates the jitter control for Class5 BroadSync HD transmission. It is a per-port setting.

- At the start of each Slot:

- Reset the credit in the shaping bucket to Class5\_BW, if the queue is empty.

- Reset the credit in the shaping bucket to Class5\_BW, if the queue is not empty and Class5\_Window is set to 0.

- Reset the credit in the shaping bucket to Class5\_BW, if the queue is not empty, Class5\_Window is set to 1, and the credit remained in the shaping bucket is greater than MaxAVPacketSize.

- Add Class5\_BW to the credit in the shaping bucket, if the queue is not empty, Class5\_Window is set to 1, and the credit remained in the shaping bucket is less than or equal to MaxAVPacketSize.

- The credit in the shaping bucket decrements for every byte transmitted for the Class 5 BroadSync HD traffic through the port.

- If the credit reaches 0 before the end of the current slot while transmitting a Class 5 BroadSync HD packet, the

ongoing packet transmission is not interrupted and the credit stays at 0 until being reset at the start of next slot.

- The credit decrements resumes at the next Slot if the ongoing transmission continues.

- As long as the credits in the shaping bucket is greater than 0, a Class 5 BroadSync HD packet is allowed to be scheduled for transmission.

### 2.18.2.2 BroadSync HD Class4 Media Traffic

The CoS4 queue is dedicated for BroadSync HD Class 4 traffic only, and a CoS4 packet always yields to CoS5 traffic (if allowed to be scheduled), but takes precedence over the traffic from CoS0~CoS3 queues or follows the weight ratio between CoS4 and CoS0~CoS3 for transmission scheduling, if it is allowed by the Shaper B that operates as follows.

- The Shaper B is an emulation of fixed bandwidth pipe for Class 4 BroadSync HD traffic with relaxed jitter to handle interference from non-BroadSync HD or Class 5 BroadSync HD traffic adaptively. It also statistically levels the Class 4 BroadSync HD transmission bursts towards the next hop switch to reduce the buffering requirements by using slot (instead of MacroSlot) as the pacing mechanism. The preamble and IPG transmission are not accounted for in the pipe operation.

- Tunable parameters for the Shaper B are listed as follows:

- MacroSlot\_Period indicates the periodic cycle time to shape the Class 4 traffic. It is a global setting to indicate 1 ms, 2 ms, or 4 ms.

- MaxAVPacketSize indicates the maximum packet size allowed on an AV-Enabled port. It is a global setting. (same as for BroadSync HD Class 5 setting)

- Class4\_BW indicates the evenly divided bandwidth share per Slot, which is derived from dividing the reserved bandwidth for Class 4 BroadSync HD traffic at granularity of Byte (per MacroSlot) by the number of slots within a MacroSlot. It is a per-port setting.

- At the start of each slot,

- If the slot is the first one for the current MacroSlot, reset the credit bucket to Class4\_BW+MaxAVPacketSize; (MaxAVPacketSize is used as the deficit base)

- Otherwise, add Class4\_BW to the credit in the shaping bucket.

- The shaping credit bucket decrements for every byte transmitted for the Class 4 BroadSync HD traffic.

As long as the credits in the shaping bucket is greater than or equal to MaxAVPacketSize, a Class 4 BroadSync HD packet is allowed to be scheduled for transmission

### 2.19 CableChecker

The BCM53134S provides cable diagnostic capabilities for unmanaged environments. The actual cable diagnostic feature lies in the PHY functional block. The BCM53134S lets the user monitor the cable diagnostic results through LED display by setting the appropriate bits in the LED refresh registers.

The BCM53134S uses the existing LED display (which is already assigned to various functions) to indicate the cable diagnostic results. Table 4 shows the cable diagnostic result output for each LED function where 1 and 0 represent the LED indication pin status; 1 indicates active and 0 indicates inactive.

NOTE:

- The best way for a user to visualize the cable diagnostic test result through LEDs is to bring out the LINK status bit to the LED display along with other functions to be displayed per port. In this way, the user can observe the cable diagnostic result from the flashing (or lit) LED of other functions while LINK LED is off. The switch turn off the LINK status LED during the cable diagnostic mode.

- The cable diagnostic is expected to be most effective when the user cannot establish the link with the partner.

| LED Function in LED Function Register | Cable Diagnostic Output                    |

|---------------------------------------|--------------------------------------------|

| PHYLED4                               | 1 = Cable diagnostic failed                |

|                                       | 0 = Cable diagnostic passed                |

| LNK                                   | No output during the cable diagnostic mode |

| DPX                                   | 1 = Passed                                 |

|                                       | 0 = Failed                                 |

| ACT                                   | 1 = Passed                                 |

|                                       | 0 = Failed                                 |

| COL                                   | 1 = Passed                                 |

|                                       | 0 = Failed                                 |

| LNK/ACT                               | No output during the cable diagnostic mode |

| DPX/COL                               | 1 = Passed                                 |

|                                       | 0 = Failed                                 |

| SPD10M                                | 1 = Failed                                 |

|                                       | 0 = Passed                                 |

| SPD100M                               | In LED function0 map                       |

|                                       | 1 = Cable diagnostic passed                |

|                                       | 0 = Failed                                 |

|                                       | In LED function1 map                       |

|                                       | 1 = Cable diagnostic failed                |

|                                       | 0 = Passed                                 |

#### Table 4: Cable Diagnostic Output

#### Table 4: Cable Diagnostic Output (Continued)

| LED Function in LED Function Register | Cable Diagnostic Output     |

|---------------------------------------|-----------------------------|

| SPD1G                                 | 1 = Passed                  |

|                                       | 0 = Failed                  |

| 10M/ACT                               | 1 = Failed                  |

|                                       | 0 = Passed                  |

| 100M/ACT                              | In LED function0 map        |

|                                       | 1 = Cable diagnostic passed |

|                                       | 0 = Failed                  |

|                                       | In LED function1 map        |

|                                       | 1 = Cable diagnostic failed |

|                                       | 0 = Passed                  |

| 10–100M/ACT                           | 1 = Failed                  |

|                                       | 0 = Passed                  |

| 1G/ACT                                | 1 = Passed                  |

|                                       | 0 = Failed                  |

| PHYLED3                               | 1 = Failed                  |

|                                       | 0 = Passed                  |

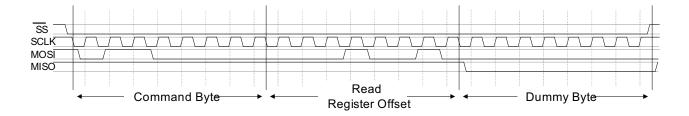

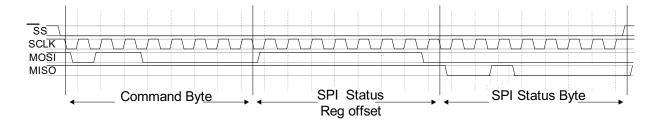

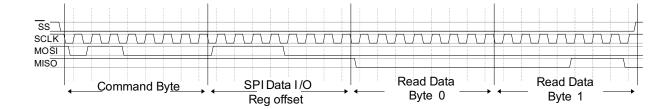

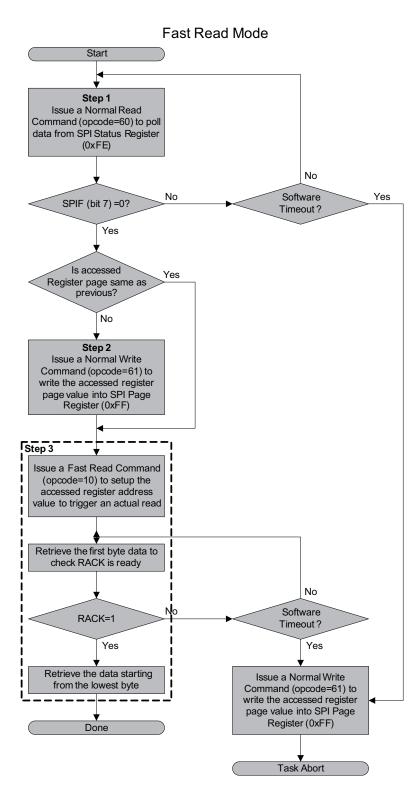

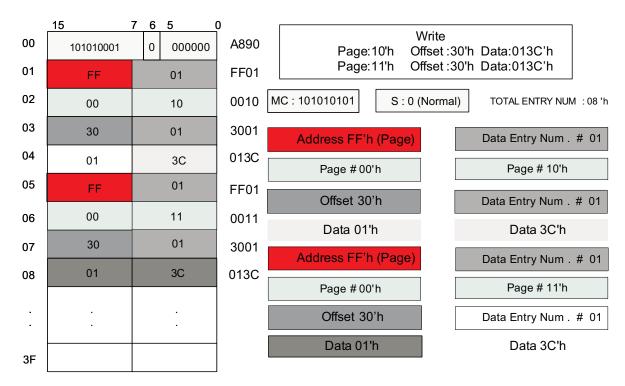

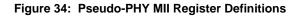

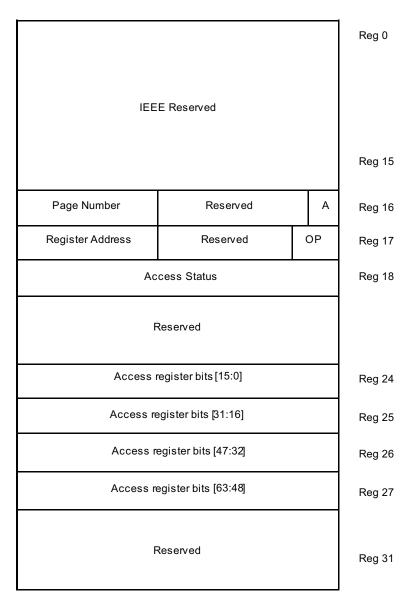

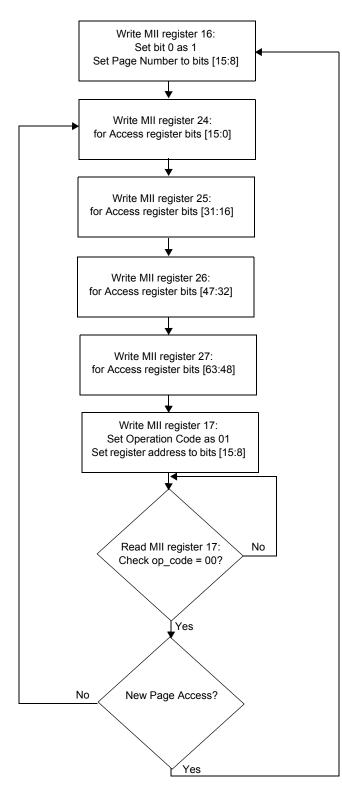

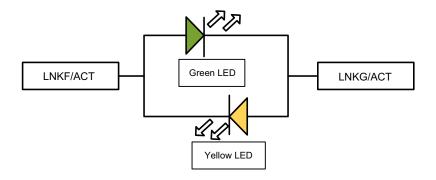

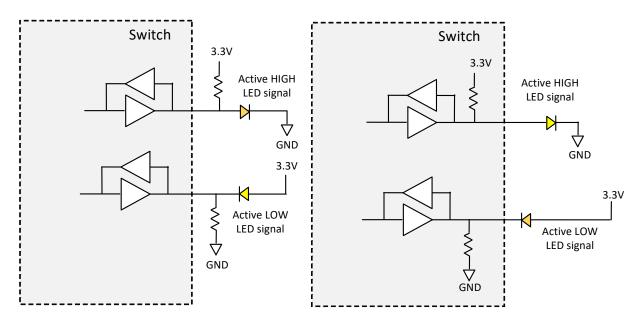

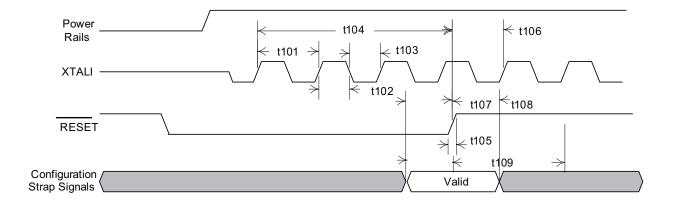

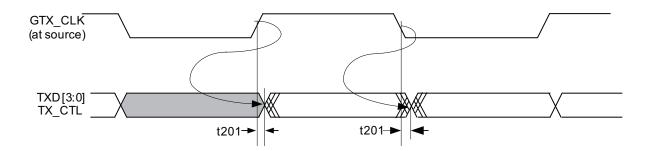

# 2.20 Egress PCP Remarking