#

# BCM53156XU

# Ultra-Low Power Layer2 GE/FE Switch with 10G Uplinks

### **General Descriptions**

Broadcom's BCM53156XU is a family of highly integrated Ethernet switches that are optimally designed for costeffective low-power applications in the SMB, Enterprise, Service-Provider, and SOHO markets that rapidly transition to Gigabit-Ethernet connectivity and beyond.

The BCM53156XU is based on the industry-leading 28 nm RoboSwitch<sup>™</sup> architecture, also known as Robo 2. The product line includes multiple models with 6 to 15 interfaces that support 100M/1GE/2.5GE and 10GE of bandwidth.

The BCM53156XU is designed for standalone low portcount configurations and high port-count configurations with support for cascading.

The BCM53156XU allows customers to design complete product platforms that target new cost-effective low-power applications demanding 1GE/10GbE connectivity. Among those, SMB switch with 10G uplinks, Enterprise switches, routers and security appliances, next generation Industrial Ethernet switches, and Service Provider access equipment.

The BCM53156XU is also designed to support basic applications that include Auto DOS, Auto VOIP, Auto QoS, and more. The product line takes advantage of a low-power integrated ARM Cortex-M7 CPU to offer on-chip support for certain protocols, including Auto IGMP snooping as well as tools for monitoring and troubleshooting. The product line is offered in Commercial-grade as well as Industrial-grade temperature ranges.

### Features

- ARM Cortex-M7 at up to 400 MHz.

- Operational mode: Unmanaged.

- Up to 8×10/100/1000BASE-T ports with integrated ultra-low-power GPHYs.

- Up to 1×10G XFI with KR support.

- 1 × RGMII.

- Switch cascading.

- 16K entry MAC address table.

- 1K multicast group support.

- 128 KB packet buffer.

- srTCM and trTCM meters (support color aware and color blind modes).

- Eight CoS queues per port with priority flow-control.

- IEEE 802.1p, MAC, and DSCP packet classification.

- Auto Loop detection.

- Auto DoS.

- Auto VOIP.

- Auto QOS.

- Auto IGMP snooping.

- 1K packets and bytes counters.

- IEEE 802.3az Energy Efficient Ethernet (EEE).

- Jumbo frame support: up to 9728 bytes.

- 311-pin, 13×13 mm<sup>2</sup> FBGA package.

- JTAG support.

- Includes one UART and MDIO interface, seven I<sup>2</sup>C interfaces, and 9 GPIOs (via the MFIO).

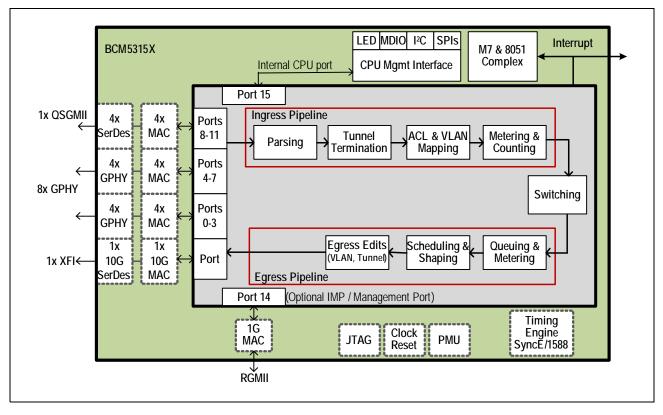

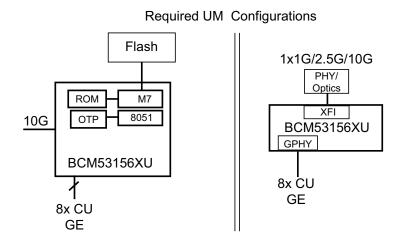

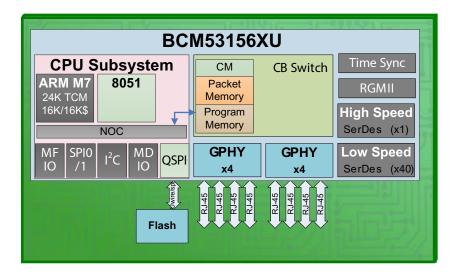

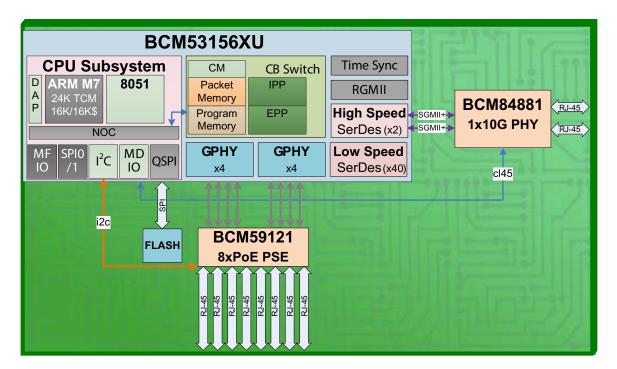

#### Figure 1: Functional Block Diagram

# **Table of Contents**

| Chapter 1: Introduction                           |    |

|---------------------------------------------------|----|

| 1.1 Overview                                      | 8  |

| 1.2 Target Markets                                | 8  |

| 1.3 Operational Mode                              |    |

| 1.4 BCM53156XU Devices                            |    |

| 1.5 System Functional Blocks                      |    |

| 1.5.1 Overview                                    |    |

| 1.5.2 Media Access Controller                     | 14 |

| 1.5.2.1 Receive Function                          | 14 |

| 1.5.2.2 Transmit Function                         |    |

| 1.5.2.3 Flow Control                              |    |

| 1.5.2.3.1 10/100 Mb/s Half-Duplex                 | 15 |

| 1.5.2.3.2 10/100/1000 Mb/s Full-Duplex            |    |

| 1.5.2.3.3 Priority Flow Control                   |    |

| 1.5.3 Integrated 10/100/1000 PHY                  |    |

| 1.5.3.1 Encoder                                   |    |

| 1.5.3.2 Decoder                                   |    |

| 1.5.3.3 Link Monitor                              |    |

| 1.5.3.4 Digital Adaptive Equalizer                |    |

| 1.5.3.5 Echo Canceler                             |    |

| 1.5.3.6 Crosstalk Canceler                        |    |

| 1.5.3.7 Analog-to-Digital Converter               |    |

| 1.5.3.8 Clock Recovery/Generator                  |    |

| 1.5.3.9 Baseline Wander Correction                |    |

| 1.5.3.10 Multimode TX Digital-to-Analog Converter |    |

| 1.5.3.11 Stream Cipher                            |    |

| 1.5.3.12 Wire Map and Pair Skew Correction        |    |

| 1.5.3.13 Automatic MDI Crossover                  |    |

| 1.5.3.14 10/100BASE-TX Forced Mode Auto-MDIX      | 20 |

| 1.5.3.15 PHY Address                              | 20 |

| 1.5.3.16 Super Isolate Mode                       | 20 |

| 1.5.3.17 Standby Power-Down Mode                  | 21 |

| 1.5.3.18 Auto Power-Down Mode                     | 21 |

| 1.5.3.19 External Loopback Mode                   | 21 |

| 1.5.3.20 Full-Duplex Mode                         |    |

| 1.5.3.20.1 Copper Mode                            |    |

| 1.5.3.21 Master/Slave Configuration               | 23 |

| 1.5.3.22 Next Page Exchange                       | 23 |

| 1.5.3.23 XLMAC                                  | 23 |

|-------------------------------------------------|----|

| 1.5.4 Interdevice Interface                     | 24 |

| 1.5.4.1 Switch to Control Plane: CB Tag         | 25 |

| 1.5.4.2 Switch to Control Plane: Time Stamp Tag | 27 |

| 1.5.4.3 Control Plane to Switch: CB Tag         | 27 |

| 1.5.5 MIB Engine                                | 28 |

| 1.5.5.1 MIB Counters                            | 29 |

| 1.5.6 Integrated High-Performance Memory        |    |

| 1.5.7 Robo 2 Switch Core                        |    |

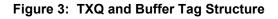

| 1.5.7.1 Buffer Management                       |    |

| 1.5.7.2 Memory Arbitration                      |    |

| 1.5.7.3 Transmit Output Port Queues             |    |

| 1.6 Notational Conventions                      |    |

| Chapter 2: Features and Operation               |    |

| 2.1 Overview                                    |    |

| 2.2 ARM Cortex-M7 Core                          |    |

| 2.3 Software Reset                              |    |

| 2.4 Jumbo Frame Support                         |    |

| 2.5 AutoDOS                                     |    |

| 2.6 AutoVOIP                                    |    |

| 2.7 AutoQoS                                     |    |

| 2.7.1 Egress Scheduling                         |    |

| 2.7.2 Flow Control                              |    |

| 2.7.3 Flood Limiting                            |    |

| 2.8 Auto LoopDetect                             |    |

| 2.8.1 Auto Loop Detect Configurations           |    |

| 2.8.2 Port Shutdown Feature                     |    |

| 2.9 Auto IGMP Snooping                          |    |

| 2.9.1 General IGMP Snooping                     |    |

| 2.9.2 Static Multicast Router Interface         | 40 |

| 2.9.3 Block Unknown Multicast Interface         | 40 |

| 2.9.4 Leave Implementation                      | 40 |

| 2.10 Cascading                                  | 40 |

| 2.11 Cable Diagnosis                            | 40 |

| 2.12 Power-Saving Modes                         | 41 |

| 2.12.1 Auto Power Down Mode                     | 41 |

| 2.12.2 Energy Efficient Ethernet Mode           | 41 |

| Chapter 3: Applications and Configuration       |    |

| 3.1 Overview                                    | 43 |

| 3.2  | 2 Unmanaged Applications (UM)                                         | 43 |

|------|-----------------------------------------------------------------------|----|

|      | 3.2.1 Unmanaged Base Configuration                                    | 43 |

|      | 3.2.2 Unmanaged with Advanced Features                                | 45 |

|      | 3.2.3 High-Speed Unmanaged                                            | 45 |

|      | 3.2.4 Unmanaged Cascade Support                                       | 46 |

| Cha  | pter 4: Software Components                                           |    |

| 4.1  | 1 8051 and M7 Running Environment                                     | 49 |

| 4.2  | 2 M7 Operating System Environment                                     |    |

| 4.3  | 3 Unmanaged Application                                               |    |

| Cha  | pter 5: System Interfaces                                             | 51 |

| 5.1  | 1 Overview                                                            | 51 |

| 5.2  | 2 Copper Interface                                                    | 51 |

|      | 5.2.1 Auto-Negotiation                                                | 51 |

|      | 5.2.2 Lineside (Remote) Loopback Mode                                 |    |

| 5.3  | 3 Frame Management Port Interface                                     |    |

|      | 5.3.1 RGMII Interface                                                 |    |

| 5.4  | 4 SerDes Interface                                                    |    |

|      | 5 Configuration Pins                                                  |    |

|      | 6 Programming Interfaces                                              |    |

| •••• | 5.6.1 SPI Interface                                                   |    |

|      | 5.6.2 SPI Slave                                                       |    |

|      | 5.6.2.1 SPI Transactions                                              |    |

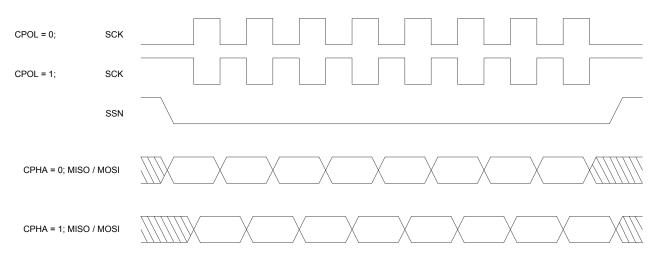

|      | 5.6.2.1.1 Clock Polarity and Phase                                    |    |

|      | 5.6.2.1.2 Fields                                                      |    |

|      | 5.6.2.1.3 Command Word Format                                         |    |

|      | 5.6.2.1.4 Burst Length                                                | 54 |

|      | 5.6.2.1.5 Supported Transactions                                      | 54 |

|      | 5.6.2.1.6 SPIS and Chip Reset                                         |    |

|      | 5.6.2.1.7 Read/Write Status Format                                    |    |

|      | 5.6.2.1.8 SPI Status                                                  |    |

|      | 5.6.2.1.9 ACK/NACK Byte Format                                        |    |

|      | 5.6.2.2 SPI Slave Operation                                           |    |

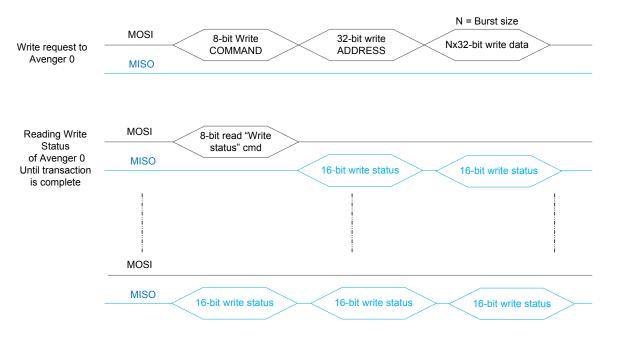

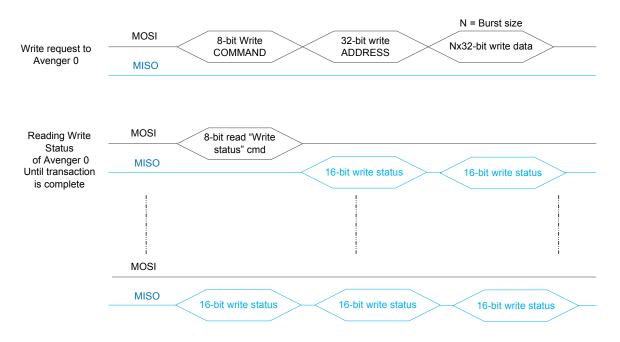

|      | 5.6.2.2.1 Slave Mode Normal Write<br>5.6.2.2.2 Slave Mode Normal Read |    |

|      | 5.6.2.2.3 Slave Mode Fast Read                                        |    |

|      | 5.6.2.2.4 Slave Mode Fast Write                                       |    |

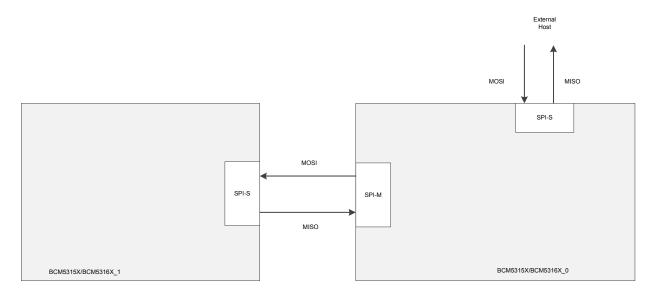

|      | 5.6.3 SPI Master                                                      |    |

|      | 5.6.3.1 SPI Master Operation                                          |    |

|      | 5.6.3.1.1 Master Operation                                            |    |

|      | 5.6.3.1.2 Master Mode Normal Read                                     |    |

|      | 5.6.4 Quad SPI Flash Interface                                        |    |

|      |                                                                       |    |

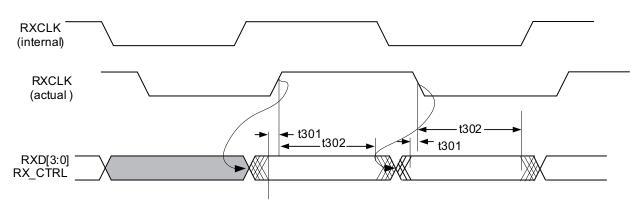

|      | 5.6.5 MDC/MDIO Interface                                | 63 |

|------|---------------------------------------------------------|----|

|      | 5.6.5.1 MDC/MDIO Interface Register Programming         | 63 |

| 5.7  | LED Interfaces                                          | 64 |

| 5.8  | Digital Voltage Regulator (LDO)                         | 65 |

| 5.9  | MFIO Interface                                          | 66 |

| Chap | pter 6: Hardware Signal Definitions                     | 68 |

| 6.1  | I/O Signal Types                                        | 68 |

| 6.2  | Signal Descriptions                                     | 69 |

|      | 6.2.1 13×13 mm <sup>2</sup> Package                     | 69 |

| Chap | pter 7: Pin Assignment                                  | 76 |

| 7.1  | Pin List by Pin Number (13×13 mm2)                      | 76 |

| 7.2  | Pin List by Pin Name (13×13 mm2)                        | 79 |

| 7.3  | Ball Map (13×13 mm2 Package)                            | 82 |

| Chap | pter 8: Electrical Characteristics                      |    |

| 8.1  | Absolute Maximum Ratings                                | 83 |

| 8.2  | Recommended Operating Conditions and DC Characteristics | 84 |

|      | 8.2.1 Standard 3.3V Signals                             | 85 |

|      | 8.2.2 Standard 2.5V Signals                             | 85 |

|      | 8.2.3 REFCLK Input Timing                               | 85 |

|      | 8.2.4 XFI Transmitter Performance Specification         | 86 |

|      | 8.2.5 XFI Transmitter DC Characteristics                | 86 |

|      | 8.2.6 XFI Receiver Input Performance Specification      | 87 |

|      | 8.2.7 XFI Receiver DC Characteristics                   |    |

|      | 8.2.8 RGMII Pin Operation at 2.5V VDDO_RGMII            |    |

|      | 8.2.9 RGMII Pin Operation at 1.5V VDDO_RGMII            |    |

| 8.3  | Power Consumption                                       |    |

|      | 8.3.1 Power Consumption                                 |    |

| Chap | pter 9: Timing Characteristics                          |    |

| 9.1  | Reset and Clock Timing                                  |    |

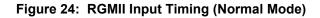

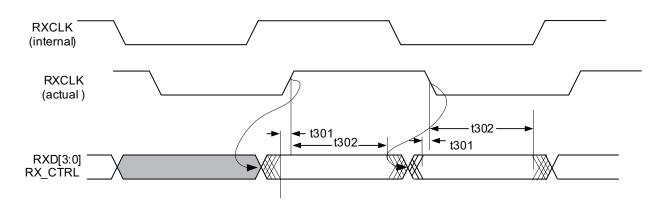

| 9.2  | RGMII Interface Timing                                  |    |

|      | 9.2.1 RGMII Output Timing (Normal Mode)                 | 90 |

|      | 9.2.2 RGMII Output Timing (Delayed Mode)                |    |

|      | 9.2.3 RGMII Input Timing (Normal Mode)                  |    |

|      | 9.2.4 RGMII Input Timing (Delayed Mode)                 |    |

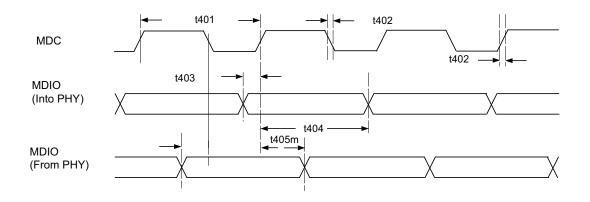

|      | MDC/MDIO Timing                                         |    |

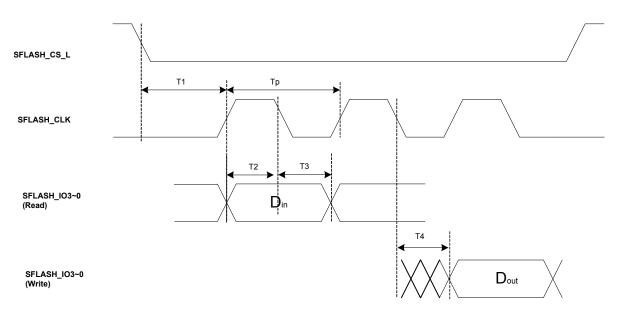

|      | Serial Flash Timing                                     |    |

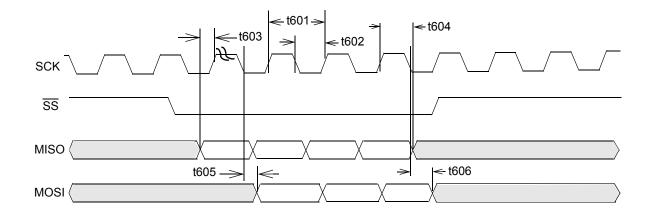

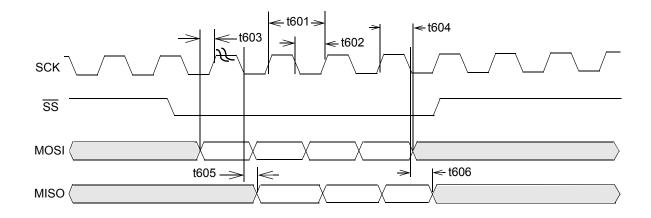

| 9.5  | SPI Interface Timing                                    |    |

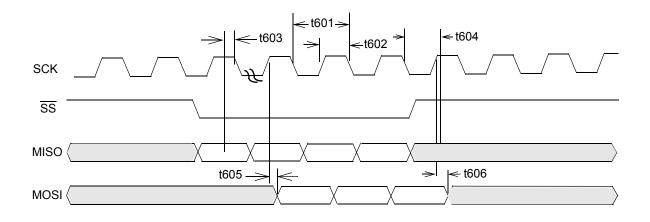

|      | 9.5.1 BCM53156XU SPI-1 Master Interface Timing (A1)     |    |

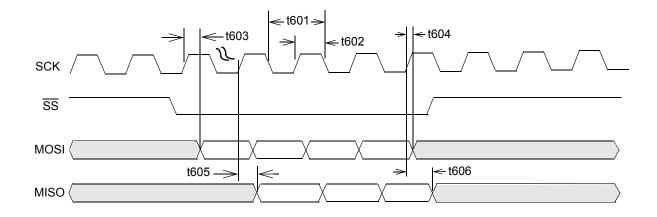

|      | 9.5.2 BCM53156XU SPI-2 Slave Interface Timing (A1)      |    |

| 9.5.3 BCM53156XU SPI-1 Master Interface Timing (B0)                           |     |

|-------------------------------------------------------------------------------|-----|

| 9.5.4 BCM53156XU SPI-2 Slave Interface Timing (B0)                            |     |

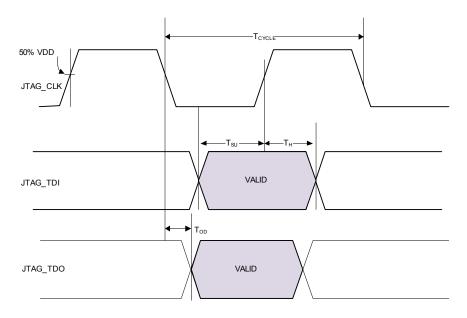

| 9.6 JTAG Interface                                                            |     |

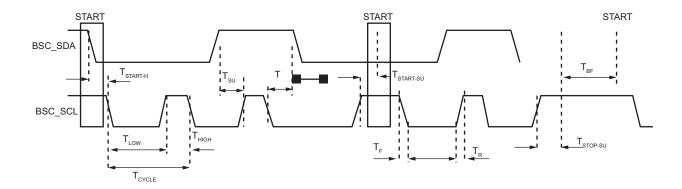

| 9.7 BSC Timing                                                                |     |

| 9.8 Serial LED Interface Timing                                               |     |

| 9.9 SGMII/SerDes Timing                                                       |     |

| 9.10 2.5GE/SerDes Timing                                                      |     |

| 9.11 Synchronous Ethernet Interface                                           | 103 |

| Chapter 10: Thermal Characteristics                                           | 104 |

| 10.1 BCM53156XU/BCM53158XU Package with Heat Sink (35×35×15 mm <sup>3</sup> ) |     |

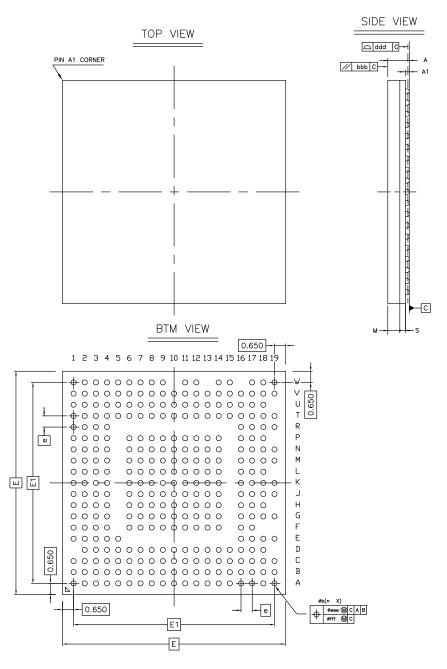

| Chapter 11: Mechanical Information                                            | 105 |

| Chapter 12: Ordering Information                                              |     |

| Revision History                                                              |     |

|                                                                               |     |

# **Chapter 1: Introduction**

### 1.1 Overview

This document provides details of the functional, operational, and electrical characteristics of the Broadcom<sup>®</sup> BCM53156XU. This document is for designers interested in integrating the BCM53156XU switches into their hardware designs and for others who need specific data about the physical characteristics and operation of the BCM53156XU switches.

The BCM53156XU is a highly integrated Ethernet switch that is optimally designed for cost-effective low-power applications in the SMB, Enterprise, Service-Provider, and Industrial-Ethernet markets. The BCM53156XU is the first product in the RoboSwitch<sup>®</sup> product line to introduce 10 GE ports, which are relevant in markets that are rapidly transitioning to Gigabit-Ethernet connectivity anywhere.

The BCM53156XU switch core supports full-duplex packet forwarding bandwidth of 19 Gb/s for all packet lengths (64 byte to 9720 Jumbo frames).

The chip is based on a core technology that supports:

- Eight 10/100/1000BASE-TX ports with integrated Gigabit MACs (GMACs), and integrated PHYs (GPHYs)

- One 10GE/2.5GE/1GE XFI ports with integrated XMACs

- One RGMII port for PHY-less connection to the management agent (available only in full-duplex mode)

- An integrated Motorola SPI-compatible interface

- High-performance, integrated packet buffer memory

- An address resolution engine

The GMACs support full-duplex and half-duplex modes for 10 Mb/s and 100 Mb/s, and full-duplex for 1000 Mb/s. Flow control is supported in half-duplex mode with backpressure. In full-duplex mode, IEEE 802.3x frame-based flow control is supported. The GMACs are IEEE 802.3-compliant and support a maximum frame size of 9720 bytes.

The BCM53156XUX supports advanced ContentAware<sup>™</sup> processing using a compact field processor (CFP). Up to four intelligent ContentAware processes are performed in parallel for every packet. This flexible engine uses TCAM-based architecture which allows wildcard capabilities. Action examples include dropping, changing the forward port map, adding forward port, assigning the priority of a frame, and so on. These advanced ContentAware processes are well suited for access control lists (ACLs) and DoS prevention.

An integrated address management engine provides address learning and recognition functions at maximum frame rates. The address table provides capacity for learning up to 16K unicast addresses. Addresses are added to the table after receiving an error-free packet.

The MIB statistics registers collect receive and transmit statistics for each port and provide direct hardware support for the EtherLike-MIB, MIB II (interfaces), and the first four groups of the RMON MIB. All nine groups of RMON can be supported by using additional capabilities, such as port mirroring/snooping, together with an external microcontroller to process some MIB attributes. The MIB registers can be accessed through the Serial Peripheral Interface Port by an external microcontroller.

# 1.2 Target Markets

The BCM53156XU series targets four main markets:

SMB – The BCM53156XU was designed to support this market segment by providing 1/2.5GE connectivity toward the WAN.

### 1.3 Operational Mode

The BCM53156XU device supports Unmanaged Mode (U) operational modes.

Unmanaged mode (U) – This mode should be used by customers who would like to build the most basic switching platform with a single bridging domain, no support for virtual LANs, that is, IEEE 802.1Q VLANS and no ability to rate limit incoming or outgoing traffic. This unmanaged mode does provide customers with 8 traffic classes per port, a default 1:1 mapping between incoming traffic VLAN priority bits and those queues (p-bits with value X will be mapped to queue X+1) and default WRR scheduling weights for improved scheduling of traffic from the queues (the weights are 1:1:2:2:4:4:8:8).

In this mode, the device is shipped to customers with a basic out-of-the-box configuration that activates the switch in a single, no VLAN support, bridging domain. This basic configuration is available on the device's internal ROM and no additional memory is required. However, customers can get additional functionality to that mentioned above by using an external flash and downloading BRDCM's Advanced Unmanaged software. This software supports, in addition to the basic functionality, Auto-Loopdetect, Auto-Dos, and Auto-VoIP functionality, autoQos, and auto IGMP snooping that are further explained here. This mode is termed "Advanced Unmanaged." Note that this mode is not offered separately from the regular Unmanaged mode (U) as it mainly requires that the end user deploy external flash for additional memory.

| Layer                 | Feature                                      | Unmanaged (U)<br>(* = Features Requires Flash) |

|-----------------------|----------------------------------------------|------------------------------------------------|

| er)                   | Processor                                    | Integrated M7 CPU                              |

| Ň                     | ROM memory for image and config              | Internal ROM + Flash                           |

| р<br>Д                |                                              | Flash is necessary                             |

| varo                  | Operating System                             | Bare Metal                                     |

| m<br>Software, Power) | Software Format Delivered to Customers       | Binary Code                                    |

| System<br>Basic S     | SDK Support                                  | ✓                                              |

|                       |                                              | Initialization RSDK                            |

| Loc                   | Direct Register Access Support               | $\checkmark$                                   |

| len                   | Packet Memory                                | 1 MB                                           |

| (CPU, Memory,         | CPU Memory                                   | 8 KB                                           |

|                       | Cable Diagnostic                             | √*                                             |

|                       | Cascading                                    | √*                                             |

| <b>~</b> .            | EEE power saving (IEEE 802.3az) <sup>a</sup> | ✓                                              |

|                       | AVS3                                         | √*                                             |

|                       | Link Aggregation (LAG)                       | ×                                              |

|                       |                                              |                                                |

#### Table 1: BCM53156XU Operational Modes

#### Table 1: BCM53156XU Operational Modes

| Layer            | Feature                                  | Unmanaged (U)<br>(* = Features Requires Flash) |

|------------------|------------------------------------------|------------------------------------------------|

|                  | Jumbo Frames                             | √ (9720)                                       |

| L2 Forwarding    | Switching/MAC Learning                   | ✓ (16K)                                        |

|                  | Broadcast Storm Control                  | √*                                             |

|                  | VLAN support (multiple bridging domains) | ×                                              |

|                  | VLAN translation                         | ×                                              |

|                  | Isolation group (tree)                   | ×                                              |

| varo             | Ingress Mirroring                        | ×                                              |

| 2012             | Egress Mirroring                         | ×                                              |

| 2                | Traffic Sampling                         | ×                                              |

| -                | CFP support (ACLs)                       | ×                                              |

|                  | AutoLoop                                 | √*                                             |

|                  | AutoVOIP                                 | √*                                             |

|                  |                                          | (256 SA)                                       |

|                  | AutoDOS                                  | √*                                             |

|                  | Queues per port                          | 8                                              |

|                  | IEEE 802.1p Priority mapping             | √*                                             |

|                  |                                          | Through AutoQoS – mapping is fixed             |

|                  | DSCP priority mapping                    | √*                                             |

|                  |                                          | Through AutoQoS – mapping is fixed             |

|                  | Scheduling configurable SP               | √*                                             |

| S                |                                          | Through AutoQoS                                |

| Gos              | Scheduling configurable WRR              | √*                                             |

| L2               |                                          | Through AutoQoS - Weights are configurable     |

|                  | Metering Rate Limiting                   | ×                                              |

|                  | Shaping queue/port                       | ×                                              |

|                  | Hierarchical Shaping                     | ×                                              |

|                  | Flow Control – PAUSE IEEE 802.3x         | √*                                             |

|                  | Flow Control – PFC IEEE 802.1QBB         | √*                                             |

| ant              | Debug CLI                                | ✓                                              |

| me               | RESTful API                              | ×                                              |

| lage             | Rx and Tx Counters                       | ×                                              |

| Management       |                                          |                                                |

| ast              | IGMP Snooping                            | √*                                             |

| Multicast        |                                          |                                                |

| Mu               |                                          |                                                |

| Dueteeste        | LLDP                                     | ×                                              |

| Protocols<br>and | Rapid Spanning Tree                      | ×                                              |

| Advanced         | Cisco MAC-in-MAC                         | ×                                              |

| Features         | Port Extender/IEEE 802.1BR               | ×                                              |

|                  |                                          |                                                |

#### Table 1: BCM53156XU Operational Modes

| Layer                     | Feature                                                      | Unmanaged (U)<br>(* = Features Requires Flash) |

|---------------------------|--------------------------------------------------------------|------------------------------------------------|

| ort                       | IEEE 802.1AS (subset of 1588) – One Step                     | ×                                              |

| Support                   | IEEE 802.1AS (subset of 1588) – Two Steps                    | ×                                              |

|                           | IEEE 802.1Qbv (enhancements ftraffic scheduling)             | ×                                              |

| (TSN)                     | IEEE 802.1Qcc (Stream Reservation Protocol –SRP, HW support) | ×                                              |

| ing                       | Cut-Through mode                                             | ×                                              |

| or<br>Y                   | IEEE 802.1Qav (TSN Forwarding and Queuing)                   | ×                                              |

| Time-Sensitive Networking | AVB (class A and class B)                                    | ×                                              |

a. When EEE is enabled (EEE feature is for GPHY port only), the cut-through latency time is impacted causing very high latency (tens of microsceonds). The selection of either EEE or cut-through does not impact performance since both are not available.

### 1.4 BCM53156XU Devices

The BCM53156 is a 8×GE switch with 10GE/2.5GE/1GE uplinks. See the full SKU list in Section 12: "Ordering Information," on page 106.

The BCM53156XU is offered in one 13×13 mm<sup>2</sup> package with 311 pins.

provides a detailed list of the physical characteristics for the BCM53156XU switch.

#### Table 2: BCM53156XU Family Features

| Features                                                | BCM53156XU            |

|---------------------------------------------------------|-----------------------|

| RGMII (port 14)                                         | 1                     |

| GPHY (ports 0 through 7) 10/100/BASE-T                  | 0                     |

| GPHY (ports 0 through 7) 10/100/1000BASE-T              | 8                     |

| SGMII (ports 8 through 11) 100/1000BASE-FX/2500BASE-FXF | 0                     |

| QSGMII (ports 8 through 11)                             | 0                     |

| XFI (ports 12 through 13) 2.5GE/1GE                     | 0                     |

| XFI (ports 12 through 13) 10GE/2.5GE/1GE                | 1                     |

| MDIO                                                    | 1                     |

| SPI                                                     | 3 (QSPI+2SP)          |

| LED (28 pins)                                           | N/A                   |

| LED (2 pins) <sup>a</sup>                               | Serial                |

| JTAG (w/ 2 jtce)                                        | 1                     |

| 1588                                                    | No                    |

| SyncE                                                   | Yes                   |

| I <sup>2</sup> C                                        | 7                     |

| MFIO                                                    | 9                     |

| WB-FBGA                                                 | 13x13 mm <sup>2</sup> |

| Package                                                 | 0.65 mm               |

|                                                         | pitch                 |

|                                                         | 311 balls             |

| PCB Layers                                              | 4                     |

| Weight                                                  | 511 mg                |

| Ambient Temp <sup>b</sup>                               | 0°C to 70°C           |

a. Serial LED uses two bits from the 28-bit parallel LED. Both cannot be active at the same time.

b. 0°C to 70°C for commercial SKUs; -40°C to +85°C for industrial SKUs.

# **1.5 System Functional Blocks**

### 1.5.1 Overview

The BCM53156XU includes the following blocks:

- Media Access Controller

- Integrated 10/100/1000 PHY

- Interdevice Interface

- MIB Engine

- Integrated High-Performance Memory

- Robo 2 Switch Core

Each of these blocks is discussed in additional detail in the following sections.

### 1.5.2 Media Access Controller

The BCM53156XU contains eight 10/100/1000 MACs, one 1G/2.5G/10G XMACs and four 10/100/1000/2.5G MACs.

The MAC automatically selects the appropriate speed (CSMA/CD or full-duplex) based on the PHY auto-negotiation result. In full-duplex mode, IEEE 802.3x PAUSE frame-based flow control is also determined through auto-negotiation. The MAC is IEEE 802.3, IEEE 802.3u, and IEEE 802.3x-compliant.

#### 1.5.2.1 Receive Function

The MAC initiates frame reception following the assertion of receive data valid indication from the physical layer. The MAC monitors the frame for the following error conditions:

- Receive error indication from the PHY

- Runt frame error if frame is fewer than 64 bytes

- CRC error

- Long frame error if frame is greater than standard max. frame size or 9,720 bytes for jumbo-enabled ports.

**NOTE:** Frames longer than standard max. frame size are considered oversized frames. When jumbo-frame mode is enabled, only the frames longer than 9,720 bytes are bad frames and dropped.

If no errors are detected, the frame is processed by the switch controller. Frames with errors are discarded. Receive functions can be disabled using register settings.

#### 1.5.2.2 Transmit Function

Frame transmission begins with the switch controller queuing a frame to the MAC transmitter. The frame data is transmitted as received from the switch controller. The transmit controller is responsible for preamble insertion, carrier deferral, collision back-off, and inter-packet gap enforcement.

In 10/100 Mb/s half-duplex mode, when a frame is queued for transmission, the transmit controller behaves as specified by the IEEE 802.3 requirements for frame deferral. Following deferral, the transmitter adds 8 bytes of preamble and SFD to the frame data received from the switch controller. If, during frame transmission, a collision is observed and the collision window timer has not expired, the transmit controller asserts jam and then executes the back-off algorithm. The frame is retransmitted when appropriate. On the 16th consecutive collision, the back-off algorithm starts over at the initial state, the collision counter is reset, and attempts to transmit the current frame continue. Following a late collision, the frame is aborted, and the switch controller is allowed to queue the next frame for transmission.

While in full-duplex mode, the transmit controller ignores carrier activity and collision indication. Transmission begins after the switch controller queues the frame and the 96-bit times of IPG have been observed. Transmit functions can be disabled using register settings.

#### 1.5.2.3 Flow Control

The BCM53156XU implements an intelligent flow-control algorithm to minimize the system impact resulting from traffic congestion. Buffer memory allocation is adaptive to the status of each port's speed and duplex mode, providing an optimal balance between flow management and per-port memory depth. The BCM53156XU initiate flow control in response to buffer memory conditions on a per-port basis.

The MACs are capable of flow control in full-duplex mode.

#### 1.5.2.3.1 10/100 Mb/s Half-Duplex

In 10/100 half-duplex mode, the MAC back-pressures a receiving port by transmitting a 96-bit time jam packet to the port. A single jam packet is asserted for each received packet for the duration of the time the port is in the flow-control state.

#### 1.5.2.3.2 10/100/1000 Mb/s Full-Duplex

Flow control in full-duplex mode functions as specified by the IEEE 802.3x requirements. In the receiver, MAC flow-control frames are recognized and, when properly received, set the flow-control pause time for the transmit controller. The pause time is assigned from the 2-byte pause time field following the pause opcode. MAC control PAUSE frames are not forwarded from the receiver to the switch controller.

When the switch controller requests flow control, the transmit controller transmits a MAC control PAUSE frame with the pause time set to maximum. When the condition that caused the flow control state is no longer present, a second MAC control PAUSE frame is sent with the pause time field set to 0.

#### 1.5.2.3.3 Priority Flow Control

Priority Flow Control (PFC) is a mechanism of conveying the per priority XON/XOFF information for 8 different classes using MAC control frames. Unimac provides the flexibility to program the DA, TYPE, and OPCODE fields for the PFC frames. The PFC feature can be independently enabled inside the MAC and pause should be disabled while PFC is operational to ensure IEEE compliance.

### 1.5.3 Integrated 10/100/1000 PHY

There are two integrated quad-PHY blocks in the BCM53156XU. For more information see Copper Interface. The following sections describe the operations of the internal PHY block.

#### 1.5.3.1 Encoder

The PHY is the Ethernet transceiver that appropriately processes data presented by the MAC into an analog data stream to be transmitted at the MDI interface, which performs the reverse process on data received at the MDI interface. The registers of the PHY are read using the Programming Interfaces. The following sections describe the operations of the internal PHY block. For additional information, see Copper Interface.

In 10BASE-T mode, Manchester encoding is performed on the data stream that is transmitted on the twisted-pair cable. The multimode transmit digital-to-analog converter (DAC) performs preequalization for 100m of Category 3 cabling.

In 100BASE-TX mode, the BCM53156XU transmits a continuous data stream over the twisted-pair cable. The transmit packet is encapsulated by replacing the first two nibbles of preamble with a start-of-stream delimiter (/J/K codes) and appending an end-of-stream delimiter (/T/R codes) to the end of the packet. The transmitter repeatedly sends the idle code group between packets. The encoded data stream is serialized and then scrambled by the stream cipher block, as described in Stream Cipher. The scrambled data is then encoded into MLT3 signal levels.

In 1000BASE-T mode, the BCM53156XU simultaneously transmits and receives a continuous data stream on all four pairs of the Category 5 cable. Byte-wide data from the transmit data pins is scrambled when the transmit enable is asserted, and the trellis (a PAM-5 symbol on each of the four twisted-pairs) is encoded into a four-dimensional code group and then inserted into the transmit data stream. The transmit packet is encapsulated by replacing the first two bytes of the preamble with a start-of-stream delimiter, and appending an end-of-stream delimiter to the end of the packet. When the transmit error input is asserted during a packet transmission, a transmit error code group is sent in place of the corresponding data code group. The transmitter sends idle code groups or carrier-extend code groups between packets. Carrier extension is used by the MAC to separate packets within a multiple-packet burst and is indicated by asserting the transmit error signal and placing 0Fh on the transmit data pins while the transmit enable is low. A carrier extend error is indicated by replacing the transmit data input with 1Fh during carrier extension.

The encoding complies with the IEEE 802.3ab standard and is fully compatible with previous versions of the Broadcom 1000BASE-T PHYs.

#### 1.5.3.2 Decoder

In 10BASE-T mode, Manchester decoding is performed on the data stream.

In 100BASE-TX mode, following equalization and clock recovery, the receive data stream is converted from MLT3 to serial nonreturn-to-zero (NRZ) data. The NRZ data is descrambled by the stream cipher block, as described later in this document. The descrambled data is then deserialized and aligned into 5-bit code groups. The 5-bit code groups are decoded into 4-bit data nibbles. The start-of-stream delimiter is replaced with preamble nibbles, and the end-of-stream delimiter and idle codes are replaced with 0h. The decoded data is driven onto the MII receive data pins. When an invalid code group is detected in the data stream, the BCM53156XU asserts the MII receive error (RX\_ER) signal. RX\_ER is also asserted when the link fails, or when the descrambler loses lock during packet reception.

In 1000BASE-T mode, the receive data stream is:

- Passed through the Viterbi decoder

- Descrambled

- Translated back into byte-wide data

The start-of-stream delimiter is replaced with preamble bytes, and the end-of-stream delimiter and idle codes are replaced with 00h. Carrier extend codes are replaced with 0Fh or 1Fh. Decoding complies with IEEE standard IEEE 802.3ab and is fully compatible with previous versions of Broadcom 1000BASE-T PHYs.

#### 1.5.3.3 Link Monitor

In 10BASE-T mode, a link-pulse detection circuit constantly monitors the TRD pins for the presence of valid link pulses.

In 100BASE-TX mode, receive signal energy is detected by monitoring the receive pair for transitions in the signal level. Signal levels are qualified using squelch-detect circuits. When no signal is detected on the receive pair, the link monitor enters the Link Fail state and the transmission and reception of data packets is disabled. When a valid signal is detected on the receive pair for a minimum of 1 ms, the link monitor enters the Link Pass state and the transmit and receive functions are enabled.

Following auto-negotiation in 1000BASE-T mode, the master transceiver begins sending data on the media. The slave transceiver also begins transmitting when it has recovered the master transceiver's timing. Each end of the link continuously monitors its local receiver status. When the local receiver status has been good for at least 1 microsecond, the link monitor enters the Link Pass state, and the transmission and reception of data packets are enabled. When the local receiver status is bad for more than 750 ms, the link monitor enters the Link Fail state and the transmission and reception of data packets are disabled.

#### 1.5.3.4 Digital Adaptive Equalizer

The digital adaptive equalizer removes intersymbol interference (ISI) created by the transmission channel media. The equalizer accepts sampled unequalized data from the analog-to-digital converter (ADC) on each channel and produces equalized data. The BCM53156XU achieves an optimum signal-to-noise ratio by using a combination of feed forward equalization (FFE) and decision feedback equalization (DFE) techniques. Under harsh noise environments, these powerful techniques achieve a bit error rate (BER) of less than  $1 \times 10^{-12}$  for transmissions up to 100m on Category 5 twisted-pair cabling (100m on Category 3 UTP cable for 10BASE-T mode). The all-digital nature of the design makes the performance very tolerant to noise. The filter coefficients are self-adapting to accommodate varying conditions of cable quality and cable length.

#### 1.5.3.5 Echo Canceler

Because of the bidirectional nature of the channel in 1000BASE-T mode, an echo impairment is caused by each transmitter. The output of the echo filter is added to the FFE output to remove the transmitted signal impairment from the incoming receive signal. The echo canceler coefficients are self-adapting to manage the varying echo impulse responses caused by different channels, transmitters, and environmental conditions.

#### 1.5.3.6 Crosstalk Canceler

The BCM53156XU transmits and receives a continuous data stream on four channels. For a given channel, the signals sent by the other three local transmitters cause impairments on the received signal because of near-end crosstalk (NEXT) between the pairs. It is possible to cancel the effect because each receiver has access to the data for the other three pairs that cause this interference. The output of the adaptive NEXT canceling filters is added to the FFE output to cancel the NEXT impairment.

#### 1.5.3.7 Analog-to-Digital Converter

Each receive channel has its own 125 MHz analog-to-digital converter (ADC) that samples the incoming data on the receive channel and feeds the output to the digital adaptive equalizer. Advanced analog circuit techniques achieve the following results:

- Low offset

- High power-supply noise rejection

- Fast settling time

- Low bit error rate

#### 1.5.3.8 Clock Recovery/Generator

The clock recovery and generator block creates the transmit and receive clocks for 1000BASE-T, 100BASE-TX, and 10BASE-T operation.

In 10BASE-T or 100BASE-TX mode, the transmit clock is locked to the 25 MHz crystal input, and the receive clock is locked to the incoming data stream.

In 1000BASE-T mode, the two ends of the link perform loop timing. One end of the link is configured as the master, and the other is configured as the slave. The master transmit and receive clocks are locked to the 25 MHz crystal input. The slave transmit and receive clocks are locked to the incoming receive data stream. Loop timing allows for the cancellation of echo and NEXT impairments by ensuring that the transmitter and receiver at each end of the link are operating at the same frequency.

#### 1.5.3.9 Baseline Wander Correction

1000BASE-T and 100BASE-TX data streams are not always DC-balanced. Because the receive signal must pass through a transformer, the DC offset of the differential receive input can vary with data content. This effect, which is known as baseline wander, can greatly reduce the noise immunity of the receiver. The BCM53156XU automatically compensates for baseline wander by removing the DC offset from the input signal, thereby significantly reducing the probability of a receive symbol error.

In 10BASE-T mode, baseline wander correction is not performed because the Manchester coding provides a perfect DC balance.

#### 1.5.3.10 Multimode TX Digital-to-Analog Converter

The multimode transmit digital-to-analog converter (DAC) transmits PAM-5, MLT3, and Manchester coded symbols. The transmit DAC performs signal-wave shaping that decreases the unwanted high-frequency signal components, reducing electromagnetic interference (EMI). The transmit DAC uses a current drive output that is well-balanced, and therefore, produces very low noise transmit signals.

#### 1.5.3.11 Stream Cipher

In 1000BASE-T and 100BASE-TX modes, the transmit data stream is scrambled to reduce radiated emissions and to ensure that there are adequate transitions within the data stream. The 1000BASE-T scrambler also ensures that there is no correlation among symbols on the four different wire pairs and in the transmit and receive data streams. The scrambler reduces peak emissions by randomly spreading the signal energy over the transmit frequency range and eliminating peaks at certain frequencies. The randomization of the data stream also assists the digital adaptive equalizers and echo/crosstalk cancelers. The algorithms in these circuits require there to be no sequential or cross-channel correlation among symbols in the various data streams.

In 100BASE-TX mode, the transmit data stream is scrambled by exclusive ORing the encoded serial data stream. This is done with the output of an 11-bit wide linear feedback shift register (LFSR), producing a 2047-bit nonrepeating sequence.

In 1000BASE-T mode, the transmit data stream is scrambled by exclusive ORing the input data byte with an 8-bit wide cipher text word. The cipher text word generates each symbol period from eight uncorrelated maximal length data sequences that are produced by linear remapping of the output of a 33-bit wide LFSR. After the scrambled data bytes are encoded, the sign of each transmitted symbol is again randomized by a 4-bit wide cipher text word that is generated in the same manner as the 8-bit word. The master and slave transmitters use different scrambler sequences to generate the cipher text words. For repeater or switch applications, where all ports can transmit the same data simultaneously, signal energy is randomized further by using a unique seed to initialize the scrambler sequence for each PHY.

The receiver descrambles the incoming data stream by exclusive ORing it with the same sequence generated at the transmitter. The descrambler detects the state of the transmit LFSR by looking for a sequence representing consecutive idle code groups. The descrambler locks to the scrambler state after detecting a sufficient number of consecutive idle codes. The BCM53156XU enables transmission and reception of packet data only when the descrambler is locked. The receiver continually monitors the input data stream to ensure that it has not lost synchronization by checking that inter-packet gaps containing idles or frame extensions are received at expected intervals. When the BCM53156XU detects loss of synchronization, it notifies the remote PHY of the inability to receive packets (1000BASE-T mode only) and attempts to resynchronize to the received data stream. If the descrambler is unable to resynchronize for a period of 750 ms, the BCM53156XU is forced into the Link Fail state.

In 10BASE-T mode, scrambling is not required to reduce radiated emissions.

#### 1.5.3.12 Wire Map and Pair Skew Correction

During 1000BASE-T operation, the BCM53156XU has the ability to automatically detect and correct some UTP cable wiring errors. The symbol decoder detects and compensates for (internal to the BCM53156XU) the following errors:

- Wiring errors caused by the swapping of pairs within the UTP cable.

- Polarity errors caused by the swapping of wires within a pair.

The BCM53156XU also automatically compensates for differences in the arrival times of symbols on the four pairs of the UTP cable. The varying arrival times are caused by differing propagation delays (commonly referred to as delay skew) between the wire pairs. The BCM53156XU can tolerate delay skews of up to 64 ns long. Auto-negotiation must be enabled to take advantage of the wire map correction.

During 10/100 Mb/s operation, pair swaps are corrected. Delay skew is not an issue though, because only one pair of wires is used in each direction.

#### 1.5.3.13 Automatic MDI Crossover

During copper auto-negotiation, one end of the link must perform an MDI crossover so that each transceiver's transmitter is connected to the other receiver. The BCM53156XU can perform an automatic media-dependent interface (MDI) crossover, eliminating the need for crossover cables or cross-wired (MDIX) ports. During auto-negotiation, the BCM53156XU normally transmits and receives on the TRD pins.

When connecting to another device that does not perform MDI crossover, the BCM53156XU automatically switches its TRD in pairs when necessary to communicate with the remote device. When connecting to another device that does have MDI crossover capability, an algorithm determines which end performs the crossover function.

During 1000BASE-T operation, the BCM53156XU swaps the transmit symbols on pairs 0 and 1 and pairs 2 and 3 if autonegotiation completes in the MDI crossover state. The 1000BASE-T receiver automatically detects pair swaps on the receive inputs and aligns the symbols properly within the decoder. The automatic MDI crossover function cannot be disabled when in 1000BASE-T mode. During 10BASE-TX and 100BASE-T operation, pair swaps automatically occur within the device and do not require user intervention. The automatic MDI crossover function by default works only when auto-negotiation is enabled. This function can be disabled during auto-negotiation using a register write.

**NOTE:** This function operates only when the copper auto-negotiation is enabled.

#### 1.5.3.14 10/100BASE-TX Forced Mode Auto-MDIX

The automatic MDI crossover function can also be enabled when in forced 10BASE-T or forced 100BASE-TX mode. This feature allows the user to disable the copper auto-negotiation in either 10BASE-T or 100BASE-TX and still take advantage of the automatic MDI crossover function. Whenever the forced link is down for at least 4 seconds, then auto-negotiation is internally enabled with its automatic MDI crossover function until link pulses or 100TX idles are detected. Once detected, the PHY returns to forced mode operation.

NOTE: This function operates only when the copper auto-negotiation is disabled.

#### 1.5.3.15 PHY Address

The BCM53156XU has eight unique PHY addresses for MII management of the internal PHYs. The PHY addresses for each port are as follows,

- PHY address for Port 0 is 1

- PHY address for Port 1 is 2

- PHY address for Port 2 is 3

- PHY address for Port 3 is 4

- PHY address for Port 4 is 5

- PHY address for Port 5 is 6

- PHY address for Port 6 is 7

- PHY address for Port 7 is 8

#### 1.5.3.16 Super Isolate Mode

When in Super Isolate mode, the transmit and receive functions on the Copper Media Dependent Interface are disabled (no link is established with the PHY's copper link partner). Any data received from the switch is ignored by the BCM53156XU and no data is sent from the BCM53156XU.

#### 1.5.3.17 Standby Power-Down Mode

The BCM53156XU can be placed into standby power-down mode using software commands. In this mode, all PHY functions except for the serial management interface are disabled. There are three ways to exit standby power-down mode:

- Clear MII Control register, bit 11 = 0.

- Set the software RESET bit 15.

- Assert the hardware RESET pin.

Read or write operations to any MII register, other than MII Control register, while the device is in the standby power-down mode returns unpredictable results. Upon exiting standby power-down mode, the BCM53156XU remains in an internal reset state for 40 µs and then resumes normal operation.

#### 1.5.3.18 Auto Power-Down Mode

The BCM53156XU can be placed into auto power-down mode. Auto power-down mode reduces device power when the signal from the copper link partner is not present. The auto power-down mode works whether the device is in Autonegotiation Enabled or Forced mode. This mode is enabled by setting bit 5 =1 of Auto Power-Down register. When auto power-down mode is enabled, the BCM53156XU automatically enters the low-power mode when energy on the line is lost, and it resumes normal operation when energy is detected. The energy-detect circuit is always enabled even when a port is in low-power mode. When the BCM53156XU is in auto power-down mode, it wakes up after 2.7s or 5.4s, which determined by bit 4 of Auto Power-Down register, and sends link pulses to the link partner. The BCM53156XU enters normal operation and establishes a link if energy is detected.

**NOTE:** Auto power-down mode is a Broadcom proprietary feature and is based on IEEE standard.

#### 1.5.3.19 External Loopback Mode

The External Loopback mode allows in-circuit testing of the BCM53156XU as well as the transmit path through the magnetics and the RJ-45 connector. External loopback can be performed with and without a jumper block. External loopback with a jumper block tests the path through the magnetics and RJ-45 connector. External loopback without the jumper block tests only the BCM53156XU's transmit and receive circuitry. In 1000BASE-T, 100BASE-TX, and 10BASE-T modes, a jumper block must be inserted into the RJ-45 connector to support external loopback. The jumper block should have the following RJ-45 pins connected together:

1-----3 2-----6 4-----7 5-----8

The following six tables describe how the external loopback is enabled for 1000BASE-T, 100BASE-TX, and 10BASE-T modes with and without a jumper block.

| Register Writes                            | Comments                                                  |

|--------------------------------------------|-----------------------------------------------------------|

| Write 1800h to 1000BASE-T Control register | Enable 1000BASE-T Master Mode                             |

| Write 0040h to MII Control register        | Enable Force 1000BASE-T                                   |

| Write 8400h to Auxiliary Control register  | Enable External Loopback Mode with external loopback plug |

#### Table 4: 1000BASE-T External Loopback Without External Loopback Plug

| Register Writes                            | Comments                                                     |

|--------------------------------------------|--------------------------------------------------------------|

| Write 1800h to 1000BASE-T Control register | Enable 1000BASE-T Master Mode                                |

| Write 0040h to MII Control register        | Enable Force 1000BASE-T                                      |

| Write 8400h to Auxiliary Control register  | Enable External Loopback Mode                                |

| Write 0014h to Auxiliary Control register  | Enable External Loopback Mode without external loopback plug |

#### Table 5: 100BASE-TX External Loopback with External Loopback Plug

| Register Writes                     | Comments                                 |

|-------------------------------------|------------------------------------------|

| Write 2100h to MII Control register | Enable Force 100BASE-TX full-duplex mode |

#### Table 6: 100BASE-TX External Loopback Without External Loopback Plug

| Register Writes                           | Comment                                                      |

|-------------------------------------------|--------------------------------------------------------------|

| Write 2100h to MII Control register       | Enable Force 100BASE-TX full-duplex mode                     |

| Write 0014h to Auxiliary Control register | Enable external loopback mode without external loopback plug |

#### Table 7: 10BASE-T External Loopback with External Loopback Plug

| Register Writes                     | Comments                               |

|-------------------------------------|----------------------------------------|

| Write 0100h to MII Control register | Enable Force 10BASE-T full-duplex mode |

#### Table 8: 10BASE-T External Loopback Without External Loopback Plug

| Register Writes                           | Comments                                                     |

|-------------------------------------------|--------------------------------------------------------------|

| Write 0100h to MII Control register       | Enable Force 10BASE-T full-duplex mode                       |

| Write 0014h to Auxiliary Control register | Enable external loopback mode without external loopback plug |

**NOTE:** To exit the External Loopback mode, a software or hardware reset is recommended.

#### 1.5.3.20 Full-Duplex Mode

The BCM53156XU supports full-duplex operation. While in full-duplex mode, a transceiver can simultaneously transmit and receive packets on the cable.

#### 1.5.3.20.1 Copper Mode

When auto-negotiation is disabled, full-duplex operation can be enabled using register settings.

When auto-negotiation is enabled, the full-duplex capability is advertised for one of the following, depending on the register settings:

- 10BASE-T

- 100BASE-T

- 1000BASE-T

#### 1.5.3.21 Master/Slave Configuration

In 1000BASE-T mode, the BCM53156XU and its link partner perform loop timing. One end of the link must be configured as the timing master, and the other end as the slave. Master/slave configuration is performed by the auto-negotiation function. The auto-negotiation function first looks at the manual master/slave configuration bits advertised by the local PHY and the link partner. If neither PHY requests manual configuration, then the auto-negotiation function looks at the advertised repeater/DTE settings. If one PHY is advertised as a repeater port and the other is advertised as a DTE port, then the repeater port is configured as the master and the DTE port as the slave. Each end generates an 11-bit random seed if the two settings are equal, and the end with the higher seed is configured as the master. If the local PHY and the link partner generate the same random seed, then auto-negotiation is restarted.

If both ends of the link attempt to force the same manual configuration (both master or both slave), or the random seeds match seven consecutive times, then the BCM53156XU sets the Master/Slave Configuration Fault bit in the 1000BASE-T Status register, and auto-negotiation is restarted. This is used to set the BCM53156XU to manual master/slave configuration or to set the advertised repeater/DTE configuration.

#### 1.5.3.22 Next Page Exchange

The 1000BASE-T configuration requires the exchange of three auto-negotiation next pages between the BCM53156XU and its link partner. Exchange of 1000BASE-T Next Page information takes place automatically when the BCM53156XU is configured to advertise 1000BASE-T capability.

The BCM53156XU also supports software controlled Next Page exchanges. This includes the three 1000BASE-T Next Pages, which are always sent first. The BCM53156XU automatically generates the appropriate message code field for the 1000BASE-T pages. When the BCM53156XU is not configured to advertise 1000BASE-T capability, the 1000BASE-T Next Pages are not sent.

When the BCM53156XU is not configured to advertise 1000BASE-T capability, the BCM53156XU does not advertise Next Page ability.

#### 1.5.3.23 XLMAC

XLMAC is used for the implementation of 10G Ethernet layer for the BCM53156XU. The XLMAC core is designed as a single module, supporting four 10G/2.5G/1G/100M/10M MACs. The basic idea is to have a single core optimized for multi-lane operation to save area and power.

### 1.5.4 Interdevice Interface

The BCM53156XU can connect to two types of external devices: another BCM53156XU (cascade) and/or and external processor (CP). The information required for these two application is similar and uses a common header.

The processor can be connected to any port including the internal processor. In Robo terminology, this port is designated as an IMP (internal management port). Frames that are sent to these destinations use the same forwarding rules as any other destination, for example DLIs. There are various ways frames can be directed to each of these destinations including the CFP, ARL, and various filters. Part of the DLI instruction could be to insert the CB tag which provides additional information to aid in processing the frames.

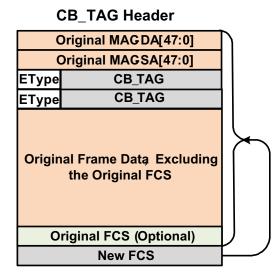

There is one type of IMP header designs which the BCM53156XU supports: CB TAG – 8B CB tag which is inserted directly after the MAC-SA

- This format is parseable via the CT-TAG Ethertype.

- This format might include an optional timestamp with a separate Ethertype.

#### Figure 2: IMP/CB Header Formats

The following rules and guidelines are used for:

- All frames on a cascade port will carry the CB tag.

- Traffic on the IMP port may or may not have the CB tag.

- Normal processing (for example, a port is the destination of the frame) can be sent without a tag.

- When a CB receives a frame with a CB\_TAG, the SPG, SLI, and VSI are reconstituted based on information in the tag. It is presented to the ARL lookups as if the frame was processed by the receive logic.

- There are few exceptions to this i.e. traps, mirroring and directed forwarding.

- After the tag is parsed it is removed.

- **NOTE:** For unicast, multicast, traps, and exception forwarding, it is intended that the source information (SPG, LIN, VSI) is populated in the receive header. This enables the CPU to use this in processing to determine the how to forward the frame. In addition, it is expected the CPU properly sets these fields when it sends a frame to the switch which is sent out.

The Switch to CP and CP to Switch tag formats are purposely defined to be consistent across the IMP and Cascade modes. The forwarding codes (fwd\_op) are defined to allow the hardware to interpret the intended function from the code point regardless of the specific IMP or Cascade type in most cases.

#### 1.5.4.1 Switch to Control Plane: CB Tag

This tag is used to communicate information to an attached CPU or cascaded BCM53156XU. The format and fields are defined in the following tables. The tag is attached to frames using editing directives. The directive could be associated with a port (PET table) or DLI. The Ethertype for this tag is taken from a configuration register. The format and fields are defined in Table 9.

#### Table 9: Switch to CB TAG Format

| 15 | 14        | 13       | 12        | 11                                                     | 10                                   | 09 | 08 | 07 | 06                     | 05 | 04 | 03 | 02 | 01 | 00 |

|----|-----------|----------|-----------|--------------------------------------------------------|--------------------------------------|----|----|----|------------------------|----|----|----|----|----|----|

|    | Ethertype |          |           |                                                        |                                      |    |    |    |                        |    |    |    |    |    |    |

|    | тс        |          | D         | Р                                                      | P FWD_OP                             |    |    |    | LBH/TRAP_GROUP/SPP/DPP |    |    |    |    |    |    |

|    | DI        | EST[11:0 | ] - deper | nds on FWD_OP {for example, DLLI/DG/EXCEPTION} R R SPG |                                      |    |    |    |                        |    | G  |    |    |    |    |

|    | SPG       |          | Т         |                                                        | N_VSI [11:0] (VSI or LIN based on T) |    |    |    |                        |    |    |    |    |    |    |

#### Table 10: Switch to CP Header Format Fields

| Field          | Function                                                                                                                              |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Ethertype      | Configured value                                                                                                                      |

| ТС             | TC value classified for the packet by the switch                                                                                      |

| DP             | Discard precedence                                                                                                                    |

| DEV            | Source device identifier; configured by software                                                                                      |

| SPG            | Source Port Group – SPG determined for the frame                                                                                      |

| FWD_OP         | Forwarding Operation – see table                                                                                                      |

| Т              | LIN Type indicator. 0 is LIN, 1 is PV format                                                                                          |

| N_VSI          | Source Local Logical Interface: If T = 1 (type PV), SLLI = {1,0,SPG}; VSI=N_VSI else(type LIN)<br>SLLI={0,N_VSI}; VSI=LIN2VSI(N_VSI); |

| DEST - overlay | Overlay field with one of the following depending on FWD_OP                                                                           |

| DLLI           | Destination Logical Local Interface: If FWD_OP = UNICAST                                                                              |

| DG             | Destination Group (multicast/broadcast): If FWD_OP = MULTICAST                                                                        |

| EXCEPTION      | Exception – Identifies the reason a trap was triggered (TRAP, SLIC, CFP): If FWD_OP = TRAP                                            |

| LBH - overlay  | Trap Group/Load Balancing Hash : If FWD_OP=TRAP, TRAP_GROUP else LBH                                                                  |

| LBH            | Load balancing hash- Valid for all op codes except 2                                                                                  |

| Trap_group     | Trap group for the SLICT and CFP traps in FWD_OP=2                                                                                    |

| SPP            | Source Physical Port for traps (FWD_OP=2)                                                                                             |

| DPP            | Destination Physical Port                                                                                                             |

| RSVD           | Reserved – write as zero, ignore on receipt                                                                                           |

The forwarding operation (FWD\_OP) field defines the content of the DEST field and provides information to the CPU regarding why the frame was delivered. The DEST field in the header is overlay with number of meanings summarized in the following table.

| FWDOP          | Function                            | DEST                      | LRN? | TG/LBH/SPP | Notes – processing at EPP                                                                                                                                                      |

|----------------|-------------------------------------|---------------------------|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0              | CP Directed<br>Forwarding           | 0                         | No   | DPP        | Frame is directly sent on port specified by LBH/DPP field.                                                                                                                     |

| 0              | Unicast<br>Directed<br>Forwarding   | DLLI                      | Yes  | LBH        | Unicast forwarding with known destination, that is, the DLI. The SPG, N_VSI, and T fields are used to reconstitute the SLI for the frame before the ARL Source lookup is done. |

| 1              | Multicast<br>Directed<br>Forwarding | DG                        | Yes  | LBH        | Multicast forwarding with known destination i.e. DG. The SPG, N_VSI, and T fields are used to reconstitute the SLI for the frame before the ARL Source lookup is done.         |

| 2 <sup>a</sup> | SA Learn                            | SA_LRN<br>(trap_id)       | Yes  | LBH        | Learning message: This is generated based on SA Miss in the source device ARL lookup. The SPG, T and N_VSI are used to in the ARL lookup. This is converted to CA_SA_LRN trap. |

| 2 <sup>a</sup> | SA Move                             | SA_MOVE<br>(trap_id)      | Yes  | LBH        | SA Move message: This is generated based on SA move in the source device ARL lookup. The SPG, T and N_VSI are used to in the ARL lookup. This is converted to CA_SA_LRN trap.  |

| 2 <sup>a</sup> | Mirror                              | 128-191<br>(mirror_ld)    | No   | LBH        | This is a copy generated due to mirroring, the mirror id is extracted from the DEST and the MTGT is used to determine how the frame is handled.                                |

| 2 <sup>a</sup> | Trap                                | 1-127 (trap_id)           | No   | SPP        | This is a copy generated due to a trap condition. The trap_id is extracted from the DEST field and the TCT table will govern the handling of this frame.                       |

| 2 <sup>a</sup> | SLIC_TRAP                           | 256-511<br>(slic_trap)    | No   | Trap_group | This is a copy generated due to a SLIC trap condition. The trap_group is extracted from the LBH field and the MTGT table is use to determine how the frame is handled.         |

| 2 <sup>a</sup> | CFP_TRAP                            | 2048-3071<br>(action_idx) | No   | Trap_group | This is a copy generated due to a CFP trap condition. The trap_group is extracted from the LBH field and the MTGT table is use to determine how the frame is handled.          |

| 2 <sup>a</sup> | NULL TAG                            | 0x0                       | Yes  | X          | NOP TAG – CB tag is removed and processed as if it arrived on the CPU port (backwards compatibility so all frames can have a tag), This use and unused trap_group code point.  |

| 3–7            | Reserved                            | n/a                       | n/a  | Na/        | Reserved for future use.                                                                                                                                                       |

| Table 11: I | IMP Header F | Forwarding | <b>Operation:</b> | Switch to CP |

|-------------|--------------|------------|-------------------|--------------|

|-------------|--------------|------------|-------------------|--------------|

a. For FWD\_OP = 2 the DEST is defined as an EXCEPTION following the encoding shown in Figure 23.

Here are some notes on processing frames at the CPU/Cascaded Device:

- The CB tag is removed on ingress.

- If fwd\_op = 0x0 and DLLI is zero, a valid destination was not determined by the switch (DLF destination lookup failure).

- Flooding uses a multicast forwarding with a zero DG. In this case, the flooding map (pg\_map) comes from the VSIT based on the VSI in the frame (or LIN2VSI).

- Multicast is handled by used the DG as multicast group.

- For FWD\_OP = 2 the encoding the DEST field is used to identify the type of frame (SA-Learn, Mirror, TRAP). The encoding follows the EXCEPTION space shown in Figure 23.

- The DEV field must be preserved if the frame is sent to a CPU with CB\_TAG. This allows the CPU to determine which

of the two devices the originated exception frame.

- SA learning and SA movement traps are converted to cascaded version of the trap and the {vsi, smac} is inserted in the ARL table if possible.

- Mirror implies the frame was mirrored or sampled; the mirror\_group is extracted from the DEST field and the mirror is handled group gives further information or will be used by a cascaded BCM53156XU to process the mirror.

- SA learn packets will be locally learned and converted to local cascaded traps for cascade processing.

• The trap packet uses the trap\_group to process the frame. Note this is the only format that has a SPP versus a SPG.

#### 1.5.4.2 Switch to Control Plane: Time Stamp Tag

This section describes the tag used from the switch to CPU to send the time stamp. This tag is added using an egress editing directive. The format and fields are defined in the following tables. The Ethertype for this tag is taken from a configuration register.

#### Table 12: Egress CB TS Tag

| 15 | 14               | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----|------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    | Ethertype        |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|    | TIMESTAMP[47:32] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|    | TIMESTAMP[31:16] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|    | TIMESTAMP[15:0]  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

The Ethertype is taken from a software configured register. Timestamp is the 48 bit value sampled at Start of Packet when the frame arrived.

#### 1.5.4.3 Control Plane to Switch: CB Tag

This section describes the tag used from the Control Plane to Switch. The fields are the same as the Switch to CP format described above. Normal frame processing (Unicast, Multicast, and Flooding) rely on the SPG, T and N\_VSI field being set properly by the CPU. As noted before, this fields will be valid for frames received by the CPU. It is therefore possible, to direct this frame to a DLI by simply populating the DLI, FWD\_OP and sending the frame back into the switch using this format. The following notes apply to sending frames from the CPU:

- To send a Unicast frame out a port group ; Frame learned by ARL and egress edits ARE applied:

- Set FWD\_OP=0 to Unicast Directed Forwarding

- Set DEST = DLLI frame will be forwarded based specified DLI

- Set T, SPG, N\_VSI frame will be learned in this context

- To send a Unicast frame out a physical port without any checks (VLAN membership, STP, or filters); Frame is not learned by ARL and egress edits ARE NOT applied:

- Set FWD\_OP=0 to Unicast Directed Forwarding

- Set DEST = 0

- Set LBH/DPP field to desired port (DPP); Note this is the only format that has a DPP vs DPG.

- To send a frame to a multicast group:

- Set FWD\_OP=1 to Multicast Directed Forwarding;

- Set DEST to DG frame will be forwarded based specified DLI

- Set T, SPG, N\_VSI the SLLID to SLLID for frame will be derived from these fields for source port knock-out.

- To send a frame and have the switch forward the frame; Frame is learned by ARL:

- Send the frame without the IMP/CP tag

### 1.5.5 MIB Engine

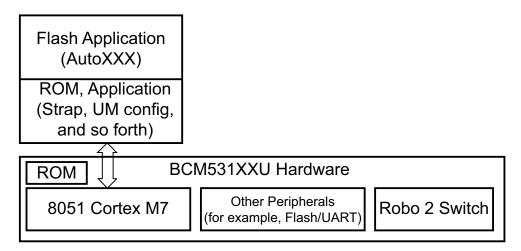

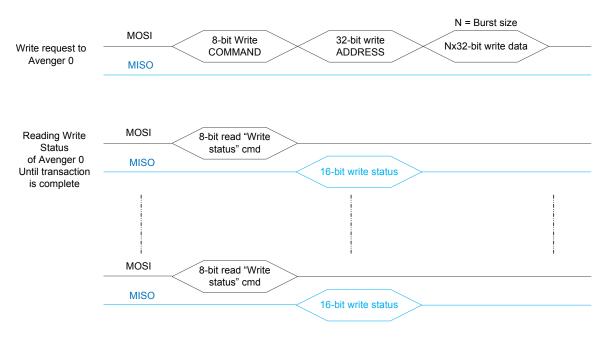

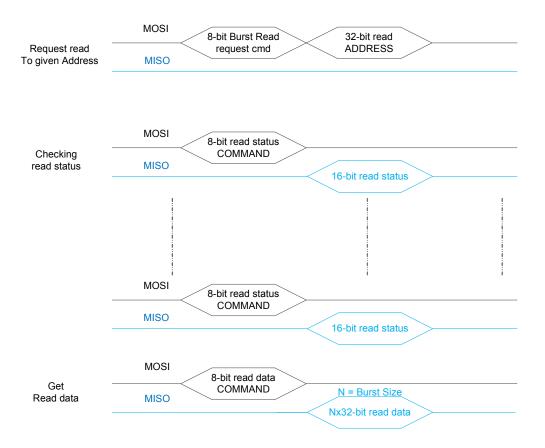

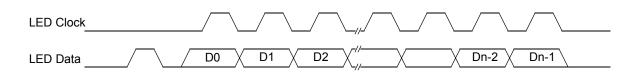

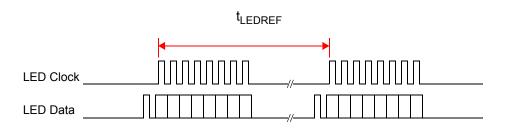

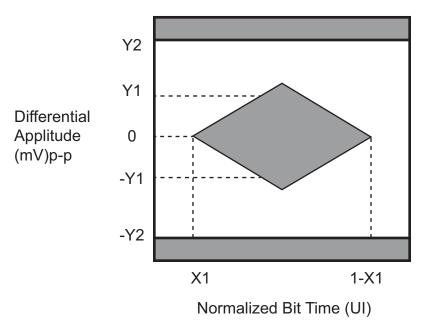

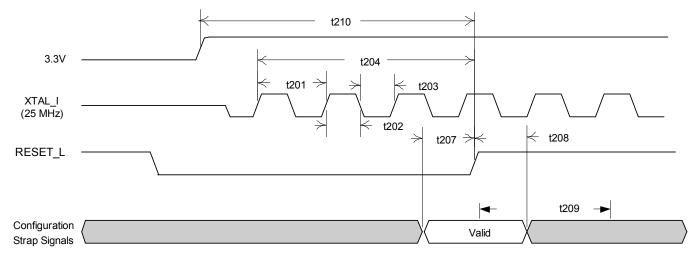

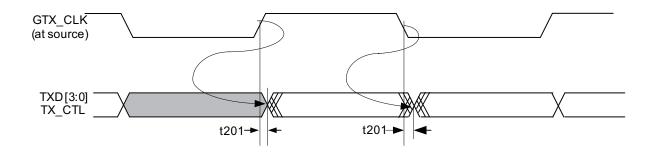

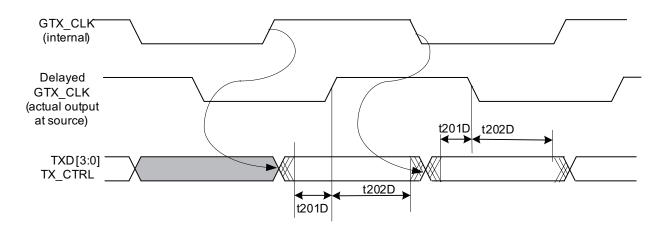

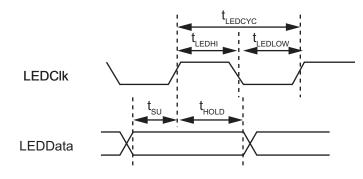

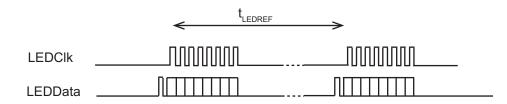

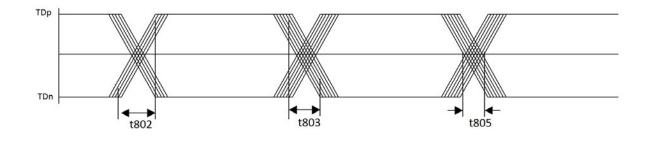

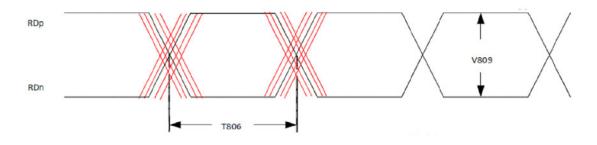

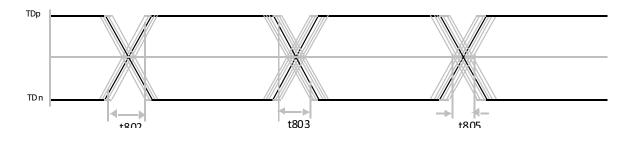

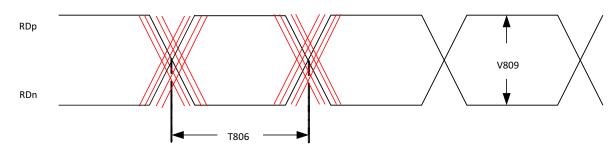

The MIB Engine is responsible for processing status words received from each port. Based on whether it is a receive status or transmit status, appropriate MIB counters are updated. The BCM53156XU implements 66 MIB counters on a per-port basis. MIB counters can be categorized into three groups: receive-only counters, transmit-only counters, and receive or transmit counters. This latter group can, as a group, be selectively steered to the receive or transmit process on a per-port basis. The section below describes each individual counter.