# Integrated 10/100BASE-T/TX Six-Port Switch

#### GENERAL DESCRIPTION

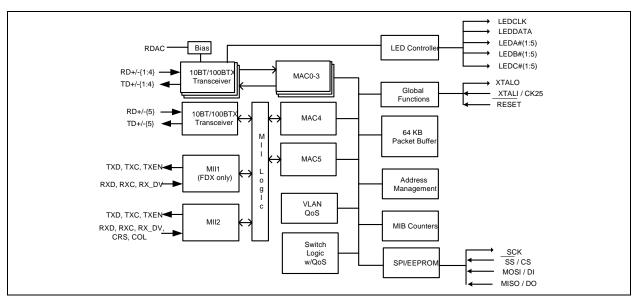

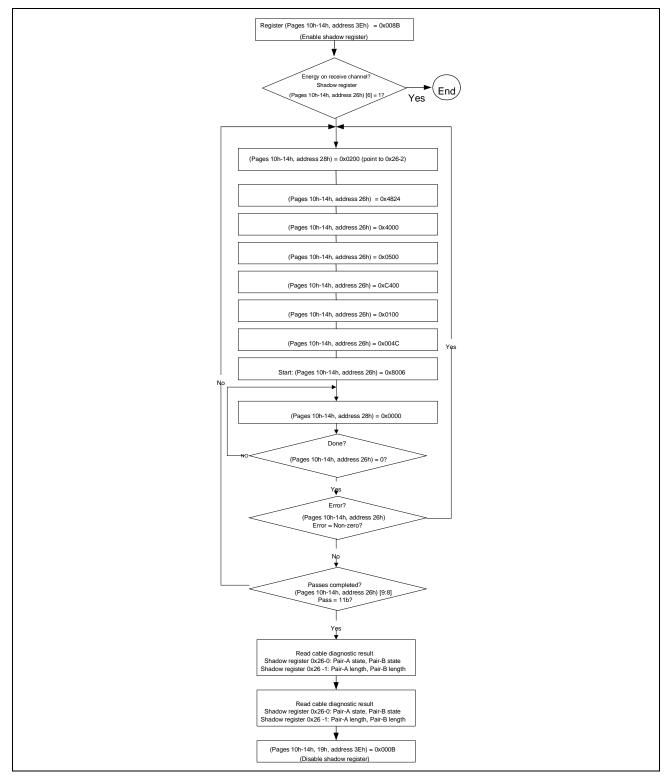

The BCM5325F is a six-port 10/100BASE-T/TX integrated switch targeted at cost-sensitive Fast Ethernet managed switch systems. The device contains five fullduplex 10BASE-T/100BASE-TX Fast Ethernet transceivers, each of which performs all of the physical layer interface functions for 10BASE-T Ethernet on CAT 3, 4, or 5 unshielded twisted-pair (UTP) cable and 100BASE-TX Fast Ethernet on CAT 5 UTP cable. 100BASE-EFX is supported through the use of external fiber optic transceivers.

The BCM5325F device provides a very highly integrated solution. It combines all of the functions of a high-speed switch system, including packet buffer, transceivers, media access controllers (MACs), address management and a non-blocking switch controller, into a single monolithic 0.18-µm CMOS device. It complies with the IEEE 802.3, 802.3u, and 802.3x specifications, including the MAC control Pause frame and auto-negotiation subsections, providing compatibility with all industry-standard Ethernet and Fast Ethernet devices. This function requires only a small low-cost microcontroller to initialize and configure the device.

#### FEATURES

- Six-port, 10/100 Mbps integrated switch controller fully non-blocking configuration

- Five integrated 10/100BASE-T/TX/EFX IEEE 802.3u compliant transceivers—fifth transceiver can be connected to external MII interface.

- Integrated full-duplex capable IEEE 802.3x-compliant MACs

- 64 KB on-chip packet buffer

- Two configurable MII interfaces

- MII port connection for TX/FX uplink.

- Reversed MII for CPU.

- Integrated address management—supports up to 1K unicast addresses

- Port mirroring and Layer-3 IGMP snooping

- IEEE 802.1p QoS packet classification with four priority queues and DSCP priorities in IPv4 and IPv6

- 16 entries IEEE 802.1q-based and Port-based VLAN

- Supports IEEE 802.1x EAPOL higher layer protocol

- EEPROM (93C46) allows further un-managed capabilities

- 25-MHz crystal or oscillator

- Low-power 3.3/1.8V, 0.18 µm CMOS technology

- HP auto-MDIX function hardware selectable

- 128-pin MQFP package.

- Ingress/egress rate control.

- · Protected port capability.

- MPin compatible with BCM5325.

- DTE/DPM power over Ethernet detection

Figure 1: Functional Block Diagram

## **REVISION HISTORY**

| Revision     | Date     | Description                                                                                                         |

|--------------|----------|---------------------------------------------------------------------------------------------------------------------|

| 5325F-DS14-R | 09/16/08 | Updated:                                                                                                            |

|              |          | • "FEATURES"                                                                                                        |

|              |          | "Rate Control Register" on page 154.                                                                                |

| 5325F-DS13-R | 04/22/08 | Updated:                                                                                                            |

|              |          | <ul> <li>Table 30, "Port 4 and MII Ports Configurations Examples," on page 64</li> </ul>                            |

|              |          | Removed                                                                                                             |

|              |          | <ul> <li>Figure 28, "Electrical Characteristics," on page 66.</li> </ul>                                            |

|              |          | Figure 33, "VDDBIAS Circuitry," on page 82.                                                                         |

| 5325F-DS12-R | 06/01/07 | Added:                                                                                                              |

|              |          | <ul> <li>"100BASE-Enhanced FX" on page 23</li> </ul>                                                                |

|              |          | • Vidiff (for full threshold and half threshold) and Vicm to Table 171, "Recommended                                |

|              |          | Operating Conditions," on page 177.                                                                                 |

|              |          | <ul> <li>TDV cm and VO symbols to Table 172, "Electrical Characteristics," on page 178.</li> </ul>                  |

| 5325F-DS11-R | 03/06/07 | Updated:                                                                                                            |

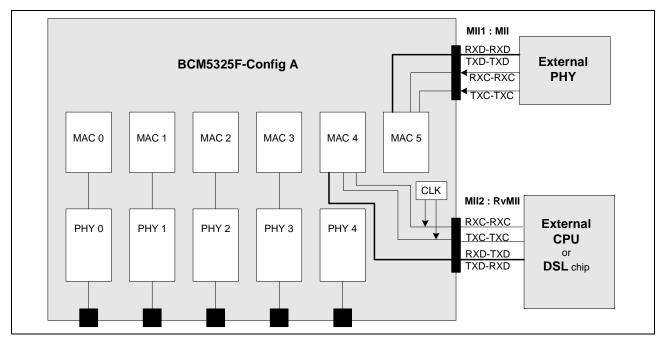

|              |          | <ul> <li>Figure 23, "MII Configuration A," on page 64.</li> </ul>                                                   |

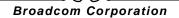

|              |          | • Figure 24, "MII Configuration B," on page 65.                                                                     |

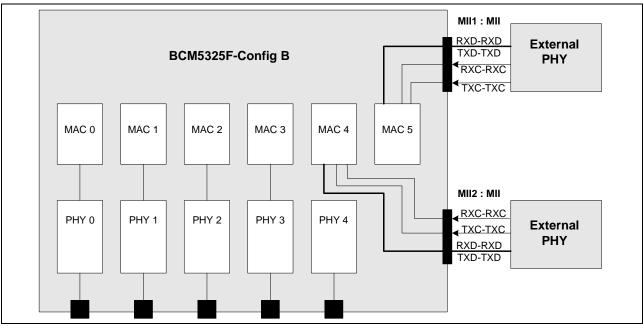

|              |          | • Figure 25, "MII Configuration C," on page 65.                                                                     |

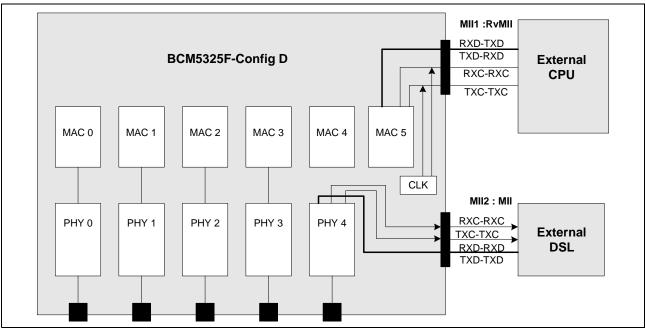

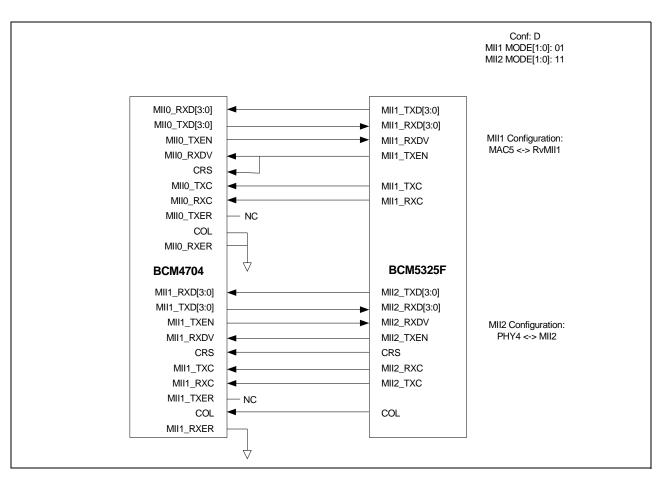

|              |          | • Figure 26, "MII Configuration D," on page 66.                                                                     |

|              |          | Figure 27, "MII Configuration E," on page 66.                                                                       |

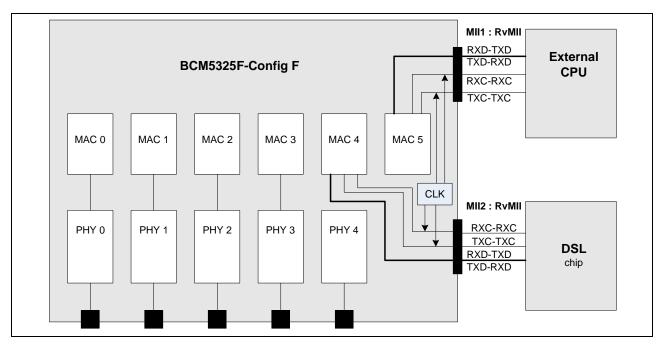

|              |          | Figure 28, "MII Configuration F," on page 67.                                                                       |

|              |          | Table 172, "Electrical Characteristics," on page 177.                                                               |

|              |          | <ul> <li>Table 173, "128-MQFP Thermal Characteristics—Without Heat Sink (2-Layer PCB),"<br/>on page 178</li> </ul>  |

|              |          | Added:                                                                                                              |

|              |          | <ul> <li>Table 174, "128-MQFP Thermal Characteristics—Without Heat Sink (4-Layer PCB),"<br/>on page 178.</li> </ul> |

|              |          | • Table 175, "128-MQFP Thermal Characteristics—With Heat Sink," on page 178.                                        |

| 5325F-DS10-R | 12/22/06 | Updated:                                                                                                            |

|              |          | Table 29, "Pseudo PHY MII Register Definitions," on page 63.                                                        |

| 5325F-DS09-R | 11/02/06 | Updated:                                                                                                            |

|              |          | Table 41 on page 88.                                                                                                |

|              |          | Added:                                                                                                              |

|              |          | <ul> <li>"LED Flash Control Register" on page 95.</li> </ul>                                                        |

|              |          | <ul> <li>"LEDa Control Register" on page 95.</li> </ul>                                                             |

|              |          | <ul> <li>"LEDb Control Register" on page 96.</li> </ul>                                                             |

|              |          | <ul> <li>"LEDc Control Register" on page 96.</li> </ul>                                                             |

| 5325F-DS08-R | 07/18/06 | Updated:                                                                                                            |

|              |          | <ul> <li>TXD[0] should be pulled down during power-up ("MII1_TXD[0]" on page 81).</li> </ul>                        |

|              |          | <ul> <li>TXD[1] should be pulled down during power-up ("MII1_TXD[1]" on page 81).</li> </ul>                        |

|              |          | <ul> <li>"DNC" on page 83)"Ingress Mirror Divider Register" on page 106.</li> </ul>                                 |

|              |          | <ul> <li>"Egress Mirror Divider Register" on page 108.</li> </ul>                                                   |

### **Data Sheet**

09/16/08

| Revision     | Date     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5325F-DS07-R | 04/19/06 | <ul> <li>Updated:</li> <li>"MIB Engine" on page 45.</li> <li>Table 142, "IEEE 802.1Q VLAN Registers (Page 0x34)," on page 154.</li> <li>Table 143, "IEEE 802.1Q VLAN Control 0 Register (Page: 0x34, Address 0x00)," on page 155.</li> <li>Table 152, "Default IEEE 802.1Q Tag Register Address Summary," on page 162.</li> <li>Table 166, "Reverse MII Mode Output Timings," on page 173.</li> <li>Table 172, "Electrical Characteristics," on page 178.</li> </ul>                                                                                                                                                                                          |

| 5325F-DS06-R | 10/04/05 | <ul> <li>Updated:</li> <li>DNC in Table 35, "Signal Description," on page 67.</li> <li>Pin Assignment by Pin Number," on page 73.</li> <li>Table 37, "Pin Assignment by Signal Name," on page 76.</li> <li>Ingress_VID_check in Table 140, "802.1Q VLAN Control 4 Register (Page: 0x34, Address 0x04)," on page 143 and drop_Vtable_miss in Table 141, "802.1Q VLAN Control 5 Register (Page: 0x34, Address 0x05)," on page 144.</li> <li>Note below Section 11 Ordering Information.</li> </ul>                                                                                                                                                              |

|              |          | <ul> <li>Added:</li> <li>MII1_TXD[0] and MII1_TXD[1] to Table 35, "Signal Description," on page 67.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5325F-DS05-R | 08/02/05 | <ul> <li>Updated:</li> <li>"MIB Counters Per Port" on page 43.</li> <li>Figure 23, "MII Configuration A," on page 64.</li> <li>Table 30, "Port 4 and MII Ports Configurations Examples," on page 64.</li> <li>Figure 24, "MII Configuration B," on page 65.</li> <li>Figure 25, "MII Configuration C," on page 65.</li> <li>Figure 26, "MII Configuration D," on page 66.</li> <li>Figure 27, "MII Configuration E," on page 66.</li> <li>Figure 28, "MII Configuration F," on page 67.</li> <li>Figure 30, "MAC-to-MAC MII Connection in Reverse MII Mode Between BCM4704 and BCM5325F," on page 68.</li> <li>"Ordering Information" on page 164.</li> </ul> |

| 5325F-DS04-R | 04/01/05 | Minor edits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Revision     | Date     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5325F-DS02-R | 09/17/04 | Updated:         "Features"         "Overview"         "Bidge Management"         "Bridge Management"         "Bridge Management"         "Bidge Management"         "Disable"         "Disable"         "Blocking"         "Listening"         "Management Frames"         "Independent Management Port"         "OPCODE Field in BRCM Tag for Management Port Frame" table         "MII Port"         "Programming Interfaces"         Moved "Register Access through Pseudo PHY Interface" after "EEPROM Interface"         "Switch Mode Register"         "Mirror Capture Control Register (Page 0x02: Address 0x10–0x11)" table         "Multiport Vector 1 Register (Page 0x04: Address 0x26–0x27)" table         "Secure Source Port Mask (Page 0x04: Addresses 0x30–0x31)" table         "Port4 and MII Ports Configurations Examples" table         "Behavior for Reserved Multicast Addresses" table.         "MII Management (MDC/MDIO)"         "Signal Description" table         "Control Registers (Page 0x00)" table         "Secure Destination Port Mask (Page 0x04: Addresses 0x32–0x33) "table         "PHY Port Status Register (Pages 0x10–0x14, 0x19, Address 0x04–0x07)" table |

|              |          | Added:<br>- "Cable Analyzer"<br>- "Revision ID Register (Page 0x02: Address 0x02)"<br>- "Queue 0 TXDSC Control 3 Register"<br>- "Queue 1 TXDSC Control 3 Register"<br>- "Queue 2 TXDSC Control 3 Register"<br>- "Queue 3 TXDSC Control 3 Register"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |          | Removed: <ul> <li>"Serial Management"</li> <li>"SMP Control Register"</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5325F-DS01-R | 04/13/04 | <ul> <li>Updated:</li> <li>"Switch Mode Register (Page 0x00: Address 0x0B)" table</li> <li>"MII1 Port State Override Register (Page 0x00: Address 0x0E)" table</li> <li>"Secure Destination Port Mask"</li> <li>"Page 0x31 VLAN Registers" table</li> <li>"Port VLAN Control Register Serial, MII, Ports[0:4] (Page 31h, Address 00d–09d, 16d–19d, 00h–09h, 10h–13h)" table</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5325F-DS00-R | 03/22/04 | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Broadcom Corporation 5300 California Avenue Irvine, California 92617

© 2008 by Broadcom Corporation All rights reserved Printed in the U.S.A.

Broadcom<sup>®</sup>, the pulse logo, Connecting everything<sup>®</sup>, the Connecting everything logo, and RoboSwitch<sup>™</sup> are among the trademarks of Broadcom Corporation and/or its affiliates in the United States, certain other countries and/or the EU. Any other trademarks or trade names mentioned are the property of their respective owners.

This data sheet (including, without limitation, the Broadcom component(s) identified herein) is not designed, intended, or certified for use in any military, nuclear, medical, mass transportation, aviation, navigations, pollution control, hazardous substances management, or other high risk application. BROADCOM PROVIDES THIS DATA SHEET "AS-IS", WITHOUT WARRANTY OF ANY KIND. BROADCOM DISCLAIMS ALL WARRANTIES, EXPRESSED AND IMPLIED, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT.

# TABLE OF CONTENTS

| Section 1: Introduction               | 1 |

|---------------------------------------|---|

| Overview                              | 1 |

| Audience                              |   |

| Data Sheet Information                | 2 |

| Section 2: Features and Operation     | 3 |

| Overview                              |   |

| QoS                                   |   |

| Software Control                      |   |

| Egress Transmit Queues                |   |

| Port-Based QoS                        |   |

| Diff-Serv QoS                         |   |

| IEEE 802.1P QoS                       |   |

| MAC-Based QoS                         |   |

| Frame Priority Decision Tree          | 5 |

| Port-Based VLAN                       | 5 |

| IEEE 802.1Q VLAN                      |   |

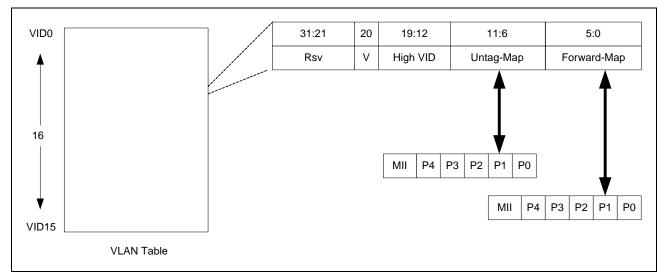

| IEEE 802.1Q VLAN Table Organization   |   |

| Programming the VLAN Table            | 7 |

| High Order 8-Bit VLAN ID              | 7 |

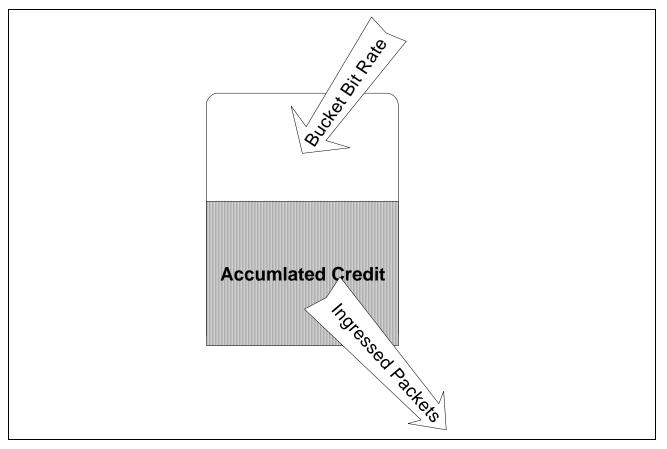

| Rate Control                          |   |

| Protected Ports                       |   |

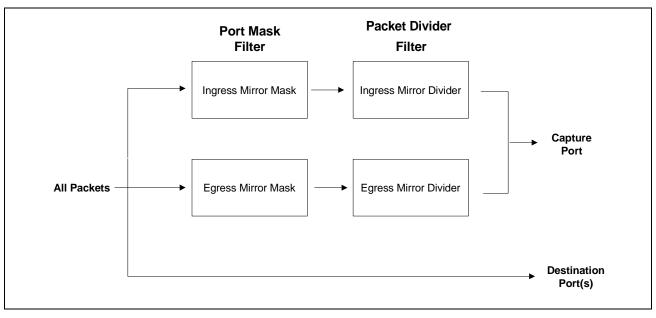

| Port Mirroring                        |   |

| Enabling Port Mirroring               | 9 |

| Capture Port                          |   |

| Mirror Filtering Rules                |   |

| Port Mask Filter                      |   |

| Packet Divider Filter                 |   |

| IGMP Snooping                         |   |

| WAN Port                              |   |

| IEEE 802.1X Port-Based Security       |   |

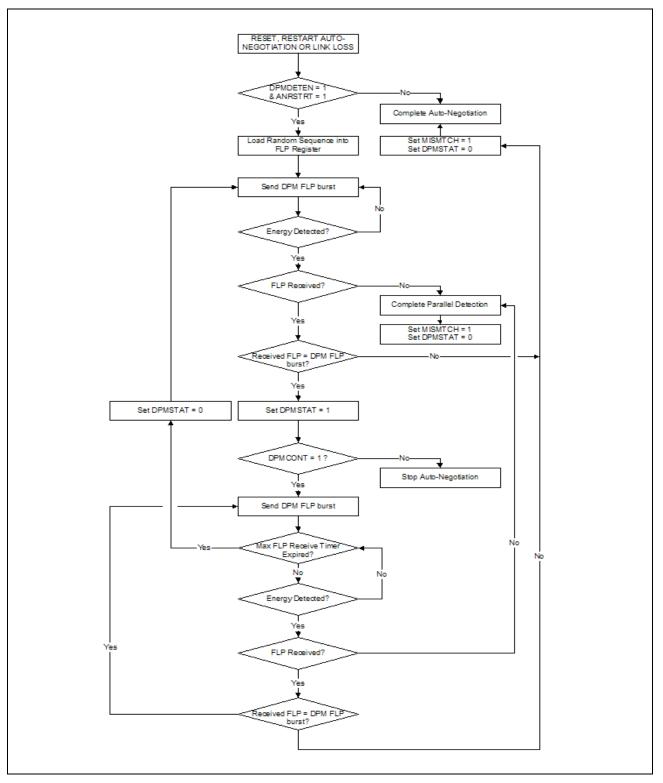

| DTE/DPM Power Over Ethernet Detection |   |

| DPM Detection Description             |   |

| DPM Detection                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPM Register Description                                                                                                                                                                                                                                                                                                                                                                                                                      | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| FLPWIDTH[4:0]: FLP Width in DPMDETEN Mode                                                                                                                                                                                                                                                                                                                                                                                                     | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DPMCONT: Continuous DPM Detect Enable                                                                                                                                                                                                                                                                                                                                                                                                         | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LPXTND: Extend Link Pulse Width                                                                                                                                                                                                                                                                                                                                                                                                               | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MISMTCH: Word Mismatch                                                                                                                                                                                                                                                                                                                                                                                                                        | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DPMSTAT: DPM Status                                                                                                                                                                                                                                                                                                                                                                                                                           | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ANRSTRT: Restart                                                                                                                                                                                                                                                                                                                                                                                                                              | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DPMDETEN: DPM Detection Enable                                                                                                                                                                                                                                                                                                                                                                                                                | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DPM Interrupts Register Description                                                                                                                                                                                                                                                                                                                                                                                                           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DPMINT: DPM Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                         | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DPMMASK: DPM Mask                                                                                                                                                                                                                                                                                                                                                                                                                             | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

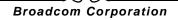

| Cable Analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Cable Analyzer Registers and Programming                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Shadow Register Description                                                                                                                                                                                                                                                                                                                                                                                                                   | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Programming Example                                                                                                                                                                                                                                                                                                                                                                                                                           | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Cable Analyzer Programming                                                                                                                                                                                                                                                                                                                                                                                                                    | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

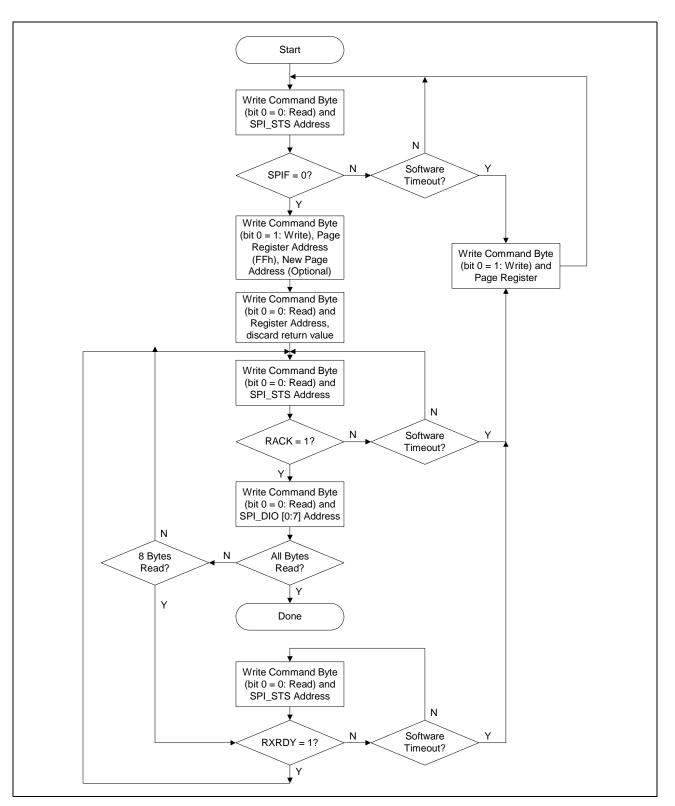

| Cable Analyzer Flow Chart                                                                                                                                                                                                                                                                                                                                                                                                                     | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Cable Analyzer Flow Chart 100BASE-Enhanced FX                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 100BASE-Enhanced FX                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 100BASE-Enhanced FX                                                                                                                                                                                                                                                                                                                                                                                                                           | 22<br>23<br>23                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

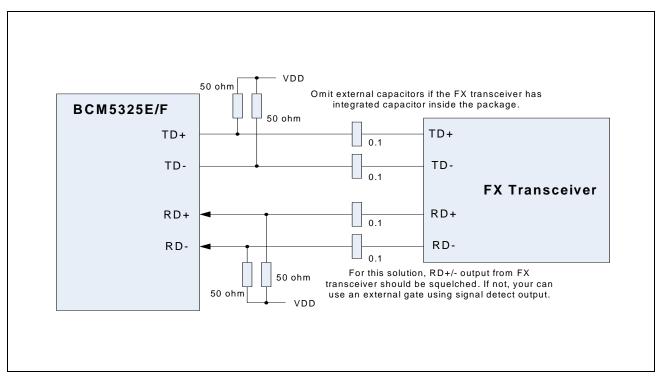

| 100BASE-Enhanced FX<br>Address Management<br>Address Table Organization                                                                                                                                                                                                                                                                                                                                                                       | 22<br>23<br>23<br>23                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 100BASE-Enhanced FX<br>Address Management<br>Address Table Organization<br>Address Learning                                                                                                                                                                                                                                                                                                                                                   | 22<br>23<br>23<br>24<br>24                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 100BASE-Enhanced FX<br>Address Management<br>Address Table Organization<br>Address Learning<br>Address Resolution and Frame Forwarding                                                                                                                                                                                                                                                                                                        | 22<br>23<br>23<br>24<br>24<br>24<br>24                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 100BASE-Enhanced FX<br>Address Management<br>Address Table Organization<br>Address Learning<br>Address Resolution and Frame Forwarding<br>Unicast Addresses                                                                                                                                                                                                                                                                                   | 22<br>23<br>24<br>24<br>24<br>24<br>24<br>24<br>25                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 100BASE-Enhanced FX<br>Address Management<br>Address Table Organization<br>Address Learning<br>Address Resolution and Frame Forwarding<br>Unicast Addresses<br>Multicast Addresses                                                                                                                                                                                                                                                            | 22<br>23<br>23<br>24<br>24<br>24<br>24<br>25<br>27                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 100BASE-Enhanced FX<br>Address Management<br>Address Table Organization<br>Address Learning<br>Address Resolution and Frame Forwarding<br>Unicast Addresses<br>Multicast Addresses<br>Static Address Entries                                                                                                                                                                                                                                  | 22<br>23<br>23<br>24<br>24<br>24<br>24<br>25<br>27<br>28                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 100BASE-Enhanced FX<br>Address Management<br>Address Table Organization<br>Address Learning<br>Address Resolution and Frame Forwarding<br>Unicast Addresses<br>Multicast Addresses<br>Static Address Entries<br>Accessing the ARL Table Entries                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 100BASE-Enhanced FX.<br>Address Management<br>Address Table Organization<br>Address Learning<br>Address Resolution and Frame Forwarding<br>Unicast Addresses<br>Multicast Addresses<br>Static Address Entries<br>Accessing the ARL Table Entries<br>Reading an ARL Entry.                                                                                                                                                                     | 22<br>23<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>27<br>27<br>28<br>28 |

| 100BASE-Enhanced FX.         Address Management         Address Table Organization         Address Learning         Address Resolution and Frame Forwarding.         Unicast Addresses         Multicast Addresses         Static Address Entries         Accessing the ARL Table Entries         Reading an ARL Entry.         Writing an ARL Entry.                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 100BASE-Enhanced FX         Address Management         Address Table Organization                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 100BASE-Enhanced FX.         Address Management         Address Table Organization         Address Learning         Address Resolution and Frame Forwarding.         Unicast Addresses         Multicast Addresses         Static Address Entries         Accessing the ARL Table Entries         Reading an ARL Entry.         Writing an ARL Entry         Searching the ARL Table         Address Aging                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 100BASE-Enhanced FX         Address Management         Address Table Organization         Address Learning         Address Resolution and Frame Forwarding         Unicast Addresses         Multicast Addresses         Static Address Entries         Accessing the ARL Table Entries         Reading an ARL Entry         Writing an ARL Entry         Searching the ARL Table         Address Aging         Using the Multiport Addresses |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Blocking                            |  |

|-------------------------------------|--|

| Listening                           |  |

| Learning                            |  |

| Forwarding                          |  |

| Management Frames                   |  |

| Section 3: System Functional Blocks |  |

| Overview                            |  |

| Media Access Controller             |  |

| Receive Function                    |  |

| Transmit Function                   |  |

| Flow Control                        |  |

| Physical Layer Transceiver          |  |

| Encoder/Decoder                     |  |

| Link Monitor                        |  |

| Collision Detection                 |  |

| Automatic MDI Crossover (Auto-MDIX) |  |

| Auto-Negotiation                    |  |

| Digital Adaptive Equalizer          |  |

| ADC                                 |  |

| Digital Clock Recovery/Generator    |  |

| Baseline Wander Correction          |  |

| Digital to Analog Converter         |  |

| Stream Cipher                       |  |

| 100BASE-FX Fiber Mode               |  |

| Frame Management                    |  |

| Independent Management Port         |  |

| Switch Controller                   |  |

| Buffer Management                   |  |

| Memory Arbitration                  |  |

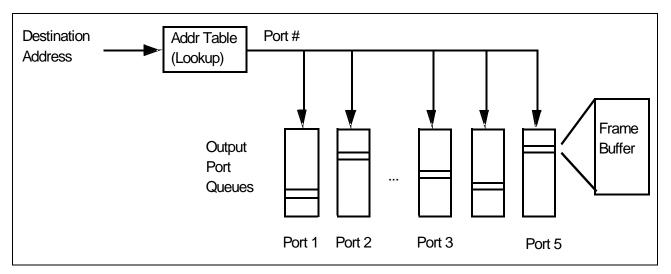

| Transmit Output Port Queues         |  |

| Integrated High-Performance Memory  |  |

| Clocking                            |  |

| MIB Engine                          |  |

| MIB Counters Per Port               |  |

| Group 0                                      |    |

|----------------------------------------------|----|

| Group 1                                      | 42 |

| Section 4: System Interfaces                 |    |

| Overview                                     |    |

| MII Port                                     |    |

| Programming Interfaces                       | 46 |

| SPI Interface                                | 46 |

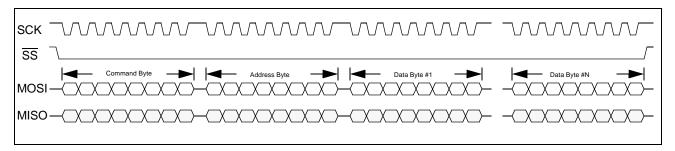

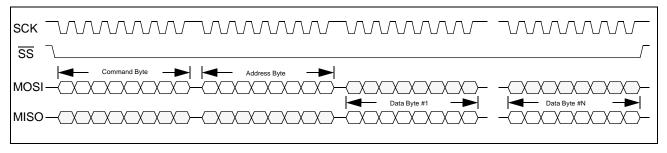

| Normal SPI Mode                              | 48 |

| Fast SPI Mode                                |    |

| EEPROM Interface                             | 53 |

| Register Access through Pseudo PHY Interface | 54 |

| MII Ports and Port 4 Configurations          | 59 |

| MII Management (MDC/MDIO)                    | 64 |

| PHY Address                                  | 64 |

| Register Programming                         | 64 |

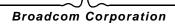

| LED Interfaces                               | 65 |

| Parallel LED Interface                       | 65 |

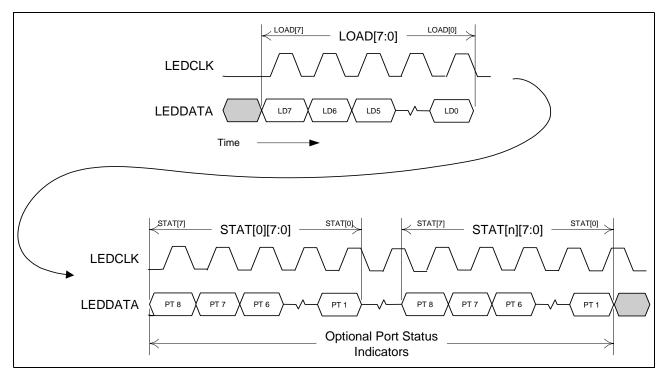

| Serial LED Interface                         |    |

| Load Meter LED                               | 69 |

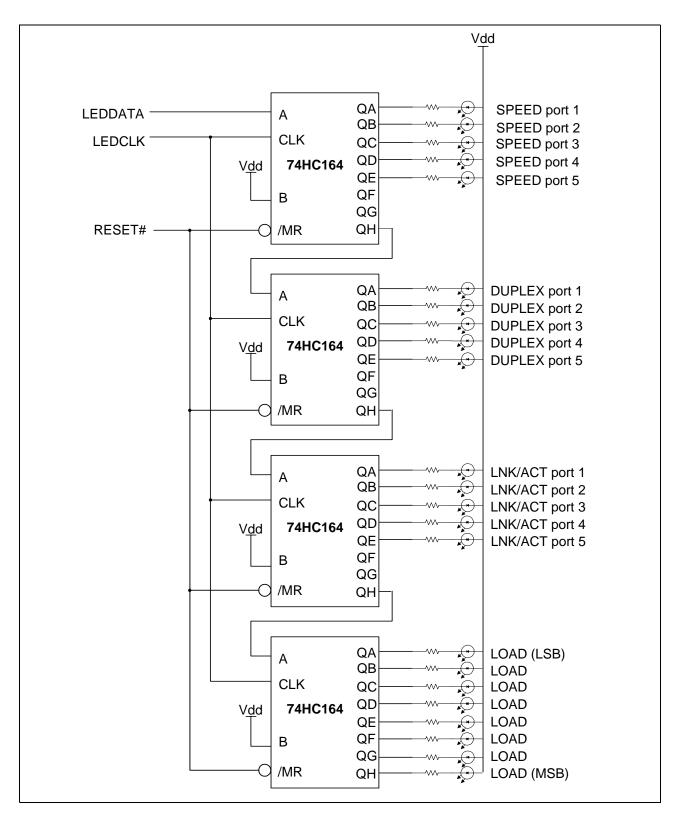

| Internal Voltage Regulator                   | 70 |

| Section 5: Hardware Signal Definitions       | 71 |

| Pin Assignment List                          |    |

| Pin Assignment by Pin Number                 |    |

| Pin Assignment by Signal Name                | 79 |

| Section 6: Register Definitions              | 80 |

| Register Notations                           | 80 |

| Global Switch Register Map                   | 81 |

| Page 0x00: Control Registers                 | 82 |

| 10/100 Port Control Register                 | 83 |

| MII Port Control Register                    | 84 |

| Switch Mode Register                         |    |

| MII2 Port State Override Register            |    |

| MII1 Port State Override Register            |    |

|    | Power Down Mode Register                                            | 87  |

|----|---------------------------------------------------------------------|-----|

|    | LED Flash Control Register                                          | 88  |

|    | LEDa Control Register                                               | 88  |

|    | LEDb Control Register                                               | 89  |

|    | LEDc Control Register                                               | 89  |

|    | Multicast IP Address Control Register                               | 90  |

|    | WAN Port Select Register                                            | 90  |

|    | Protected Mode Control Register                                     | 90  |

| Pa | ge 0x01: Status Registers                                           | 91  |

|    | Link Status Summary                                                 | 91  |

|    | Link Status Change                                                  | 92  |

|    | Port Speed Summary                                                  | 92  |

|    | Duplex Status Summary                                               | 93  |

|    | Pause Status Summary                                                | 93  |

|    | BIST Status                                                         | 94  |

| Pa | ge 0x02: Management/Mirroring Registers                             | 95  |

|    | Global Management Configuration Register                            | 96  |

|    | Revision ID Register                                                | 96  |

|    | MIB Mode Select Register                                            | 96  |

|    | Aging Time Control Register                                         | 97  |

|    | Mirror Capture Control Register                                     | 97  |

|    | Ingress Mirror Control Register                                     | 98  |

|    | Ingress Mirror Divider Register                                     | 98  |

|    | Egress Mirror Control Register                                      | 99  |

|    | Egress Mirror Divider Register                                      | 99  |

| Pa | ge 0x04: ARL Control Register                                       | 100 |

|    | Global ARL Configuration Register                                   | 101 |

|    | BPDU Multicast Address Register                                     | 101 |

|    | Multiport Address 1 Register                                        | 102 |

|    | Multiport Vector 1 Register                                         | 102 |

|    | Multiport Address 2 Register                                        | 103 |

|    | Multiport Vector 2 Register                                         | 103 |

|    | Secure Source Port Mask                                             | 104 |

|    | Secure Destination Port Mask                                        | 104 |

|    | Example: Usage of Secure Source and Destination Port Mask Registers | 105 |

|    |                                                                     |     |

| Page 0x05: ARL Access Registers                     | 106 |

|-----------------------------------------------------|-----|

| ARL Read/Write Control Register                     | 107 |

| MAC Address Index Register                          | 107 |

| VID Table Index Register                            | 108 |

| ARL Entry 0 Register                                | 108 |

| ARL Entry 1 Register                                | 109 |

| ARL Search Control Register                         | 111 |

| ARL Search Result Register                          | 112 |

| ARL Search Result Extension Register                | 113 |

| VID Entry 0 Register                                | 113 |

| VID Entry 1 Register                                | 113 |

| Page 0x08: Memory Access Registers                  | 114 |

| Memory Read/Write Control Register                  | 114 |

| Memory Read/Write Data Register                     | 115 |

| Memory Read/Write VID Register                      | 115 |

| Page 0x0A: IEEE 802.1X Control Registers            | 116 |

| IEEE 802.1X Control 1 Register                      | 117 |

| IEEE 802.1X Control 2 Register                      | 117 |

| Queue 0 TXDSC Control 3 Register                    | 118 |

| Queue 1 TXDSC Control 3 Register                    | 118 |

| Queue 2 TXDSC Control 3 Register                    | 118 |

| Queue 3 TXDSC Control 3 Register                    | 119 |

| Unicast DLF Drop Control Register                   | 120 |

| Page 0x10–0x14, 0x19: PHY Port Registers            | 121 |

| PHY Port Control Register                           | 122 |

| PHY Port Status Register                            | 123 |

| PHY Identifier Registers                            | 123 |

| Auto-Negotiation Advertisement Register             | 124 |

| Auto-Negotiation Link Partner (LP) Ability Register | 124 |

| Auto-Negotiation Expansion Register                 | 125 |

| Auto-Negotiation Next Page Register                 | 125 |

| Link Partner Next Page Register                     | 126 |

| DPM Register                                        | 126 |

| 100BASE-X Auxiliary Control Register                | 127 |

| 100BASE-X Auxiliary Status Register                 | 127 |

| 100BASE-X Receive Error Counter                         | 128 |

|---------------------------------------------------------|-----|

| 100BASE-X False Carrier Sense Counter                   | 128 |

| Auxiliary Control/Status Register                       | 128 |

| Auxiliary Status Summary Register                       | 129 |

| DPM Interrupt Register                                  | 131 |

| Auxiliary Mode 2 Register                               | 131 |

| 10BASE-T Auxiliary Error and General Status Register    | 131 |

| Auxiliary Multiple PHY Register                         | 132 |

| Broadcom Test Register                                  | 132 |

| Page 0x18: MII Port External PHY Registers              | 133 |

| Page 0x20–0x24: Port MIB Registers                      | 135 |

| Page 0x30: QoS Registers                                | 137 |

| QoS Control Register                                    | 138 |

| QoS Priority Queue Control Register                     | 138 |

| QoS IEEE 802.1P Enable Register                         | 139 |

| QoS Diff-Serv Enable Register                           | 139 |

| QoS Pause Enable Register                               |     |

| IEEE 802.1P Priority Threshold Register                 |     |

| DiffServ DSCP Priority Register                         |     |

| Page 0x31: Port-Base VLAN Registers                     |     |

| Port-Based VLAN Control Register                        |     |

| Page 0x34: IEEE 802.1Q VLAN Registers                   |     |

| IEEE 802.1Q VLAN Control 0 Register                     |     |

| IEEE 802.1Q VLAN Control 1 Register                     |     |

| IEEE 802.1Q VLAN Control 2 Register                     |     |

| IEEE 802.1Q VLAN Control 3 Register                     |     |

| IEEE 802.1Q VLAN Control 4 Register                     |     |

| IEEE 802.1Q VLAN Control 5 Register                     |     |

| IEEE 802.1Q VLAN Table Access Register                  |     |

| IEEE 802.1Q VLAN Write Register                         |     |

| IEEE 802.1Q VLAN Read Register                          | 150 |

| IEEE 802.1Q Default Port TAG Register                   | 151 |

| Priority Re-Map Register                                | 152 |

| Page 0x35: Multicast/Broadcast/DLF Suppression Register | 153 |

| Rate Control Register                                   | 154 |

|                                                         |     |

| Global Registers                      |     |

|---------------------------------------|-----|

| SPI Data I/O Register                 |     |

| SPI Status Register                   |     |

| Page Register                         | 155 |

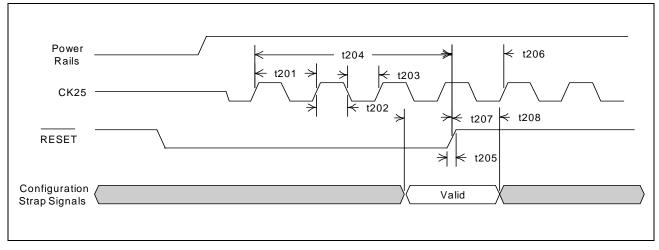

| Section 7: Timing Characteristics     | 156 |

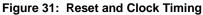

| Reset and Clock Timing                |     |

| Serial LED Interface Timing           |     |

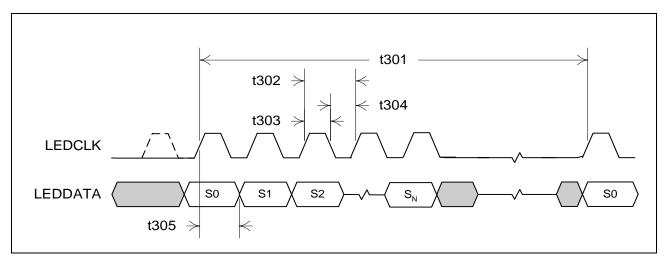

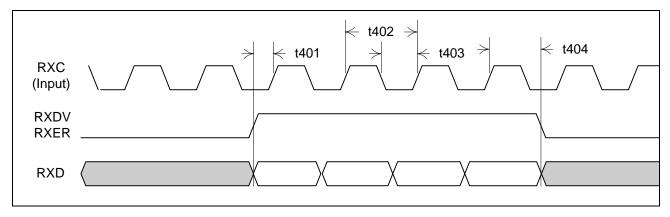

| MII Interface Timing                  |     |

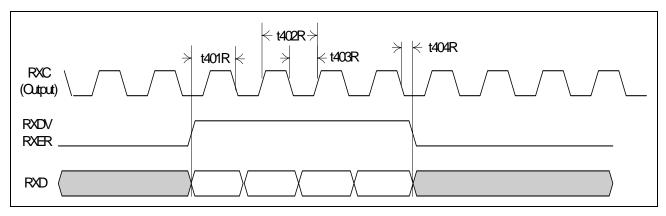

| MII Input Timing                      |     |

| MII Output Timing                     |     |

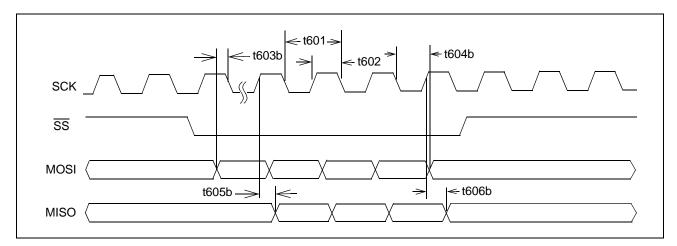

| Reverse MII Timing                    |     |

| Reverse MII Input Timing              |     |

| Reverse MII Output Timing             |     |

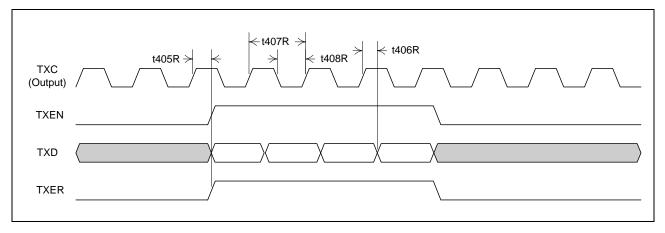

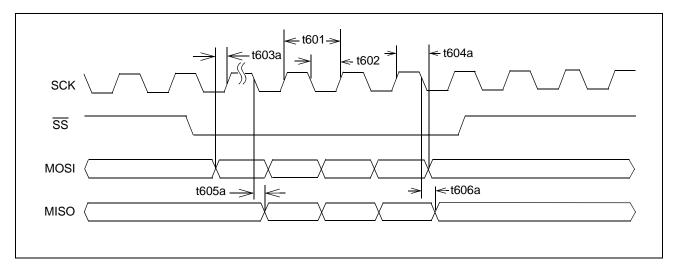

| SPI Timing                            |     |

| EEPROM Timing                         |     |

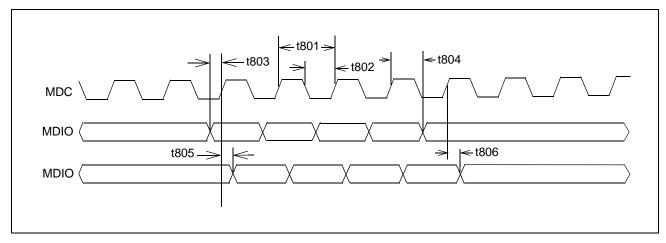

| Management Data Interface Timing      |     |

| Section 8: Electrical Characteristics |     |

| Section 9: Thermal Information        | 166 |

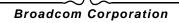

| Section 10: Mechanical Information    | 167 |

| Section 11: Ordering Information      |     |

# LIST OF FIGURES

| Functional Block Diagram                                                         | i                            |

|----------------------------------------------------------------------------------|------------------------------|

| IEEE 802.1Q VLAN Untag Table                                                     | 6                            |

| Bucket Flow                                                                      | 8                            |

| Mirror Filter Flow                                                               | 9                            |

| DPM Detection and Auto-Negotiation Flow Diagram                                  | . 12                         |

| Cable Analyzer Flow Chart                                                        | . 21                         |

| Typical EFX Connection Diagram                                                   | . 22                         |

| Mode Address Table Organization                                                  | . 23                         |

| Transmit Output Queues                                                           | . 41                         |

| Normal SPI Command Byte                                                          | . 46                         |

| Fast SPI Command Byte                                                            | . 47                         |

| SPI Serial Interface Write Operation                                             | . 47                         |

| SPI Serial Interface Read Operation                                              | . 48                         |

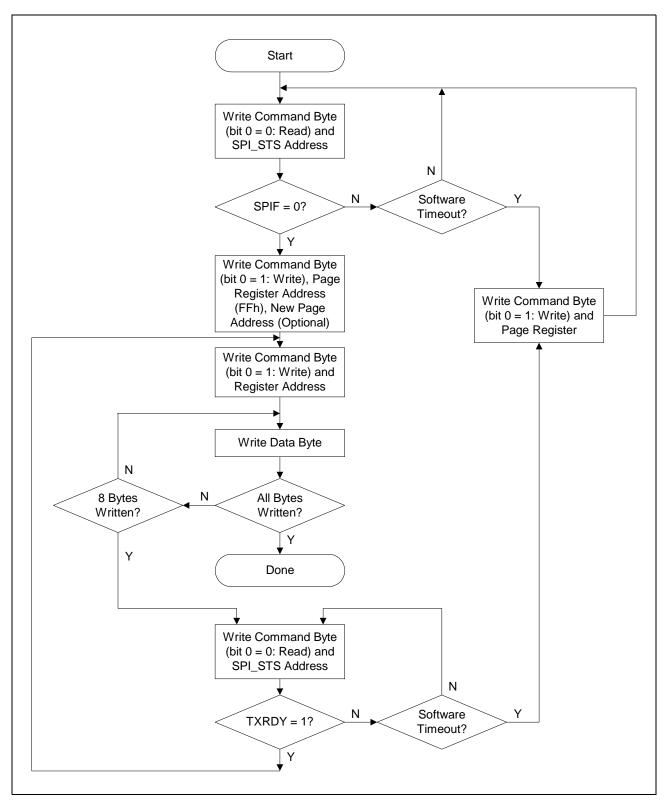

| Normal SPI Mode Read Flow Chart                                                  | . 50                         |

| Normal SPI Mode Write Flow Chart                                                 | . 51                         |

| Timing Example                                                                   | . 52                         |

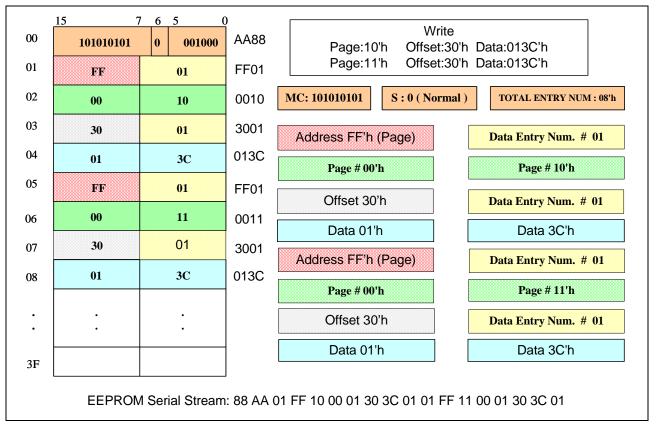

| EEPROM Programming Example                                                       | . 54                         |

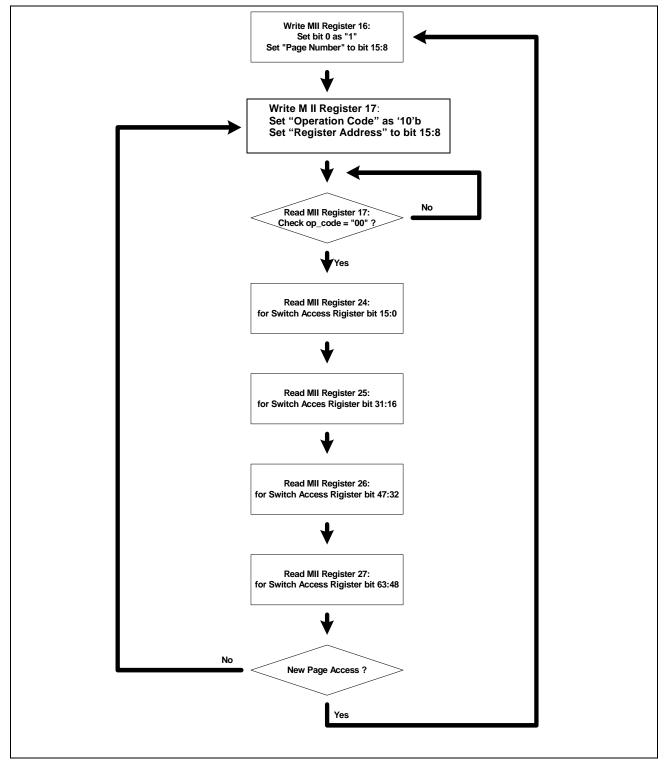

| Read Access to Switch Register Set via Pseudo PHY (Phyad = 11110) MDC/MDIO Path  | . 55                         |

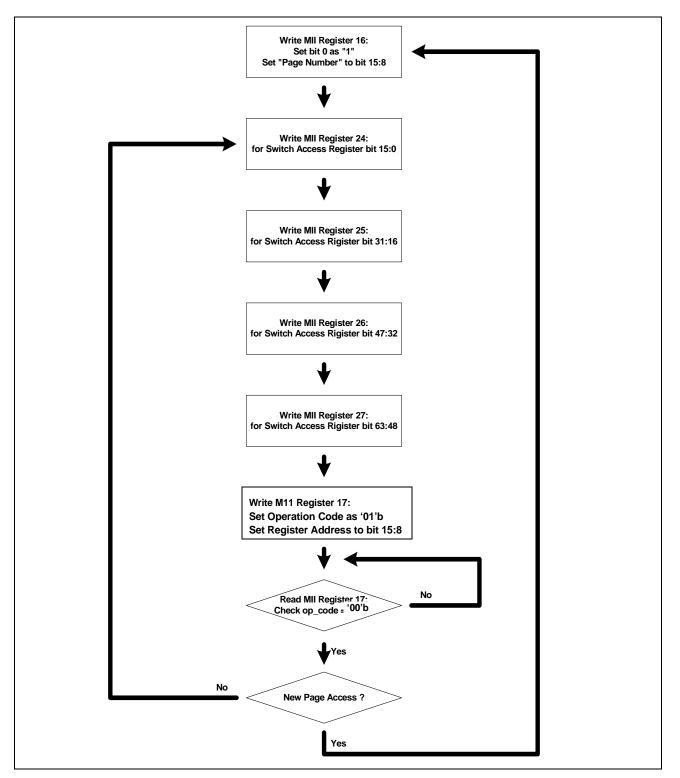

| Write Access to Switch Register Set via Pseudo PHY (Phyad = 11110) MDC/MDIO Path | . 56                         |

| Pseudo PHY MII Register Map                                                      | . 57                         |

| MII Configuration A                                                              | . 59                         |

| MII Configuration B                                                              | . 60                         |

| MII Configuration C                                                              | . 60                         |

| MII Configuration D                                                              | . 61                         |

| MII Configuration F                                                              | . 61                         |

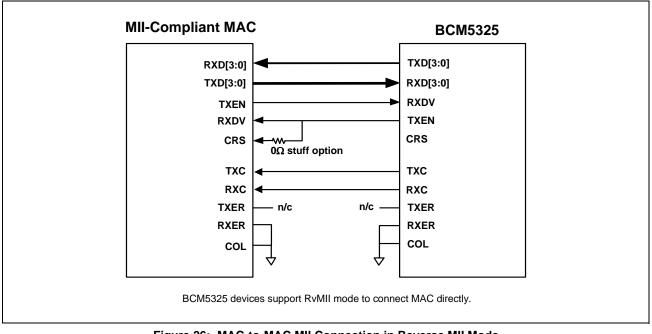

| MAC-to-MAC MII Connection in Reverse MII Mode                                    | . 62                         |

| MAC-to-MAC MII Connection in Reverse MII Mode Between BCM4704 and BCM5325F       | . 63                         |

| Serial LED Shift Sequence                                                        | . 66                         |

| Example Circuit for Serial LED Mode                                              | . 67                         |

| Regulator Connection                                                             | . 70                         |

| Reset and Clock Timing                                                           | 156                          |

| Serial LED Timing                                                                | 157                          |

| MII Interface Input Timing                                                       | 158                          |

|                                                                                  | IEEE 802.1Q VLAN Untag Table |

| Figure 34: | MII Interface Output Timings                 | 159 |

|------------|----------------------------------------------|-----|

| Figure 35: | Reverse MII Mode Input Timings               | 160 |

| Figure 36: | Reverse MII Mode Output Timings              | 160 |

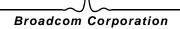

| Figure 37: | SPI Timings when SS Asserted During SCK High | 161 |

| Figure 38: | SPI Timings when SS Asserted During SCK Low  | 161 |

| Figure 39: | EEPROM Timing                                | 162 |

| Figure 40: | Management Data Interface (Slave Mode)       | 163 |

| Figure 41: | 128-Pin MQFP Package Outline Drawing         | 167 |

# LIST OF TABLES

| Table 1:  | DPM Register Summary (Pages 0x10–0x14, Address 0x1E–0x1F) | 13 |

|-----------|-----------------------------------------------------------|----|

| Table 2:  | DPM Register (Page 0x10–0x14, Address 0x1E–0x1F)          | 13 |

| Table 3:  | Interrupt Register (Pages 0x10–0x14, Address 0x34–0x35)   | 15 |

| Table 4:  | Shadow Register 28h (Pages 10h-14h, address 28h)          | 16 |

| Table 5:  | Shadow Register 0x26-0 (Pages 10h-14h, address 26h)       | 16 |

| Table 6:  | Pair-B State                                              | 16 |

| Table 7:  | Pair-A State                                              | 16 |

| Table 8:  | Shadow Register 0x26-1 (Pages 10h-14h, address 26h)       | 17 |

| Table 9:  | Pair-B Cable Diagnostics Result                           | 17 |

| Table 10: | Pair-A Cable Diagnostics Result                           | 17 |

| Table 11: | Shadow Register 0x26-2 (Pages 10h-14h, address 26h)       | 17 |

| Table 12: | Shadow Register 0x26-3 (Pages 10h-14h, address 26h)       | 18 |

| Table 13: | Shadow Register 0x26-4 S (Pages 10h-14h, address 26h)     | 18 |

| Table 14: | Shadow Register 0x26-5 (Pages 10h-14h, address 26h)       | 18 |

| Table 15: | Shadow Register 0x26-6 (Pages 10h-14h, address 26h)       | 18 |

| Table 16: | Shadow Register 0x26-7 (Pages 10h-14h, address 26h)       | 18 |

| Table 17: | Address Table Entry for Unicast Address                   | 25 |

| Table 18: | Address Table Entry for Multicast Address                 | 26 |

| Table 19: | Behavior for Reserved Multicast Addresses                 | 26 |

| Table 20: | Spanning Tree State                                       | 31 |

| Table 21: | Flow Control Modes                                        | 34 |

| Table 22: | Transmit/Receive Frame Format Over Management Port        | 38 |

| Table 23: | BRCM Tag Format                                           | 38 |

| Table 24: | OPCODE Field in BRCM Tag for Management Port Frame        | 39 |

| Table 25: | Field in BRCM Tag for Management Port Frame               | 40 |

| Table 26: | EEPROM Header Format                                      | 53 |

| Table 27: | EEPROM Contents                                           | 53 |

| Table 28: | Pseudo PHY MII Register Definitions                       | 58 |

| Table 29: | Port 4 and MII Ports Configurations Examples              | 59 |

| Table 30: | MII Management Frame Format                               | 64 |

| Table 31: | MII Read And Write Instruction Contents                   | 65 |

| Table 32: | LED Status Types                                          | 68 |

| Table 33: | LED Mode Matrix                                           | 68 |

| Table 34: | Load Meter LED Decode                                              | 69 |

|-----------|--------------------------------------------------------------------|----|

| Table 35: | I/O Signal Type Definitions                                        | 71 |

| Table 36: | Signal Description                                                 | 71 |

| Table 37: | Pin Assignment by Pin Number                                       | 78 |

| Table 38: | Pin Assignment by Signal Name                                      | 79 |

| Table 39: | Switch Global Page Register Map                                    | 81 |

| Table 40: | Control Registers (Page 0x00)                                      | 82 |

| Table 41: | 10/100 Port Control Register (Page 0x00: Address 0x00–0x04)        | 83 |

| Table 42: | MII Port Control Register (Page 0x00: Address 0x08)                | 84 |

| Table 43: | Switch Mode Register (Page 0x00: Address 0x0B)                     | 85 |

| Table 44: | MII2 Port State Override Register (Page 0x00: Address 0x0D)        | 86 |

| Table 45: | MII1 Port State Override Register (Page 0x00: Address 0x0E)        | 87 |

| Table 46: | Power Down Mode Register (Page 0x00: Address 0x0F)                 | 87 |