#

# Single-Chip 16-Port SerDes Gigabit Switch

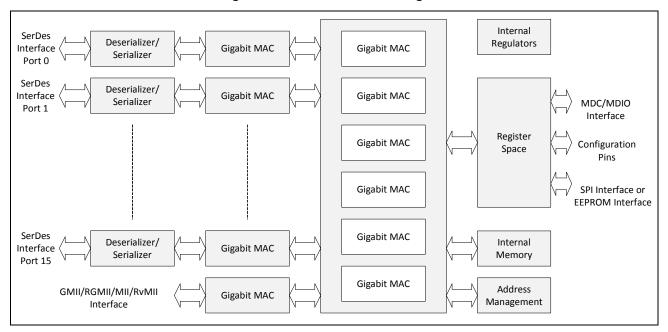

The BCM5396 is a 16-port Gigabit Ethernet (GbE) switch integrated with 16 1.25G SerDes/SGMII port interfaces for connecting to external Gigabit PHYs or fiber modules. The BCM5396 provides the lowest-power and cost GbE functionality to the desktop switching solution or WebSmart application.

The BCM5396 is a highly integrated solution, combining all of the functions of a high-speed switch system, including packet buffer, Media Access Controllers (MACs), address management, and a non-blocking switch controller into a single monolithic 0.13  $\mu$ m CMOS device. The BCM5396 complies with the IEEE 802.3, 802.3u, 802.3ab, and 802.3x specifications, including the MAC control PAUSE frame and auto-negotiation subsections, providing compatibility with all industry-standard Ethernet, Fast Ethernet, and GbE devices.

The BCM5396 device provides integrated 1.25G SerDes, reducing board footprint requirements. The 16 ports have SGMII interfaces for connecting with external GbE transceivers.

- 16-port 10/100/1000 Mbps integrated switch controller via 1.25G SerDes/SGMII/fiber

- Embedded 256 KB on-chip packet buffer

- One 10/100/1000 Mbps In-band Management Port (IMP) with GMII/RGMII/RvMII/MII interface for PHY-less connection to a CPU/management entity (for management purposes only)

- Integrated address management

- Supports up to 4K MAC addresses

- Supports jumbo frames up to 9728 bytes.

- Supports EEPROM for low-cost chip configuration

- Integrated Motorola SPI-compatible interface

- Supports port mirroring

- Port-based VLAN and 4K IEEE 802.1Q tag VLAN

- Port-, DiffServ-, MAC-, and IEEE 802.1p-based QoS for four queues

- Supports Spanning Tree, Rapid Spanning Tree, and Multiple Spanning Tree protocols (802.1D/1s/1w)

- Supports IEEE Standard 802.1X port security

- Supports pseudo-PHY MDIO access

- · MAC-based trunking with link fail-over

- Ethernet-in-the-last-mile (EFM) support: OAM and P

- Low-power (2.2W total) 1.2V core/2.5V (SGMII I/O)/3.3V (GMII/MII/RvMII) and 2.5V RGMII operation with 3.3V I/O tolerance

- 256-pin FBGA package

Figure 1: Functional Block Diagram

© 2016 by Broadcom. All rights reserved.

Broadcom<sup>®</sup>, the pulse logo, Connecting everything<sup>®</sup>, Avago Technologies, and the A logo are among the trademarks of Broadcom and/or its affiliates in the United States, certain other countries and/or the EU. The term "Broadcom" refers to Broadcom Limited and/or its subsidiaries. For more information, please visit www.broadcom.com.

Broadcom reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design. Information furnished by Broadcom is believed to be accurate and reliable. However, Broadcom does not assume any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

### **Revision History**

| Revision     | Date     | Change Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5396-DS116-R | 06/20/16 | <ul> <li>Updated:</li> <li>"Register Access Through Pseudo-PHY Interface" on page 66</li> <li>"MDC/MDIO Interface Register Programming" on page 71</li> <li>"Port 16 (IMP) State Override Register (Page 00h: Address 70h)" on page 98</li> <li>Table 93: "Internal SerDes Registers Page Descriptions 10h–1Fh," on page 127</li> <li>Table 94: "Internal SerDes Registers Page 10h–1Fh," on page 127</li> <li>Table 176: "MDC[0]/MDIO[0] Timing," on page 188</li> </ul>                                                                       |

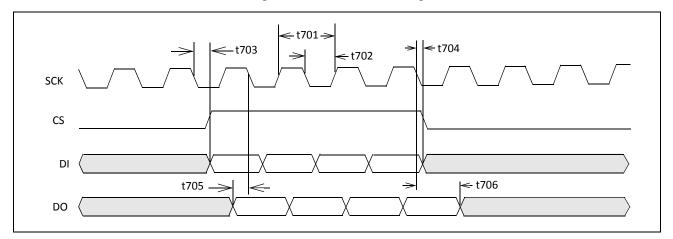

| 5396-DS115-R | 11/17/14 | <ul> <li>Updated:</li> <li>Figure 38: "256-Pin FBGA Package Outline Drawing," on page 199</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5396-DS114-R | 10/04/13 | <ul> <li>Added:</li> <li>"Ethertype Based QoS" on page 30</li> <li>Updated:</li> <li>Figure 2: "Priority Packet Mapping Flow," on page 28</li> <li>Table 1: "Frame Priority Decision Tree Summary," on page 31</li> <li>"Jumbo Frame Support" on page 34</li> <li>Table 18: "Pseudo-PHY MII Register Definitions," on page 73</li> <li>"Serial LED Interface" on page 75</li> <li>Table 46: "External PHY Scan Control Register (Page 00h: Address 86h)," on page 107</li> <li>Table 228: "Serial LED Interface Timing," on page 214</li> </ul> |

| 5396-DS113-R | 02/07/12 | <ul> <li>Updated:</li> <li>Table 139: "Internal SerDes Registers Page Descriptions 10h–1Fh," on page 145.</li> <li>Table 140: "Internal SerDes Registers Page 10h–1Fh," on page 145.</li> <li>Table 192: "New Priority Map Register (Pages 34h: Address 0C–0Fh)," on page 185.</li> </ul>                                                                                                                                                                                                                                                       |

| 5396-DS112-R | 06/10/10 | <ul> <li>Updated:</li> <li>Table 144: "Auto-Negotiation Link Partner Ability (Page 10h–1Fh: Address 0Ah–0Bh)," on page 153.</li> <li>"PRBS Status Register (Page 10h ~ 1Fh: Address 32h ~ 33h)" on page 166.</li> </ul>                                                                                                                                                                                                                                                                                                                         |

| 5396-DS111-R | 08/26/09 | <ul><li>Updated:</li><li>Section 12: "Ordering Information," on page 175.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5396-DS110-R | 02/25/08 | <ul> <li>Updated:</li> <li>"Signal Descriptions" on page 54: BIST_CLRMEM_SEL and<br/>SKIP_MEMBIST descriptions.</li> <li>Removed:</li> <li>References to behavior of management frames in unmanaged mode</li> </ul>                                                                                                                                                                                                                                                                                                                             |

| Revision     | Date     | Change Description                                                                                                                                                                                                  |

|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5396-DS109-R | 11/13/07 | Updated:                                                                                                                                                                                                            |

|              |          | • "Management Frames" on page 24, and "Frame Management" on page 32: Corrected terminology relating to the in-band management port.                                                                                 |

|              |          | <ul> <li>Table 59, "Management Mode Registers (Page 02h)," on page 81:<br/>Changed definition of bits 7:6.</li> </ul>                                                                                               |

|              |          | Added:                                                                                                                                                                                                              |

|              |          | <ul> <li>"In-Band Management Port" on page 33: Added note.</li> </ul>                                                                                                                                               |

|              |          | <ul> <li>Table 23, "Signal Descriptions," on page 53 and "Pin Assignments" on<br/>page 58: Added BIST_CLRMEM_SEL, SKIPMEMBIST, EN_EXT_CLK,<br/>and EXT_CLK signals to all signal/pin tables and figures.</li> </ul> |

| 5396-DS108-R | 06/25/07 | Updated:                                                                                                                                                                                                            |

|              |          | <ul> <li>"In-Band Management Port" on page 33.</li> </ul>                                                                                                                                                           |

|              |          | <ul> <li>Table 28, "10/100/1000 Port Control Register (Page 00h: Address 00h–<br/>0Fh)," on page 69</li> </ul>                                                                                                      |

|              |          | <ul> <li>Table 29, "IMP Port Control Register (Page 00h: Address 10h)," on page<br/>69.</li> </ul>                                                                                                                  |

|              |          | <ul> <li>Table 66, "Global Management Configuration Register (Page 02h:<br/>Address 00h)," on page 86.</li> </ul>                                                                                                   |

|              |          | <ul> <li>Table 229, "Thermal Properties, With External Heat Sink, 23 mm. ´23 mm.<br/>´15 mm. Blade Fin," on page 180.</li> </ul>                                                                                    |

|              |          | Removed:                                                                                                                                                                                                            |

|              |          | <ul> <li>Memory Test Control Register (Page 00h: Address E0h) from page 75.</li> </ul>                                                                                                                              |

| 5396-DS107-R | 07/12/06 | Updated:                                                                                                                                                                                                            |

|              |          | • Figure 39, "256-Pin FBGA Package Outline Drawing," on page 181.                                                                                                                                                   |

| 5396-DS106-R | 05/24/06 | Added:                                                                                                                                                                                                              |

|              |          | <ul> <li>Table 154, "BER/CRC Error Counter Register (Page 10h ~ 1Fh: Address<br/>2Eh ~ 2Fh)," on page 128.</li> </ul>                                                                                               |

|              |          | <ul> <li>Table 155, "PRBS Control Register (Page 10h ~ 1Fh: Address 30h ~ 31h),"<br/>on page 128.</li> </ul>                                                                                                        |

|              |          | <ul> <li>Table 156, "PRBS Control Register (Page 10h ~ 1Fh: Address 32h ~ 33h),"<br/>on page 128.</li> </ul>                                                                                                        |

|              |          | <ul> <li>Table 157, "Pattern Generator Control Register (Page 10h ~ 1Fh: Address<br/>34h ~ 35h)," on page 129.</li> </ul>                                                                                           |

|              |          | <ul> <li>Table 158, "Pattern Generator Control Register (Page 10h ~ 1Fh: Address<br/>36h ~ 37h)," on page 130.</li> </ul>                                                                                           |

|              |          | <ul> <li>Table 159, "Pattern Generator Control Register (Page 10h ~ 1Fh: Address<br/>36h ~ 37h)," on page 130.</li> </ul>                                                                                           |

|              |          | <ul> <li>Table 160, "Force Transmit 1 Register (Page 10h ~ 1Fh: Address 3Ah ~<br/>3Bh)," on page 130.</li> </ul>                                                                                                    |

|              |          | <ul> <li>Table 161, "Block Address (Pages 10h–1Fh: Address 3Eh ~ 3Fh)," on<br/>page 131.</li> </ul>                                                                                                                 |

| Revision     | Date     | Change Description                                                                                                                       |  |

|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5396-DS105-R | 04/19/06 | Updated:                                                                                                                                 |  |

|              |          | Features list on front cover.                                                                                                            |  |

|              |          | "LED Interfaces" on page 50.                                                                                                             |  |

|              |          | <ul> <li>Table 23, "Signal Descriptions," on page 53.</li> </ul>                                                                         |  |

|              |          | <ul> <li>Table 24, "Pin Assignment (Listed by Pin Number)," on page 58.</li> </ul>                                                       |  |

|              |          | <ul> <li>Table 25, "Pin Assignment (Listed by Signal Name)," on page 60.</li> </ul>                                                      |  |

|              |          | <ul> <li>Figure 21, "Pins Top View," on page 62.</li> </ul>                                                                              |  |

|              |          | <ul> <li>Table 27, "Control Registers (Page 00h)," on page 67.</li> </ul>                                                                |  |

|              |          | • LED A, B, C, and D registers to Reserved in Table 27, "Control Registers (Page 00h)," on page 67.                                      |  |

|              |          | <ul> <li>Table 65, "Strap Value Register (Page 01h: Address 70h–73h)," on page<br/>85.</li> </ul>                                        |  |

|              |          | <ul> <li>Table 94, "ARL Search Result Register 0 (Page 05h: Address 3Bh–3El<br/>on page 98.</li> </ul>                                   |  |

|              |          | <ul> <li>Table 95, "ARL Search MAC/VID Result Register 1 (Page 05h: Address 40h–47h)," on page 98.</li> </ul>                            |  |

|              |          | Table 231, "Ordering Information," on page 182.                                                                                          |  |

|              |          | Removed:                                                                                                                                 |  |

|              |          | <ul> <li>LED A, B, C, and D register descriptions from section "Control Registers"<br/>on page 67.</li> </ul>                            |  |

| 5396-DS104-R | 11/10/05 | Added:                                                                                                                                   |  |

|              |          | • I-temp package ordering information to Table 223, "Ordering Information".                                                              |  |

| 5396-DS103-R | 09/21/05 | Updated:                                                                                                                                 |  |

|              |          | <ul> <li>The minimum, typical, and maximum for the 2.5V power rail pin in Table<br/>208, "Electrical Characteristics".</li> </ul>        |  |

| 5396-DS102-R | 09/16/05 | Updated:                                                                                                                                 |  |

|              |          | <ul> <li>The minimum, typical, maximum, and units for the 2.5V power rail pin in<br/>Table 208, "Electrical Characteristics".</li> </ul> |  |

|              |          | Added:                                                                                                                                   |  |

|              |          | <ul> <li>3.3V power rail (IMP port) pin for IDD symbol in Table 208, "Electrical<br/>Characteristics"8.</li> </ul>                       |  |

| Revision              | Date     | Change Description                                                                                                                     |

|-----------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| 5396-DS101-R 09/13/05 |          | Updated:                                                                                                                               |

|                       |          | <ul> <li>Figure 16, "Serial EEPROM Connection," on page 42.</li> </ul>                                                                 |

|                       |          | <ul> <li>That the AUTO_POLL_DIS pin is pulled low, not high, during power-on/<br/>reset in "MDC/MDIO Interface" on page 44.</li> </ul> |

|                       |          | <ul> <li>Figure 17, "MDC/MDIO Interface," on page 44.</li> </ul>                                                                       |

|                       |          | • When the switch is master-sourcing to When the switch is slave-driven in<br>"MDC/MDIO Interface Register Programming" on page 49.    |

|                       |          | <ul> <li>In Table 23, "Signal Descriptions," on page 53.:</li> </ul>                                                                   |

|                       |          | <ul> <li>Description for HW_FWDG_EN.</li> </ul>                                                                                        |

|                       |          | <ul> <li>Type for EXTCLK.</li> </ul>                                                                                                   |

|                       |          | <ul> <li>Pages 50h–60h to Reserved in Table 26, "Global Page Register Map," on<br/>page 64.</li> </ul>                                 |

|                       |          | <ul> <li>The Description in Table 95, "ARL Search Control Register (Page 05h:<br/>Address 30h)," on page 98.</li> </ul>                |

|                       |          | <ul> <li>The Default in Table 169, "Queue N Weight Register (Page 30h: Address<br/>81h–84h)," on page 132.</li> </ul>                  |

|                       |          | Table 208, "Electrical Characteristics," on page 158.                                                                                  |

|                       |          | Added:                                                                                                                                 |

|                       |          | <ul> <li>Page 00 Addr 24H~25H Bit[10:8] to Table 19, "Serial LED Mode Matrix,"<br/>on page 50.</li> </ul>                              |

|                       |          | Removed:                                                                                                                               |

|                       |          | <ul> <li>From Table 7, "Behavior for Reserved Multicast Addresses," on page 19:</li> <li>01-80-C2-00-00-01</li> </ul>                  |

|                       |          | – 01-80-C2-00-00-10                                                                                                                    |

| 5396-DS100-R          | 04/15/05 | Initial release.                                                                                                                       |

# **Table of Contents**

| About This Document                      | 22 |

|------------------------------------------|----|

| Purpose and Audience                     |    |

| Acronyms and Abbreviations               | 22 |

| Document Conventions                     |    |

| Technical Support                        |    |

| Section 1: Introduction                  |    |

| Overview                                 | 23 |

| Data Sheet Information                   |    |

| Section 2: Features and Operation        |    |

| Overview                                 | 24 |

| Quality of Service                       | 24 |

| Egress Transmit Queues                   |    |

| Port-Based QoS                           |    |

| IEEE Standard 802.1P QoS                 |    |

| MAC-Based QoS                            | 27 |

| DiffServ QoS                             |    |

| Ethertype Based QoS                      | 27 |

| Frame Priority Decision Tree             |    |

| Port-Based VLAN                          |    |

| IEEE Standard 802.1Q VLAN                |    |

| VLAN Table Organization                  |    |

| Programming the VLAN Table               |    |

| Jumbo Frame Support                      |    |

| Port Trunking/Aggregation                | 31 |

| Broadcast Storm Suppression/Rate Control |    |

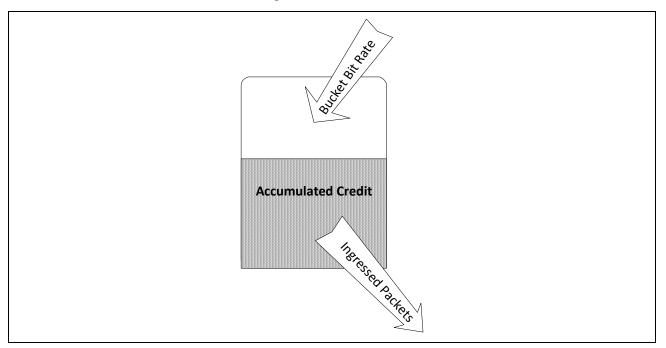

| Two-Bucket System                        |    |

| Bucket Bit Rate                          |    |

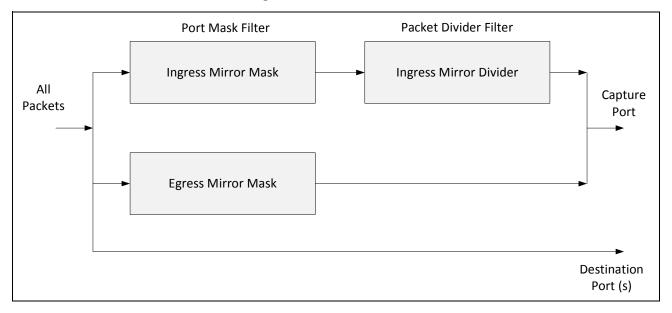

| Port Mirroring                           |    |

| Enabling Port Mirroring                  |    |

| Capture Port                             |    |

| Mirror Filtering Rules                   |    |

| Port Mask Filter                         |    |

| Packet Divider Filter                    |    |

| IGMP Snooping                            | 35 |

| ienni eneeping                           |    |

| IP Layer IGMP Snooping                   |    |

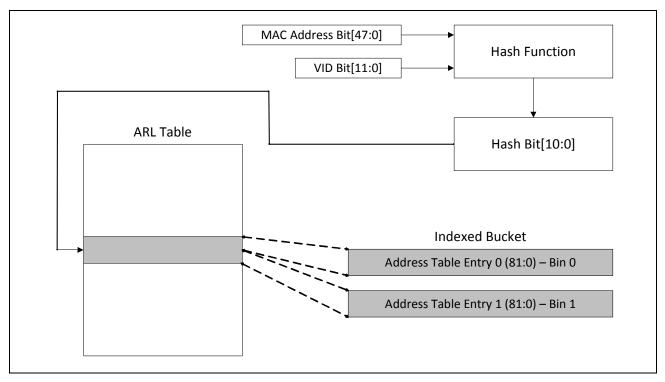

| Address Management                                     |    |

|--------------------------------------------------------|----|

| Address Table Organization                             |    |

| Address Learning                                       |    |

| Address Resolution and Frame Forwarding                |    |

| Unicast Addresses                                      |    |

| Multicast Addresses                                    |    |

| Reserved Multicast                                     |    |

| Using the Multiport Addresses                          |    |

| Static Address Entries                                 |    |

| Accessing the ARL Table Entries                        |    |

| Reading an ARL Entry                                   |    |

| Writing an ARL Entry                                   |    |

| Searching the ARL Table                                |    |

| Address Aging                                          |    |

| Fast Aging to Support Rapid Spanning Tree Protocol     |    |

| Bridge Management                                      |    |

| Spanning Tree Port State                               |    |

| Disable                                                |    |

| Blocking                                               |    |

| Listening                                              |    |

| Learning                                               |    |

| Forwarding                                             |    |

| Management Frames                                      |    |

| Multiple Spanning Tree Protocol (IEEE Standard 802.1s) |    |

| Section 3: System Functional Blocks                    |    |

| Overview                                               |    |

| Media Access Controller                                |    |

| Receive Function                                       |    |

| Transmit Function                                      |    |

| Flow Control                                           |    |

| 10/100 Mbps Half-Duplex Mode                           |    |

| 10/100/1000 Mbps Full-Duplex Mode                      |    |

| Integrated High-Performance Memory                     |    |

| Switch Controller                                      | 51 |

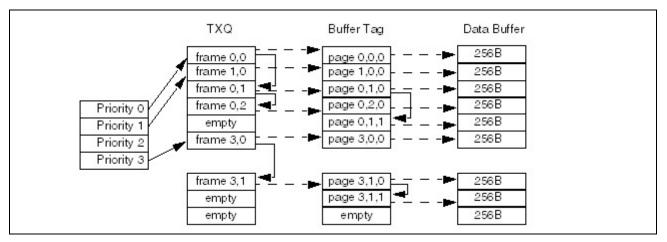

| Buffer Management                                      | 51 |

| Memory Arbitration                                     | 51 |

| Transmit Output Port Queues                            | 51 |

|                                                        |    |

| Section 4: System Interfaces                                             | 53 |

|--------------------------------------------------------------------------|----|

| Overview                                                                 | 53 |

| Serial Interface                                                         | 53 |

| SGMII Mode                                                               | 53 |

| SerDes Mode                                                              |    |

| SerDes/SGMII Auto-Negotiation                                            | 54 |

| Frame Management                                                         |    |

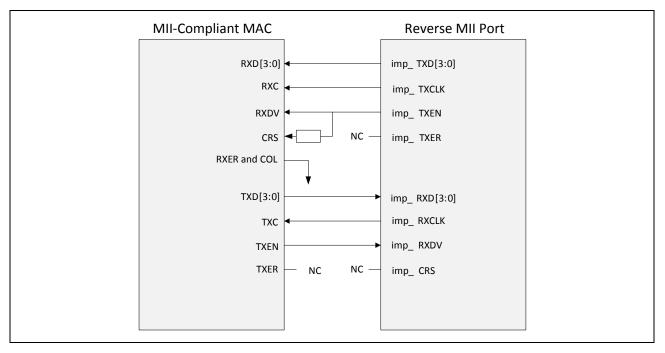

| Reverse MII Port                                                         |    |

| GMII Port                                                                | 55 |

| RGMII Port                                                               | 55 |

| In-Band Management Port                                                  |    |

| Programming Interfaces                                                   |    |

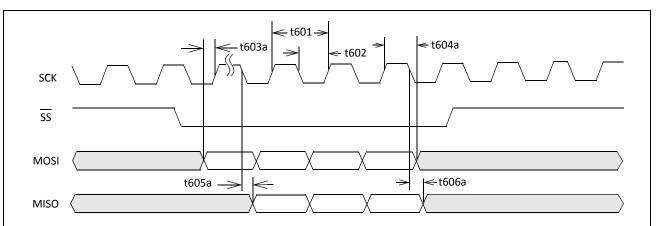

| SPI Interface                                                            |    |

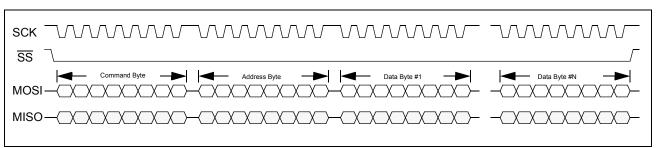

| Normal SPI Mode                                                          | 60 |

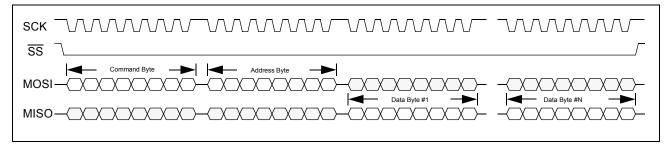

| Fast SPI Mode                                                            | 63 |

| EEPROM Interface                                                         | 64 |

| EEPROM Format                                                            | 65 |

| MDC/MDIO Interface                                                       |    |

| Register Access Through Pseudo-PHY Interface                             |    |

| MDC/MDIO Interface Register Programming                                  | 71 |

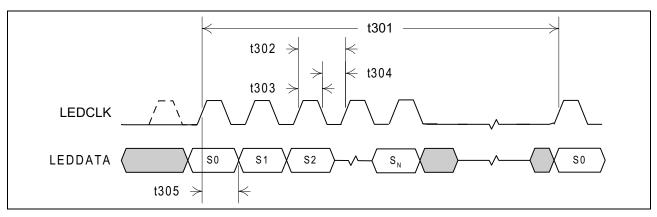

| LED Interfaces                                                           | 73 |

| Serial LED Interface                                                     | 73 |

| Section 5: Hardware Signal Definitions                                   | 76 |

| I/O Signal Types                                                         | 76 |

| Signal Descriptions                                                      | 77 |

| Section 6: Pin Assignments                                               | 83 |

| Section 7: Register Definitions                                          | 88 |

| Register Definition                                                      |    |

| Control Registers                                                        | 91 |

| 10/100/1000 Port N Control Register [0:15](Page 00h: Address 00h–0Fh)    |    |

| IMP Port (Port 16) Control Register (Page 00h: Address 10h)              |    |

| Switch Mode Register (Page 00h: Address 20h)                             |    |

| LED Control Register (Page 00h: Address 24h–25h)                         |    |

| New Control Register (Page 00h: Address 3Bh)                             |    |

| Reserved Multicast Control Register (Page 00h: Address 50h)              |    |

| Load Meter Update Rate Control Register (Page 00h: Address 51h)          |    |

| Unicast Lookup Failed Forward Map Register (Page 00h: Addr 54h–57h)      |    |

| Multicast Lookup Failed Forward Map Register (Page 00h: Address 58h–5Bh) | 97 |

|     | Port N State Override Register[0:15] (Page 00h: Address 60h–6Fh) | 97    |

|-----|------------------------------------------------------------------|-------|

|     | Port 16 (IMP) State Override Register (Page 00h: Address 70h)    | 98    |

|     | 802.1X Control Register 1 (Page 00h: Address 77h)                | 98    |

|     | 802.1X Control Register 2 (Page 00h: Address 78h–7Bh)            | 99    |

|     | SD_DEFAULT Register (Page 00h: Address 80h-83h)                  | 99    |

|     | SD_SEL_EARLY Register (Page 00h: Address 84h-85h)                | 99    |

|     | EXTERNAL_PHY_SCAN_CONTROL Register                               | 100   |

|     | Fast Aging Control Register (Page 00h: Address 88h)              | 100   |

|     | Fast Aging Port Register (Page 00h: Address 89h)                 | 101   |

|     | Fast Aging VID Register (Page 00h: Address 8Ah–8Bh)              | 101   |

|     | Pause Frame Detection Control Register (Page 00h: Address 90h)   | . 102 |

| Sta | tus Registers                                                    | 103   |

|     | Link Status Summary (Page 01h: Address 00h–03h)                  | 104   |

|     | Link Status Change (Page 01h: Address 04h–07h)                   | 104   |

|     | Port Speed Summary (Page 01h: Address 08h–0Fh)                   | 104   |

|     | Duplex Status Summary (Page 01h: Address 10h–13h)                | 105   |

|     | TX Pause Status Summary (Page 01h: Address 14h–17h)              | .105  |

|     | RX Pause Status Summary (Page 01h: Address 18h–1Bh)              | 105   |

|     | Port N PHY Status Register[0:15] (Page 01h: Address 20h–2Fh)     | 106   |

|     | SerDes Signal Detect Status Register (Page 01h: Address 40h)     | 106   |

|     | BIST Status Register (Page 01h, Address 46h)                     | 106   |

|     | Strap Value Register (Page 01h: Address 70h–73h)                 | 107   |

| Ма  | nagement Mode Registers                                          | . 108 |

|     | Global Management Configuration Register                         | 108   |

|     | Aging Time Control (Page 02h: Address 0Ch–0Fh)                   | 109   |

|     | Mirror Capture Control Register (Page 02h: Address 10h–11h)      | 109   |

|     | Ingress Mirror Control Register (Page 02h: Address 12h–15h)      | 110   |

|     | Ingress Mirror Divider (Page 02h: Address 16h–17h)               | 110   |

|     | Egress Mirror Control Register (Page 02h: Address 1Ch–1Fh)       | 110   |

|     | Model ID (Page 02h: Address 30h)                                 | . 111 |

|     | Revision ID (Page 02h: Address 40h)                              | 111   |

| AR  | L Control Registers                                              | . 112 |

|     | Global ARL Configuration Register (Page 04h: Address 00h)        | 112   |

|     | BPDU Multicast Address Register (Page 04h: Address 04h–09h)      | 113   |

|     | Multiport Address 1 Register (Page 04h: Address 10h–15h)         | 113   |

|     | Multiport Vector 1 Register (Page 04h: Address 16h–19h)          | 113   |

|     | Multiport Address 2 Register (Page 04h: Address 20h–25h)         | 114   |

|     | Multiport Vector 2 Register (Page 04h: Address 26h–29h)          | 114   |

| AR  | L/VLAN Table Access Registers                                    | . 114 |

|     |                                                                  |       |

|      | ARL Read/Write Control Register (Page 05h: Address 00h)          | 115 |

|------|------------------------------------------------------------------|-----|

|      | MAC Address Index Register (Page 05h: Address 02h–07h)           | 115 |

|      | VLAN ID Index Register (Page 05h: Address 08h–09h)               | 116 |

|      | ARL MAC/VID Entry 0 Register (Page 05h: Address 10h–17h)         | 116 |

|      | ARL FWD Entry 0 Register (Page 05h: Address 18h–1Bh)             | 116 |

|      | ARL MAC/VID Entry 1 Register (Page 05h: Address 20h–27h)         | 117 |

|      | ARL FWD Entry 1 Register (Page 05h: Address 28h–2Bh)             | 118 |

|      | ARL Search Control Register (Page 05h: Address 30h)              | 119 |

|      | ARL Search Address Register (Page 05h: Address 31h–32h)          | 119 |

|      | ARL Search MAC/VID Result Register 0 (Page 05h: Address 33h–3Ah) | 120 |

|      | ARL Search Result Register 0 (Page 05h: Address 3Bh–3Eh)         | 120 |

|      | ARL Search MAC/VID Result Register 1 (Page 05h: Address 40h–47h) | 121 |

|      | ARL Search Result Register 1 (Page 05h: Address 48h–4Bh)         | 121 |

|      | VLAN Table Read/Write Control Register (Page 05h: Address 60h)   | 122 |

|      | VLAN Table Address Index Register (Page 05h: Address 61h–62h)    | 122 |

|      | VLAN Table Entry Register (Page 05h: Address 63h–6Ah)            | 123 |

| Rese | erved Registers                                                  | 123 |

|      | Reserved (Page 0Ah: Register 00h–01h)                            | 125 |

|      | Reserved (Page 0Ah: Register 10h–11h)                            | 125 |

|      | Reserved (Page 0Ah: Register 20h–27h)                            | 125 |

|      | Reserved (Page 0Ah: Register 28h–2Fh)                            | 125 |

|      | Reserved (Page 0Ah: Register 30h–37h)                            | 125 |

|      | Reserved (Page 0Ah: Register 38h–3Fh)                            | 125 |

|      | Reserved (Page 0Ah: Register 40h–47h)                            | 125 |

|      | Reserved (Page 0Ah: Register 48h–4Fh)                            | 125 |

|      | Reserved (Page 0Ah: Register 56h–57h)                            | 125 |

|      | Reserved (Page 0Ah: Register 58h–59h)                            | 125 |

|      | Reserved (Page 0Ah: Register 5Ah–5Bh)                            | 125 |

|      | Reserved (Page 0Ah: Register 5Ch–5Dh)                            | 125 |

|      | Reserved (Page 0Ah: Register 60h–67h)                            | 125 |

|      | Reserved (Page 0Ah: Register 70h–77h)                            | 125 |

|      | Reserved (Page 0Ah: Register 78–79h)                             | 125 |

|      | Reserved (Page 0Ah: Register 80h–81h)                            | 125 |

|      | Reserved (Page 0Ah: Register 90h–91h)                            | 125 |

|      | Reserved (Page 0Ah: Register 92h–93h)                            | 126 |

|      | Reserved (Page 0Ah: Register 94h–95h)                            | 126 |

|      | Reserved (Page 0Ah: Register 96h–97h)                            | 126 |

|      | Reserved (Page 0Ah: Register 98h–99h)                            | 126 |

|      | Reserved (Page 0Ah: Register 9Ah–9Bh)                            | 126 |

|      | Reserved (Page 0Ah: Register 9Ch–9Dh)                                  | 126 |

|------|------------------------------------------------------------------------|-----|

|      | Reserved (Page 0Ah: Register 9Eh–9Fh)                                  | 126 |

| Inte | rnal SerDes Registers (Port 0–15): Page 10h–1fh                        | 127 |

|      | MII Control Register (Page 10h–1Fh: Address 00h–01h)                   | 128 |

|      | MII Status Register (Page 10h–1Fh: Address 02h–03h)                    | 129 |

|      | Auto-Negotiation Advertisement (Page 10h–1Fh: Address 08h–09h)         | 131 |

|      | Auto-Negotiation Link Partner Ability (Page 10h–1Fh: Address 0Ah–0Bh)  | 131 |

|      | Auto-Negotiation Expansion (Page 10h–1Fh: Address 0Ch–0Dh)             | 133 |

|      | Extended Status Register (Page 10h–1Fh: Address 1Eh–1Fh)               | 133 |

|      | SerDes/SGMII Control 1 (Page 10h–1Fh: Address 20H ~ 21H, BLOCK 0)      | 133 |

|      | Analog Transmit Register (Page 10H ~ 1FH: Address 20H ~ 21H BLOCK 1.)  | 136 |

|      | SerDes/SGMII Control 2 (Page 10h–1Fh: Address 22h–23h)                 | 136 |

|      | SerDes/SGMII Control 3 (Page 10h–1Fh: Address 24h–25h)                 | 137 |

|      | Reserved (Page 10h–1Fh: Address 26h–27h)                               | 138 |

|      | SerDes/SGMII Status 1 (Page 10h–1Fh: Address 28h–29h)                  | 138 |

|      | SerDes/SGMII Status 2 (Page 10h–1Fh: Address 2Ah–2Bh)                  | 139 |

|      | SerDes/SGMII Status 3 (Page 10h–1Fh: Address 2Ch–2Dh)                  | 140 |

|      | BER/CRC Error Counter Register (Page 10h ~ 1Fh: Address 2Eh ~ 2Fh)     | 141 |

|      | PRBS Control Register (Page 10h ~ 1Fh: Address 30h ~ 31h)              | 141 |

|      | PRBS Status Register (Page 10h ~ 1Fh: Address 32h ~ 33h)               | 142 |

|      | Pattern Generator Control Register (Page 10H ~ 1Fh: Address 34h ~ 35h) | 142 |

|      | Pattern Generator Control Register (Page 10H ~ 1Fh: Address 36h ~ 37h) | 143 |

|      | Force Transmit 1 Register (Page 10h ~ 1Fh: Address 3Ah ~ 3Bh)          | 144 |

|      | Force Transmit 2 Register (Page 10h ~ 1Fh: Address 3Ch ~ 3Dh)          | 144 |

|      | Block Address (Pages 10h–1Fh: Address 3Eh ~ 3Fh)                       | 144 |

| Qos  | S Registers                                                            | 145 |

|      | QoS Global Control Register(Page 30h: Address 00h)                     | 146 |

|      | QoS Threshold Control Register (Page 30h: Address 01h–02h)             | 147 |

|      | QoS 1P Enable Register (Page 30h: Address 04h–07h)                     | 147 |

|      | QoS DiffServ Enable Register (Page 30h: Address 08h–0Bh)               | 147 |

|      | 802.1P/1Q Priority Map Register (Page 30h: Address 10h-13h)            | 147 |

|      | DiffServ Priority Map 0 Register (Page 30h: Address 30h-35h)           | 148 |

|      | DiffServ Priority Map 1 Register (Page 30h: Address 36h–3Bh)           | 149 |

|      | DiffServ Priority Map 2 Register (Page 30h: Address 3Ch-41h)           | 150 |

|      | DiffServ Priority Map 3 Register(Page 30h: Address 42h-47h)            | 150 |

|      | QoS RX Port N (0–16) Control Register(Page 30h: Address 50h–71h)       | 151 |

|      | QoS TX Control Register (Page 30h: Address 80h)                        |     |

|      | Queue N (0-3) Weight Register (Page 30h: Address 81h-84h)              | 152 |

|      | EtherType Priority Control Register (Page 30h: Address 88h-8Bh)        | 153 |

| Enable Traffic Priority Remap Control Register (Page 30h: Address A0h–A3h)      | 153 |

|---------------------------------------------------------------------------------|-----|

| Traffic Priority Remap Register (Page 30h: Address A4h)                         | 153 |

| Port-Based VLAN Control Registers                                               | 154 |

| Port VLAN Control Register (Page 31h: Address 00h–43h)                          | 154 |

| Trunking Registers                                                              |     |

| MAC Trunking Control Register (Page 32h: Address 01h)                           | 156 |

| Trunking Group Register (Page 32h: Address 90h–9Fh)                             | 157 |

| IEEE Standard 802.1Q VLAN Registers                                             |     |

| Global Control 0 Register (Page 34h: Address 00h)                               | 158 |

| Global Control 1 Register (Page 34h: Address 01h)                               | 159 |

| Global Control 2 Register (Page 34h: Address 02h)                               | 160 |

| Global Control 3 Register (Page 34h: Address 03h)                               | 160 |

| Global Control 4 Register (Page 34h: Address 07h)                               | 160 |

| Global Control 5 Register (Page 34h: Address 08h)                               | 161 |

| New Priority Map Register (Page 34h: Address 0Ch-0Fh)                           | 162 |

| Port N (0–16) Default 802.1Q Tag Register (Page 34h: Address 10h–31h)           | 162 |

| Jumbo Frame Control Registers                                                   |     |

| Jumbo Frame Port Mask Register (Page 40h: Address 01h–04h)                      | 163 |

| Broadcast Storm Suppression Registers                                           |     |

| Suppression Control Register (Page 41h: Address 00h–03h)                        | 165 |

| Port N (0–15) Receive Rate Control Register (Page 41h: Address 10h–4Fh)         | 166 |

| Port N (0–15) Suppressed Packet Drop Count Register (Page 41h: Address 80h–9Fh) | 168 |

| IEEE Standard 802.1s Multiple Spanning Tree Registers                           | 169 |

| Multiple Spanning Tree Control Register (Page 43h: Address 00h)                 | 170 |

| Multiple Spanning Tree Table Register (Page 43h: Address 10h–CFh)               | 170 |

| Page 80–8Fh: External PHY Registers (Serial Ports)                              | 172 |

| Global Registers                                                                |     |

| SPI Data I/O Register                                                           |     |

| SPI Status Register                                                             | 175 |

| Page Register                                                                   | 175 |

| Section 8: Electrical Characteristics                                           | 176 |

| Absolute Maximum Ratings                                                        |     |

| Recommended Operating Conditions                                                |     |

| Electrical Characteristics                                                      |     |

| Section 9: Timing Characteristics                                               |     |

| Reset and Clock Timing                                                          |     |

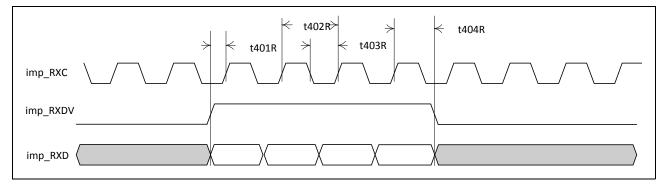

| Reverse MII Timing                                                              |     |

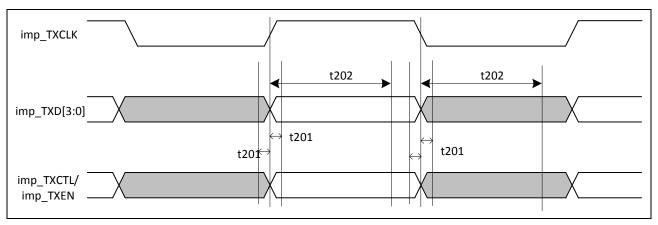

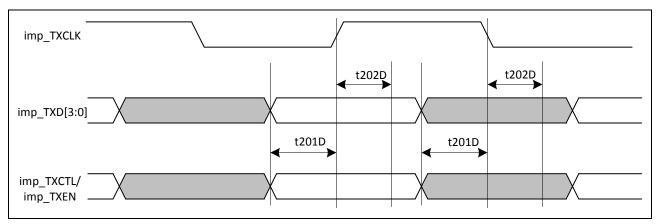

| Reverse MII Output Timing                                                       |     |

|                                                                                 |     |

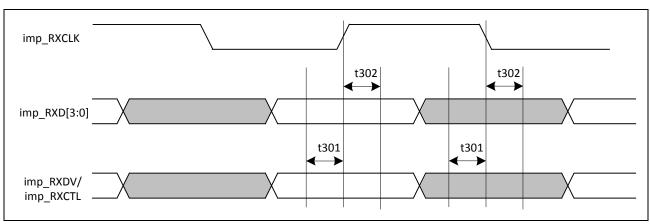

| Reverse MII Input Timing            |     |

|-------------------------------------|-----|

| RGMII Interface Timing              |     |

| RGMII Output Timing (Normal Mode)   |     |

| RGMII Output Timing (Delayed Mode)  |     |

| RGMII Input Timing (Normal Mode)    |     |

| RGMII Input Timing (Delayed Mode)   |     |

| GMII Interface Timing               |     |

| GMII Interface Output Timing        |     |

| GMII Interface Input Timing         |     |

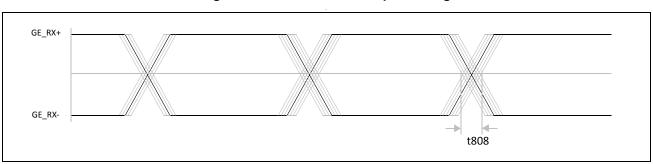

| Serial Interface Timing             |     |

| Serial Interface Output Timing      |     |

| Serial Interface Input Timing       |     |

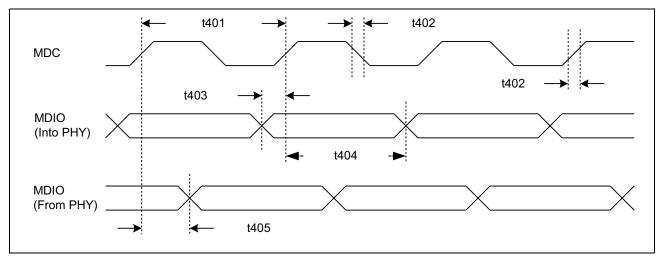

| MDC[0]/MDIO[0] Timing               |     |

| Serial LED Interface Timing         |     |

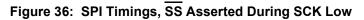

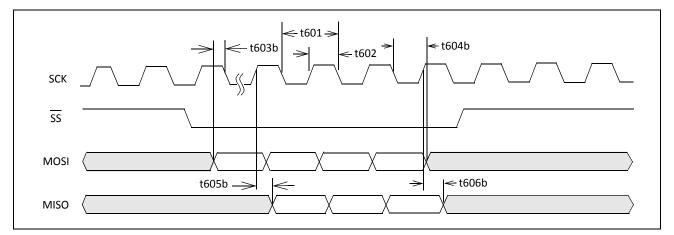

| SPI Timings                         |     |

| EEPROM Timing                       |     |

| Section 10: Thermal Characteristics | 192 |

| Section 11: Mechanical Information  | 193 |

| Section 12: Ordering Information    |     |

# List of Figures

| Figure 1: Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Figure 2: Priority Packet Mapping Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25                                                                        |

| Figure 3: VLAN Table Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29                                                                        |

| Figure 4: Bucket Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32                                                                        |

| Figure 5: Mirror Filter Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34                                                                        |

| Figure 6: Address Table Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37                                                                        |

| Figure 7: TXQ and Buffer Tag Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52                                                                        |

| Figure 8: RvMII Port Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55                                                                        |

| Figure 9: Normal SPI Command Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 59                                                                        |

| Figure 10: Fast SPI Command Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59                                                                        |

| Figure 11: SPI Serial Interface Write Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 60                                                                        |

| Figure 12: SPI Serial Interface Read Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60                                                                        |

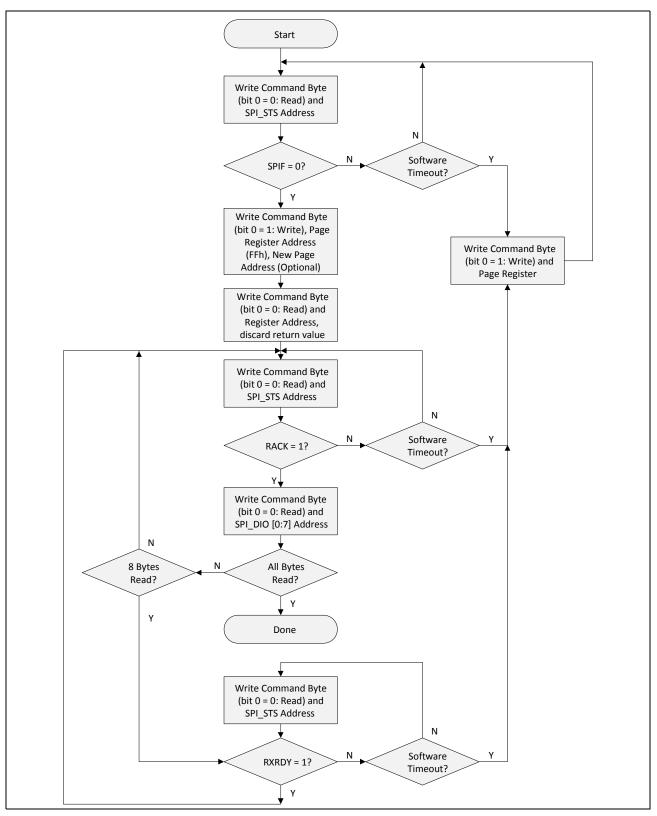

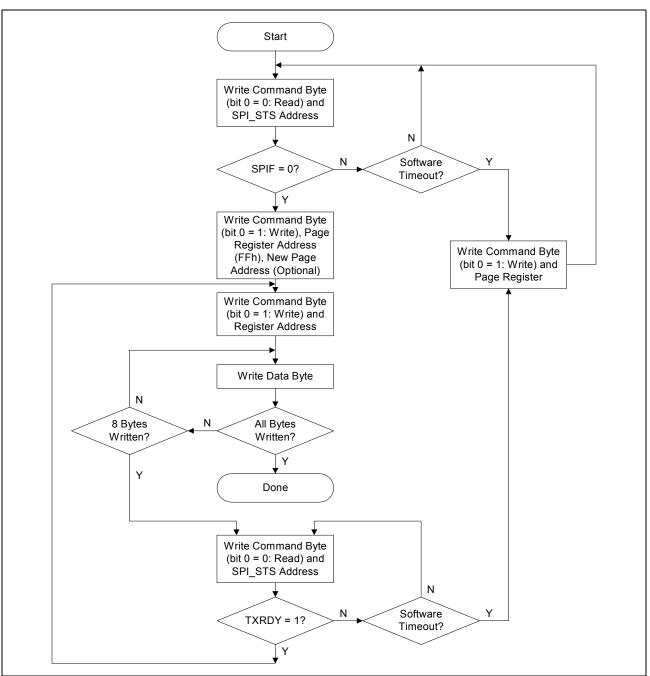

| Figure 13: Normal SPI Mode Read Flow Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 61                                                                        |

| Figure 14: Normal SPI Mode Write Flow Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63                                                                        |

| Figure 15: Timing Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64                                                                        |

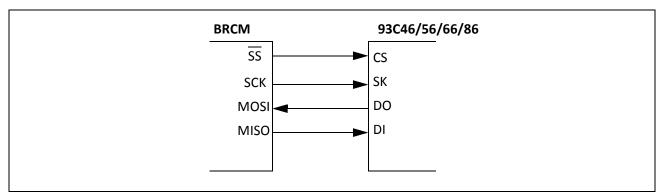

| Figure 16: Serial EEPROM Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65                                                                        |

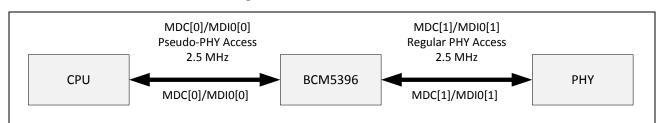

| Figure 17: MDC/MDIO Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66                                                                        |

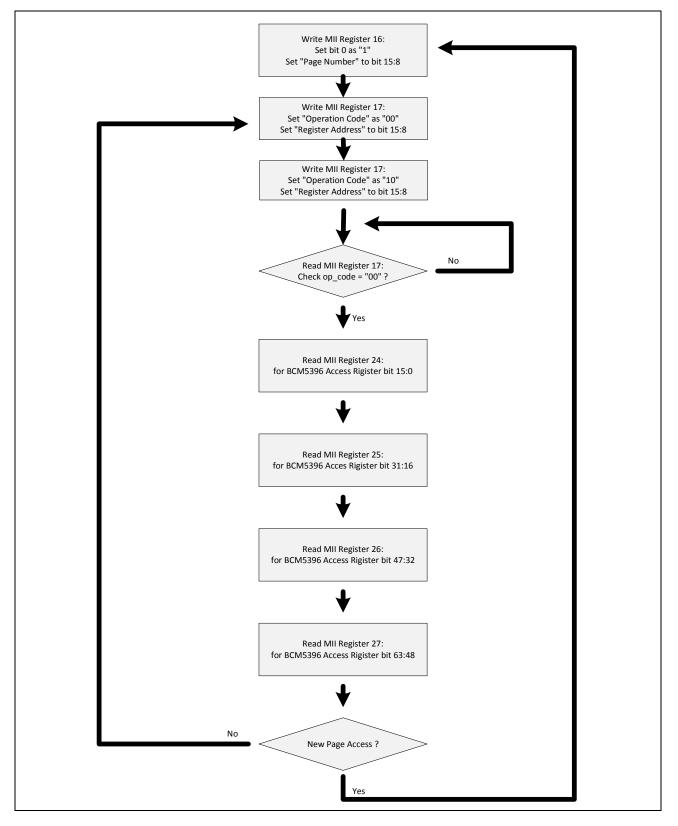

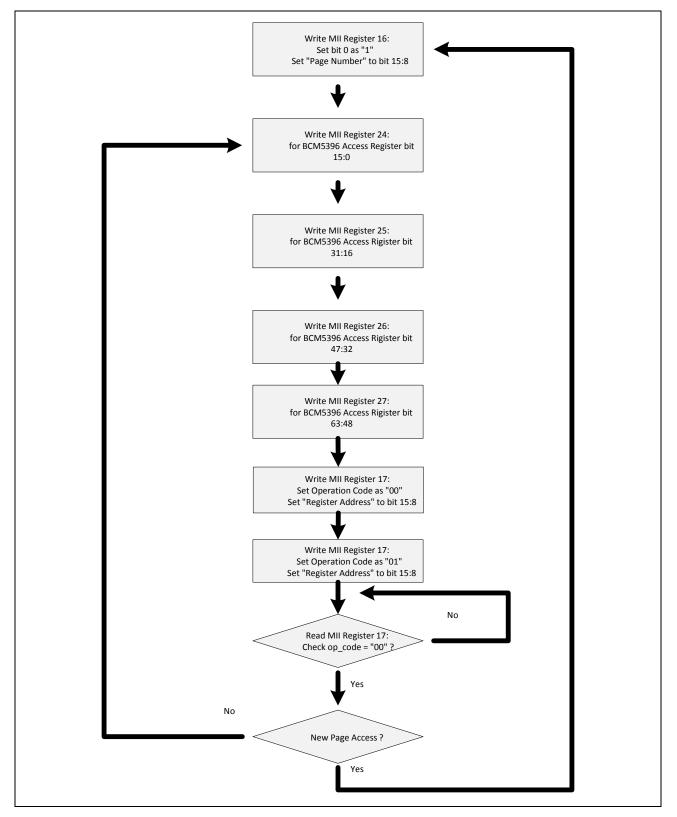

| Figure 18: Read Access to Switch via Pseudo-PHY (PHY ADD = 1_1110) MDC[0]/MDIO[0] Path                                                                                                                                                                                                                                                                                                                                                                                                                                          | 68                                                                        |

| Figure 19: Write Access to Switch via Pseudo-PHY (PHY ADD = 1_1110) MDC[0]/MDIO[0] Path                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69                                                                        |

| Figure 20: Pseudo-PHY MII Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70                                                                        |

| Figure 21: Pins Top View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87                                                                        |

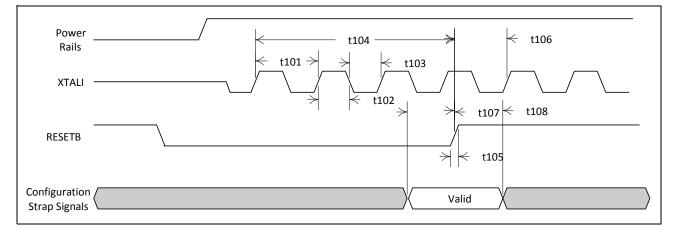

| Figure 22: Reset and Clock Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |

| rigure 22. Reset and Glock Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 179                                                                       |

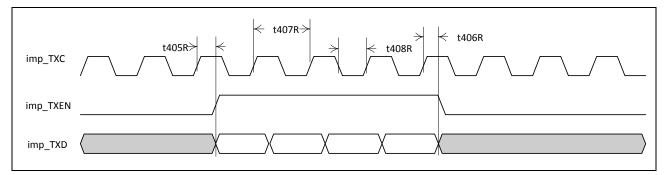

| Figure 23: RvMII Mode Output Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 180                                                                       |

| Figure 23: RvMII Mode Output Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 180<br>180                                                                |

| Figure 23: RvMII Mode Output Timings<br>Figure 24: RvMII Mode Input Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 180<br>180<br>181                                                         |

| Figure 23: RvMII Mode Output Timings<br>Figure 24: RvMII Mode Input Timings<br>Figure 25: RGMII Output Timing (Normal Mode)                                                                                                                                                                                                                                                                                                                                                                                                     | 180<br>180<br>181<br>182                                                  |

| Figure 23:       RvMII Mode Output Timings         Figure 24:       RvMII Mode Input Timings         Figure 25:       RGMII Output Timing (Normal Mode)         Figure 26:       RGMII Output Timing (Delayed Mode)                                                                                                                                                                                                                                                                                                             | 180<br>180<br>181<br>182<br>183                                           |

| <ul> <li>Figure 23: RvMII Mode Output Timings</li> <li>Figure 24: RvMII Mode Input Timings</li> <li>Figure 25: RGMII Output Timing (Normal Mode)</li> <li>Figure 26: RGMII Output Timing (Delayed Mode)</li> <li>Figure 27: RGMII Input Timing (Normal Mode)</li> </ul>                                                                                                                                                                                                                                                         | 180<br>180<br>181<br>182<br>183<br>184                                    |

| <ul> <li>Figure 23: RvMII Mode Output Timings</li> <li>Figure 24: RvMII Mode Input Timings</li> <li>Figure 25: RGMII Output Timing (Normal Mode)</li> <li>Figure 26: RGMII Output Timing (Delayed Mode)</li> <li>Figure 27: RGMII Input Timing (Normal Mode)</li> <li>Figure 28: RGMII Input Timing (Delayed Mode)</li> </ul>                                                                                                                                                                                                   | 180<br>180<br>181<br>182<br>183<br>184<br>185                             |

| <ul> <li>Figure 23: RvMII Mode Output Timings</li> <li>Figure 24: RvMII Mode Input Timings</li> <li>Figure 25: RGMII Output Timing (Normal Mode)</li> <li>Figure 26: RGMII Output Timing (Delayed Mode)</li> <li>Figure 27: RGMII Input Timing (Normal Mode)</li> <li>Figure 28: RGMII Input Timing (Delayed Mode)</li> <li>Figure 29: GMII Output Timing (Delayed Mode)</li> </ul>                                                                                                                                             | 180<br>180<br>181<br>182<br>183<br>183<br>185<br>185                      |

| <ul> <li>Figure 23: RvMII Mode Output Timings</li> <li>Figure 24: RvMII Mode Input Timings</li> <li>Figure 25: RGMII Output Timing (Normal Mode)</li> <li>Figure 26: RGMII Output Timing (Delayed Mode)</li> <li>Figure 27: RGMII Input Timing (Normal Mode)</li> <li>Figure 28: RGMII Input Timing (Delayed Mode)</li> <li>Figure 29: GMII Output Timing (Delayed Mode)</li> <li>Figure 30: GMII Input Timing</li> </ul>                                                                                                       | 180<br>180<br>181<br>182<br>183<br>184<br>185<br>185<br>186               |

| <ul> <li>Figure 23: RvMII Mode Output Timings</li> <li>Figure 24: RvMII Mode Input Timings</li> <li>Figure 25: RGMII Output Timing (Normal Mode)</li> <li>Figure 26: RGMII Output Timing (Delayed Mode)</li> <li>Figure 27: RGMII Input Timing (Normal Mode)</li> <li>Figure 28: RGMII Input Timing (Delayed Mode)</li> <li>Figure 29: GMII Output Timing (Delayed Mode)</li> <li>Figure 29: GMII Output Timing</li> <li>Figure 30: GMII Input Timing</li> <li>Figure 31: Serial Interface Output Timing</li> </ul>             | 180<br>180<br>181<br>182<br>183<br>183<br>185<br>185<br>186<br>187        |

| <ul> <li>Figure 23: RvMII Mode Output Timings</li> <li>Figure 24: RvMII Mode Input Timings</li> <li>Figure 25: RGMII Output Timing (Normal Mode)</li> <li>Figure 26: RGMII Output Timing (Delayed Mode)</li> <li>Figure 27: RGMII Input Timing (Normal Mode)</li> <li>Figure 28: RGMII Input Timing (Delayed Mode)</li> <li>Figure 29: GMII Output Timing (Delayed Mode)</li> <li>Figure 30: GMII Output Timing</li> <li>Figure 31: Serial Interface Output Timing</li> <li>Figure 32: Serial Interface Input Timing</li> </ul> | 180<br>180<br>181<br>182<br>183<br>183<br>185<br>185<br>186<br>187<br>187 |

| Figure 36: SPI Timings, SS Asserted During SCK Low | 190   |

|----------------------------------------------------|-------|

| Figure 37: EEPROM Timing                           | . 191 |

| Figure 38: 256-Pin FBGA Package Outline Drawing    | 193   |

# **List of Tables**

| Table 1: Frame Priority Decision Tree Summary                             |    |

|---------------------------------------------------------------------------|----|

| Table 2: Bucket Bit Rate                                                  | 33 |

| Table 3: Unicast Forward Field Definitions                                | 39 |

| Table 4: Address Table Entry for Unicast Address                          | 39 |

| Table 5: Multicast Forward Field Definitions                              | 41 |

| Table 6: Address Table Entry for Multicast ARL Address                    | 41 |

| Table 7: Behavior for Reserved Multicast Addresses                        | 42 |

| Table 8: Spanning Tree State                                              | 46 |

| Table 9: SGMII and SerDes Auto-Negotiation                                | 54 |

| Table 10: Transmit/Receive Frame Format Over Management Port              | 56 |

| Table 11: OPCODE Field in BRCM Tag for Management Port Frame              | 57 |

| Table 12: IMP Broadcom TAG RX from CPU                                    | 57 |

| Table 13: IMP Broadcom TAG TX to CPU                                      | 58 |

| Table 14: EEPROM_EXT[1:0] Settings                                        | 64 |

| Table 15: EEPROM Header Format                                            | 65 |

| Table 16: EEPROM Contents                                                 | 65 |

| Table 17: Pseudo-PHY MII Register Definitions                             | 71 |

| Table 18: MII Management Frame Format                                     | 72 |

| Table 19: Serial LED Mode Matrix                                          | 73 |

| Table 20: Serial LED Status Types                                         | 74 |

| Table 21: Load Meter LED Decode                                           | 74 |

| Table 22: I/O Signal Type Definitions                                     | 76 |

| Table 23: Signal Descriptions                                             | 77 |

| Table 24: Pin Assignment (Listed by Pin Number)                           | 83 |

| Table 25: Pin Assignment (Listed by Signal Name)                          | 85 |

| Table 26: Global Page Register Map                                        | 88 |

| Table 27: Control Registers (Page 00h)                                    | 91 |

| Table 28: 10/100/1000 Port Control Register (Page 00h: Address 00h–0Fh)   | 93 |

| Table 29: IMP Port Control Register (Page 00h: Address 10h)               | 93 |

| Table 30: Switch Mode Register (Page 00h: Address 20h)                    | 94 |

| Table 31: LED A Register (Page 00h: Address 24h–25h)                      | 95 |

| Table 32: New Control Register (Page 00h: Address 3Bh)                    | 95 |

| Table 33: Reserved Multicast Register (Page 00h: Address 50h)             |    |

| Table 34: Load Meter Update Rate Control Register (Page 00h: Address 51h) | 96 |

| Table 35: Unicast Lookup Failed Forward Map Register (Page 00h: 54h–57h)  | 97 |

| Table 36: | Multicast Lookup Failed Forward Map Register (Page 00h: Address 58h-5Bh)        | 97  |

|-----------|---------------------------------------------------------------------------------|-----|

| Table 37: | Port N State Override Register (Page 00h: Address 60–6Fh)                       | 97  |

| Table 38: | Port 16 (IMP) State Override Register (Page 00h: Address 70h)                   | 98  |

| Table 39: | 802.1X Control Register 1 (Page 00h: Address 77h)                               | 98  |

| Table 40: | 802.1X Control Register 2 (Page 00h: Address 78h–7Bh)                           | 99  |

| Table 41: | SerDes Default Values Register (Page 00h: Address 80h-83h)                      | 99  |

| Table 42: | SerDes Select Early Version of CRS and COL Register (Page 00h: Address 84h-85h) | 99  |

| Table 43: | External PHY Scan Control Register (Page 00h: Address 86h)                      | 100 |

| Table 44: | Fast Aging Control Register (Page 00h: Address 88h)                             | 100 |

| Table 45: | Fast Aging Port Register (Page 00h: Address 89h)                                | 101 |

| Table 46: | Fast Aging VID Register (Page 00h: Address 138d–139d, 8Ah–8Bh)                  | 101 |

| Table 47: | Pause Frame Detection Control Register (Page 00h: Address 90h)                  | 102 |

| Table 48: | Status Registers (Page 01h)                                                     | 103 |

| Table 49: | Link Status Summary Register (Page 01h: Address 00h–03h)                        | 104 |

| Table 50: | Link Status Change Register (Page 01h: Address 04h–07h)                         | 104 |

| Table 51: | Port Speed Summary Register (Page 01h: Address 08h–0Fh)                         | 104 |

| Table 52: | Duplex Status Summary Register (Page 01h: Address 10h–13h)                      | 105 |

| Table 53: | TX PAUSE Status Summary Register (Page 01h: Address 14h–17h)                    | 105 |

| Table 54: | RX PAUSE Status Summary Register (Page 01h: Address 18h–1Bh)                    | 105 |

| Table 55: | Port N PHY Status Register (Page 01h: Address 20–2Fh)                           | 106 |

| Table 56: | SerDes Signal Detect Status Register (Page 01h: Address 40h)                    | 106 |

| Table 57: | BIST Status Register (Page 01h, Address 46h)                                    | 106 |

| Table 58: | Strap Value Register (Page 01h: Address 70h–73h)                                | 107 |

| Table 59: | Management Mode Registers (Page 02h)                                            | 108 |

| Table 60: | Global Management Configuration Register (Page 02h: Address 00h)                | 108 |

| Table 61: | Aging Time Control Register (Page 02h: Address 0Ch-0Fh)                         | 109 |

| Table 62: | Mirror Capture Control Register (Page 02h: Address 10h-11h)                     | 109 |

| Table 63: | Ingress Mirror Control Register (Page 02h: Address 12h–15h)                     | 110 |

| Table 64: | Ingress Mirror Divider Register (Page 02h: Address 16h–17h)                     | 110 |

| Table 65: | Egress Mirror Control Register (Page 02h: Address 1Ch-1Fh)                      | 110 |

| Table 66: | Model ID Register (Page 02h: Address 30h)                                       | 111 |

| Table 67: | Revision ID Register (Page 02h: Address 40h)                                    | 111 |

| Table 68: | ARL Control Registers (Page 04h)                                                | 112 |

| Table 69: | Global ARL Configuration Register (Page 04h: Address 00h)                       | 112 |

| Table 70: | BPDU Multicast Address Register (Page 04h: Address 04h–09h)                     | 113 |

| Table 71: | Multiport Address 1 Register (Page 04h: Address 10h–15h)                        | 113 |

| Table 72: | Multiport Vector 1 Register (Page 04h: Address 16h–19h)                         | 113 |

| Table 73: Multiport Address 2 Register (Page 04h: Address 20h–25h)               | 114 |

|----------------------------------------------------------------------------------|-----|

| Table 74: Multiport Vector 2 Register (Page 04h: Address 26h–29h)                | 114 |

| Table 75: ARL/VLAN Access Registers (Page 05h)                                   | 114 |

| Table 76: ARL Read/Write Control Register (Page 05h: Address 00h)                | 115 |

| Table 77: MAC Address Index Register (Page 05h: Address 02h–07h)                 | 115 |

| Table 78: VID Index Register (Page 05h: Address 08h–09h)                         | 116 |

| Table 79: ARL MAC/VID Entry 0 Register (Page 05h: Address 10h–17h)               | 116 |

| Table 80: ARL FWD Entry 0 Register (Page 05h: Address 18h–1Bh)                   | 116 |

| Table 81: ARL MAC/VID Entry 1 Register (Page 05h: Address 20h–27h)               | 117 |

| Table 82: ARL FWD Entry 1 Register (Page 05h: Address 28h–2Bh)                   | 118 |

| Table 83: ARL Search Control Register (Page 05h: Address 30h)                    | 119 |

| Table 84: ARL Search Address Register (Page 05h: Address 31h–32h)                | 119 |

| Table 85: ARL Search MAC/VID Result Register 0 (Page 05h: Address 33h–3Ah)       | 120 |

| Table 86: ARL Search Result Register 0 (Page 05h: Address 3Bh-3Eh)               | 120 |

| Table 87: ARL Search MAC/VID Result Register 1 (Page 05h: Address 40h-47h)       | 121 |

| Table 88: ARL Search Result Register 1 (Page 05h: Address 48h–4Bh)               | 121 |

| Table 89: VLAN Table Read/Write Control Register (Page 05h: Address 60h)         | 122 |

| Table 90: VLAN Table Address Index Register (Page 05h: Address 61h-62h)          | 122 |

| Table 91: VLAN Table Entry Register (Page 05h: Address 63h–6Ah)                  | 123 |

| Table 92: Flow Control Registers (Page 0Ah)                                      | 123 |

| Table 93: Internal SerDes Registers Page Descriptions 10h–1Fh                    | 127 |

| Table 94: Internal SerDes Registers Page 10h–1Fh                                 | 127 |

| Table 95: MII Control (Page 10h–1Fh: Address 00h–01h)                            | 128 |

| Table 96: MII Status (Page 10h–1Fh: Address 02h–03h)                             | 129 |

| Table 97: Auto-Negotiation Advertisement (Page 10h–1Fh: Address 08h–09h)         | 131 |

| Table 98: Auto-Negotiation Link Partner Ability (Page 10h–1Fh: Address 0Ah–0Bh)  | 131 |

| Table 99: Auto-Negotiation Expansion (Page 10h–1Fh: Address 0Ch–0Dh)             | 133 |

| Table 100: Extended Status (Page 10h–1Fh: Address 1Eh–1Fh)                       | 133 |

| Table 101: SerDes/SGMII Control1 (Page 10h–1Fh: Address 20h–21h, Block 0)        | 133 |

| Table 102: Analog Transmit Register (Page 10h ~ 1Fh: Address 20h ~ 21h, Block 1) | 136 |

| Table 103: SerDes/SGMII Control 2 (Page 10h–1Fh: Address 22h–23h)                | 136 |

| Table 104: SerDes/SGMII Control 3 (Page 10h–1Fh: Address 24h–25h)                | 137 |

| Table 105: SerDes/SGMII Status 1 (Page 10h–1Fh: Address 28h–29h)                 | 138 |

| Table 106: SerDes/SGMII Status 2 (Page 10h–1Fh: Address 2Ah–2Bh)                 | 139 |

| Table 107: SerDes/SGMII Status 3 (Page 10h–1Fh: Address 2Ch–2Dh)                 | 140 |

| Table 108: BER/CRC Error Counter Register (Page 10h ~ 1Fh: Address 2Eh ~ 2Fh)    | 141 |

| Table 109: PRBS Control Register (Page 10h ~ 1Fh: Address 30h ~ 31h)             | 141 |

| Table 110: | PRBS Status Register (Page 10h ~ 1Fh: Address 32h ~ 33h)                   | . 142 |

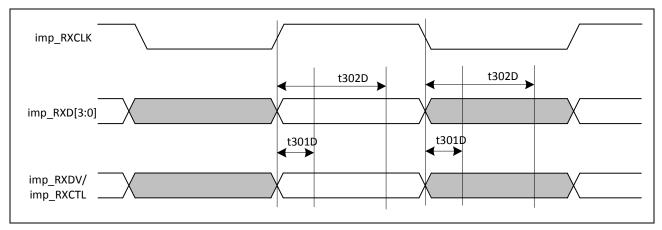

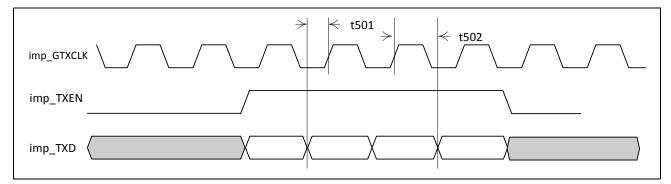

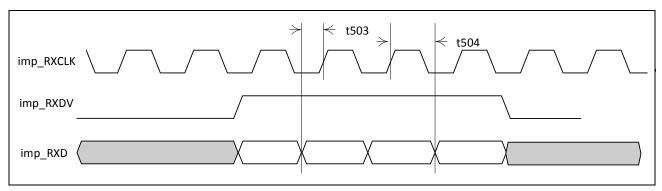

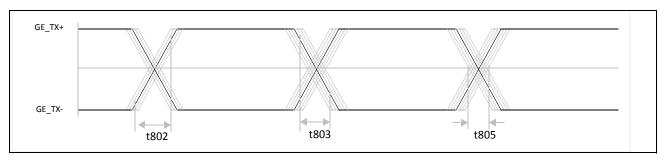

|------------|----------------------------------------------------------------------------|-------|