## HCPL-2602, HCPL-2612 High CMR Line Receiver Optocouplers

# **Data Sheet**

## Description

The HCPL-2602/12 are optically coupled line receivers that combine a GaAsP light emitting diode, an input current regulator and an integrated high gain photo detector. The input regulator serves as a line termination for line receiver applications. It clamps the line voltage and regulates the LED current so line reflections do not interfere with circuit performance.

The regulator allows a typical LED current of 8.5 mA before it starts to shunt excess current. The output of the detector IC is an open collector Schottky clamped transistor. An enable input gates the detector. The internal detector shield provides a guaranteed common mode transient immunity specification of 1000 V/ms for the 2602, and 3500 V/ms for the 2612.

DC specifications are defined similar to TTL logic. The optocoupler ac and dc operational parameters are guaranteed from  $0^{\circ}$ C to  $70^{\circ}$ C allowing trouble-free interfacing with digital logic circuits. An input current of 5 mA will sink an eight gate fan-out (TTL) at the output.

## Features

- 1000 V/µs minimum Common Mode Rejection (CMR) at  $V_{CM}=50$  V for HCPL-2602 and 3.5 kV/µs minimum CMR at  $V_{CM}=300$  V for HCPL-2612

- · Line termination included no extra circuitry required

- · Accepts a broad range of drive conditions

- · LED protection minimizes LED efficiency degradation

- High speed: 10 MBd (limited by transmission line in many applications)

- Guaranteed AC and DC performance over temperature:  $0^\circ\text{C}$  to  $70^\circ\text{C}$

- External base lead allows "LED peaking" and LED current adjustment

- Safety approval UL recognized – 3750 V rms for 1 Minute CSA approved

- MIL-PRF-38534 hermetic version available (HCPL-1930/1)

#### **Applications**

- · Isolated line receiver

- Computer-peripheral interface

- · Microprocessor system interface

- Digital isolation for A/D, D/A conversion

- Current sensing

- · Instrument input/output isolation

- · Ground loop elimination

- · Pulse transformer replacement

- · Power transistor isolation in motor drives

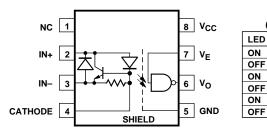

## **Functional Diagram**

A 0.1 µF bypass capacitor must be connected between pins 5 and 8.

CAUTION: It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

TRUTH TABLE (POSITIVE LOGIC)

OUTPUT

н

н

н

L

н

ENABLE

н

н

L

NC

The HCPL-2602/12 are useful as line receivers in high noise environments that conventional line receivers cannot tolerate. The higher LED threshold voltage provides improved immunity to differential noise and the internally shielded detector provides orders of magnitude improvement in common mode rejection with little or no sacrifice in speed.

#### **Selection Guide**

| Minimum CMR     |                        | Input                  |                  | 8-Pin DIP                    | (300 Mil)                  | Small-Outline                | SO-8(400 Mil)              | Widebody<br>Hermetic         | Hermetic                               |

|-----------------|------------------------|------------------------|------------------|------------------------------|----------------------------|------------------------------|----------------------------|------------------------------|----------------------------------------|

| dV∕dt<br>(V∕µs) | V <sub>CM</sub><br>(V) | On-<br>Current<br>(mA) | Output<br>Enable | Single<br>Channel<br>Package | Dual<br>Channel<br>Package | Single<br>Channel<br>Package | Dual<br>Channel<br>Package | Single<br>Channel<br>Package | Single and<br>Dual Channel<br>Packages |

| NA              | NA                     | 5                      | YES              | 6N137                        |                            | HCPL-0600                    |                            | HCNW137                      |                                        |

|                 |                        |                        | NO               |                              | HCPL-2630                  |                              | HCPL-0630                  |                              |                                        |

| 5,000           | 50                     | -                      | YES              | HCPL-2601                    |                            | HCPL-0601                    |                            | HCNW2601                     |                                        |

|                 |                        |                        | NO               |                              | HCPL-2631                  |                              | HCPL-0631                  |                              |                                        |

| 10.000          | 1.000                  |                        | YES              | HCPL-2611                    |                            | HCPL-0611                    |                            | HCNW2611                     |                                        |

|                 |                        |                        | NO               |                              | HCPL-4661                  |                              | HCPL-0661                  |                              |                                        |

| 1,000           | 50                     |                        | YES              | HCPL-2602 <sup>[1]</sup>     |                            |                              |                            |                              |                                        |

| 3,500           | 300                    | -                      | YES              | HCPL-2612 <sup>[1]</sup>     |                            |                              |                            |                              |                                        |

| 1,000           | 50                     | 3                      | YES              | HCPL-261A                    |                            | HCPL-061A                    |                            |                              |                                        |

|                 |                        |                        | NO               |                              | HCPL-263A                  |                              | HCPL-063A                  |                              |                                        |

| 1,000[2]        | 1,000                  |                        | YES              | HCPL-261N                    |                            | HCPL-061N                    |                            |                              |                                        |

|                 |                        |                        | NO               |                              | HCPL-263N                  |                              | HCPL-063N                  |                              |                                        |

| 1,000           | 50                     | 12.5                   | [3]              |                              |                            |                              |                            |                              | HCPL-193X<br>HCPL-56XX<br>HCPL-66XX    |

#### Notes:

1. HCPL-2602/2612 devices include input current regulator.

2. 15 kV/ $\mu$ s with V<sub>CM</sub> = 1 kV can be achieved using Avago application circuit.

3. Enable is available for single channel products only, except for HCPL-193X devices.

## Ordering Information HCPL-2602/HCPL-2612 is UL Recognized with 3750 Vrms for 1 minute per UL1577.

|                | Option            |                       |               |                  |              |                |               |

|----------------|-------------------|-----------------------|---------------|------------------|--------------|----------------|---------------|

| Part<br>Number | RoHS<br>Compliant | non RoHS<br>Compliant | Package       | Surface<br>Mount | Gull<br>Wing | Tape<br>& Reel | Quantity      |

| HCPL-2602      | -000E             | no option             | 300 mil DIP-8 |                  |              |                | 50 per tube   |

| HCPL-2612      | -300E             | #300                  |               | Х                | Х            |                | 50 per tube   |

|                | -500E             | #500                  |               | Х                | Х            | Х              | 1000 per reel |

To order, choose a part number from the part number column and combine with the desired option from the option column to form an order entry.

Example 1:

HCPL-2602-500E to order product of Gull Wing Surface Mount package in Tape and Reel packaging and RoHS compliant.

Example 2:

HCPL-2612 to order product of 300 mil DIP package in Tube packaging and non RoHS compliant.

Option datasheets are available. Contact your Avago sales representative or authorized distributor for information.

Remarks: The notation '#XXX' is used for existing products, while (new) products launched since July 15, 2001 and RoHS compliant will use '-XXXE.'

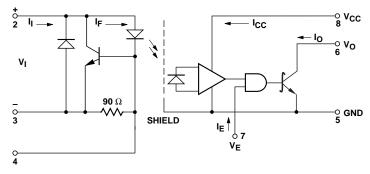

Schematic

USE OF A 0.1  $\mu F$  BYPASS CAPACITOR CONNECTED BETWEEN PINS 5 AND 8 IS REQUIRED (SEE NOTE 1).

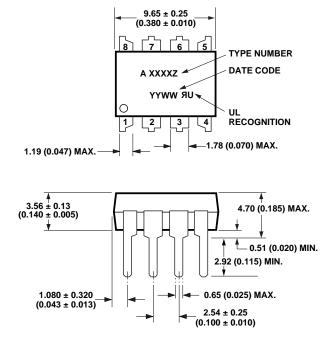

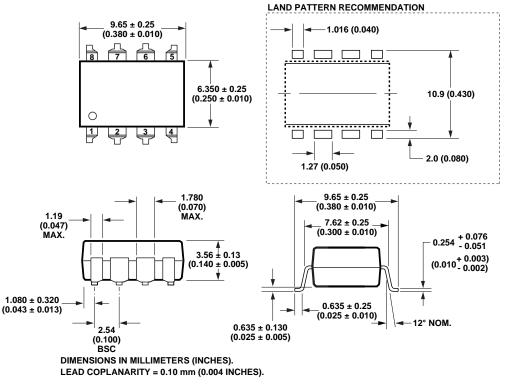

## Package Outline Drawings 8-Pin DIP Package

DIMENSIONS IN MILLIMETERS AND (INCHES). NOTE: FLOATING LEAD PROTRUSION IS 0.25 mm (10 mils) MAX.

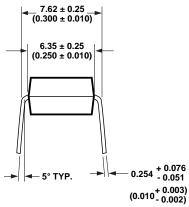

## 8-Pin DIP Package with Gull Wing Surface Mount Option 300

NOTE: FLOATING LEAD PROTRUSION IS 0.25 mm (10 mils) MAX.

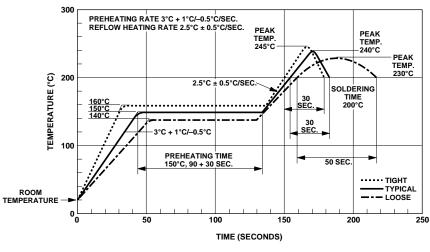

## **Solder Reflow Thermal Profile**

Note: Non-halide flux should be used.

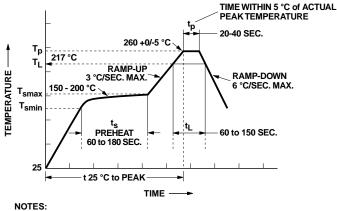

#### **Recommended Pb-Free IR Profile**

THE TIME FROM 25 °C to PEAK TEMPERATURE = 8 MINUTES MAX. T<sub>smax</sub> = 200 °C, T<sub>smin</sub> = 150 °C

Note: Non-halide flux should be used.

Insulation and Safety Related Specifications

| Parameter                                              | Symbol | Value | Units | Conditions                                                                                                                                                       |

|--------------------------------------------------------|--------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Min. External Air Gap<br>(External Clearance)          | L(I01) | 7.1   | mm    | Measured from input terminals to output terminals, shortest distance through air.                                                                                |

| Min. External Tracking<br>Path (External Creepage)     | L(102) | 7.4   | mm    | Measured from input terminals to output terminals, shortest distance path along body.                                                                            |

| Min. Internal Plastic<br>Gap (Internal Clearance)      |        | 0.08  | mm    | Through insulation distance, conductor to conductor,<br>usually the direct distance between the photoemitter<br>and photodetector inside the optocoupler cavity. |

| Tracking Resistance<br>(Comparative Tracking<br>Index) | CTI    | 200   | V     | DIN IEC 112/VDE 0303 Part 1                                                                                                                                      |

| Isolation Group                                        |        | Illa  |       | Material Group (DIN VDE 0110, 1/89, Table 1)                                                                                                                     |

Option 300 - surface mount classification is Class A in accordance with CECC 00802.

## **Regulatory Information**

The HCPL-2602/2612 have been approved by the following organizations:

## UL

Recognized under UL 1577, Component Recognition Program, File E55361.

## CSA

Approved under CSA Component Acceptance Notice #5, File CA 88324.

| Absolute Maximum | Ratings | (No | Derating | Rec | uired u | ip to | 85°C) |

|------------------|---------|-----|----------|-----|---------|-------|-------|

|                  |         |     |          |     |         |       |       |

| Parameter                                                                                   | Symbol          | Min.                                          | Max.                  | Units |  |

|---------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------|-----------------------|-------|--|

| Storage Temperature                                                                         | Ts              | -55                                           | 125                   | °C    |  |

| Operating Temperature                                                                       | TA              | - 40                                          | 85                    | °C    |  |

| Forward Input Current                                                                       | lı              |                                               | 60                    | mA    |  |

| Reverse Input Current                                                                       | I <sub>IR</sub> |                                               | 60                    | mA    |  |

| Input Current, Pin 4                                                                        |                 | -10                                           | 10                    | mA    |  |

| Supply Voltage (1 Minute Maximum)                                                           | V <sub>CC</sub> |                                               | 7                     | V     |  |

| Enable Input Voltage (Not to Exceed V <sub>CC</sub> by more than 500 mV)                    | VE              |                                               | V <sub>CC</sub> + 0.5 | V     |  |

| Output Collector Current                                                                    | I <sub>0</sub>  |                                               | 50                    | mA    |  |

| Output Collector Voltage (Selection for Higher<br>Output Voltages up to 20 V is Available.) | Vo              |                                               | 7                     | V     |  |

| Output Collector Power Dissipation                                                          | Po              |                                               | 40                    | mW    |  |

| Lead Solder Temperature                                                                     | T <sub>LS</sub> | 260°C for 10 sec., 1.6 mm below seating plane |                       |       |  |

| Solder Reflow Temperature Profile                                                           |                 | See Package Outline Drawings sectio           |                       |       |  |

## **Recommended Operating Conditions**

| Parameter                      | Symbol          | Min. | Max.            | Units     |

|--------------------------------|-----------------|------|-----------------|-----------|

| Input Current, Low Level       | IIL             | 0    | 250             | μA        |

| Input Current, High Level      | I <sub>IH</sub> | 5*   | 60              | mA        |

| Supply Voltage, Output         | V <sub>CC</sub> | 4.5  | 5.5             | V         |

| High Level Enable Voltage      | V <sub>EH</sub> | 2.0  | V <sub>CC</sub> | V         |

| Low Level Enable Voltage       | V <sub>EL</sub> | 0    | 0.8             | V         |

| Fan Out (@ $R_L = 1 k\Omega$ ) | N               |      | 5               | TTL Loads |

| Output Pull-up Resistor        | R <sub>L</sub>  | 330  | 4 K             | Ω         |

| Operating Temperature          | T <sub>A</sub>  | 0    | 70              | °C        |

\*The initial switching threshold is 5 mA or less. It is recommended that an input current between 6.3 mA and 10 mA be used to obtain best performance and to provide at least 20% LED degradation guardband.

## Electrical Characteristics Over recommended temperature ( $T_A = 0^{\circ}C$ to +70°C) unless otherwise specified. See note 1.

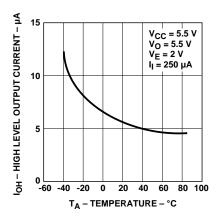

| Parameter                    | Sym.             | Min. | Тур.* | Max. | Units | Test Conditions                                                                                                                                               | Fig.           | Note |

|------------------------------|------------------|------|-------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|

| High Level Output<br>Current | I <sub>OH</sub>  |      | 5.5   | 100  | μΑ    | $\label{eq:V_CC} \begin{split} V_{CC} &= 5.5 \ V, \ V_0 = 5.5 \ V, \\ I_1 &= 250 \ \mu A, \ V_E = 2.0 \ V \end{split}$                                        | 1              |      |

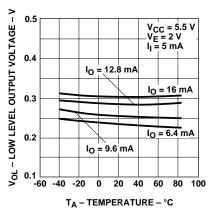

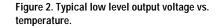

| Low Level Output<br>Voltage  | V <sub>OL</sub>  |      | 0.35  | 0.6  | V     | $V_{CC} = 5.5 \text{ V}, \text{ I}_{\text{I}} = 5 \text{ mA},$<br>$V_{\text{E}} = 2.0 \text{ V},$<br>$\text{I}_{\text{OL}} \text{ (Sinking)} = 13 \text{ mA}$ | 2, 4,<br>5, 14 |      |

| High Level Supply<br>Current | I <sub>ССН</sub> |      | 7.5   | 10   | mA    | $V_{CC} = 5.5 \text{ V}, \text{ I}_{\text{I}} = 0 \text{ mA},$<br>$V_{\text{E}} = 0.5 \text{ V}$                                                              |                |      |

| Low Level Supply<br>Current  | I <sub>CCL</sub> |      | 10    | 13   | mA    | $\label{eq:V_CC} \begin{split} V_{CC} &= 5.5 \text{ V}, \text{ I}_{\text{I}} = 60 \text{ mA}, \\ V_{\text{E}} &= 0.5 \text{ V} \end{split}$                   |                |      |

| High Level Enable<br>Current | I <sub>EH</sub>  |      | -0.7  | -1.6 | mA    | $V_{CC} = 5.5 \text{ V}, \text{ V}_{E} = 2.0 \text{ V}$                                                                                                       |                |      |

| Low Level Enable<br>Current  | I <sub>EL</sub>  |      | -0.9  | -1.6 | mA    | $V_{CC} = 5.5 \text{ V}, \text{ V}_{E} = 0.5 \text{ V}$                                                                                                       |                |      |

| High Level Enable<br>Voltage | V <sub>EH</sub>  | 2.0  |       |      | V     |                                                                                                                                                               |                | 10   |

| Low Level Enable<br>Voltage  | V <sub>EL</sub>  |      |       | 0.8  | V     |                                                                                                                                                               |                |      |

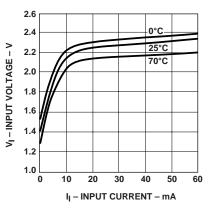

| Innut Voltago                | VI               |      | 2.0   | 2.4  | V     | I <sub>I</sub> = 5 mA                                                                                                                                         | 3              |      |

| Input Voltage                | V                |      | 2.3   | 2.7  | v     | I <sub>I</sub> = 60 mA                                                                                                                                        |                |      |

| Input Reverse<br>Voltage     | V <sub>R</sub>   |      | 0.75  | 0.95 | V     | I <sub>R</sub> = 5 mA                                                                                                                                         |                |      |

| Input Capacitance            | C <sub>IN</sub>  |      | 90    |      | pF    | V <sub>I</sub> = 0 V, f = 1 MHz                                                                                                                               |                |      |

\*All typicals at V\_{CC} = 5 V, T\_A = 25 ^{\circ}C.

## **Switching Specifications**

Over recommended temperature (T<sub>A</sub> = 0°C to +70°C), V<sub>CC</sub> = 5 V, I<sub>I</sub> = 7.5 mA, unless otherwise specified.

|                                                                                                       |                                    |           | 1    |        |           |          |                                                                                                                                                                               |                                                                                                                  | 1      |             |

|-------------------------------------------------------------------------------------------------------|------------------------------------|-----------|------|--------|-----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------|-------------|

| Parameter                                                                                             | Symbol                             | Device    | Min. | Тур.*  | Max.      | Units    | Test                                                                                                                                                                          | Conditions                                                                                                       | Fig.   | Note        |

| Propagation Delay<br>Time to High Output<br>Level                                                     | t <sub>PLH</sub>                   |           | 20   | 48     | 75<br>100 | ns<br>ns | $T_A = 25^{\circ}C$                                                                                                                                                           |                                                                                                                  | 6,7,8  | 3           |

| Propagation Delay                                                                                     |                                    |           |      |        | 75        | -        | T <sub>A</sub> = 25°C                                                                                                                                                         |                                                                                                                  |        |             |

| Time to Low Output                                                                                    | t <sub>PHL</sub>                   |           | 25   | 50     | 75        | ns       | 1 <sub>A</sub> = 25°C                                                                                                                                                         |                                                                                                                  | 6,7,8  | 4           |

| Level                                                                                                 | -FIL                               |           |      |        | 100       | ns       |                                                                                                                                                                               | P = 250 O                                                                                                        | -,.,-  |             |

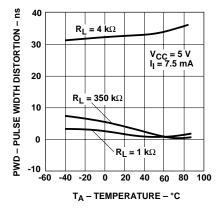

| Pulse Width<br>Distortion                                                                             | t <sub>PHL</sub> -t <sub>PLH</sub> |           |      | 3.5    | 35        | ns       |                                                                                                                                                                               | $\begin{array}{l} R_{L} = 350 \ \Omega \\ C_{L} = 15 \ pF \end{array}$                                           | 9      | 13          |

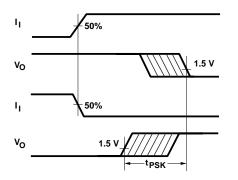

| Propagation Delay<br>Skew                                                                             | t <sub>PSK</sub>                   |           |      |        | 40        | ns       |                                                                                                                                                                               |                                                                                                                  |        | 12,<br>13   |

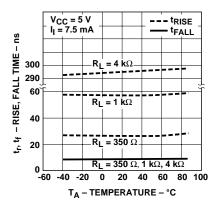

| Output Rise Time<br>(10-90%)                                                                          | tr                                 |           |      | 24     |           | ns       |                                                                                                                                                                               |                                                                                                                  | 12     |             |

| Output Fall Time<br>(90-10%)                                                                          | t <sub>f</sub>                     |           |      | 10     |           | ns       |                                                                                                                                                                               |                                                                                                                  | 12     |             |

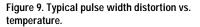

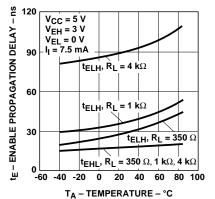

| $\begin{array}{c} Propagation \ Delay\\ Time \ of \ Enable \ from\\ V_{EH} \ to \ V_{EL} \end{array}$ | t <sub>ELH</sub>                   |           |      | 30     |           | ns       | $ \begin{array}{l} {\sf R}_{\sf L} = 350 \; \Omega, \; {\sf C}_{\sf L} = 15 \; p{\sf F}, \\ {\sf V}_{\sf EL} = 0 \; {\sf V}, \; {\sf V}_{\sf EH} = 3 \; {\sf V} \end{array} $ |                                                                                                                  | 10, 11 | 5           |

| Propagation Delay Time of Enable from $V_{EL}$ to $V_{EH}$                                            | t <sub>EHL</sub>                   |           |      | 20     |           | ns       | $ \begin{array}{l} {\sf R}_{\sf L} = 350 \; \Omega, \; {\sf C}_{\sf L} = 15 \; p{\sf F}, \\ {\sf V}_{\sf EL} = 0 \; {\sf V}, \; {\sf V}_{\sf EH} = 3 \; {\sf V} \end{array} $ |                                                                                                                  | 10, 11 | 6           |

| Common Mode                                                                                           |                                    | HCPL-2602 | 1000 | 10,000 |           |          | V <sub>CM</sub> = 50 V                                                                                                                                                        | $V_{O(MIN)} = 2 V_{,}$                                                                                           | 10     |             |

| Transient<br>Immunity at High<br>Output Level                                                         | CM <sub>H</sub>                    | HCPL-2612 | 3500 | 15,000 |           | V/µs     | V <sub>CM</sub> = 300 V                                                                                                                                                       | $ \begin{array}{l} & - & R_L = 350 \ \Omega, \\ & I_I = 0 \ mA, \\ & T_A = 25^{\circ}C \end{array} \end{array} $ | 13     | 7, 9,<br>10 |

| Common Mode                                                                                           |                                    | HCPL-2602 | 1000 | 10,000 |           |          | V <sub>CM</sub> = 50 V                                                                                                                                                        | $V_{O(MAX)} = 0.8 V_{,}$                                                                                         |        |             |

| Transient<br>Immunity at Low<br>Output Level                                                          | CM <sub>L</sub>                    | HCPL-2612 | 3500 | 15,000 |           | V/µs     | V <sub>CM</sub> = 300 V                                                                                                                                                       | $R_L = 350 \Omega,$<br>$I_I = 7.5 mA,$<br>$T_A = 25°C$                                                           | 13     | 8, 9<br>10  |

\*All typicals at V  $_{_{CC}}$  = 5 V, T  $_{_{A}}$  = 25°C.

## **Package Characteristics**

All Typicals at  $T_A = 25^{\circ}C$

| Parameter                                    | Sym.             | Min. | Тур.             | Max. | Units | Test Conditions                                                                   | Fig. | Note  |

|----------------------------------------------|------------------|------|------------------|------|-------|-----------------------------------------------------------------------------------|------|-------|

| Input-Output Momentary<br>Withstand Voltage* | V <sub>ISO</sub> | 3750 |                  |      | V rms | $\begin{array}{l} RH \leq 50\%,  t=1 \; min., \\ T_{A} = 25^{\circ}C \end{array}$ |      | 2, 11 |

| Input-Output Resistance                      | R <sub>I-O</sub> |      | 10 <sup>12</sup> |      | Ω     | V <sub>I-0</sub> = 500 Vdc                                                        |      | 2     |

| Input-Output Capacitance                     | C <sub>I-O</sub> |      | 0.6              |      | pF    | f = 1 MHz                                                                         |      | 2     |

\*The Input-Output Momentary Withstand Voltage is a dielectric voltage rating that should not be interpreted as an input-output continuous voltage rating. For the continuous voltage rating refer to the IEC/EN/DIN EN 60747-5-2 Insulation Characteristics Table (if applicable), your equipment level safety specification or Avago Application Note 1074 entitled "Optocoupler Input-Output Endurance Voltage."

#### Notes:

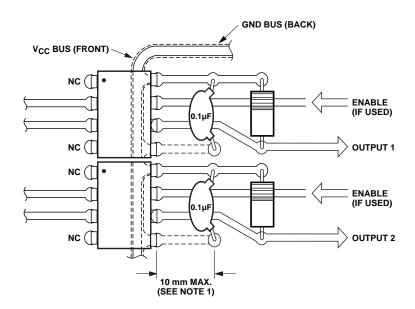

- 1. Bypassing of the power supply line is required, with a 0.1 μF ceramic disc capacitor adjacent to each optocoupler as illustrated in Figure 15. Total lead length between both ends of the capacitor and the isolator pins should not exceed 20 mm.

- 2. Device considered a two terminal device: pins 1, 2, 3, and 4 shorted together, and pins 5, 6, 7, and 8 shorted together.

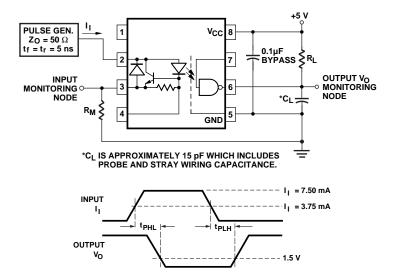

- 3. The t<sub>PLH</sub> propagation delay is measured from the 3.75 mA point on the falling edge of the input pulse to the 1.5 V point on the rising edge of the output pulse.

- The t<sub>PHL</sub> propagation delay is measured from the 3.75 mA point on the rising edge of the input pulse to the 1.5 V point on the falling edge of the output pulse.

- 5. The t<sub>ELH</sub> enable propagation delay is measured from the 1.5 V point on the falling edge of the enable input pulse to the 1.5 V point on the rising edge of the output pulse.

- 6. The t<sub>EHL</sub> enable propagation delay is measured from the 1.5 V point on the rising edge of the enable input pulse to the 1.5 V point on the falling edge of the output pulse.

- 7. CM<sub>H</sub> is the maximum tolerable rate of rise of the common mode voltage to assure that the output will remain in a high logic state (i.e., V<sub>OUT</sub> > 2.0 V).

- 8. CM<sub>L</sub> is the maximum tolerable rate of fall of the common mode voltage to assure that the output will remain in a low logic state (i.e., V<sub>OUT</sub> < 0.8 V).

9. For sinusoidal voltages,

$$\begin{array}{rcl} | \alpha v_{CM} | \\ ----- &= \pi f_{CM} V_{CM} (p-p) \\ dt & max \end{array}$$

- 10. No external pull up is required for a high logic state on the enable input. If the V<sub>E</sub> pin is not used, tying V<sub>E</sub> to V<sub>CC</sub> will result in improved CMR performance.

- 11. In accordance with UL 1577, each optocoupler is proof tested by applying an insulation test voltage of  $\geq$  4500 for one second (leakage detection current limit,  $I_{i-0} \leq 5 \mu A$ ).

- 12. t<sub>PSK</sub> is equal to the worst case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that will be seen between units at any given temperature within the operating condition range.

- 13. See application section titled "Propagation Delay, Pulse-Width Distortion and Propagation Delay Skew" for more information.

Figure 1. Typical high level output current vs. temperature.

Figure 3. Typical input characteristics.

Figure 4. Typical output voltage vs. forward input current.

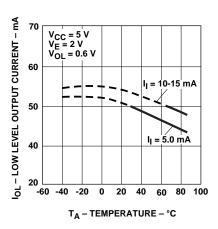

Figure 5. Typical low level output current vs. temperature.

Figure 6. Test circuit for  $t_{_{PHL}}$  and  $t_{_{PLH}}.$

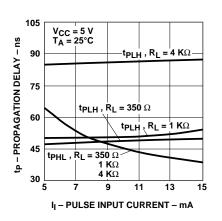

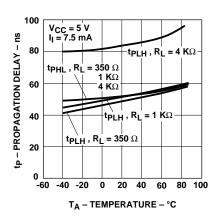

Figure 7. Typical propagation delay vs. temperature.

Figure 10. Test circuit for  $t_{\mbox{\tiny EHL}}$  and  $t_{\mbox{\tiny ELH}}$

Figure 11. Typical enable propagation delay vs. temperature.

0.1 μF BYPASS **ξ 350** Ω 7 ΑÇ OUTPUT V<sub>O</sub> MONITORING NODE 3 4 5 GND ÷ Vсм -, I) -PULSE GENERATOR  $Z_0 = 50 \Omega$ -- VCM (PEAK) Vсм 0 V SWITCH AT A:  $I_1 = 0 \text{ mA}$ СМн 5 \ Vo V<sub>O</sub> (MIN.) SWITCH AT B: II = 7.5 mA –– V<sub>O</sub> (MAX.) V<sub>O</sub> 0.5 V CML

1

в

Vcc 8

Figure 12. Typical rise and fall time vs. temperature.

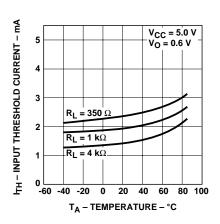

Figure 14. Typical input threshold current vs. temperature.

Figure 15. Recommended printed circuit board layout.

# Using the HCPL-2602/12 Line Receiver Optocouplers

The primary objectives to fulfill when connecting an optocoupler to a transmission line are to provide a minimum, but not excessive, LED current and to properly terminate the line. The internal regulator in the HCPL-2602/12 simplifies this task. Excess current from variable drive conditions such as line length variations, line driver differences, and power supply fluctuations are shunted by the regulator. In fact, with the LED current regulated, the line current can be increased to improve the immunity of the system to differential-mode-noise and to enhance the data rate capability. The designer must keep in mind the 60 mA input current maximum rating of the HCPL-2602/12 in such cases, and may need to use series limiting or shunting to prevent overstress.

Design of the termination circuit is also simplified; in most cases the transmission line can simply be connected directly to the input terminals of the HCPL-2602/12 without the need for additional series or shunt resistors. If reversing line drive is used it may be desirable to use two HCPL-2602/12 or an external Schottky diode to optimize data rate.

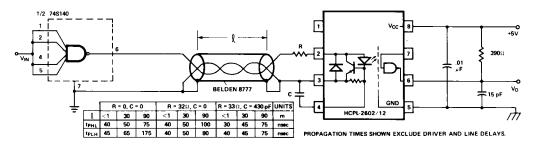

#### **Polarity Non-Reversing Drive**

High data rates can be obtained with the HCPL-2602/12 with polarity non-reversing drive. Figure (a) illustrates how a 74S140 line driver can be used with the HCPL-2602/12 and shielded, twisted pair or coax cable without any additional components. There are some reflections due to the "active termination," but they do not

interfere with circuit performance because the regulator clamps the line voltage. At longer line lengths,  $t_{_{\rm PLH}}$  increases faster than  $t_{_{\rm PHL}}$  since the switching threshold is not exactly halfway between asymptotic line conditions. If optimum data rate is desired, a series resistor and peaking capacitor can be used to equalize  $t_{PLH}$  and  $t_{PHL}$ . In general, the peaking capacitance should be as large as possible; however, if it is too large it may keep the regulator from achieving turn-off during the negative (or zero) excursions of the input signal. A safe rule:

make  $C \leq 16t$

where:

C = peaking capacitance in picofarads t = data bit interval in nanoseconds

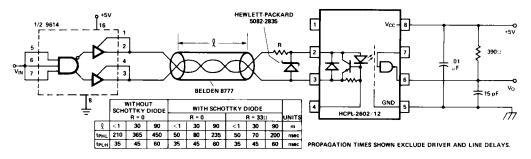

### **Polarity Reversing Drive**

A single HCPL-2602/12 can also be used with polarity reversing drive (Figure b). Current reversal is obtained by way of the substrate isolation diode (substrate to collector). Some reduction of data rate occurs, however, because the substrate diode stores charge, which must be removed when the current changes to the forward direction. The effect of this is a longer  $t_{PHL}$ . This effect can be eliminated and data rate improved considerably by use of a Schottky diode on the input of the HCPL-2602/12.

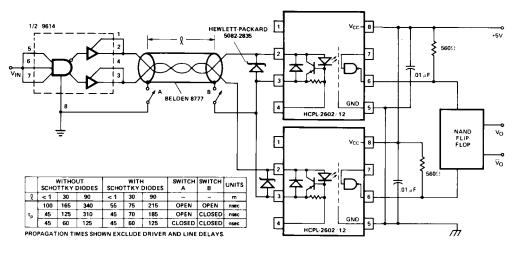

For optimum noise rejection as well as balanced delays, a splitphase termination should be used along with a flip-flop at the output (Figure c). The result of current reversal in split-phase operation is seen in Figure (c) with switches A and B both OPEN. The coupler inputs are then connected in ANTI-SERIES; however, because of the higher steady-state termination voltage, in comparison to the single HCPL-2602/12 termination, the forward current in the substrate diode is lower and consequently there is less junction charge to deal with when switching.

Closing switch B with A open is done mainly to enhance common mode rejection, but also reduces propagation delay slightly because line-to-line capacitance offers a slight peaking effect. With switches A and B both CLOSED, the shield acts as a current return path which prevents either input substrate diode from becoming reversed biased. Thus the data rate is optimized as shown in Figure (c).

## **Improved Noise Rejection**

Use of additional logic at the output of two HCPL-2602/12s, operated in the split phase termination, will greatly improve system noise rejection in addition to balancing propagation delays as discussed earlier.

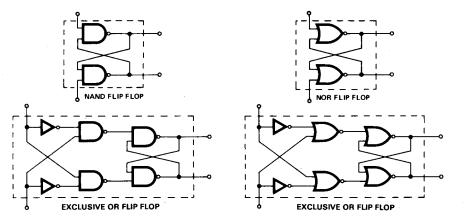

A NAND flip-flop offers infinite common mode rejection (CMR) for NEGATIVELY sloped common mode transients but requires  $t_{PHL}$ >  $t_{PLH}$  for proper operation. A NOR flip-flop has infinite CMR for POSITIVELY sloped transients but requires  $t_{PHL} < t_{PLH}$  for proper operation. An exclusive-OR flipflop has infinite CMR for common mode transients of EITHER polarity and operates with either  $t_{PHL} > t_{PLH}$  or  $t_{PHL} < t_{PLH}$ .

With the line driver and transmission line shown in Figure (c),  $t_{PHL} > t_{PLH}$ , so NAND gates are preferred in the R-S flip-flop. A higher drive amplitude or

Figure a. Polarity non-reversing.

Figure b. Polarity reversing, single ended.

Figure c. Polarity reversing, split phase.

Figure d. Flip-flop configurations.

NAND flip flop tolerates simultaneously HIGH inputs; NOR flip flop tolerates simultaneously LOW inputs; EXCLUSIVE-OR flip flop tolerates simultaneously HIGH OR LOW inputs without causing either of the outputs to change. different circuit configuration could make  $t_{PHL} < t_{PLH}$ , in which case NOR gates would be preferred. If it is not known whether  $t_{PHL} > t_{PLH}$  or  $t_{PHL} < t_{PLH}$ , or if the drive conditions may vary over the boundary for these conditions, the exclusive-OR flip-flop of Figure (d) should be used.

### RS-422 and RS-423

Line drivers designed for RS-422 and RS-423 generally provide adequate voltage and current for operating the HCPL-2602/12. Most drivers also have characteristics allowing the HCPL-2602/12 to be connected directly to the driver terminals. Worst case drive conditions, however, would require current shunting to prevent overstress of the HCPL-2602/12.

#### Propagation Delay, Pulse-Width Distortion and Propagation Delay Skew

Propagation delay is a figure of merit which describes how quickly a logic signal propagates through a system. The propagation delay from low to high  $(t_{PLH})$  is the amount of time required for an input signal to propagate to the output, causing the output to change from low to high. Similarly, the propagation delay from high to low  $(t_{PHL})$  is the amount of time required for the input signal to propagate to the output, causing the output to change from high to low (see Figure 6).

Pulse-width distortion (PWD) results when  $t_{PLH}$  and  $t_{PHL}$  differ in value. PWD is defined as the difference between  $t_{PLH}$  and  $t_{PHL}$ and often determines the maximum data rate capability of a transmission system. PWD can be expressed in percent by dividing the PWD (in ns) by the minimum pulse width (in ns) being transmitted. Typically, PWD on the order of 20-30% of the minimum pulse width is tolerable; the exact figure depends on the particular application (RS232, RS422, T-1, etc.).

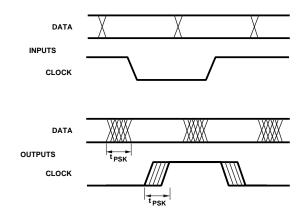

Propagation delay skew,  $t_{PSK}$ , is an important parameter to consider in parallel data applications where synchronization of signals on parallel data lines is a concern. If the parallel data is being sent through a group of optocouplers, differences in propagation delays will cause the data to arrive at the outputs of the optocouplers at different times. If this difference in propagation delays is large enough, it will determine the maximum rate at which parallel data can be sent through the optocouplers.

Propagation delay skew is defined as the difference between the minimum and maximum propagation delays, either  $t_{_{\rm PLH}}$  or  $t_{PHI}$ , for any given group of optocouplers which are operating under the same conditions (i.e., the same drive current, supply voltage, output load, and operating temperature). As illustrated in Figure 16, if the inputs of a group of optocouplers are switched either ON or OFF at the same time,  $t_{PSK}$  is the difference between the shortest propagation delay, either  $t_{PHL}$  or  $t_{_{PHI}}$ , and the longest propagation delay, either  $t_{PLH}$  or  $t_{PHL}$ .

As mentioned earlier,  $t_{PSK}$  can determine the maximum parallel data transmission rate. Figure 17 is the timing diagram of a typical parallel data application with

both the clock and the data lines being sent through optocouplers. The figure shows data and clock signals at the inputs and outputs of the optocouplers. To obtain the maximum data transmission rate, both edges of the clock signal are being used to clock the data; if only one edge were used, the clock signal would need to be twice as fast.

Propagation delay skew represents the uncertainty of where an edge might be after being sent through an optocoupler. Figure 17 shows that there will be uncertainty in both the data and the clock lines. It is important that these two areas of uncertainty not overlap, otherwise the clock signal might arrive before all of the data outputs have settled, or some of the data outputs may start to change before the clock signal has arrived. From these considerations, the absolute minimum pulse width that can be sent through optocouplers in a parallel application is twice  $t_{PSK}$ . A cautious design should use a slightly longer pulse width to ensure that any additional uncertainty in the rest of the circuit does not cause a problem.

The  $t_{PSK}$  specified optocouplers offer the advantages of guaranteed specifications for propagation delays, pulse-width distortion and propagation delay skew over the recommended temperature, input current, and power supply ranges.

Figure 17. Parallel data transmission example.

Figure 16. Illustration of propagation delay skew -  $t_{_{PSK}}$ .

For product information and a complete list of distributors, please go to our website: www.avagotech.com

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies Limited in the United States and other countries. Data subject to change. Copyright © 2007 Avago Technologies Limited. All rights reserved. Obsoletes 5989-2154EN AV01-0568EN July 18, 2007

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Broadcom manufacturer:

Other Similar products are found below :

MGA-634P8-TR1G

PEX9749-AARDK

BCM54618SEA2IFBG

ASMT-JR10-ARS01

BCM5720A0KFBG

ACPL-K75T-000E

ACPL-247

560E

HCPL-6750

HFBR-2406Z

HCMS-3903

HCPL-5430

HCPL-0720

BCM5389IFBG

PEX8750-AB RDK

BCM53405A0KFSBG

HSMZ

C110

05-50062-00

LP16-LW-OPT-2

ACPL-054L-500E

AFBR-S20W2UV

AFBR-S20W2VI

AFBR-S20W2NI

HCPL-7800A-300E

HDSP

2113

BCM54285C1KFBG

HDSP-815E

HSMS-8209-BLKG

5962-8876903FC

HCNW4506-000E

HEDS-8949

AFBR-S4N44P163

ASSR

601JV-500E

AFBR-S20M2UV

AFBR-S20M2UV