CAT28LV64 64K-Bit CMOS PARALLEL EEPROM

NOUCTOR.

## **FEATURES**

- 3.0V to 3.6 V Supply

- Read access times: – 150/200/250ns

- Low power CMOS dissipation:

- Active: 8 mA max.

- Standby: 100  $\mu$ A max.

- Simple write operation:

- On-chip address and data latches

- Self-timed write cycle with auto-clear

- Fast write cycle time: - 5ms max.

- Commercial, industrial and automotive temperature ranges

- CMOS and TTL compatible I/O

- Automatic page write operation:

- 1 to 32 bytes in 5ms

- Page load timer

- End of write detection: – Toggle bit

- DATA polling

- Hardware and software write protection

- 100,000 program/erase cycles

- 100 year data retention

## DESCRIPTION

The CAT28LV64 is a low voltage, low power, CMOS parallel EEPROM organized as 8K x 8-bits. It requires a simple interface for in-system programming. On-chip address and data latches, self-timed write cycle with autoclear and  $V_{CC}$  power up/down write protection eliminate additional timing and protection hardware. DATA Polling and Toggle status bit signal the start and end of the self-timed write cycle. Additionally, the CAT28LV64 features hardware and software write protection.

The CAT28LV64 is manufactured using Catalyst's advanced CMOS floating gate technology. It is designed to endure 100,000 program/erase cycles and has a data retention of 100 years. The device is available in JEDEC approved 28-pin DIP, 28-pin TSOP, 28-pin SOIC or 32-pin PLCC packages.

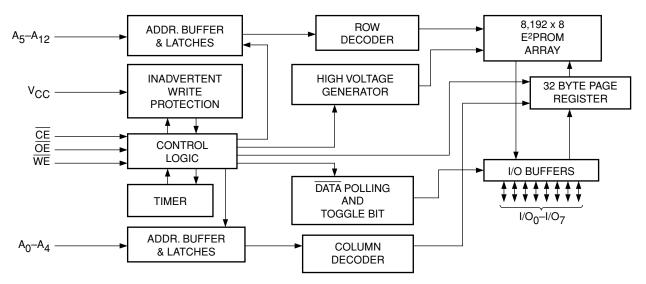

## **BLOCK DIAGRAM**

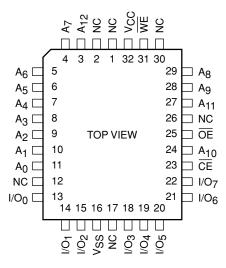

## **PIN CONFIGURATION**

#### DIP Package (P, L)

|                    |    |    | 1                  |

|--------------------|----|----|--------------------|

| NC 🗆               | •1 | 28 |                    |

| A <sub>12</sub> □  | 2  | 27 |                    |

| A <sub>7</sub> □   | 3  | 26 | D NC               |

| A <sub>6</sub> □   | 4  | 25 | □ A <sub>8</sub>   |

| A5 □               | 5  | 24 | 🗆 A9               |

| A4 □               | 6  | 23 | □ A <sub>11</sub>  |

| A3 □               | 7  | 22 |                    |

| A2 □               | 8  | 21 | □ A <sub>10</sub>  |

| A₁                 | 9  | 20 |                    |

| A <sub>0</sub> □   | 10 | 19 |                    |

| I/O <sub>0</sub>   | 11 | 18 | □ I/O <sub>6</sub> |

| I/O <sub>1</sub> □ | 12 | 17 | □ I/O <sub>5</sub> |

| I/O <sub>2</sub> □ | 13 | 16 | □ I/O <sub>4</sub> |

| $V_{SS}$           | 14 | 15 | □ I/O <sub>3</sub> |

#### PLCC Package (N, G)

# ō А Ν V ٧c Ν A

### SOIC Package (J, W) (K, X)

| NC 🗂              | •1 | 28 |                    |

|-------------------|----|----|--------------------|

| A <sub>12</sub>   | 2  | 27 | <u> </u>           |

| A <sub>7</sub>    | 3  | 26 | DN E               |

| A <sub>6</sub>    | 4  | 25 | <u> </u>           |

| A <sub>5</sub>    | 5  | 24 | <u> </u>           |

| A4 [_             | 6  | 23 | 🗅 A <sub>11</sub>  |

| A3 ⊑              | 7  | 22 | <u> </u>           |

| A <sub>2</sub>    | 8  | 21 | □ A <sub>10</sub>  |

| A <sub>1</sub>    | 9  | 20 |                    |

| A <sub>0</sub>    | 10 | 19 | L] I/O7            |

| I/O <sub>0</sub>  | 11 | 18 | □ I/O <sub>6</sub> |

| I/O <sub>1</sub>  | 12 | 17 | ] I/O5             |

| I/O <sub>2</sub>  | 13 | 16 | ☐ I/O <sub>4</sub> |

| V <sub>SS</sub> ⊑ | 14 | 15 | □ I/O3             |

#### TSOP Top View (8mm x 13.4mm) (T13, H13)

|                   | 1 ° 28 | → A <sub>10</sub>    |

|-------------------|--------|----------------------|

| A <sub>11</sub> 📼 | 2 27   |                      |

| A9 🗔              | 3 26   | └── I/O <sub>7</sub> |

| A <sub>8</sub> 🗔  | 4 25   | 1/0 <sub>6</sub>     |

|                   | 5 24   | 1/O5                 |

| WE 🗖              | 6 23   | □□ I/O <sub>4</sub>  |

| ′cc 🞞             | 7 22   | □□ I/O <sub>3</sub>  |

|                   | 8 21   |                      |

| A12 🗖             | 9 20   | 1/O <sub>2</sub>     |

| A7 🗔              | 10 19  | └── I/O1             |

| A <sub>6</sub> 🗔  | 11 18  | □ I/O <sub>0</sub>   |

| A5 🗔              | 12 17  | A0                   |

| A4 📖              | 13 16  | 🖵 A1                 |

| A3 🗔              | 14 15  | $\square A_2$        |

|                   |        | ,                    |

## **PIN FUNCTIONS**

| Pin Name                           | Function            | Pin Name        | Function            |

|------------------------------------|---------------------|-----------------|---------------------|

| A0-A12                             | Address Inputs      | WE              | Write Enable        |

| I/O <sub>0</sub> -I/O <sub>7</sub> | Data Inputs/Outputs | Vcc             | 3.0 to 3.6 V Supply |

| CE                                 | Chip Enable         | V <sub>SS</sub> | Ground              |

| ŌĒ                                 | Output Enable       | NC              | No Connect          |

## **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias–55°C to +125°C                                                     |

|-------------------------------------------------------------------------------------------|

| Storage Temperature –65°C to +150°C                                                       |

| Voltage on Any Pin with Respect to Ground <sup>(2)</sup> –2.0V to +V <sub>CC</sub> + 2.0V |

| $V_{CC}$ with Respect to Ground –2.0V to +7.0V Package Power Dissipation                  |

| Capability (Ta = 25°C) 1.0W                                                               |

| Lead Soldering Temperature (10 secs) 300°C                                                |

| Output Short Circuit Current <sup>(3)</sup> 100 mA                                        |

#### **RELIABILITY CHARACTERISTICS**

## **\*COMMENT**

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

| Symbol                             | Parameter          | Min.            | Max. | Units       | Test Method                   |

|------------------------------------|--------------------|-----------------|------|-------------|-------------------------------|

| N <sub>END</sub> <sup>(1)</sup>    | Endurance          | 10 <sup>5</sup> |      | Cycles/Byte | MIL-STD-883, Test Method 1033 |

| T <sub>DR</sub> <sup>(1)</sup>     | Data Retention     | 100             |      | Years       | MIL-STD-883, Test Method 1008 |

| VZAP <sup>(1)</sup>                | ESD Susceptibility | 2000            |      | Volts       | MIL-STD-883, Test Method 3015 |

| I <sub>LTH</sub> <sup>(1)(4)</sup> | Latch-Up           | 100             |      | mA          | JEDEC Standard 17             |

#### MODE SELECTION

| Mode                       | CE     | WE | ŌĒ | I/O              | Power   |

|----------------------------|--------|----|----|------------------|---------|

| Read                       | L      | Н  | L  | D <sub>OUT</sub> | ACTIVE  |

| Byte Write (WE Controlled) | L      |    | Н  | D <sub>IN</sub>  | ACTIVE  |

| Byte Write (CE Controlled) | $\sim$ | L  | Н  | D <sub>IN</sub>  | ACTIVE  |

| Standby, and Write Inhibit | Н      | Х  | Х  | High-Z           | STANDBY |

| Read and Write Inhibit     | Х      | Н  | Н  | High-Z           | ACTIVE  |

#### **CAPACITANCE** $T_A = 25^{\circ}C$ , f = 1.0 MHz

| Symbol                          | Test                     | Max. | Units | Conditions     |  |

|---------------------------------|--------------------------|------|-------|----------------|--|

| C <sub>I/O</sub> <sup>(1)</sup> | Input/Output Capacitance | 10   | pF    | $V_{I/O} = 0V$ |  |

| C <sub>IN</sub> <sup>(1)</sup>  | Input Capacitance        | 6    | pF    | $V_{IN} = 0V$  |  |

Note:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

(2) The minimum DC input voltage is -0.5V. During transitions, inputs may undershoot to -2.0V for periods of less than 20 ns. Maximum DC voltage on output pins is V<sub>CC</sub> +0.5V, which may overshoot to V<sub>CC</sub> +2.0V for periods of less than 20 ns.

(3) Output shorted for no more than one second. No more than one output shorted at a time.

(4) Latch-up protection is provided for stresses up to 100mA on address and data pins from -1V to V<sub>CC</sub> +1V.

### **D.C. OPERATING CHARACTERISTICS**

$V_{CC}$  = 3.0V to 3.6V, unless otherwise specified.

|                                 |                                         |      | Limits |                      |       |                                                                                        |

|---------------------------------|-----------------------------------------|------|--------|----------------------|-------|----------------------------------------------------------------------------------------|

| Symbol                          | Parameter                               | Min. | Тур.   | Max.                 | Units | Test Conditions                                                                        |

| Icc                             | $V_{CC}$ Current (Operating, TTL)       |      |        | 8                    | mA    | $\overline{CE} = \overline{OE} = V_{IL},$<br>f = 1/t <sub>RC</sub> min, All I/O's Open |

| I <sub>SBC</sub> <sup>(3)</sup> | V <sub>CC</sub> Current (Standby, CMOS) |      |        | 100                  | μA    | <mark>CE</mark> = V <sub>IHC</sub> ,<br>All I/O's Open                                 |

| ILI                             | Input Leakage Current                   | -1   |        | 1                    | μA    | $V_{IN} = GND$ to $V_{CC}$                                                             |

| ILO                             | Output Leakage Current                  | -5   |        | 5                    | μA    | $\frac{V_{OUT} = GND \text{ to } V_{CC},}{\overline{CE} = V_{IH}}$                     |

| V <sub>IH</sub> <sup>(3)</sup>  | High Level Input Voltage                | 2    |        | V <sub>CC</sub> +0.3 | V     |                                                                                        |

| VIL                             | Low Level Input Voltage                 | -0.3 |        | 0.6                  | V     |                                                                                        |

| V <sub>OH</sub>                 | High Level Output Voltage               | 2    |        |                      | V     | I <sub>OH</sub> = −100μA                                                               |

| V <sub>OL</sub>                 | Low Level Output Voltage                |      |        | 0.3                  | V     | I <sub>OL</sub> = 1.0mA                                                                |

| Vwi                             | Write Inhibit Voltage                   | 2    |        |                      | V     |                                                                                        |

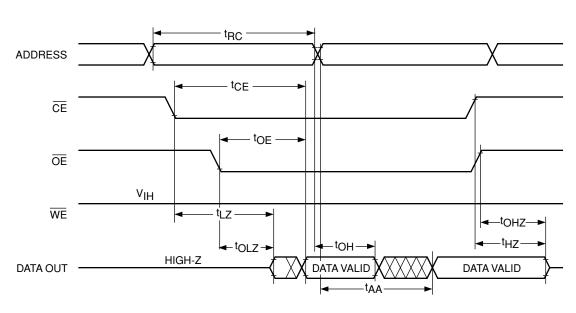

#### A.C. CHARACTERISTICS, Read Cycle

$V_{\text{CC}}$  = 3.0V to 3.6V, unless otherwise specified.

|                                    |                                    | 28LV64-15 |      | 28LV | 64-20 | 28LV64-25 |      |       |

|------------------------------------|------------------------------------|-----------|------|------|-------|-----------|------|-------|

| Symbol                             | Parameter                          | Min.      | Max. | Min. | Max.  | Min.      | Max. | Units |

| t <sub>RC</sub>                    | Read Cycle Time                    | 150       |      | 200  |       | 250       |      | ns    |

| tce                                | CE Access Time                     |           | 150  |      | 200   |           | 250  | ns    |

| taa                                | Address Access Time                |           | 150  |      | 200   |           | 250  | ns    |

| toe                                | OEAccess Time                      |           | 70   |      | 80    |           | 100  | ns    |

| t <sub>LZ</sub> <sup>(1)</sup>     | CE Low to Active Output            | 0         |      | 0    |       | 0         |      | ns    |

| toLZ <sup>(1)</sup>                | OE Low to Active Output            | 0         |      | 0    |       | 0         |      | ns    |

| t <sub>HZ</sub> <sup>(1)(2)</sup>  | CE High to High-Z Output           |           | 50   |      | 50    |           | 55   | ns    |

| t <sub>OHZ</sub> <sup>(1)(2)</sup> | OE High to High-Z Output           |           | 50   |      | 50    |           | 55   | ns    |

| t <sub>OH</sub> <sup>(1)</sup>     | Output Hold from<br>Address Change | 0         |      | 0    |       | 0         |      | ns    |

Note:

(1) This parameter is tested initially and after a design or process change that affects the parameter. (2) Output floating (High-Z) is defined as the state when the external data line is no longer driven by the output buffer. (3)  $V_{IHC} = V_{CC} - 0.3V$  to  $V_{CC} + 0.3V$ .

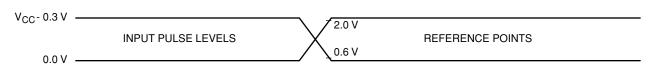

## Figure 1. A.C. Testing Input/Output Waveform<sup>(4)</sup>

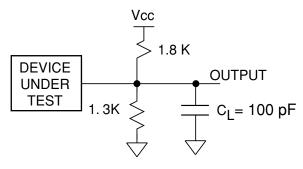

## Figure 2. A.C. Testing Load Circuit (example)

C<sub>1</sub> INCLUDES JIG CAPACITANCE

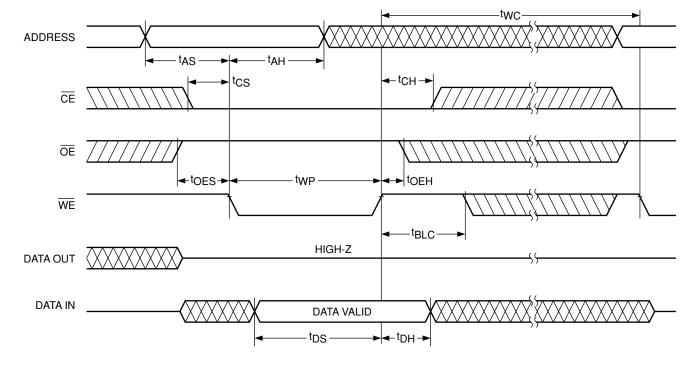

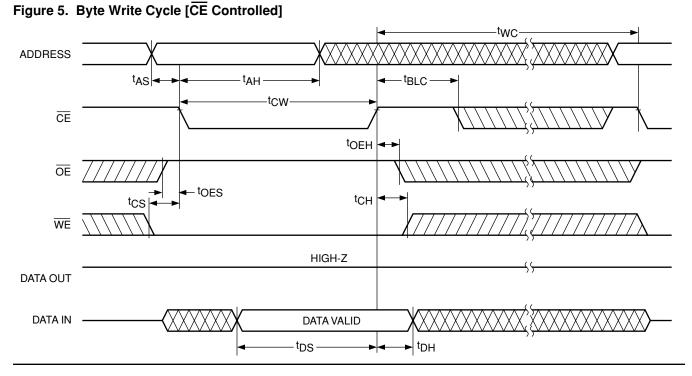

## A.C. CHARACTERISTICS, Write Cycle

$V_{CC}$  = 3.0V to 3.6V, unless otherwise specified.

|                                    |                                        | 28LV | 28LV64-15 |     | /64-20 | 28LV64-25 |     |       |  |

|------------------------------------|----------------------------------------|------|-----------|-----|--------|-----------|-----|-------|--|

| Symbol                             | Parameter                              | Min  | Max       | Min | Max    | Min       | Max | Units |  |

| twc                                | Write Cycle Time                       |      | 5         |     | 5      |           | 5   | ms    |  |

| tas                                | Address Setup Time0                    | 0    |           | 0   |        | 0         |     | ns    |  |

| tан                                | Address Hold Time                      | 100  |           | 100 |        | 100       |     | ns    |  |

| tcs                                | CE Setup Time                          | 0    |           | 0   |        | 0         |     | ns    |  |

| tсн                                | CE Hold Time                           | 0    |           | 0   |        | 0         |     | ns    |  |

| tcw <sup>(2)</sup>                 | CE Pulse Time                          | 110  |           | 150 |        | 150       |     | ns    |  |

| toes                               | OE Setup Time                          | 0    |           | 10  |        | 10        |     | ns    |  |

| tоен                               | OE Hold Time                           | 0    |           | 10  |        | 10        |     | ns    |  |

| twP <sup>(2)</sup>                 | WE Pulse Width                         | 110  |           | 150 |        | 150       |     | ns    |  |

| tDS                                | Data Setup Time                        | 60   |           | 100 |        | 100       |     | ns    |  |

| tdн                                | Data Hold Time                         | 0    |           | 0   |        | 0         |     | ns    |  |

| tinit <sup>(1)</sup>               | Write Inhibit Period<br>After Power-up | 5    | 10        | 5   | 10     | 5         | 10  | ms    |  |

| t <sub>BLC</sub> <sup>(1)(3)</sup> | Byte Load Cycle Time                   | 0.05 | 100       | 0.1 | 100    | 0.1       | 100 | μs    |  |

Note:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

(2) A write pulse of less than 20ns duration will not initiate a write cycle.

(3) A timer of duration  $t_{BLC}$  max. begins with every LOW to HIGH transition of  $\overline{WE}$ . If allowed to time out, a page or byte write will begin; however a transition from HIGH to LOW within  $t_{BLC}$  max. stops the timer.

(4) Input rise and fall times (10% and 90%) < 10 ns.

## **DEVICE OPERATION**

#### Read

Data stored in the CAT28LV64 is transferred to the data bus when  $\overline{WE}$  is held high, and both  $\overline{OE}$  and  $\overline{CE}$  are held low. The data bus is set to a high impedance state when either  $\overline{CE}$  or  $\overline{OE}$  goes high. This 2-line control architecture can be used to eliminate bus contention in a system environment.

#### Figure 3. Read Cycle

#### **Byte Write**

A write cycle is executed when both  $\overline{CE}$  and  $\overline{WE}$  are low, and  $\overline{OE}$  is high. Write cycles can be initiated using either  $\overline{WE}$  or  $\overline{CE}$ , with the address input being latched on the falling edge of  $\overline{WE}$  or  $\overline{CE}$ , whichever occurs last. Data, conversely, is latched on the rising edge of  $\overline{WE}$  or  $\overline{CE}$ , whichever occurs first. Once initiated, a byte write cycle automatically erases the addressed byte and the new data is written within 5 ms.

Figure 4. Byte Write Cycle [WE Controlled]

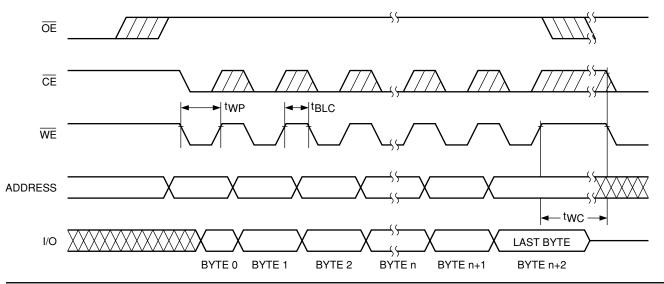

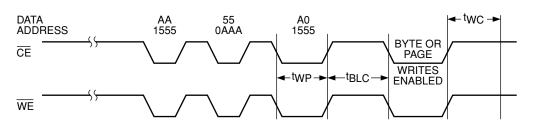

## Page Write

The page write mode of the CAT28LV64 (essentially an extended BYTE WRITE mode) allows from 1 to 32 bytes of data to be programmed within a single EEPROM write cycle. This effectively reduces the byte-write time by a factor of 32.

Following an initial WRITE operation (WE pulsed low, for twp, and then high) the page write mode can begin by issuing sequential WE pulses, which load the address and data bytes into a 32 byte temporary buffer. The page address where data is to be written, specified by bits A<sub>5</sub> to A<sub>12</sub>, is latched on the last falling edge of WE. Each byte within the page is defined by address bits A<sub>0</sub> to A<sub>4</sub>

(which can be loaded in any order) during the first and subsequent write cycles. Each successive byte load cycle must begin within  $t_{BLC\,MAX}$  of the rising edge of the preceding  $\overline{WE}$  pulse. There is no page write window limitation as long as  $\overline{WE}$  is pulsed low within  $t_{BLC\,MAX}$ .

Upon completion of the page write sequence,  $\overline{\text{WE}}$  must stay high a minimum of t<sub>BLC MAX</sub> for the internal automatic program cycle to commence. This programming cycle consists of an erase cycle, which erases any data that existed in each addressed cell, and a write cycle, which writes new data back into the cell. A page write will only write data to the locations that were addressed and will not rewrite the entire page.

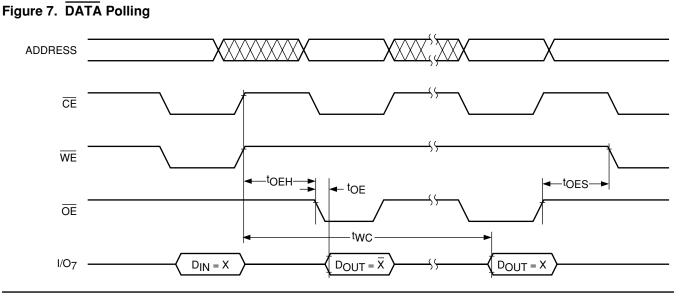

## DATA Polling

DATA polling is provided to indicate the completion of write cycle. Once a byte write or page write cycle is initiated, attempting to read the last byte written will output the complement of that data on  $I/O_7$  ( $I/O_0-I/O_6$  are indeterminate) until the programming cycle is complete. Upon completion of the self-timed write cycle, all I/O's will output true data during a read cycle.

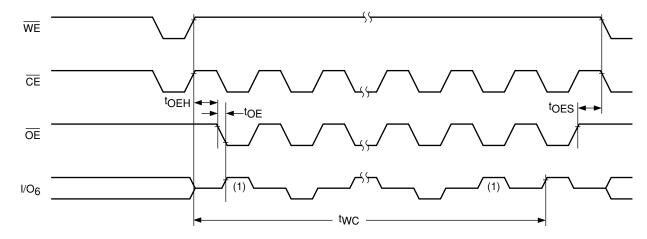

## Toggle Bit

In addition to the DATA Polling feature, the device offers an additional method for determining the completion of a write cycle. While a write cycle is in progress, reading data from the device will result in  $I/O_6$  toggling between one and zero. However, once the write is complete,  $I/O_6$ stops toggling and valid data can be read from the device.

## Figure 8. Toggle Bit

Note:

(1) Beginning and ending state of  $I/O_6$  is indeterminate.

#### HARDWARE DATA PROTECTION

The following is a list of hardware data protection features that are incorporated into the CAT28LV64.

- (1)  $V_{CC}$  sense provides for write protection when  $V_{CC}$  falls below 2.0V min.

- (2) A power on delay mechanism,  $t_{INIT}$  (see AC characteristics), provides a 5 to 10 ms delay before a write sequence, after V<sub>CC</sub> has reached 2.40V min.

- (3) Write inhibit is activated by holding any one of  $\overline{OE}$  low,  $\overline{CE}$  high or  $\overline{WE}$  high.

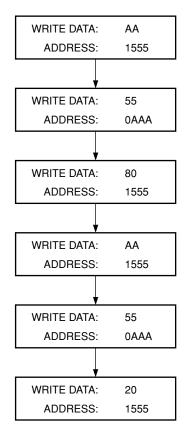

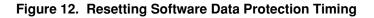

#### Figure 9. Write Sequence for Activating Software Data Protection

WRITE DATA: AA ADDRESS: 1555 WRITE DATA: 55 ADDRESS: 0AAA WRITE DATA: A0 ADDRESS: 1555 SOFTWARE DATA PROTECTION ACTIVATED (1) WRITE DATA: ΧХ TO ANY ADDRESS WRITE LAST BYTE TO LAST ADDRESS

## 28LV64 F12

#### ZOLV

#### Note:

(1) Write protection is activated at this point whether or not any more writes are completed. Writing to addresses must occur within t<sub>BLC</sub> Max., after SDP activation.

(4) Noise pulses of less than 20 ns on the WE or CE inputs will not result in a write cycle.

#### SOFTWARE DATA PROTECTION

The CAT28LV64 features a software controlled data protection scheme which, once enabled, requires a data algorithm to be issued to the device before a write can be performed. The device is shipped from Catalyst with the software protection NOT ENABLED (the CAT28LV64 is in the standard operating mode).

#### Figure 10. Write Sequence for Deactivating Software Data Protection

To activate the software data protection, the device must be sent three write commands to specific addresses with specific data (Figure 9). This sequence of commands (along with subsequent writes) must adhere to the page write timing specifications (Figure 11). Once this is done, all subsequent byte or page writes to the device must be preceded by this same set of write commands. The data protection mechanism is activated until a deactivate sequence is issued regardless of power on/off transitions. This gives the user added inadvertent write protection on power-up in addition to the hardware protection provided. To allow the user the ability to program the device with an EEPROM programmer (or for testing purposes) there is a software command sequence for deactivating the data protection. The six step algorithm (Figure 10) will reset the internal protection circuitry, and the device will return to standard operating mode (Figure 12 provides reset timing). After the sixth byte of this reset sequence has been issued, standard byte or page writing can commence.

### Figure 11. Software Data Protection Timing

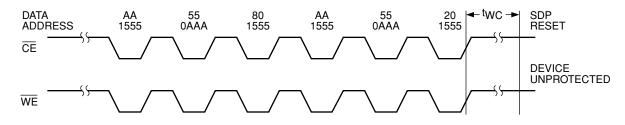

## **ORDERING INFORMATION**

\* -40°C to +125°C is available upon request

Notes:

(1) The device used in the above example is a CAT28LV64NI-25T (PLCC, Industrial temperature, 250 ns Access Time, Tape & Reel).

## **REVISION HISTORY**

| Date     | Revision | Comments                          |  |

|----------|----------|-----------------------------------|--|

| 3/29/04  | С        | Added Green packages in all areas |  |

| 04/20/04 | D        | Delete data sheet designation     |  |

|          |          | Update Ordering Information       |  |

|          |          | Update Revision History           |  |

|          |          | Update Rev Number                 |  |

#### Copyrights, Trademarks and Patents

© Catalyst Semiconductor, Inc.

Trademarks and registered trademarks of Catalyst Semiconductor include each of the following:

Beyond Memory <sup>™</sup>, DPP <sup>™</sup>, EZDim <sup>™</sup>, LDD <sup>™</sup>, MiniPot<sup>™</sup> and Quad-Mode<sup>™</sup>

Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products. For a complete list of patents issued to Catalyst Semiconductor contact the Company's corporate office at 408.542.1000.

CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.

Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.

Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.

Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.

Catalyst Semiconductor, Inc. Corporate Headquarters 2975 Stender Way Santa Clara, CA 95054 Phone: 408.542.1000 Fax: 408.542.1200 www.catsemi.com

Publication #:1010Revison:DIssue date:04/20/04

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for EEPROM category:

Click to view products by CATALYST SEMICONDUCTOR INC manufacturer:

Other Similar products are found below :

M29F040-70K6 718278CB 718620G AT28C256-15PU-ND 444358RB 444362FB BR93C46-WMN7TP 442652G 701986CB TC58NVG0S3HBAI4 5962-8751413XA TC58BVG0S3HBAI4 TH58NYG3S0HBAI6 CAT25320YIGT-KK CAT25320DWF LE24C162-R-E 5962-8751417YA 5962-8751409YA CAT25M01LI-G DS28E11P+ BR9016AF-WE2 LE2464DXATBG CAS93C66VP2I-GT3 DS28E25+T DS28EL15Q+T M95320-DFDW6TP DS28E05GB+T AT25320B-SSPDGV-T HE24C64WLCSPD BL24SA128B-CSRC 24FC16T-I/OT 24FC08T-I/OT M24128-BFMN6TP S-24CS04AFM-TFH-U M24C04-FMC5TG M24C16-DRMN3TPK M24C64-DFMN6TP 34AA02-EMS M95080-RMC6TG M95128-DFCS6TP/K M95128-DFDW6TP M95256-DFMN6TP M95320-RDW6TP M95640-RDW6TP AT17LV010-10CU AT24C01C-SSHM-B AT24C01D-MAHM-T AT24C04D-MAHM-T AT24C04D-SSHM-T AT24C08C-SSHM-B