# CWR500® Datasheet

Qi Compliant 5W Wireless Power Receiver IC

# **General Description**

CWR500 can deliver up to 5W as a highly-integrated single-chip wireless medium power receiver IC. As wireless power transfer systems are getting more popular, they require more fast charging and high efficiency solution. The CWR500 wireless power receiver IC is compliant with WPC 1.2.4 standard and supports the 5W baseband power profile (BPP). The CWR500 power receiver integrates a synchronous rectifier, a low drop-out regulator, and communication controllers which use Amplitude Shift Keying (ASK). The chip also supports the Foreign Object Detection (FOD) extension in WPC 1.2.4. For achieving chip stability, protection tools are implemented, such as over-current-protection, over-voltage-protection, thermal shutdown, and under voltage lock-out (UVLO). Configurable analog blocks can be used independently and co-operated with the control and communication unit.

## **Features Overview**

- Single-chip dual mode 5W receiver for WPC 1.2.4 compliance

- Support 5W baseline power profile (BPP)

- FOD extension supports

- Integrated Synchronous Rectifier Receiver.

- Support Output Power up to 5W.

- High Rectifier Efficiency up to 95%.

- High System Efficiency up to 90%.

- Programmable Dynamic Rectifier Voltage Control.

- Integrated Programmable Linear Regulator.

- Output voltage range of 4.5~5.5V with 0.5V control step.

- Output current limit up to 1A.

- Bi-directional channel communication

- ASK modulation for PRx to PTx

- 24-bit Power Calculation support

- Received Power Calculation for FOD function

- 12-bit ADC for voltage/current measurement.

- Adaptive Coil Power loss/offset compensation.

- Programmable Temperature Control.

- Charger Complete and Enable control inputs

- End of Power Transfer (EPT) Packet management.

- Over Current Limit

- Over Voltage Protection

- Thermal Shutdown

- QFN 40-pin 6mm x 6mm, 0.5mm pitch

- 384-bit One-Time-Programmable Device

# **Applications**

- WPC Compliant Receivers.

- Cell phones and smart phones.

- Digital Cameras.

- Power Banks.

- Wireless Power Embedded Batteries

- Bluetooth Headsets

- Portable Media Players

- Other Hand-held Device

# 1. Description for Implementation

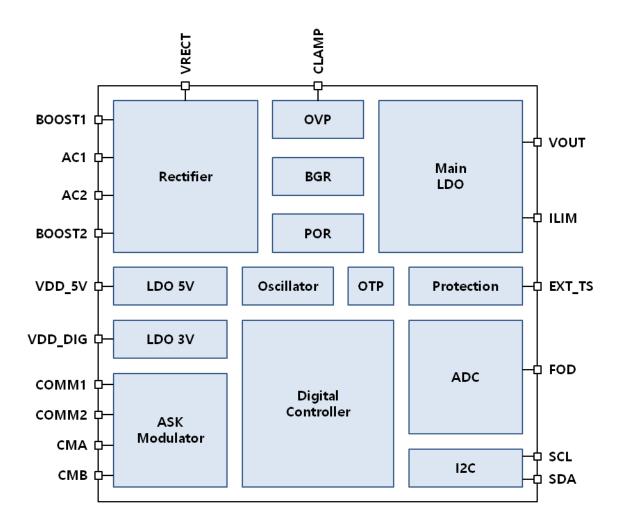

Figure 1. CWR500 Block Diagram

### 1.1 Overview

A wireless power charging system is composed of transmitter and receiver. In general, wireless power transmitter will transfer AC power using a power amplifier through a TX inductor coil. Then wireless power receiver will receive AC power through an RX inductor coil which is strongly coupled with the TX coil. In receiver part, rectifier will change the AC power to DC power and LDO will transfer the DC power to battery charger.

Figure 1 shows the block diagram of CWR500 wireless charging receiver IC. CWR500 receiver will support power transfer up to 5W and it is compliant with WPC 1.2.4 standard. It consists of rectifier, main LDO, internal LDOs, ADC, digital controller and etc.

### 1.2 Rectifier

CWR500 employs a synchronous active rectifier in order to improve AC to DC power conversion efficiency. The rectifier power conversion efficiency is very important because it has a large influence on overall

receiver efficiency. The rectifier in CWR500 will support full-wave, half-wave and passive mode according to the transferred power level. When the power transfer is started initially, the rectifier will operate in passive mode and supply the system power to overall received IC.

### 1.3 Main LDO

Main LDO regulator will transfer DC power from rectifier output to battery charger. LDO in CWR500 is designed to transfer power up to 5W and its output voltage level can be changed by user. The LDO power transistor is designed to minimize its on-resistance because the LDO drop-out voltage is directly related to overall system efficiency. Especially, in case of large power transfer, the LDO drop-out voltage (VRECT-VOUT) should be controlled as small as possible.

#### 1.4 ASK Modulator

CWR500 power receiver communicates with the power transmitter by ASK modulator. The ASK modulator make up the WPC standard 2kHz bi-phase signal by switching the capacitors between COMM1/2 and AC1/AC2. Switching the capacitance at AC1/AC2 nodes will change the impedance of transmitter coil. As a result, amplitude modulation is built up.

### 1.5 ADC

CWR500 power receiver employs 12-bit SAR ADC because it has low power, small area characteristics and moderate speed performance. ADC monitors important internal voltages and currents and gives the system information to the digital controller.

### 1.6 Protection

CWR500 power receiver employs various protection schemes in order to prevent system damage. When the VRECT voltage is too high, the OVP (Over Voltage Protection) function will turn on the clamp path or send the EPT (End Power Transfer) packet to the transmitter. When the main LDO current is too large, the OCL (Over Current Limit) function will limit the output current. When the temperature inside or outside the chip is too high, the OTP (Over Temperature Protection) function will send the EPT packet to transmitter or shutdown the receiver system.

### 1.7 Digital Controller

Digital controller in CWR500 controls all the analog blocks and entire system to perform power transfer operation according to the wireless power transfer standard, that is, WPC 1.2.4. It also supports I2C interface to communicate with external host.

# 2. Pin-out and description

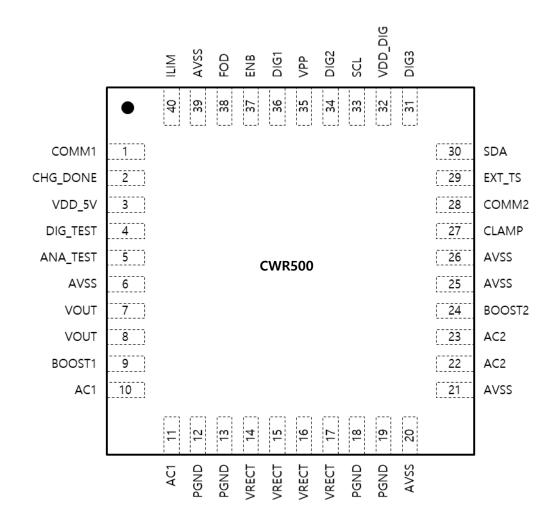

Figure 3. CWR500 Pin Configuration (QFN 40-pin 6mm x 6mm, 0.5mm pitch)

## 2.1 Pin Description (QFN 40-pin 6mm x 6mm, 0.5mm pitch)

| Pin Number | Name     | Type | Description                                                                      |

|------------|----------|------|----------------------------------------------------------------------------------|

| 1          | COMM1    | 0    | High voltage open drain output for ASK modulation.                               |

| 28         | COMM2    | 0    | riigii vottage open draiii output for ASK modutation.                            |

| 2          | CHG_DONE | 1    | Active-high input from the external battery charger to terminate power transfer. |

| 3          | VDD_5V   | 0    | Internal 5V LDO output pin for capacitor connection.                             |

| 4          | DIG_TEST | 0    | Digital test output pin.                                                         |

| 5          | ANA_TEST | 0    | Analog test output pin.                                                          |

# **CWR500**

# Qi Compliant 5W Wireless Power Receiver IC

| 6,20,21,25<br>26,39 | AVSS    |     | Analog ground pin.                                                                                                        |  |

|---------------------|---------|-----|---------------------------------------------------------------------------------------------------------------------------|--|

| 7,8                 | VOUT    | 0   | Main LDO output pin for delivering power to the battery charger.                                                          |  |

| 9                   | BOOST1  | 0   | Bootstrap capacitor connection pin for driving the high-side FETs of                                                      |  |

| 24                  | BOOST2  | 0   | synchronous rectifier.                                                                                                    |  |

| 10,11               | AC1     | I   | AC power input of synchronous rectifier.                                                                                  |  |

| 22,23               | AC2     | I   | AC power input of synchronous rectiner.                                                                                   |  |

| 12,13,18,19         | PGND    |     | Power ground for synchronous rectifier.                                                                                   |  |

| 14,15,16,17         | VRECT   | 0   | Internal synchronous rectifier output for capacitor connection.                                                           |  |

| 27                  | CLAMP   | 0   | High voltage open drain output for analog linear over-voltage protection.                                                 |  |

| 29                  | EXT_TS  | I   | External temperature sensor input. Connect this pin to external NTC thermistor. If not used, connect this pin to VDD_DIG. |  |

| 30                  | SDA     | 1/0 | I <sup>2</sup> C data input/output for internal register access.                                                          |  |

| 31                  | DIG3    | 1   | Scan clock for scan test mode.                                                                                            |  |

| 32                  | VDD_DIG | 1/0 | Internal 3V LDO output for digital block and etc.                                                                         |  |

| 33                  | SCL     | I   | I <sup>2</sup> C clock input for internal register access.                                                                |  |

| 34                  | DIG2    | I   | Scan enable for scan test mode.                                                                                           |  |

| 35                  | VPP     | 1   | 8V high voltage power for OTP programming. During the normal operation, connect this pin to VDD_DIG.                      |  |

| 36                  | DIG1    | I   | Enable scan test mode.                                                                                                    |  |

| 37                  | ENB     | I   | Active-low enable pin for the entire chip.                                                                                |  |

| 38                  | FOD     | I   | FOD offset setting pin. Connect a resistor between this pin and GND.                                                      |  |

| 40                  | ILIM    | I   | Output current or over-current limit level programming pin.                                                               |  |

# 3. Application Guide

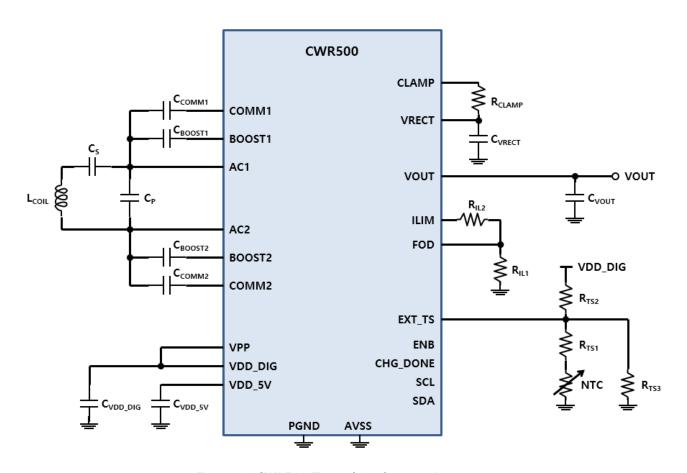

Figure 4. CWR500 Typical Application Diagram

### 3.1 Receiver Coil and Resonant Capacitors

The receiver coil design is related to the overall system application. The coil inductance, shape and material can be chosen according to your applications. The recommended receiver coil inductance for dual mode operation is between 5uH to 10uH. Series and parallel resonant capacitors  $C_S$  and  $C_P$  are set according to WPC specification. The capacitance of the resonant capacitors can be calculated by the following equations.

$$\begin{split} C_S &= \frac{1}{L'_S \times (2\pi f_S)^2} \\ C_P &= \frac{1}{L_S \times (2\pi f_D)^2 - \frac{1}{C_S}} \end{split}$$

In these equations,  $f_S$  and  $f_D$  are the dual resonant frequencies which cover the power transfer frequency range. For example,  $f_S$  can be set to 100kHz and  $f_D$  can be set to 1000kHz, respectively. L'<sub>S</sub> is coil self inductance when placed on the transmitter, and  $L_S$  is the self inductance when placed away from the transmitter.

## 3.2 Boost and Communication Capacitors

As shown in Figure 4, two external bootstrap capacitors  $C_{BOOST1}$  and  $C_{BOOST2}$  are needed to drive the high-side FETs of synchronous rectifier. Bootstrap capacitors should have voltage rating of more than 25V and their recommended capacitances are 15nF.

In order to communicate with transmitter, external capacitors should be connected between high voltage open drain output and AC1/AC2 input. CWR500 will be switching COMM1/COMM2 output in WPC mode. Typical recommended capacitance values are  $C_{COMM1} = C_{COMM2} = 22nF$ .

### 3.3 Output Regulating Capacitors

As shown in Figure 4, rectifier output VRECT and internal LDOs' output VOUT, VDD\_5V, VDD\_DIG should be connected to external capacitor for voltage regulation. Typical recommended capacitance values are  $C_{VRECT}$ =20uF,  $C_{VOUT}$ =3.3uF,  $C_{VDD}$   $_{5V}$ =1uF,  $C_{VDD}$   $_{DIG}$ =1uF, respectively.

### 3.4 Clamp Resistor

When the VRECT voltage is too high, the OVP (Over Voltage Protection) function will turn on the clamp path or send the EPT (End Power Transfer) packet to the transmitter. The clamp path uses high voltage open drain output for analog linear OVP. The recommended resistance value of  $R_{CLAMP}$  is between  $5\Omega$  to  $20\Omega$  according to the transfer power level of application.

### 3.5 Current Limit and FOD Setting Resistors

When the main LDO current is too large, the OCL (Over Current Limit) function will limit the output current. The current limit level can be adjusted by external resistors and it is calculated as follows,

$$I_{LIM} = \frac{45000}{R_{ILIM}} = \frac{45000}{R_{IL1} + R_{IL2}}$$

In this equation, the  $R_{ILIM}$  is the total resistance from the ILIM pin to ground, that is,  $R_{IL1} + R_{IL2}$  as shown in Figure 4. It is recommended to use the resistors of good tolerance less than 1%, because the current estimation in wireless power receiver is very important.

CWR500 adds an FOD offset proportional to output power level when it sends the received power packet to transmitter. The amount of the added FOD offset can be adjusted by the ratio of  $R_{IL1}$  to  $(R_{IL1} + R_{IL2})$ .

### 3.6 External Temperature Sensor

When the temperature inside or outside the chip is too high, the OTP (Over Temperature Protection) function will send the EPT packet to transmitter or shutdown the receiver system. In order to sense the temperature outside chip, connect EXT\_TS pin to external NTC (Negative temperature Coefficient) thermistor as shown in Figure 4. The NTC thermistor should be placed close to the heat emission device. The EXT\_TS voltage  $V_{\text{EXT\_TS}}$  can be calculated as follows,

$$V_{EXT\_TS} = VDD\_DIG \times \frac{\frac{(R_{NTC} + R_{TS1}) \times R_{TS3}}{(R_{NTC} + R_{TS1}) + R_{TS3}}}{\frac{(R_{NTC} + R_{TS1}) \times R_{TS3}}{(R_{NTC} + R_{TS1}) \times R_{TS3}} + R_{TS2}}$$

In this equation, VDD\_DIG is 3V from the internal LDO.

CWR500 compares  $V_{EXT\_TS}$  with internal reference voltages  $V_{TS\_HOT}$  and  $V_{TS\_COLD}$ . If  $V_{EXT\_TS} < V_{TS\_HOT}$ , it means external temperature is too high and CWR500 sends the EPT packet to transmitter. On the other hand, if

$V_{EXT\_TS} > V_{TS\_COLD}$ , it means external temperature is too low and CWR500 also sends the EPT packet to transmitter. Remind that  $V_{EXT\_TS}$  is negative slope curve vs temperature.

The internal reference voltages  $V_{TS\ HOT}$  and  $V_{TS\ COLD}$  are fixed values as follows,

| Internal TS Reference | Threshold Voltage [V] | Hysteresis [mV] |

|-----------------------|-----------------------|-----------------|

| V <sub>TS_HOT</sub>   | 0.315                 | 20              |

| $V_{TS\_COLD}$        | 0.980                 | 80              |

Recommended NTC resistance range is from hundreds of  $\Omega$  to hundreds of  $k\Omega$  vs temperature. After choosing the appropriate NTC thermistor, you can design  $R_{TS1}$ ,  $R_{TS2}$  and  $R_{TS3}$  according to your thermal protection specification. Table 1 shows an EXT\_TS thermal protection design example.

| Temp<br>[℃] | VDD_DIG<br>[V] | R <sub>NTC</sub><br>[kΩ] | $R_{TS1}$ [k $\Omega$ ] | $R_{TS2}$ [k $\Omega$ ] | $R_{TS3}$ [k $\Omega$ ] | V <sub>EXT_TS</sub> [V] | Status                                                           |

|-------------|----------------|--------------------------|-------------------------|-------------------------|-------------------------|-------------------------|------------------------------------------------------------------|

| -40         | 3.0            | 188.5                    | 3.9                     | 47                      | 68                      | 1.550                   |                                                                  |

| -30         | 3.0            | 111.3                    | 3.9                     | 47                      | 68                      | 1.429                   | $V_{EXT\_TS} > V_{TS\_COLD}$                                     |

| -20         | 3.0            | 67.8                     | 3.9                     | 47                      | 68                      | 1.278                   | Send EPT packet                                                  |

| -10         | 3.0            | 42.5                     | 3.9                     | 47                      | 68                      | 1.109                   |                                                                  |

| 0           | 3.0            | 27.3                     | 3.9                     | 47                      | 68                      | 0.938                   |                                                                  |

| 10          | 3.0            | 18.0                     | 3.9                     | 47                      | 68                      | 0.782                   |                                                                  |

| 20          | 3.0            | 12.1                     | 3.9                     | 47                      | 68                      | 0.648                   |                                                                  |

| 30          | 3.0            | 8.31                     | 3.9                     | 47                      | 68                      | 0.541                   | V <sub>TS_HOT</sub> < V <sub>EXT_TS</sub> < V <sub>TS_COLD</sub> |

| 40          | 3.0            | 5.83                     | 3.9                     | 47                      | 68                      | 0.460                   | Normal charging operation                                        |

| 50          | 3.0            | 4.16                     | 3.9                     | 47                      | 68                      | 0.399                   |                                                                  |

| 60          | 3.0            | 3.02                     | 3.9                     | 47                      | 68                      | 0.354                   |                                                                  |

| 70          | 3.0            | 2.23                     | 3.9                     | 47                      | 68                      | 0.321                   |                                                                  |

| 80          | 3.0            | 1.67                     | 3.9                     | 47                      | 68                      | 0.296                   |                                                                  |

| 90          | 3.0            | 1.27                     | 3.9                     | 47                      | 68                      | 0.278                   |                                                                  |

| 100         | 3.0            | 0.98                     | 3.9                     | 47                      | 68                      | 0.265                   | V <sub>EXT_TS</sub> < V <sub>TS_HOT</sub><br>Send EPT packet     |

| 110         | 3.0            | 0.76                     | 3.9                     | 47                      | 68                      | 0.255                   | ,                                                                |

| 120         | 3.0            | 0.60                     | 3.9                     | 47                      | 68                      | 0.247                   |                                                                  |

Table 1. EXT\_TS Thermal Protection Design Example

In this example, the hot temperature threshold  $T_{TS\_HOT}$  and the cold temperature threshold  $T_{TS\_COLD}$  are designed to be 80°C and -10°C respectively. You can change the hot and cold temperature threshold according to your application by changing the related resistors.

## 3.7 PCB Layout Guide

- Keep the trace resistance as low as possible on large current nets as shown in Table 2.

- ullet Resonant capacitors  $C_S$  and  $C_P$  need to be as close to the device as possible.

# **CWR500**

# Qi Compliant 5W Wireless Power Receiver IC

- Clamp, boost and communication capacitors (C<sub>CLAMP</sub>, C<sub>BOOST1</sub>, C<sub>BOOST2</sub>, C<sub>COMM1</sub>, C<sub>COMM2</sub>) need to be as close to the device as possible.

- Output regulating capacitors C<sub>VRECT</sub> and C<sub>VOUT</sub> need to be as close to the device as possible.

| Net (Ball)   | Туре | Maximum Current [A] |

|--------------|------|---------------------|

| AC1, AC2     | AC   | 1                   |

| VRECT        | AC   | 1                   |

| VOUT         | DC   | 1                   |

| PGND         | AC   | 1                   |

| COMM1, COMM2 | AC   | 0.5                 |

| CLAMP        | AC   | 1                   |

Table 2. Large Current Nets

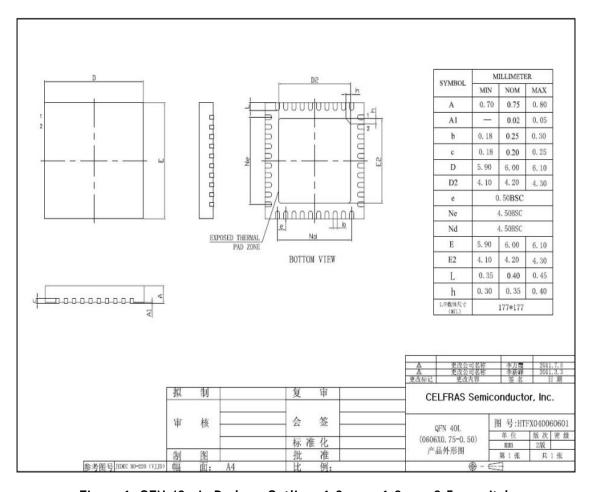

# 4. Package Outline

Figure 6. QFN 40-pin Package Outline, 6.0mm x 6.0mm, 0.5mm pitch

# 5. Electrical Characteristics

#### **Absolute Maximum Rating** 5.1

| PIN                                                           | Parameter | Rating      | Unit |

|---------------------------------------------------------------|-----------|-------------|------|

| AC1, AC2, COMM1, COMM2,<br>VRECT, CLAMP                       | Voltage   | -0.3 to 20  | ٧    |

| BOOST1, BOOST2                                                | Voltage   | -0.3 to 26  | ٧    |

| VOUT                                                          | Voltage   | -0.3 to 15  | ٧    |

| VPP                                                           | Voltage   | -0.3 to 8   | ٧    |

| VDD_5V, VDD_DIG, ENB, CHG_DONE<br>ILIM, FOD, EXT_TS, SCL, SDA | Voltage   | -0.3 to 6   | ٧    |

| PGND                                                          | Voltage   | -0.3 to 0.3 | ٧    |

| AC1, AC2, VRECT, VOUT, CLAMP, PGND                            | Current   | 2           | Α    |

| COMM1, COMM2                                                  | Current   | 1           | Α    |

#### 5.2 **Recommended Operating Condition**

| Symbol            | Description               |  | Тур. | Max. | Unit       |

|-------------------|---------------------------|--|------|------|------------|

| $V_{RECT}$        | Rectifier voltage range   |  |      | 10   | ٧          |

| Іоит              | Main LDO output current   |  |      | 1    | Α          |

| I <sub>COMM</sub> | COMM1, COMM2 sink current |  |      | 500  | mA         |

| TJ                | Junction temperature      |  |      | 125  | $^{\circ}$ |

| T <sub>A</sub>    | Ambient temperature       |  |      | 85   | $^{\circ}$ |

#### 5.3 **Device Characteristics**

| Symbol               | Description                          | Conditions                   | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------|------------------------------|------|------|------|------|

| Synchronous A        | ctive Rectifier                      |                              |      |      |      |      |

| $V_{IN\_RECT}$       | AC1, AC2 input voltage range         |                              | 4.0  |      | 10   | ٧    |

| f <sub>IN_RECT</sub> | AC1, AC2 input frequency range       |                              | 80   |      | 500  | kHz  |

| E <sub>ff_RECT</sub> | AC to DC power conversion efficiency |                              |      | 92   |      | %    |

| $V_{UVLO}$           | Under voltage lockout                | V <sub>RECT</sub> : 0V to 4V |      | 3.2  | 3.3  | ٧    |

| $V_{UVLO\_HYS}$      | Under voltage lockout hysteresis     | V <sub>RECT</sub> : 4V to 0V |      | 400  |      | mV   |

| Main LDO             |                                      |                              |      |      |      |      |

| $V_{IN\_MLDO}$       | Main LDO input voltage range         |                              | 4.0  |      | 10   | ٧    |

# **CWR500**

# Qi Compliant 5W Wireless Power Receiver IC

|                            | T                                                                                   |                                                        |     |       |     |            |

|----------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------|-----|-------|-----|------------|

| V <sub>OUT_MLDO</sub>      | Main LDO output voltage range<br>Register programmable                              | V <sub>RECT</sub> >5V                                  | 4.5 | 5.0   | 5.5 | ٧          |

| V <sub>OUT_MLDO_STEP</sub> | Main LDO output voltage control step                                                |                                                        |     | 0.5   |     | ٧          |

| I <sub>OUT_MLDO</sub>      | Main LDO output current range                                                       |                                                        |     |       | 1.3 | Α          |

| P <sub>SRR_MLDO</sub>      | Main LDO power supply rejection ratio                                               | C <sub>VOUT</sub> =3.3uF<br>DC to 100MHz               | 20  |       |     | dB         |

| Internal LDO               |                                                                                     |                                                        |     |       |     |            |

| V <sub>OUT_VDD_5V</sub>    | Internal VDD_5V LDO output voltage range                                            | V <sub>RECT</sub> >5V                                  |     | 5     |     | ٧          |

| V <sub>OUT_VDD_DIG</sub>   | Internal VDD_DIG LDO output voltage range                                           | V <sub>RECT</sub> >3V                                  |     | 3     |     | ٧          |

| BGR                        |                                                                                     |                                                        |     |       |     |            |

| $V_{BGR}$                  | Internal BGR output voltage<br>Register programmable                                | V <sub>RECT</sub> >3V                                  |     | 1.22  |     | ٧          |

| Oscillator                 |                                                                                     |                                                        |     |       |     |            |

| f <sub>osc</sub>           | Internal oscillator frequency<br>Register programmable                              | V <sub>RECT</sub> >3V                                  |     | 15    |     | MHz        |

| ADC                        |                                                                                     |                                                        |     |       |     |            |

| N <sub>ADC</sub>           | ADC resolution                                                                      | V <sub>RECT</sub> >3V                                  |     | 12    |     | bit        |

| f <sub>SAMPLE</sub>        | ADC sampling rate                                                                   | f <sub>OSC</sub> =15MHz                                |     | 217   |     | kSa/s      |

| N <sub>CH_ADC</sub>        | ADC channel                                                                         |                                                        |     | 7     |     |            |

| Protection                 |                                                                                     |                                                        |     |       |     |            |

| l <sub>OCL</sub>           | I <sub>OUT</sub> over current limit protection<br>Programmable by R <sub>ILIM</sub> | R <sub>ILIM</sub> =24kΩ<br>I <sub>OUT</sub> : 0A to 2A |     | 1.875 |     | А          |

| I <sub>OCL_HYS</sub>       | OCL hysteresis                                                                      | I <sub>OUT</sub> : 2A to 0A                            |     | 50    |     | mA         |

| Тотр                       | Over temperature protection Thermal shutdown temperature                            | Temperature:<br>30℃ to 160℃                            |     | 150   |     | $^{\circ}$ |

| T <sub>OTP_HYS</sub>       | OTP hysteresis                                                                      | Temperature:<br>160°C to 30°C                          |     | 20    |     | $^{\circ}$ |

| V <sub>TS_HOT</sub>        | EXT_TS hot temperature protection threshold voltage                                 | V <sub>EXT_TS</sub> : 0V to 0.5V                       |     | 0.315 |     | ٧          |

| V <sub>TS_HOT_HYS</sub>    | V <sub>TS_HOT</sub> hysteresis                                                      | V <sub>EXT_TS</sub> : 0.5V to 0V                       |     | 20    |     | mV         |

| V <sub>TS_COLD</sub>       | EXT_TS cold temperature protection threshold voltage                                | V <sub>EXT_TS</sub> : 0.5V to 1.5V                     |     | 0.980 |     | ٧          |

| V <sub>TS_COLD_HYS</sub>   | V <sub>TS_COLD</sub> hysteresis                                                     | V <sub>EXT_TS</sub> : 1.5V to 0.5V                     |     | 80    |     | mV         |

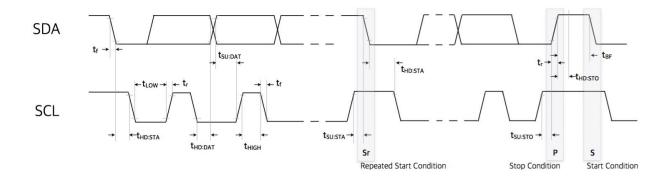

# 6. I<sup>2</sup>C Signal Timing

Figure 7. Timing Diagram for I<sup>2</sup>C interface

| Symbol              | Description                                    | Conditions                      | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------------------------|---------------------------------|------|------|------|------|

| $V_{IL\_SDA}$       | Input low threshold level SDA                  | V <sub>PULLUP</sub> =VDD_DIG=3V |      |      | 0.7  | ٧    |

| $V_{IH\_SDA}$       | Input high threshold level SDA                 | V <sub>PULLUP</sub> =VDD_DIG=3V | 2.3  |      |      | ٧    |

| $V_{IL\_SCL}$       | Input low threshold level SCL                  | V <sub>PULLUP</sub> =VDD_DIG=3V |      |      | 0.7  | ٧    |

| V <sub>IH_SCL</sub> | Input high threshold level SCL                 | V <sub>PULLUP</sub> =VDD_DIG=3V | 2.3  |      |      | ٧    |

| f <sub>SCL</sub>    | SCL clock frequency                            |                                 |      |      | 400  | kHz  |

| t <sub>LOW</sub>    | SCL clock low time                             |                                 | 1.3  |      |      | us   |

| t <sub>HIGH</sub>   | SCL clock high time                            |                                 | 0.6  |      |      | us   |

| t <sub>r</sub>      | Rise time of both SDA and SCL                  |                                 |      |      | 0.3  | us   |

| t <sub>f</sub>      | Fall time of both SDA and SCL                  |                                 |      |      | 0.3  | us   |

| t <sub>SU,STA</sub> | Setup time for START condition                 |                                 | 0.6  |      |      | us   |

| t <sub>HD,STA</sub> | Hold time for START condition                  |                                 | 0.6  |      |      | us   |

| t <sub>su,dat</sub> | Data setup time                                |                                 | 0.1  |      |      | us   |

| t <sub>HD,DAT</sub> | Data hold time                                 |                                 | _    |      | 0.9  | us   |

| t <sub>su,sto</sub> | Setup time for STOP condition                  |                                 | 0.6  |      |      | us   |

| t <sub>BF</sub>     | Bus free time between STOP and START condition |                                 | 1.3  | _    | _    | us   |

Table 3. I<sup>2</sup>C Characteristics

# **Revision History**

| Date       | Version No. | Description         |

|------------|-------------|---------------------|

| 2018/07/01 | 1.0         | Preliminary Release |

|            |             |                     |

|            |             |                     |

|            |             |                     |

|            |             |                     |

|            |             |                     |

# Ordering Information

| Part<br>Number | Package | Shipping<br>Carrier | Description  |

|----------------|---------|---------------------|--------------|

| CWR500         | QFN 40  | Tray                | VOUT=5V(BPP) |

# **Contact US**

# > Headquarters

## CELFRAS Semiconductor Inc. 江西联智集成电路有限公司

59 Chuangxin No.1 Road, Nanchang Hi-tech Development Zone, Nanchang, Jiangxi, P.R.CHINA, Zip:330000

### > International

### **CELFRAS Design Center Inc.**

7F, 225-14, Pangyoyeok-ro, Bundang-gu, Seongnam-si, Gyeonggi-do, 13494, Korea

Tel. +82-70-4055-6466

Fax +82-31-707-8825

### > Contact

Website

### **Technical Support**

cts@celfras.com, june\_yoo@celfras.com

**Sales Contact**

marketing@celfras.com

Copyright © 2018 CELFRAS., Inc. All rights reserved. CELFRAS., Inc.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Battery Management category:

Click to view products by Celfras manufacturer:

Other Similar products are found below:

MP2602DQ-LF-P MP26053DQ-LF-Z MP2611GL-P NCP347MTAHTBG LM3658SD-AEV/NOPB MP2607DL-LF-P MP26121DQ-LF-P MP26123DR-LF-P MP2633GR-P MP2637GR-P BQ24212EVM-678 NCP1855FCCT1G MP2636GR-P FAN54063UCX MAX14680EWC+T MAX14634EWC+T DS2745U+T&R MAX14578EETE+T DS2781EVKIT+ DS2781E+T&R MP2605DQ-LF-P DS2710G+T&R MAX17040G+T MAX14525ETA+T MP2615GQ-P MAX14578EEWC+T LC05132C01NMTTTG MAX8971EWP+T MAX14630EZK+T MAX1873TEEE+T PSC5415A AUR9811DGD SN2040DSQR DS2715BZ+T&R MAX1508ZETA+T MAX14921ECS+T MAX77301EWA+T BD8668GW-E2 MAX16024PTBS+T DS2715Z+T&R MAX16024LTBZ18+T DS2782E+T&R DS2782G+T&R MAX1908ETI+T ISL95522IRZ ISL95522HRZ ARD00558 NCP4371AAEDR2G BD8665GW-E2 MAX8934EETI+T