## CMX991/CMX992

# RF Quadrature Transmitter and RF Quadrature/Low IF Receiver

D/991\_992/22 May 2017 Provisional Issue

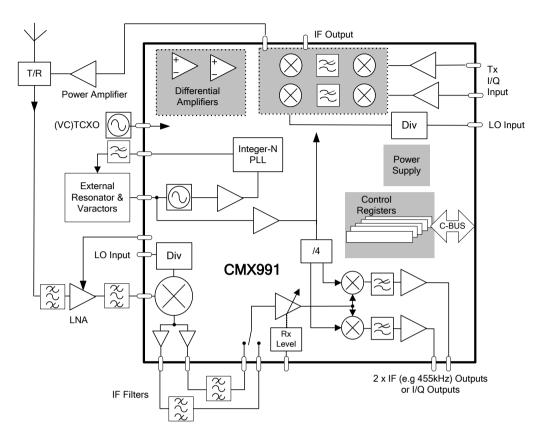

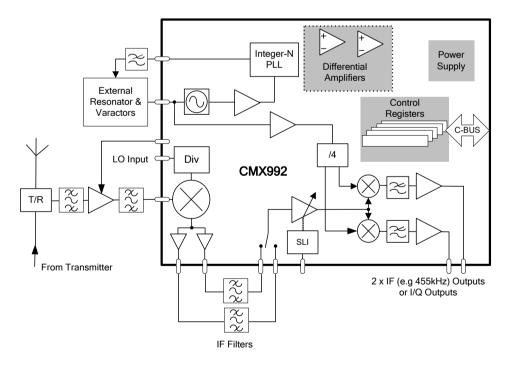

This document describes two separate, high performance, RF ICs covering the range: 100MHz<sup>1</sup> to 1GHz. The CMX991 is an RF Quadrature Transceiver and the CMX992 is an RF Quadrature Receiver.

#### **Features**

- Rx (CMX991 and CMX992)

- o RF mixer with output select

- o 1st IF input select

- Selectable low IF outputs (450kHz/455kHz)

- o 1st IF Variable Gain Amplifier (VGA)

- 1st IF Signal Level Indicator (SLI)

- o Two-mode demodulator

- o I/Q Zero-IF with differential outputs

- Tx (CMX991 only)

- o I/Q modulator to IF

- Image-reject up-converter

- IF and RF outputs

- IF (CMX991 and CMX992)

- o IF LO synthesiser

- o IF VCO negative resistance amplifier

- 3.3V low power operation

### **Applications**

- Analogue/digital multimode radio

- Software Defined Radio (SDR)

- Portable, mobile and base station terminals

- Data telemetry modems

- TETRA (CMX992)

- ETSI: EN 300 113, EN 301 166, EN 302 561, EN 300 220, TS 102 361 (DMR)

- Automatic Identification System (AIS) transponders

- Constant envelope and linear modulation

- Compatible with CMX998 (CMX992 only)

- Narrowband: e.g. 25kHz, 12.5kHz, 6.25kHz

- Wideband: up to 2MHz

- APCO Project 25 (P25) Phase 1 and Phase 2 TDMA: TIA-102.CAAB

- Satellite communications

### 1 Brief Description

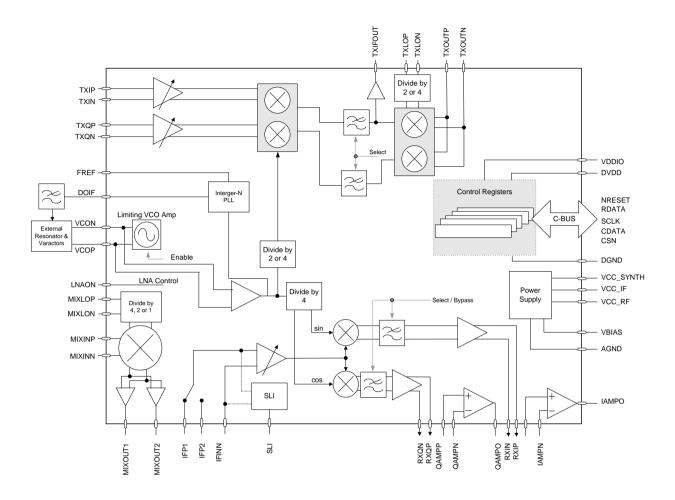

The CMX991 is a single-chip, high performance, RF transceiver that provides the core functions required to implement a full-featured radio transmitter and receiver. It operates from 100MHz to 1GHz and its I/Q architecture supports multiple modulation types and bandwidths with a single radio design. The half-duplex CMX991 integrates Tx modulators, Rx demodulators, IF PLL and IF VCO subsystems to minimise the external circuits needed when implementing a complete transceiver. User-selected modes suit different application requirements.

The Tx path includes an I/Q modulator to accurately generate modulation at the IF frequency, which may then be translated to the final RF frequency by an integrated image-reject up-converter system. The I/Q modulator IF output is also made available for conversion to RF via external circuits, if desired.

The Rx path includes an integrated 1<sup>st</sup> Rx mixer having two outputs to support two external 1<sup>st</sup> IF filter choices, then an integrated 2:1 input mux followed by VGA and wideband signal level measurement functions, to support AGC implementation. The 1<sup>st</sup> IF signal is then either I/Q demodulated to Zero-IF or mixed to a Low IF output. The CMX991 provides differential and single-ended Rx output options and differential amplifiers for flexible signal conditioning.

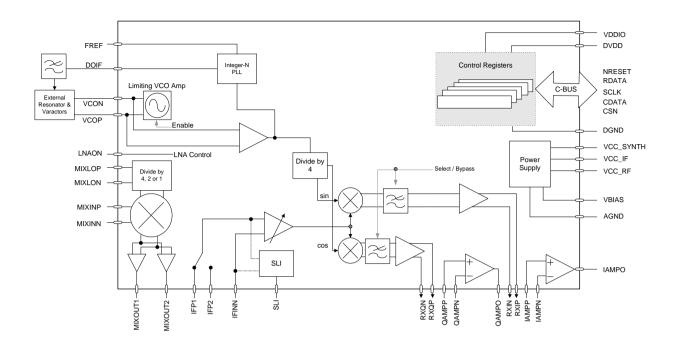

The CMX992 is a single-chip, high performance, RF receiver that includes the core RF and IF receive functions of the CMX991 above and can be used in a wide range of narrowband and wideband wireless products, including multi-mode analogue/digital terminals.

The CMX992 can be used where highly linear modulations are being used, e.g. for applications such as TETRA, where a typical transmitter solution would include the CMX998 Cartesian Feedback Transmitter.

Both devices operate from a single 3.3V supply over a temperature range of -40°C to +85°C and are available in 48-pin VQFN (Q3) packages.

<sup>&</sup>lt;sup>1</sup> The CMX991/CMX992 may be used at lower frequencies by using appropriate external components. Use below 100MHz is covered in a separate application note available from the CML website.

Figure 1 CMX991 - RF Quadrature Transceiver

Figure 2 CMX992 - RF Quadrature/Low IF Receiver

D/991\_992/22

### **CONTENTS**

| Se | ction       |                                                                    | Page           |

|----|-------------|--------------------------------------------------------------------|----------------|

| 1  |             | Brief Description                                                  |                |

|    | 1.1         | History                                                            |                |

| 2  |             | Block Diagrams                                                     | 8              |

| 3  |             | Pin List                                                           | 10             |

|    | 3.1         | Signal Definitions                                                 | 11             |

| 4  |             | External Components                                                | 12             |

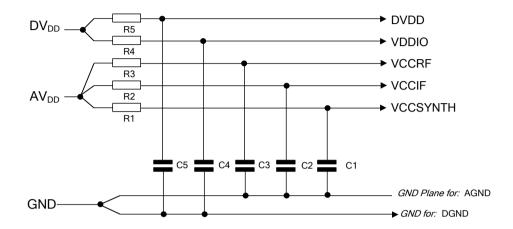

| •  | 4.1         | Power Supply Decoupling                                            |                |

|    | 4.2         | Receiver (CMX991 and CMX992)                                       |                |

|    | 4.3         | Transmitter (CMX991 only)                                          |                |

|    | 4.4         | Main Local Oscillator                                              |                |

|    | 4.5         | IF Local Oscillator (CMX991 and CMX992)                            | 19             |

| 5  |             | General Description                                                | 21             |

|    | 5.1         | Overview                                                           | 21             |

|    | 5.2         | Receiver                                                           |                |

|    | 5.3         | Transmitter (CMX991 only)                                          |                |

|    | 5.4         | Local Oscillators                                                  |                |

|    | 5.5         | V <sub>BIAS</sub>                                                  |                |

|    | 5.6         | Data Interface                                                     |                |

| 6  |             | C-BUS Interface and Register Description                           |                |

|    | 6.1         | General Reset Command (CMX991/CMX992)                              | 29             |

|    | 6.2         | General Control Register (CMX991/CMX992)                           |                |

|    | 6.3<br>6.4  | Rx Control Register (CMX991/CMX992)                                |                |

|    | 6.5         | Rx Mode Register (CMX991/CMX992) Tx Control Register (CMX991 only) |                |

|    | 6.6         | Tx Mode Register (CMX991 only)                                     |                |

|    | 6.7         | Tx Gain Register (CMX991 only)                                     |                |

|    | 6.8         | IF PLL M Divider (CMX991/CMX992)                                   |                |

|    | 6.9         | PLL N Divider (CMX991/CMX992)                                      |                |

| 7  |             | Application Notes                                                  | 36             |

| '  | 7.1         | General                                                            |                |

|    | 7.2         | Using the CMX992 with the CMX998                                   |                |

|    | 7.3         | Receiver Gain Issues                                               |                |

|    | 7.4         | Oscillator Components for Alternative Intermediate Frequencies     |                |

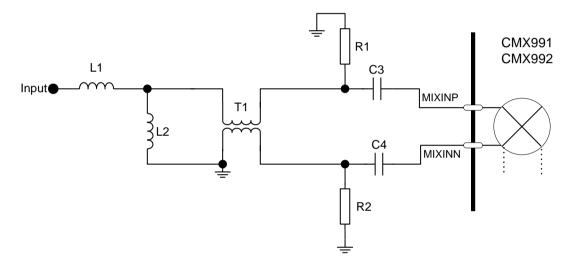

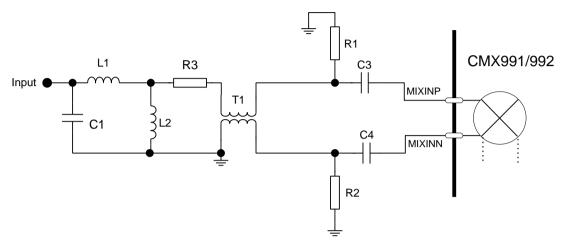

|    | 7.5         | RF Mixer Input Matching                                            | 39             |

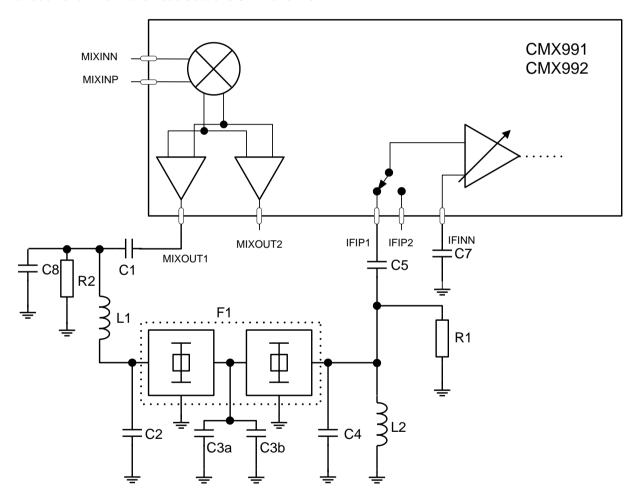

|    | 7.6         | RF Mixer IF Output Matching                                        |                |

|    | 7.7         | IF Input Matching                                                  |                |

|    | 7.8         | Signal Level Indicator (SLI)                                       |                |

|    | 7.9         | Receiver Spurious Rejection Performance                            |                |

|    | 7.10<br>7.1 |                                                                    |                |

|    | 7.1         |                                                                    |                |

|    | 7.1         |                                                                    | <del></del> 50 |

|    |             | ·                                                                  |                |

| 8  | 0 1         | Performance Specification                                          |                |

|    | 8.1         | Electrical Performance                                             | 51<br>60       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <u>Page</u>                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Table 1 Pin List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11                                                                                                                |

| Table 2 Definition of Power Supply and Reference Voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11                                                                                                                |

| Table 3 Decoupling Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12                                                                                                                |

| Table 4 Typical Rx 1 <sup>st</sup> Mixer Input Matching Components for 455MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13                                                                                                                |

| Table 5 1 <sup>st</sup> IF Filtering Components for 45MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                   |

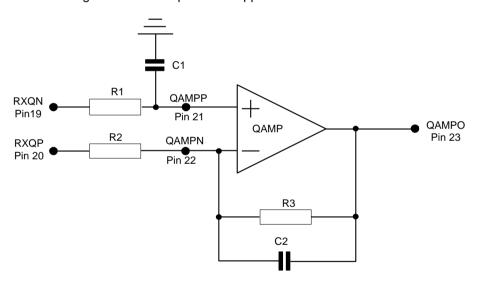

| Table 6 Rx I/Q Differential to Single Ended Amplifier Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                   |

| Table 7 Rx Low IF (455kHz) Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                   |

| Table 8 Transmitter Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                   |

| Table 9 I/Q Modulator Output Matching Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                   |

| Table 10 Rx LO Input Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                   |

| Table 11 IF VCO LO Internal VCO Amplifier Tank Circuit for 180MHz Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                   |

| Table 12 IF LO 3 <sup>rd</sup> Order Loop Filter Circuit for 180MHz Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                   |

| Table 13 Typical IF Gain Compression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                   |

| Table 14 Typical IF VCO Circuit Values for a Variety of IF Frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |

| Table 15 Receiver Input Match Circuit for Other Operating Frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                   |

| Table 16 MIXOUT Equivalent Impedances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                   |

| Table 17 Noise Figure and Gain of IF Amp, VGA, I/Q Mixer and Baseband Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                   |

| Table 18 IFIP1 Port Impedance (Parallel Equivalent Circuit Models)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                   |

| Table 19 IF Noise Figure Measurements at 45 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                   |

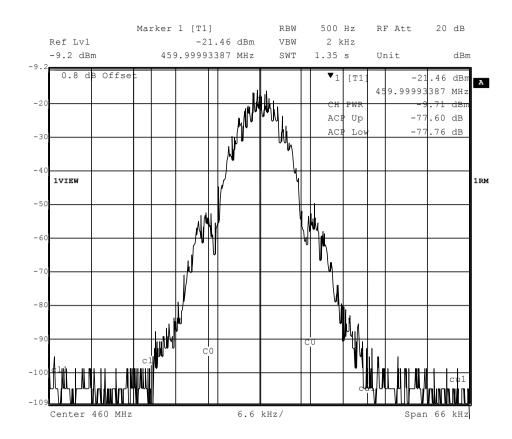

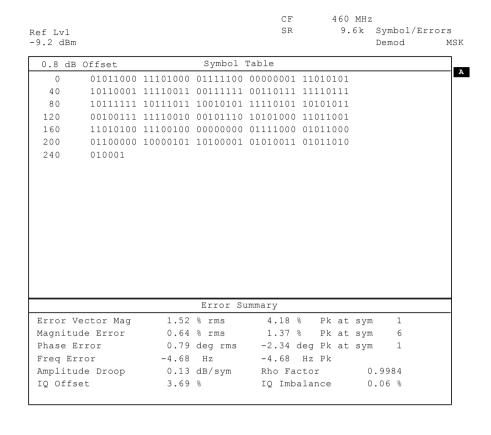

| Table 20 Symbol/Error Table for the Tx with 9.6kbps GMSK from an EV9100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                   |

| <u>Figure</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u>Page</u>                                                                                                       |

| Figure 1 CMX991 – RF Quadrature Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                   |

| Figure 1 CMX991 – RF Quadrature Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2                                                                                                                 |

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2<br>2                                                                                                            |

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2<br>2<br>8                                                                                                       |

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2<br>8<br>9                                                                                                       |

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2<br>8<br>9<br>12                                                                                                 |

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2<br>8<br>9<br>12<br>13                                                                                           |

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver  Figure 3 CMX991 Block Diagram  Figure 4 CMX992 Block Diagram  Figure 5 Recommended Power Supply Connections and Decoupling.  Figure 6 Example External Components – Receive 1 <sup>st</sup> Mixer Input  Figure 7 Example External Components – Receive 1 <sup>st</sup> IF Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2<br>8<br>9<br>12<br>13<br>14                                                                                     |

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver  Figure 3 CMX991 Block Diagram  Figure 4 CMX992 Block Diagram  Figure 5 Recommended Power Supply Connections and Decoupling  Figure 6 Example External Components – Receive 1 <sup>st</sup> Mixer Input  Figure 7 Example External Components – Receive 1 <sup>st</sup> IF Section  Figure 8 Example External Components – Receive I/Q Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2<br>8<br>9<br>12<br>13<br>14<br>15                                                                               |

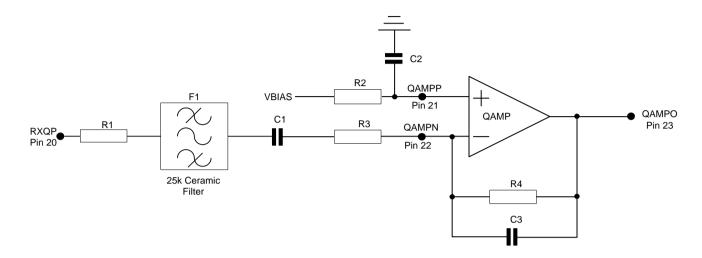

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver  Figure 3 CMX991 Block Diagram  Figure 4 CMX992 Block Diagram  Figure 5 Recommended Power Supply Connections and Decoupling  Figure 6 Example External Components – Receive 1 <sup>st</sup> Mixer Input  Figure 7 Example External Components – Receive 1 <sup>st</sup> IF Section  Figure 8 Example External Components – Receive I/Q Output  Figure 9 Example External Components – Receive Low IF Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2<br>8<br>9<br>12<br>13<br>14<br>15<br>16                                                                         |

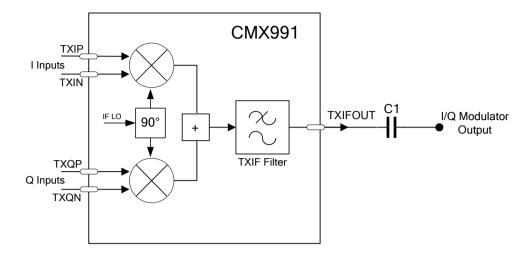

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver  Figure 3 CMX991 Block Diagram  Figure 4 CMX992 Block Diagram  Figure 5 Recommended Power Supply Connections and Decoupling  Figure 6 Example External Components – Receive 1 <sup>st</sup> Mixer Input  Figure 7 Example External Components – Receive 1 <sup>st</sup> IF Section  Figure 8 Example External Components – Receive I/Q Output  Figure 9 Example External Components – Receive Low IF Output  Figure 10 Example External Components – Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2<br>8<br>9<br>12<br>13<br>14<br>15<br>16<br>17                                                                   |

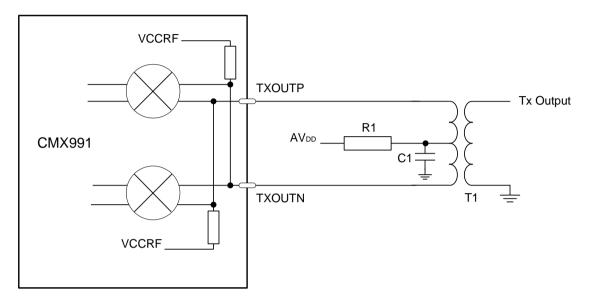

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver Figure 3 CMX991 Block Diagram Figure 4 CMX992 Block Diagram Figure 5 Recommended Power Supply Connections and Decoupling Figure 6 Example External Components – Receive 1 <sup>st</sup> Mixer Input Figure 7 Example External Components – Receive 1 <sup>st</sup> IF Section Figure 8 Example External Components – Receive I/Q Output Figure 9 Example External Components – Receive Low IF Output Figure 10 Example External Components – Transmitter Figure 11 Example External Components – I/Q Modulator Output                                                                                                                                                                                                                                                                                                                                                                                | 2<br>8<br>9<br>12<br>13<br>14<br>15<br>16<br>17                                                                   |

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver Figure 3 CMX991 Block Diagram Figure 4 CMX992 Block Diagram Figure 5 Recommended Power Supply Connections and Decoupling Figure 6 Example External Components – Receive 1 <sup>st</sup> Mixer Input Figure 7 Example External Components – Receive 1 <sup>st</sup> IF Section Figure 8 Example External Components – Receive I/Q Output Figure 9 Example External Components – Receive Low IF Output Figure 10 Example External Components – Transmitter Figure 11 Example External Components – I/Q Modulator Output Figure 12 Example External Components – Rx LO Input                                                                                                                                                                                                                                                                                                                            | 2891213141516171819                                                                                               |

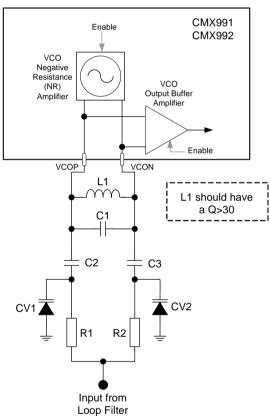

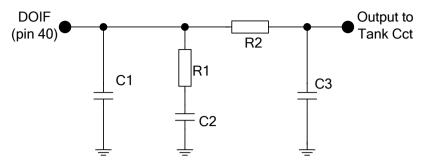

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver Figure 3 CMX991 Block Diagram Figure 4 CMX992 Block Diagram Figure 5 Recommended Power Supply Connections and Decoupling Figure 6 Example External Components – Receive 1st Mixer Input Figure 7 Example External Components – Receive 1st IF Section Figure 8 Example External Components – Receive I/Q Output Figure 9 Example External Components – Receive Low IF Output Figure 10 Example External Components – Transmitter Figure 11 Example External Components – I/Q Modulator Output Figure 12 Example External Components – Rx LO Input Figure 13 Example External Components – IF LO VCO External Tank Circuit                                                                                                                                                                                                                                                                            | 2<br>9<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20                                                      |

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver Figure 3 CMX991 Block Diagram Figure 4 CMX992 Block Diagram Figure 5 Recommended Power Supply Connections and Decoupling. Figure 6 Example External Components – Receive 1st Mixer Input Figure 7 Example External Components – Receive 1st IF Section Figure 8 Example External Components – Receive I/Q Output Figure 9 Example External Components – Receive Low IF Output Figure 10 Example External Components – Transmitter Figure 11 Example External Components – I/Q Modulator Output Figure 12 Example External Components – Rx LO Input Figure 13 Example External Components – IF LO VCO External Tank Circuit Figure 14 Example External Components – IF LO Loop Filter                                                                                                                                                                                                                 | 2<br>8<br>9<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>18<br>19<br>20                                           |

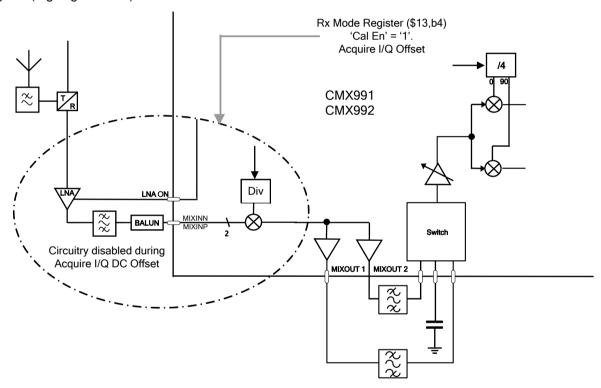

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver Figure 3 CMX991 Block Diagram Figure 4 CMX992 Block Diagram Figure 5 Recommended Power Supply Connections and Decoupling Figure 6 Example External Components – Receive 1st Mixer Input Figure 7 Example External Components – Receive 1st IF Section Figure 8 Example External Components – Receive I/Q Output Figure 9 Example External Components – Receive Low IF Output Figure 10 Example External Components – Transmitter Figure 11 Example External Components – I/Q Modulator Output Figure 12 Example External Components – Rx LO Input Figure 13 Example External Components – IF LO VCO External Tank Circuit Figure 14 Example External Components – IF LO Loop Filter Figure 15 DC Offset Calibration Mode                                                                                                                                                                             | 2<br>8<br>9<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>19<br>20<br>22                                     |

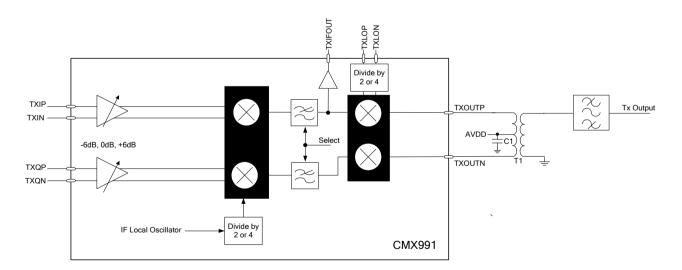

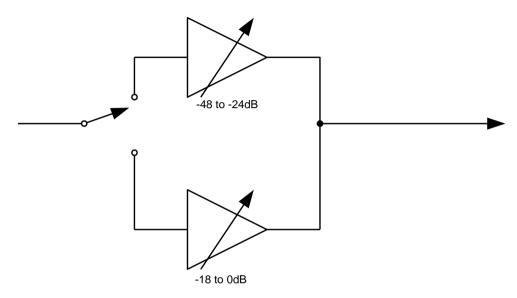

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver  Figure 3 CMX991 Block Diagram  Figure 4 CMX992 Block Diagram  Figure 5 Recommended Power Supply Connections and Decoupling  Figure 6 Example External Components – Receive 1st Mixer Input  Figure 7 Example External Components – Receive 1st IF Section  Figure 8 Example External Components – Receive I/Q Output  Figure 9 Example External Components – Receive Low IF Output  Figure 10 Example External Components – Transmitter  Figure 11 Example External Components – I/Q Modulator Output  Figure 12 Example External Components – Rx LO Input  Figure 13 Example External Components – IF LO VCO External Tank Circuit  Figure 14 Example External Components – IF LO Loop Filter  Figure 15 DC Offset Calibration Mode  Figure 16 CMX991 Transmitter Architecture                                                                                                                     | 2<br>9<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>22<br>23                                          |

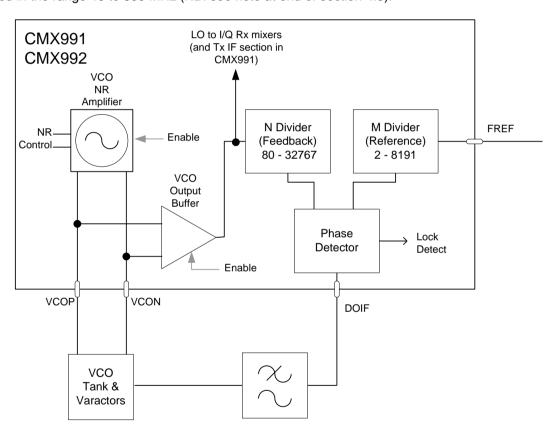

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver Figure 3 CMX991 Block Diagram Figure 4 CMX992 Block Diagram Figure 5 Recommended Power Supply Connections and Decoupling Figure 6 Example External Components – Receive 1st Mixer Input Figure 7 Example External Components – Receive 1st IF Section Figure 8 Example External Components – Receive I/Q Output Figure 9 Example External Components – Receive Low IF Output Figure 10 Example External Components – Transmitter Figure 11 Example External Components – I/Q Modulator Output Figure 12 Example External Components – Rx LO Input Figure 13 Example External Components – IF LO VCO External Tank Circuit Figure 14 Example External Components – IF LO Loop Filter Figure 15 DC Offset Calibration Mode Figure 16 CMX991 Transmitter Architecture Figure 17 CMX991/CMX992 IF Local Oscillator                                                                                       | 2<br>8<br>9<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>18<br>19<br>20<br>22<br>23<br>24                         |

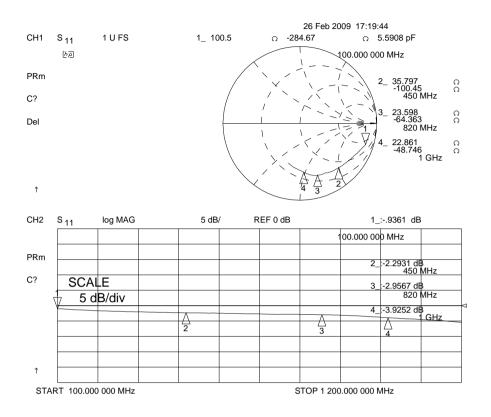

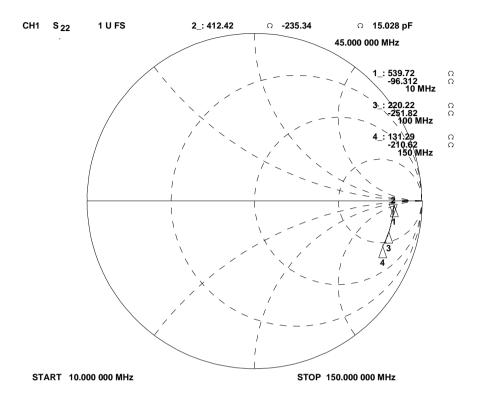

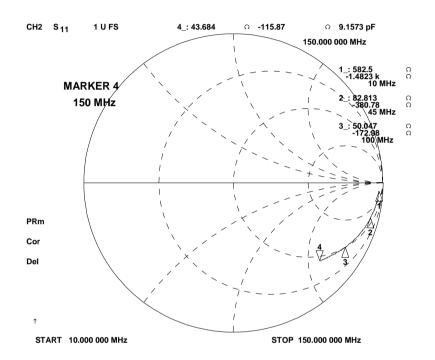

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver  Figure 3 CMX991 Block Diagram  Figure 4 CMX992 Block Diagram  Figure 5 Recommended Power Supply Connections and Decoupling.  Figure 6 Example External Components – Receive 1 <sup>st</sup> Mixer Input.  Figure 7 Example External Components – Receive 1 <sup>st</sup> IF Section  Figure 8 Example External Components – Receive I/Q Output.  Figure 9 Example External Components – Receive Low IF Output.  Figure 10 Example External Components – Transmitter  Figure 11 Example External Components – I/Q Modulator Output.  Figure 12 Example External Components – Rx LO Input.  Figure 13 Example External Components – IF LO VCO External Tank Circuit.  Figure 14 Example External Components – IF LO Loop Filter  Figure 15 DC Offset Calibration Mode.  Figure 16 CMX991 Transmitter Architecture.  Figure 17 CMX991/CMX992 IF Local Oscillator  Figure 18 Typical LO Input Impedance | 2<br>8<br>9<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>22<br>23<br>24<br>26<br>28                   |

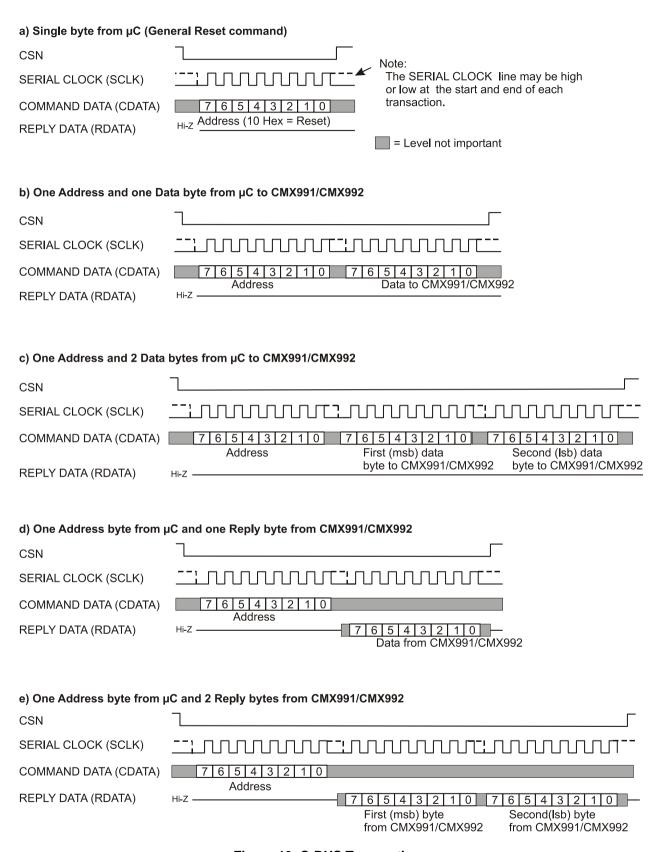

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver Figure 3 CMX991 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2<br>8<br>9<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>22<br>23<br>24<br>24<br>26<br>28                   |

| Figure 2 CMX992 – RF Quadrature/Low IF Receiver Figure 3 CMX991 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2<br>8<br>9<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>18<br>19<br>20<br>22<br>23<br>24<br>26<br>23<br>24<br>21 |

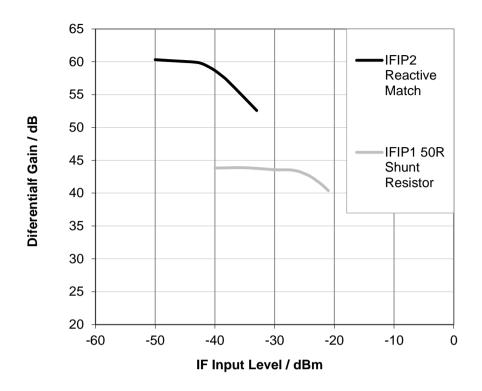

| Figure 24 | IFIP1 Input Impedance at 0dB attenuation                          | 41 |

|-----------|-------------------------------------------------------------------|----|

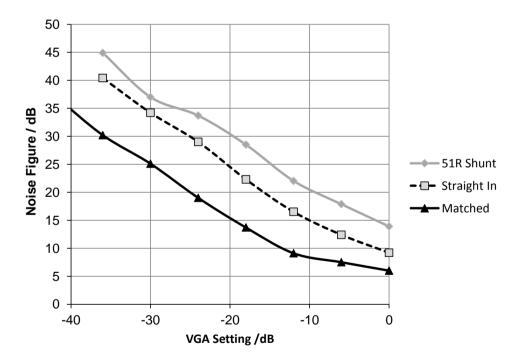

| Figure 25 | Typical Variation in IF Noise Figure                              | 42 |

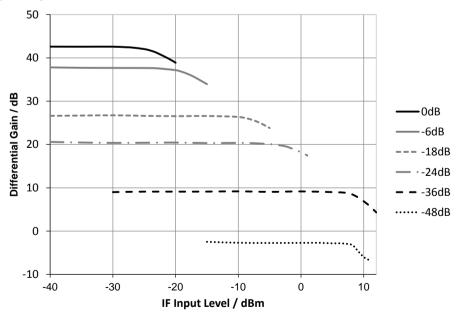

| Figure 26 | Typical Variation in IF Gain Compression                          | 43 |

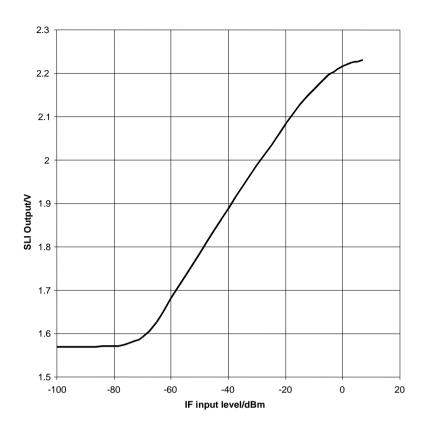

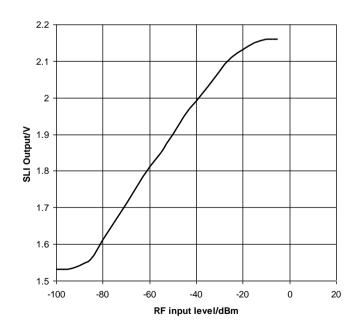

| Figure 27 | Typical SLI Performance                                           | 44 |

| Figure 28 | Typical SLI Performance in an Application Circuit (EV9920B)       | 44 |

| Figure 29 | IF Output Response with and without Blocking Signal Present       | 45 |

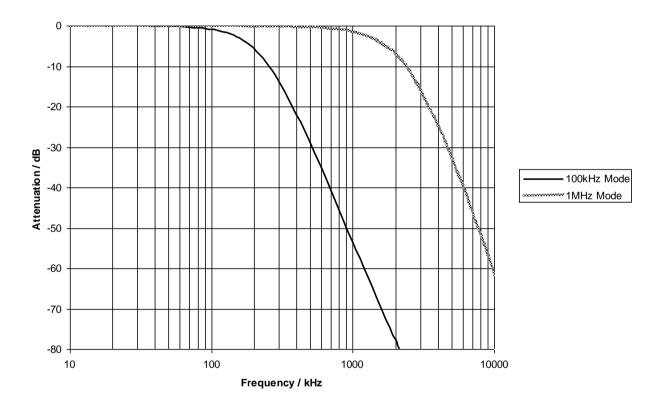

| Figure 30 | Typical Receiver I/Q Frequency Response                           | 46 |

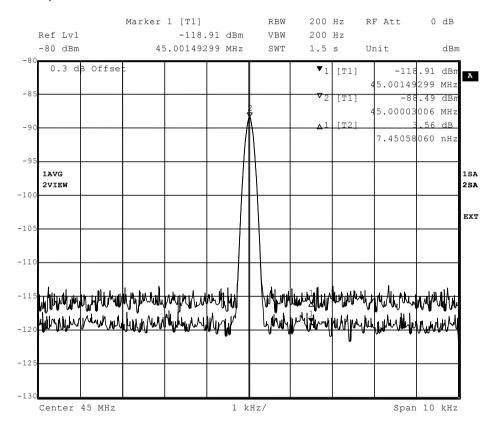

| Figure 31 | Tx Output with 9.6kbps GMSK from an EV9100                        | 47 |

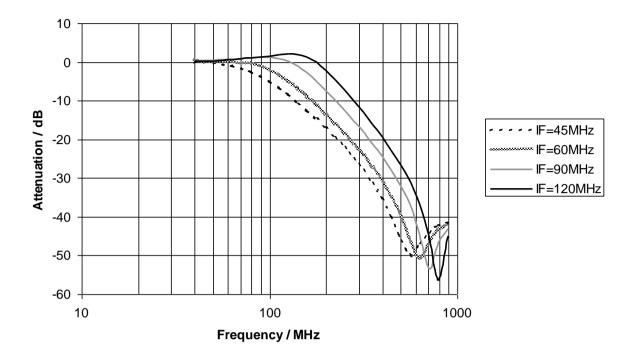

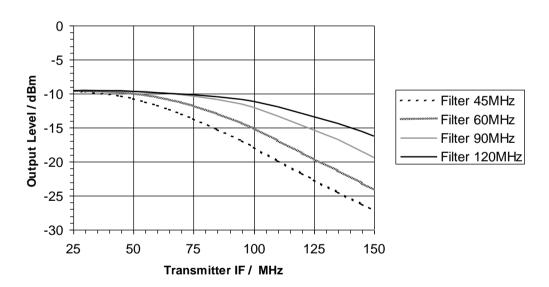

| Figure 32 | Transmitter Path IF Filters                                       | 49 |

| Figure 33 | Transmitter IF Output Showing Filter Responses with IFH bit = '1' | 49 |

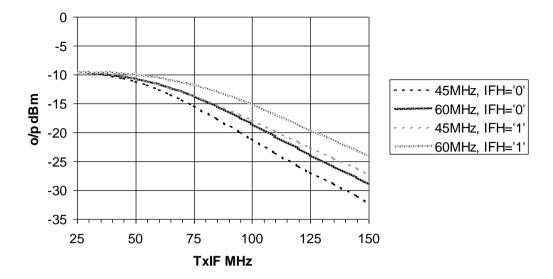

| Figure 34 | Effect of IFH on 45MHz and 60MHz Transmitter IF Filters           | 50 |

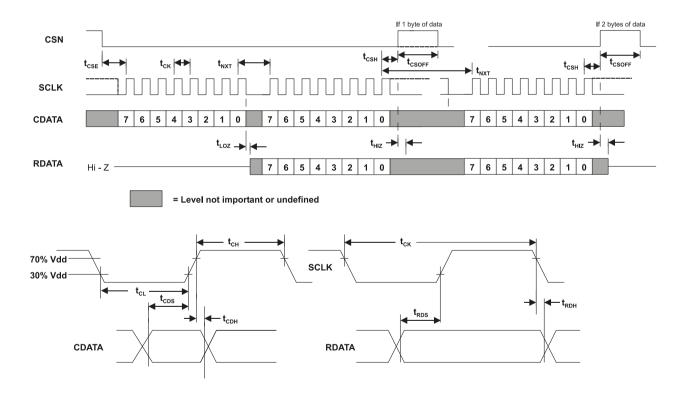

| Figure 35 | C-BUS Timing                                                      | 59 |

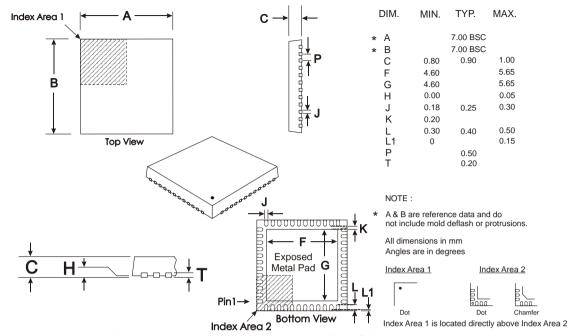

| Figure 36 | Q3 Mechanical Outline:                                            | 60 |

### 1.1 History

| Version | Changes                                                                                                                     | Date       |

|---------|-----------------------------------------------------------------------------------------------------------------------------|------------|

| 22      | For clarification changed Typical Gain Distribution to 7.3.1 System Gain with                                               | May 2017   |

|         | reference made to evaluation board documentation for more technical                                                         |            |

|         | details.                                                                                                                    |            |

|         | Clarified description of RF mixer input impedance                                                                           |            |

|         | Typos corrected, clarifications made                                                                                        |            |

| 21      | Correct typos in Table 19.                                                                                                  | Jun 2016   |

|         | <ul> <li>Figure 3, Figure 4 and Section 7.8: clarified position of SLI circuit.</li> </ul>                                  |            |

|         | <ul> <li>New data in section 7.7.2 on noise figure of the IF stages.</li> </ul>                                             |            |

|         | <ul> <li>New information on IF gain compression in section 7.3.3 and 7.7.3.</li> </ul>                                      |            |

| 20      | <ul> <li>1S305 (typo) corrected to 1SV305; SMV1279 (typo) corrected to SMV1249</li> </ul>                                   | Feb 2015   |

|         | <ul> <li>Typo in note to section 4.5 corrected, 'b1' corrected to 'b7'</li> </ul>                                           |            |

|         | Information added on Rx dc offset variation with temperature (section 7.13)                                                 |            |

| 19      | <ul> <li>Receiver IF section 1 dB Compression point changed to typical;</li> </ul>                                          | Oct 2012   |

|         | measurement method clarified (section 8.1.3.2).                                                                             |            |

|         | • Half IF specification changed to reflect production test limit (section 8.1.3.2).                                         |            |

|         | JDV2S08S replaced with 1S305FCT in Table 14 as JDV diode is obsolete.                                                       |            |

| 18      | <ul> <li>Various editorial corrections.</li> </ul>                                                                          | May 2012   |

|         | Alternative diodes added in Table 11.                                                                                       |            |

| 17      | <ul> <li>VCO N divider start-up issue when using an external VCO (section 4.5)</li> </ul>                                   | Feb 2012   |

| 16      | <ul> <li>Clarification of gain and noise of IF stage in 'Straight in' case (section 7.7)</li> </ul>                         | Jun 2011   |

|         | <ul> <li>Editorial changes for consistency of table header format</li> </ul>                                                |            |

|         | Update of receiver gain partition (section 7.3.1)                                                                           |            |

| 15      | <ul> <li>Details of receiver gain switching added (Section 7.3.2)</li> </ul>                                                | Mar 2011   |

|         | <ul> <li>PLL frequency formula added (section 5.4.1)</li> </ul>                                                             |            |

|         | <ul> <li>Phase noise formula typo corrected (M not N) (section 8.1.3.2 Note 94)</li> </ul>                                  |            |

| 14      | CMX991: Transmitter LO Leakage specification clarified and limits adjusted                                                  | Dec 2010   |

|         | CMX991: Transmitter LO Image typical value updated                                                                          |            |

| 13      | • Transmitter I and Q channels shown in error causing a spectrum inversion in                                               | Sep 2010   |

|         | Tx path. Pins TXQN and TXQP swapped (Table 1)                                                                               |            |

|         | Editorial error in Error! Reference source not found. corrected.                                                            |            |

| 12      | <ul> <li>Rx IMD minimum specification improved after evaluation of production test<br/>fixture (section 8.1.3.2)</li> </ul> | Jun 2010   |

| 11      | Redundant series capacitor deleted and separate capacitors shown for C3 in                                                  | Mar 2010   |

| ''      | Figure 7 and Table 5                                                                                                        | 14101 2010 |

|         | <ul> <li>Extra information on Mixer Output Impedance added (section 7.6).</li> </ul>                                        |            |

|         | Error! Reference source not found. updated.                                                                                 |            |

|         | <ul> <li>Extra information added on IF gain measurement conditions in (section 7.7).</li> </ul>                             |            |

|         | <ul> <li>Extra information added on Rx I/Q Filter, (section 7.10).</li> </ul>                                               |            |

|         | <ul> <li>Extra information added on Tx Filter, (section 7.12).</li> </ul>                                                   |            |

|         | <ul> <li>Maximum limits added for 'Total Current Consumption' figures', (Section</li> </ul>                                 |            |

|         | 8.1.3.1)                                                                                                                    |            |

|         | <ul> <li>LO Leakage performance specification updated; clarification of Note 7 and</li> </ul>                               |            |

|         | 7a; new Note 7b; reference corrected in Note 11; test frequency of 45MHz                                                    |            |

|         | moved from Note 17 to Note 10; Gain of I/Q Filter moved to overall IF                                                       |            |

|         | Amplifier and I/Q Demodulator table (Section 8.1.3.2).                                                                      |            |

| 10      | PLL Phase noise specification corrected and definition added                                                                | Jan 2010   |

|         | I/Q Bandwidth clarified in section 4.2.3.2.                                                                                 |            |

| 9 | VCO specification corrected. It should be 400MHz (max).                   | Nov 2009  |  |  |

|---|---------------------------------------------------------------------------|-----------|--|--|

|   | <ul> <li>dBV/V terminology clarified. It should be dB(V/V)</li> </ul>     |           |  |  |

|   | Clarification of Rx 1st Mixer Input 3rd order Intercept Point measurement |           |  |  |

|   | Correction to C5 in Figure 7, the circuit referenced in IIP3 measurement  |           |  |  |

| 8 | Updated with further application information (e.g. IF VCO options).       | July 2009 |  |  |

| 7 | Updated with enhanced application information.                            | May 2009  |  |  |

| 6 | Original published document for both the CMX991 and CMX992 devices.       | Mar 2009  |  |  |

It is always recommended that you check for the latest product datasheet version from the CML website: <a href="www.cmlmicro.com">www.cmlmicro.com</a>].

### 2 Block Diagrams

Figure 3 CMX991 Block Diagram

Figure 4 CMX992 Block Diagram

### 3 Pin List

| Package<br>Q3<br>Pin No. | Pin Name<br>(CMX991) | Pin Name<br>(CMX992) | Signal<br>Type | Description                                                                                     |

|--------------------------|----------------------|----------------------|----------------|-------------------------------------------------------------------------------------------------|

| 1                        | VCCIF                | VCCIF                | Power          | Supply for IF circuits                                                                          |

|                          |                      |                      | O/P            | CMX991: Tx section positive output                                                              |

| 2                        | TXOUTP               | NC                   | NC             | CMX992: Do not connect to this pin, reserved for future use                                     |

|                          |                      |                      | O/P            | CMX991: Tx section positive output                                                              |

| 3                        | TXOUTN               | NC                   | NC             | CMX992: Do not connect to this pin, reserved for future use                                     |

| 4                        | NC                   | NC                   | NC             | Do not connect to this pin, reserved for future use                                             |

| 5                        | NC                   | NC                   | NC             | Do not connect to this pin, reserved for future use                                             |

|                          |                      |                      | I/P            | CMX991: Tx local oscillator negative input                                                      |

| 6                        | TXLON                | NC                   | NC             | CMX992: Do not connect to this pin, reserved for future use                                     |

| _                        |                      |                      | I/P            | CMX991: Tx local oscillator positive input                                                      |

| 7                        | TXLOP                | NC                   | NC             | CMX992: Do not connect to this pin, reserved for                                                |

| 0                        | MIVININI             | MINIMI               |                | future use                                                                                      |

| 8                        | MIXINN<br>MIXINP     | MIXINN<br>MIXINP     | I/P<br>I/P     | Rx mixer negative input                                                                         |

| 10                       | MIXLON               | MIXLON               | I/P            | Rx mixer positive input Rx mixer local oscillator negative input                                |

| 11                       | MIXLON               | MIXLOP               | I/P            | Rx mixer local oscillator positive input                                                        |

| 12                       | VCCRF                | VCCRF                | Power          | Supply for RF circuits                                                                          |

| 13                       | MIXOUT1              | MIXOUT1              | O/P            | Rx mixer output 1                                                                               |

| 14                       | MIXOUT2              | MIXOUT2              | O/P            | Rx mixer output 2                                                                               |

| 15                       | IFIP1                | IFIP1                | I/P            | Rx IF positive input 1                                                                          |

| 16                       | IFIP2                | IFIP2                | I/P            | Rx IF positive input 2                                                                          |

| 17                       | IFINN                | IFINN                | I/P            | Rx IF negative input                                                                            |

| 18                       | SLI                  | SLI                  | O/P            | Receiver Signal Level Indicator (SLI) output                                                    |

| 19                       | RXQN                 | RXQN                 | O/P            | RxQ negative output                                                                             |

| 20                       | RXQP                 | RXQP                 | O/P            | RxQ positive output                                                                             |

| 21                       | QAMPP                | QAMPP                | I/P            | RxQ amplifier positive input                                                                    |

| 22                       | QAMPN                | QAMPN                | I/P            | RxQ amplifier negative input                                                                    |

| 23                       | QAMPO                | QAMPO                | O/P            | Low IF output or RxQ amp output                                                                 |

| 24                       | RXIN                 | RXIN                 | O/P            | RxI negative output                                                                             |

| 25                       | RXIP                 | RXIP                 | O/P            | RxI positive output                                                                             |

| 26                       | IAMPP                | IAMPP                | I/P            | RxI amplifier positive input                                                                    |

| 27                       | IAMPN                | IAMPN                | I/P            | RxI amplifier negative input                                                                    |

| 28                       | IAMPO                | IAMPO                | O/P            | RxI amplifier output                                                                            |

| 29                       | DGND                 | DGND                 | Power          | Digital ground                                                                                  |

| 30                       | CSN                  | CSN                  | I/P            | C-BUS chip select (active low), used to enable a C-BUS data read or write operation on the chip |

| 31                       | RDATA                | RDATA                | T/S            | C-BUS serial data 3-state output (reply data) to host                                           |

| 32                       | SCLK                 | SCLK                 | I/P            | C-BUS clock input from the host                                                                 |

| 33                       | CDATA                | CDATA                | I/P            | C-BUS serial data input (command data) from the host                                            |

| 34                       | RESETN               | RESETN               | I/P            | C-BUS reset (low for reset condition)                                                           |

| 35                       | DVDD                 | DVDD                 | Power          | Supply to digital circuits                                                                      |

10

| Package<br>Q3<br>Pin No. | Pin Name<br>(CMX991) | Pin Name<br>(CMX992) | Signal<br>Type | Description                                                             |

|--------------------------|----------------------|----------------------|----------------|-------------------------------------------------------------------------|

| 36                       | VDDIO                | VDDIO                | Power          | Supply to C-BUS circuits                                                |

| 37                       | LNAON                | LNAON                | O/P            | Control line to enable/disable Rx LNA                                   |

| 38                       | VCCSYNTH             | VCCSYNTH             | Power          | Supply to IF integer N PLL                                              |

| 39                       | FREF                 | FREF                 | I/P            | Reference frequency input                                               |

| 40                       | DOIF                 | DOIF                 | O/P            | IF PLL charge pump output                                               |

| 41                       | VCOP                 | VCOP                 | I/P            | IF PLL VCO positive input                                               |

| 42                       | VCON                 | VCON                 | I/P            | IF PLL VCO negative input                                               |

| 43                       | VBIAS                | VBIAS                | O/P            | Bandgap generated bias voltage – measurement output                     |

|                          | TVOD                 |                      | I/P            | CMX991: TxQ positive input                                              |

| 44                       | TXQP<br>(Note 2)     | NC                   | NC             | CMX992: Do not connect to this pin, reserved for future use             |

|                          | TXQN                 |                      | I/P            | CMX991: TxQ negative input                                              |

| 45                       | (Note 2)             | NC                   | NC             | CMX992: Do not connect to this pin, reserved for future use             |

|                          |                      |                      | I/P            | CMX991: Txl negative input                                              |

| 46                       | TXIN                 | NC                   | NC             | CMX992: Do not connect to this pin, reserved for future use             |

|                          |                      |                      | I/P            | CMX991: TxI positive input                                              |

| 47                       | TXIP                 | NC                   | NC             | CMX992: Do not connect to this pin, reserved for future use             |

|                          |                      |                      | O/P            | CMX991: Tx IF output                                                    |

| 48                       | TXIFOUT              | NC                   | NC             | CMX992: Do not connect to this pin, reserved for future use             |

| EXPOSED<br>METAL PAD     | AGND                 | AGND                 | Power          | The exposed metal pad must be electrically connected to analogue ground |

Total = 49 Pins (48 pins and central, exposed metal ground pad)

### Table 1 Pin List

### Notes:

1) I/P = Input O/P = Output T/S = 3-state

NC = Not Connected

2) In versions of the datasheet before D/991\_992/13 these pins were incorrectly referenced as pin 44 = TXQN and pin 45 = TXQP causing a spectrum inversion at the modulator output.

### 3.1 Signal Definitions

| Signal Name       | Pins                   | Usage                                                                                                                                                                                                                 |

|-------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $AV_{DD}$         | VCCIF, VCCRF, VCCSYNTH | Power supply for analogue circuits.                                                                                                                                                                                   |

| $DV_DD$           | DVDD                   | Power supply for digital circuits.                                                                                                                                                                                    |

| $V_{DD}IO$        | VDDIO                  | Power supply voltage for digital interface (C-BUS).                                                                                                                                                                   |

| V <sub>BIAS</sub> | VBIAS                  | Bandgap generated bias voltage used as a reference for differential amplifier stages. Decoupling is optional but, if used, a capacitor of >200nF should be connected between V <sub>BIAS</sub> and AV <sub>SS</sub> . |

| DV <sub>SS</sub>  | DGND                   | Ground for digital circuits.                                                                                                                                                                                          |