# PE0402 Evaluation Kit User Manual

UM0402/2 December 2010

# Features

- CMX704x/CMX714x *FirmASIC*<sup>®</sup> product range evaluation

- Serial Flash Option for Function Image<sup>™</sup> with Incircuit Programming

- On-board supply regulators operate from a single 5 volt supply

- Command and control by PC via the PE0002 interface card or user's μC development application or emulator

- 19.2MHz oscillator, 6.144MHz crystal or external clock input to CMX7040

- On-board access to all CMX7040 signals, commands and data

# **1** Brief Description

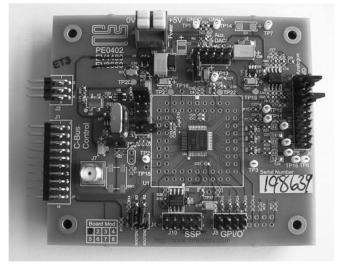

The PE0402 Platform Evaluation Kit is designed to assist in the evaluation and application development of the CMX704x/CMX714x range of *FirmASIC*<sup>®</sup> products. The kit is in the form of a populated PCB comprising a CMX7040 IC and appropriate supporting components and circuitry.

The board also incorporates all of the necessary power-supply regulation facilities for operation from a single 5 volt supply.

The board is fitted with a C-BUS connector allowing the PE0402 to be operated by connection to either of the two C-BUS ports on a CML PE0002 Interface Card, and used with the associated PC GUI software, or by direct connection between the CMX7040 C-BUS and the user's  $\mu$ C development application or emulation system.

The CMX704x Function Image<sup>™</sup> (FI) can be loaded, on power-up, directly into the on-board target IC (CMX7040) using the PE0002 interface or the user's system. Alternatively, it can be automatically loaded from the on-board serial memory, on power-up. In this case, the on-board serial memory has to be pre-loaded with the FI by using a suitable third party programmer or by using the 'Program Serial Memory' tab on the PE0002 GUI software. This software is available from the CML website.

Function images suitable for the CMX704x/CMX714x range of products can be downloaded from the CML Technical Portal.

<sup>© 2010</sup> CML Microsystems Plc

## CONTENTS

| <u>Se</u> | <u>ction</u> | <u> </u>                                                   | Page |

|-----------|--------------|------------------------------------------------------------|------|

| 1         |              | cription                                                   |      |

|           | 1.1 Hi       | story                                                      | 3    |

| 2         | Prelimina    | ry Information                                             | 5    |

|           |              | boratory Equipment                                         |      |

|           |              | andling Precautions                                        |      |

|           | 2.2.1        | Static Protection                                          |      |

|           | 2.2.2        | Contents - Unpacking                                       | 5    |

|           | 2.3 Ap       | pprovals                                                   |      |

| ~         |              | -4                                                         | ~    |

| 3         |              | rt                                                         |      |

|           |              | ith PE0002                                                 |      |

|           | 3.1.1        | Setting-Up                                                 |      |

|           | 3.1.2        | Operation                                                  |      |

|           | 3.2 W        | ithout PE0002                                              | /    |

| 4         | Signal Lis   | sts                                                        | 8    |

| •         | e.gae        |                                                            |      |

| 5         | Circuit Sc   | hematics and Board Layouts                                 | 12   |

| 6         | Detailed D   | Description                                                | .13  |

|           |              | ardware Description                                        |      |

|           | 6.1.1        | Power Supplies                                             |      |

|           | 6.1.2        | Clock Options                                              |      |

|           | 6.1.3        | Control Interface                                          |      |

|           | 6.1.4        | Serial Memory                                              |      |

|           | 6.1.5        | Baseband Interfacing                                       |      |

|           | 6.1.6        | Digital Interfacing                                        |      |

|           |              | ljustments and Controls                                    |      |

|           |              | inction Image <sup>™</sup>                                 |      |

|           | 6.3.1        | Load Function Image <sup>™</sup> via C-BUS                 | .15  |

|           | 6.3.2        | Load Function Image <sup>™</sup> from Serial Memory Device | .16  |

|           | 6.3.3        | Program Serial Memory                                      | .17  |

|           | 6.4 Ev       | /aluation Tests                                            |      |

|           | 6.4.1        | Write to and Read from a Register                          | .19  |

|           | 6.4.2        | Check Analogue Path and Set Input Gain                     | 19   |

|           | 6.4.3        | Check Analogue Path and Set Output Gain                    | 20   |

|           | 6.4.4        | Generate Two External Digital Clocks                       | 20   |

|           | 6.5 Tr       | oubleshooting                                              | .21  |

|           | 6.5.1        | Modification State                                         | 21   |

| 7         | Performa     | nce Specification                                          | .22  |

| -         |              | ectrical Performance                                       |      |

|           | 7.1.1        | Absolute Maximum Ratings                                   |      |

|           | 7.1.2        | Operating Limits                                           |      |

|           | 7.1.2        | Operating Characteristics                                  |      |

|           | 7.1.4        | Operating Characteristics - Timing Diagrams                |      |

|           |              |                                                            |      |

2

#### Page

| Table                                                               | Page |

|---------------------------------------------------------------------|------|

| Table 1 – Signal List                                               | 9    |

| Table 2 – Test Points                                               | 10   |

| Table 3 – Jumpers                                                   | 11   |

| Table 4 – LEDs                                                      | 11   |

| Table 5 – Clock Select Jumper Positions                             | 13   |

| Table 6 – Serial Memory Types                                       | 17   |

| Table 7 – CMX7040 Register Settings - Analogue Path and Input Gain  | 19   |

| Table 8 – CMX7040 Register Settings - Analogue Path and Output Gain | 20   |

| Table 9 – CMX7040 Register Settings - External Digital Clocks       | 20   |

|                                                                     |      |

### Fi

| Figure                                                   | Page |

|----------------------------------------------------------|------|

| Figure 1 – Block Diagram                                 | 4    |

| Figure 2 – PE0402 used with PE0002                       | 6    |

| Figure 3 – PCB Layout: Top                               | 12   |

| Figure 4 – Function Image™ Load Tab – via C-BUS          | 15   |

| Figure 5 – Function Image™ Load Tab – from Serial Memory | 16   |

| Figure 6 – Program Serial Memory Tab                     | 17   |

| Figure 7 – Thick Stub Loaded Message Box                 | 18   |

| Figure 8 – Program Serial Memory Complete Message Box    | 18   |

| Figure 9 – Examples of Mod State Identification          | 21   |

It is always recommended that you check for the latest product datasheet version from the Datasheets page of the CML website: [www.cmlmicro.com].

#### 1.1 History

| Version | Changes                                                                               | Date                    |

|---------|---------------------------------------------------------------------------------------|-------------------------|

|         |                                                                                       |                         |

| 2       | Covers two types of serial memory used – dependant upon mod state and serial numbers. | 9 <sup>th</sup> Dec '10 |

| 1       | Original document.                                                                    | 28th Aug '09            |

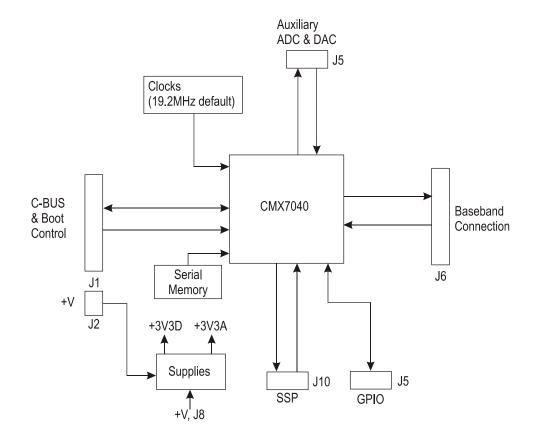

Figure 1 – Block Diagram

$\ensuremath{\textcircled{}^{\circ}}$  2010 CML Microsystems PIc

4

The PE0402 is designed to support the CMX704x/CMX714x range of *FirmASIC*<sup>®</sup> devices using their respective Function Image<sup>TM</sup>.

The CMX7040 IC fitted to the PE0402 is a special evaluation IC with the architecture of all CMX704x/CMX714x series ICs. The functionality of this evaluation IC is obtained from the relevant Function Image<sup>TM</sup> (FI); evaluation FIs are downloaded from the CML Technical Portal. Each Function Image<sup>TM</sup> can represent a different set of features.

# 2.1 Laboratory Equipment

The following laboratory equipment is needed to use this evaluation kit:

A 5 Volt dc regulated power supply.

If the PE0402 is being used with the PE0002 Interface Card, the following items will also be required:

1. An IBM compatible PC with the following requirements:

- One of the following Windows operating systems installed: 2000sp4 or XPsp2.

- USB port.

- Minimum screen resolution 800 x 600. Recommended resolution 1024 x 768.

- 2. A USB type A male to mini B male cable.

- 3. Software application ES000230.exe, or later version, installed on the PC.

# 2.2 Handling Precautions

Like most evaluation kits, this product is designed for use in office and laboratory environments. The following practices will help ensure its proper operation.

#### 2.2.1 Static Protection

This product uses low power CMOS circuits that can be damaged by electrostatic discharge. Partially damaged circuits can function erroneously, leading to misleading results. Observe ESD precautions at all times when handling this product.

#### 2.2.2 Contents - Unpacking

Please ensure that you have received all of the items on the separate information sheet (EK0402) and notify CML within 7 working days if the delivery is incomplete.

# 2.3 Approvals

This product is not approved to any EMC or other regulatory standard. Users are advised to observe local statutory requirements, which may apply to this product.

PE0402

This section is divided into two sub-sections. The first is for those users who are using the PE0402 with a PE0002 controller card and its Windows PC GUI software. The second is for users who are using the PE0402 by itself, without a PE0002.

# 3.1 With PE0002

Note that the C-BUS connector J1 and the power connector J2 are both right angle headers and are designed to plug directly into sockets J5 (C-BUS 1 port) and J9 respectively, or sockets J3 (C-BUS 2 port) and J7 respectively, of a PE0002.

### 3.1.1 Setting-Up

- Refer to the PE0002 user manual, and follow the instructions given in the quick start section.

- Ensure the jumpers on J4 are open circuit. The BootEn1 and BootEn2 signals are driven from the PE0002.

The basic arrangement, when used with the PE0002 is shown below:

Figure 2 – PE0402 used with PE0002

## 3.1.2 Operation

The Function Image<sup>TM</sup> (FI) must now be loaded into the CMX7040 device. A FI is provided as a 'C' type header file and must be obtained from the CML Project Resource Portal. There are two methods available for loading the FI:

1. Directly from a file on the PE0002 host PC to the CMX7040.

From the on-board PE0402 serial memory. To use this method the serial memory must first be programmed with the FI by using the 'Program Serial Memory' tab on the PE0002 GUI software.

The PE0402 should now be ready for evaluation of the CMX7040 with the chosen FI.

# 3.2 Without PE0002

As an alternative to using the PE0002 controller kit, users may control the CMX7040 target device with a user-supplied host controller card. C-BUS connections are made via connector J1.

The power-up, or boot state of the CMX7040 BOOTEN1 and BOOTEN2 pins may be set using jumpers on header, J4. Consult the relevant CMX704x/CMX714x documentation for valid modes. A jumper in-circuit on header, J4, corresponds to a '0' state on the boot pins. Alternatively the state of these pins may be set via the connector, J1, pins 13 and 14. By default,  $47k\Omega$  pullup resistors on the PE0402 board provide a '1' state on each of the two BOOTEN pins.

A FI for the CMX7040 device must be either included in the customer's host system and loaded into the CMX7040 device on power-up or programmed into the on-board serial memory following the guidelines in the application note: 'Writing a Function Image<sup>TM</sup> to Serial Memory'.

# 4 Signal Lists

| CONNECTOR PINOUT  |                           |         |     |                                                      |  |  |

|-------------------|---------------------------|---------|-----|------------------------------------------------------|--|--|

| Connector<br>Ref. | Connector<br>Pin No.      | 5       |     | Description                                          |  |  |

| J1                | 1, 3, 5, 7,<br>9, 15 to18 | N/C     | -   |                                                      |  |  |

|                   | 2                         | CSN     | I/P | Chip select. Connects to host $\mu$ C.               |  |  |

|                   | 4                         | CDATA   | I/P | Serial Data input. Connects to host $\mu$ C.         |  |  |

|                   | 6                         | SCLK    | I/P | Serial clock input. Connects to host $\mu$ C.        |  |  |

|                   | 8                         | RDATA   | O/P | Serial data output. Connects to host $\mu$ C.        |  |  |

|                   | 10                        | IRQN    | O/P | Interrupt request. Connects to host $\mu$ C.         |  |  |

|                   | 11, 12                    | GNDD    | PWR | Digital supply ground.                               |  |  |

|                   | 13                        | BOOTEN1 | I/P | CMX7040 Hardware Boot Control.                       |  |  |

|                   | 14                        | BOOTEN2 | I/P | CMX7040 Hardware Boot Control.                       |  |  |

|                   | 19, 20                    | +3V3D   | PWR | 3.3V dc digital supply rail.                         |  |  |

| J2                | 1, 2                      | GNDD    | PWR | Digital supply ground.                               |  |  |

|                   | 3 to 6                    | +V      | PWR | External supply voltage – Daisy chained from PE0002. |  |  |

| J3                | 1                         | GPIO1   | BI  | General purpose I/O pin.                             |  |  |

|                   | 3                         | GPIO2   | BI  | General purpose I/O pin.                             |  |  |

|                   | 5                         | GPIOA   | BI  | General purpose I/O pin.                             |  |  |

|                   | 7                         | GPIOB   | BI  | General purpose I/O pin.                             |  |  |

|                   | 2, 4, 6, 8                | GNDD    | PWR | Digital supply ground.                               |  |  |

| J5                | 1                         | AUXADC4 | I/P | Auxiliary ADC input.                                 |  |  |

|                   | 2                         | AUXDAC1 | O/P | Auxiliary DAC output.                                |  |  |

|                   | 3                         | AUXADC3 | I/P | Auxiliary ADC input.                                 |  |  |

|                   | 4                         | AUXDAC2 | O/P | Auxiliary DAC output.                                |  |  |

|                   | 5                         | AUXADC2 | I/P | Auxiliary ADC input.                                 |  |  |

|                   | 6                         | AUXDAC3 | O/P | Auxiliary DAC output.                                |  |  |

|                   | 7                         | AUXADC1 | I/P | Auxiliary ADC input.                                 |  |  |

|                   | 8                         | AUXDAC4 | O/P | Auxiliary DAC output.                                |  |  |

|                   | 9, 10                     | GNDA    | PWR | Analogue supply ground.                              |  |  |

| co                               | CONNECTOR PINOUT                         |                |                            |                                          |  |  |  |

|----------------------------------|------------------------------------------|----------------|----------------------------|------------------------------------------|--|--|--|

| Connector Connector Ref. Pin No. |                                          | Signal<br>Name | Signal<br>Type             | Description                              |  |  |  |

| J6                               | 1                                        | IP1            | I/P                        | Channel 1 inverting input.               |  |  |  |

|                                  | 3                                        | IP2            | I/P                        | Channel 2 inverting input.               |  |  |  |

|                                  | 5                                        | IP3            | I/P                        | Channel 3 inverting input.               |  |  |  |

|                                  | 7                                        | MOD1           | O/P                        | Channel 1 output.                        |  |  |  |

|                                  | 9                                        | MOD2           | O/P                        | Channel 2 output.                        |  |  |  |

|                                  | 11                                       | AUDIO          | O/P                        | Channel 3 output.                        |  |  |  |

|                                  | 13                                       | BUF1IN         | I/P                        | High impedance buffered input.           |  |  |  |

|                                  | 15                                       | BUF1OUT        | O/P                        | Buffered output.                         |  |  |  |

|                                  | 17                                       | BUF2IN         | I/P                        | High impedance buffered input.           |  |  |  |

|                                  | 19                                       | BUF2OUT        | F2OUT O/P Buffered output. |                                          |  |  |  |

|                                  | 2, 4, 6, 8,<br>10, 12, 14,<br>16, 18, 20 | GNDA           | PWR                        | Analogue supply ground.                  |  |  |  |

| J7                               |                                          | CLK EXT        | I/P                        | External input option for CMX7040 clock. |  |  |  |

| J8                               |                                          | +V             | PWR                        | External supply voltage.                 |  |  |  |

|                                  |                                          | 0V             | PWR                        | External supply ground.                  |  |  |  |

| J10                              | 1                                        | SSOUT/<br>FSO  | BI                         | SSP Frame sync.                          |  |  |  |

|                                  | 3                                        | MOSI           | O/P                        | SSP Master output, slave input.          |  |  |  |

|                                  | 5                                        | MISO           | I/P                        | SSP Master input, slave output.          |  |  |  |

|                                  | 7                                        | SSPCLK         | BI                         | SSP Clock.                               |  |  |  |

|                                  | 2, 4, 6, 8                               | N/C            | -                          |                                          |  |  |  |

|                                  | 9, 10                                    | GNDD           | PWR                        | Digital supply ground.                   |  |  |  |

|                                  |                                          |                |                            |                                          |  |  |  |

Table 1 – Signal List

$\ensuremath{\textcircled{}^{\odot}}$  2010 CML Microsystems PIc

| -                                          | TEST POINTS |                                                                            |  |  |  |

|--------------------------------------------|-------------|----------------------------------------------------------------------------|--|--|--|

| Test Point Default<br>Ref. Measuremen<br>t |             | Description                                                                |  |  |  |

| TP2                                        | 0V          | Loop – CMX7040 system clock 2 output.                                      |  |  |  |

| TP3                                        | 0V          | Loop – CMX7040 system clock 1 output.                                      |  |  |  |

| TP5                                        | 0V          | Loop – GNDD, digital ground.                                               |  |  |  |

| TP6                                        | 0V          | Loop – GNDA, analogue ground.                                              |  |  |  |

| TP7                                        | 0V          | Loop – GNDA, analogue ground.                                              |  |  |  |

| TP8                                        | -           | Loop – IP1 - Channel 1 inverting input.                                    |  |  |  |

| TP9                                        | -           | Loop – IP2 - Channel 2 inverting input.                                    |  |  |  |

| TP10                                       | -           | Loop – IP3 - Channel 3 inverting input.                                    |  |  |  |

| TP11                                       | HiZ         | Loop – MOD1 - Channel 1 output.                                            |  |  |  |

| TP12                                       | HiZ         | Loop – MOD2 - Channel 2 output.                                            |  |  |  |

| TP13                                       | HiZ         | Loop – Audio - Channel 3 output.                                           |  |  |  |

| TP14                                       | 0V          | Loop – GNDA, analogue ground.                                              |  |  |  |

| TP15                                       | 0V          | Loop – GNDA, analogue ground.                                              |  |  |  |

| TP19                                       | 3.3V        | Pad – Output from on-board regulator. DC supply voltage for analogue rail. |  |  |  |

| TP20                                       | 3.3V        | Pad – Output from on-board regulator. DC supply voltage for digital rail.  |  |  |  |

| TP21                                       | 2.5V        | Pad – CMX7040 internally generated voltage.                                |  |  |  |

| TP22                                       | 0V          | Pad – CMX7040 VBIAS.                                                       |  |  |  |

Table 2 – Test Points

$\ensuremath{\textcircled{}^{\odot}}$  2010 CML Microsystems PIc

Link

Ref.

JUMPERS

Positions

Default

Position

| Description                              |

|------------------------------------------|

| •                                        |

| plates digital supply rail from CMX7040. |

| lates analogue supply rail from CMX7040. |

| JP1 | 1-2   | Short | Isolates digital supply rail from CMX7040.               |  |

|-----|-------|-------|----------------------------------------------------------|--|

| JP2 | 1-2   | Short | Isolates analogue supply rail from CMX7040.              |  |

|     |       |       |                                                          |  |

| J4  | 1-2   | Open  | Manual BootEn1 control (short = LO).                     |  |

|     | 3-4   | Open  | Manual BootEn2 control (short = LO).                     |  |

|     |       |       |                                                          |  |

| J9  | 1-2   | Short | 19.2MHz oscillator clock source.                         |  |

|     | 3-4   | Open  | External clock source.                                   |  |

|     | 5-6   | Open  | Crystal clock source – if components fitted by customer. |  |

|     | 7-8   | Short | Ground external clock input.                             |  |

|     | 9-10  | Open  | Crystal clock source – if components fitted by customer. |  |

|     |       |       |                                                          |  |

| J6  | 13-14 | Short | Ground input to uncommitted buffer1.                     |  |

|     | 17-18 | Short | Ground input to uncommitted buffer2.                     |  |

|     |       |       |                                                          |  |

# Table 3 – Jumpers

| LEDs     |                                                       |  |  |  |

|----------|-------------------------------------------------------|--|--|--|

| LED Ref. | Description                                           |  |  |  |

| D2       | Indicates that the digital supply voltage is present. |  |  |  |

# Table 4 – LEDs

| BI<br>HiZ<br>I/P<br>N/C<br>O/P | =<br>=<br>=<br>= | Bidirectional<br>High impedance<br>Input<br>Not connected |

|--------------------------------|------------------|-----------------------------------------------------------|

| O/P                            | =                | Output                                                    |

| PWR                            | =                | Power supply connection                                   |

$\ensuremath{\textcircled{}^{\odot}}$  2010 CML Microsystems Plc

Notes:

# 5 Circuit Schematics and Board Layouts

For clarity, circuit schematics are available as separate high-resolution files. These can be obtained via the CML website.

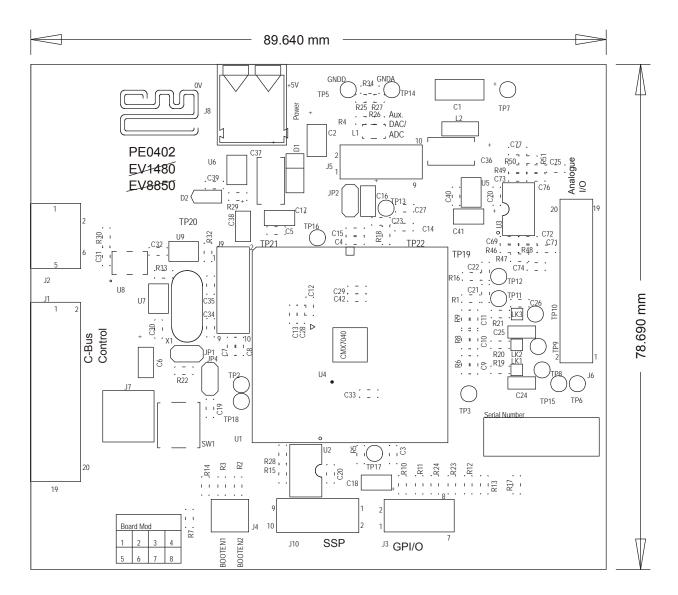

Figure 3 – PCB Layout: Top

# 6 Detailed Description

## 6.1 Hardware Description

The PE0402 as shipped may not have the optimum configuration or component values for all function images. Check the PE0402 schematic against recommendations in the specific CMX704x/CMX714x datasheet.

#### 6.1.1 Power Supplies

The board is fitted with two voltage regulators. U5 and U6 provide the analogue and digital supply rails respectively. The input to these two regulators should be provided by an external 5V dc regulated power supply, which can be daisy chained from the PE0002 or connected to the board via connector J8, a push type connector.

The analogue and digital supply voltage levels can be monitored on test points TP19 and TP20 respectively.

LED illumination confirms the on-board presence of the +3.3V dc digital voltage supply.

#### 6.1.2 Clock Options

The PCB is designed to provide three CMX7040 device clock options. The board is supplied with a 19.2MHz oscillator module fitted. This option allows convenient RF synthesiser configuration to typical channel spacings.

Other options are an external clock source at J7 or a 6.144MHz quartz crystal oscillator circuit (C34, C35 and X1).

Header J9 is used with jumper sockets to select the required option as shown in the table below. Shaded cells illustrate locations where a jumper socket should be fitted.

| J4       | Clock Option |          |                |  |  |

|----------|--------------|----------|----------------|--|--|

| Jumper   | 19.2MHz TCXO | External | Quartz crystal |  |  |

| Position | (default)    |          | -              |  |  |

| 1-2      |              |          |                |  |  |

| 3-4      |              |          |                |  |  |

| 5-6      |              |          |                |  |  |

| 7-8      |              |          |                |  |  |

| 9-10     |              |          |                |  |  |

Table 5 – Clock Select Jumper Positions

#### 6.1.3 Control Interface

The C-BUS and CMX7040 boot control signals are brought out on connector J1. This is a right angle male header designed to plug directly into the PE0002 interface card that has a matching female header.

Alternatively, if not using the PE0002, the CMX7040 boot control signals can be manually set with jumpers on header J4.

#### 6.1.4 Serial Memory

The serial memory, U2, can be used for non-volatile storage of a Function Image<sup>™</sup>. The PE0402 is shipped with a blank serial memory.

#### 6.1.5 Baseband Interfacing

Connector J5 provides access to Auxiliary ADCs 1 to 4 and Auxiliary DACs 1 to 4 of the CMX7040 device.

The CMX7040 device baseband input amplifiers for IP1, IP2 and IP3 are configured as ac coupled, unity gain, inverting amplifiers. The inputs to these circuits are fed from connector J6.

The CMX7040 device baseband outputs, MOD1, MOD2 and AUDIO, are fed through an RC network to connector J6.

A dual op amp IC is fitted to the board, with both amplifiers configured as unity-gain buffers. It is possible to set up other op amp based configurations with the addition of passive components to the PCB footprints provided. It is recommended that 0603 sized surface mount components be used. Access to the input and output of each of these uncommitted amplifiers is also from connector J6.

#### 6.1.6 Digital Interfacing

Connector J3 provides access to four general purpose I/O lines.

Connector J10 provides access to a synchronous serial port.

Use of these signals is Function Image<sup>TM</sup> dependant. In some cases they will have no function. See relevant CMX704x/CMX714x documentation.

## 6.2 Adjustments and Controls

The boot state of the CMX7040 device can be set manually, using jumpers on header, J4. If using with the PE0002, the jumpers should be left open circuit.

# 6.3 Function Image<sup>™</sup>

There are two methods by which a FI may be loaded into the CMX7040 device.

Whenever power is removed from the PE0402 the FI data will be erased from the CMX7040 device. Therefore, whenever power is applied a FI must be loaded, either from the serial memory or via the C-BUS interface.

If the PE0402 is used with the PE0002 PC interface, function images can be loaded as described in sections 6.3.1, 6.3.2 and 6.3.3.

# 6.3.1 Load Function Image<sup>™</sup> via C-BUS

Use the Function Image<sup>™</sup> Load tab. Select Function Image<sup>™</sup> Source: 'C-BUS'.

- Enter the name of the file containing the Function Image<sup>™</sup>, or navigate to the required file using the 'Browse' button.

- Enter the activation code in the lower edit box. Alternatively select one of two previously used codes in the drop down list.

- Select Target Board.

- Click the "Load" button. The progress of the download is shown visually on the progress bar and when the download has completed a message box will be displayed indicating if the result of the download operation was successful or not.

| Target Device Setup and Operation                                                                                | X |

|------------------------------------------------------------------------------------------------------------------|---|

| C-BUS Control   C-BUS Ctrl Ext.1   C-BUS Ctrl Ext.2 Function Image Load   Program Serial Memory   Script Handler |   |

| Select Function Image Source                                                                                     |   |

| CBUS (Load Function Image from PC)                                                                               |   |

| Serial Memory (Load Function Image from on board memory)                                                         |   |

|                                                                                                                  |   |

| Function Image Browse                                                                                            |   |

| Block 1 Checksum                                                                                                 |   |

| Block 2 Checksum                                                                                                 |   |

| Activation Code                                                                                                  |   |

| Select Target Board                                                                                              |   |

| C-BUS Header 1                                                                                                   |   |

| C C-BUS Header 2                                                                                                 |   |

| Load Function Image                                                                                              |   |

| Load                                                                                                             |   |

|                                                                                                                  |   |

| Close                                                                                                            |   |

Figure 4 – Function Image<sup>™</sup> Load Tab – via C-BUS

<sup>© 2010</sup> CML Microsystems Plc

## 6.3.2 Load Function Image<sup>™</sup> from Serial Memory Device

It is assumed that the serial memory has been programmed with the Function Image<sup>™</sup> prior to using this load method. This can be carried out with the serial memory in circuit using the ES0002xx 'Program Serial Memory' tab.

Use the Function Image<sup>™</sup> Load tab. Select Function Image<sup>™</sup> Source: 'Serial Memory'.

- Enter the block 1 and block 2 checksum values in the edit boxes. Alternatively select one of two previously used values in the drop down list for each block.

- Enter the activation code in the lower edit box. Alternatively select one of two previously used codes in the drop down list.

- Select Target Board.

- Click the 'Load' button. The progress of the download is shown visually on the progress bar and when the download has completed a message box will be displayed indicating if the result of the download operation was successful or not.

| 🛎 Target Device Setup and Operation                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C-BUS Control C-BUS Ctrl Ext.1 C-BUS Ctrl Ext.2 Function Image Load Program Serial Memory Script Handler<br>Select Function Image Source<br>C C-BUS (Load Function Image from PC)<br>Serial Memory (Load Function Image from on board memory) |

| Function Image     Browse       Block 1 Checksum     Image       Block 2 Checksum     Image       Activation Code     Image                                                                                                                   |

| Select Target Board<br>C-BUS Header 1<br>C-BUS Header 2                                                                                                                                                                                       |

| Load Function Image Load                                                                                                                                                                                                                      |

Figure 5 – Function Image<sup>™</sup> Load Tab – from Serial Memory

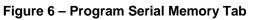

#### 6.3.3 Program Serial Memory

The specific serial memory device fitted to the PE0402 and the appropriate "thick stub" application software are shown below. The "thick stub" application software is available from the CML Technical Portal.

| Revision           | Serial       | Memory type               | Thick Stub          |

|--------------------|--------------|---------------------------|---------------------|

|                    | numbers      |                           |                     |

| Up to Rev B Mod 2* | Up to 198841 | Atmel AT25F512A           | FI_FLASH_xx.h       |

| From Rev B Mod 3*  |              | ST M25P10A or equivalent. | EF0402_M25P10A_xx.h |

#### Table 6 – Serial Memory Types

\* For correct identification of mod state (modification state) see section 6.5.1

Use the 'Program Serial Memory' tab:

- Enter the name of the file containing the thick stub, or navigate to the required file using the 'Browse' button. This file is in the same 'C' language header format as the Function Image<sup>™</sup>.

- Enter the name of the file containing the Function Image<sup>™</sup>, or navigate to the required file using the 'Browse' button.

- Enter, in units of MHz, the crystal/clock input frequency of the CMX7040 device. The default is 19.2MHz. The 'Clk. Divide Setting' is dependent on the entered frequency value and is calculated by the software, requiring no intervention from the user.

- Select Target Board.

- Click the 'Load' button.

| Target Device Setup and Operation                                                               |                |

|-------------------------------------------------------------------------------------------------|----------------|

| C-BUS Control   C-BUS Ctrl Ext.1   C-BUS Ctrl Ext.2   Function Image Load Program Serial Memory | Script Handler |

| Select Function Image Source                                                                    |                |

| Thick Stub Browse                                                                               |                |

| Function Image Browse                                                                           |                |

| Frequency (MHz) 19.2                                                                            |                |

| Clk. Divide Setting E0C8                                                                        |                |

|                                                                                                 |                |

|                                                                                                 |                |

|                                                                                                 |                |

| Select Target Board     C-BUS Header 1                                                          |                |

| C-BUS Header 1                                                                                  |                |

|                                                                                                 |                |

| Program Serial Memory                                                                           |                |

| Load                                                                                            |                |

|                                                                                                 |                |

|                                                                                                 | Close          |

© 2010 CML Microsystems Plc

Shortly after pressing the Load button, a message box will confirm that the application has loaded the Thick Stub.

Figure 7 – Thick Stub Loaded Message Box

Click on the message box OK button and the application will proceed to programme the Function Image<sup>™</sup> into the serial memory on the PE0402 card. Progress is shown visually on the progress bar. When programming is complete a message box will be displayed indicating if the operation was successful or not.

| Program | Serial Memory                | ×   |

|---------|------------------------------|-----|

| (į)     | Program Serial Memory comple | ete |

|         | OK                           |     |

Figure 8 – Program Serial Memory Complete Message Box

# 6.4 Evaluation Tests

Before a Function Image<sup>™</sup> is loaded into the CMX7040 device; there is a limited functionality that can be demonstrated directly by programming the C-BUS registers. The following examples can be used to verify control of the CMX7040 via the C-BUS interface. These registers can be programmed using the 'C-BUS Control' tab in the PE0002 software.

#### 6.4.1 Write to and Read from a Register

- Write any 16-bit number to register \$C0.

The data transferred to the device on the Command Data pin looks like this:

{C0} { <ms byte> } { <ls byte> }

..... Command Data

- The value written to this register (the Powerdown Control register) can be read back from register \$C4 by issuing a single command byte, then reading two data bytes from the Reply Data pin, as follows:

{ C4 }

{ <ms byte> } { <ls byte> }

..... Command Data ..... Reply Data

Note that the power consumption of the device will increase once this register has been written to, since some parts of the device will no longer be powersaved.

## 6.4.2 Check Analogue Path and Set Input Gain

Configure the CMX7040 with the C-BUS register data given in Table 7.

|            | C-BUS Register |                               |  |

|------------|----------------|-------------------------------|--|

| Write Data | Address        | Name                          |  |

| \$5061     | \$C0           | Powerdown Control             |  |

| \$770F     | \$B0           | Analogue Gain                 |  |

| \$0830     | \$B1           | Input Gain and Signal Routing |  |

| \$0008     | \$CF           | Test Mode                     |  |

Table 7 – CMX7040 Register Settings - Analogue Path and Input Gain

Apply a 1kHz, audio signal to the input, IP3 (J6 pin 5 or TP10), at a level of -10dBm (the maximum signal level before distortion is about +1dBm).

Check the audio signal coming out of the AUDIO OUT pin (TP13). The level should be nominally 6.4dB, above the level of the input signal.

6.4.3

Configure the CMX7040 with the C-BUS register data given in Table 8.

|            | C-BUS Register |                   |  |

|------------|----------------|-------------------|--|

| Write Data | Address        | Name              |  |

| \$A3E1     | \$C0           | Powerdown Control |  |

| \$650C     | \$B0           | Analogue Gain     |  |

| \$0001     | \$CF           | Test Mode         |  |

Table 8 – CMX7040 Register Settings - Analogue Path and Output Gain

Apply a differential 1kHz, audio signal across the inputs, IP1 (J6, pin 1 or TP8) and IP2 (J6, pin 2 or TP9), at a level of 0dBm between them.

Check the audio signal coming out of the AUDIO OUT pin (TP13). The level should be –9.2dBm.

Check the audio signal coming out of the MOD1 pin (J6, pin 7 or TP11). The level should be -8.0dBm.

Check the audio signal coming out of the MOD2 pin (J6, pin 9 or TP12). The level should be -10.0dBm.

The MOD1 and MOD2 outputs should have a DC bias level of approximately 1.65 volts.

## 6.4.4 Generate Two External Digital Clocks

Configure the CMX7040 with the C-BUS register data given in Table 9.

|            | C-BUS Re | gister                                            |

|------------|----------|---------------------------------------------------|

| Write Data | Address  | Name                                              |

| \$0021     | \$C0     | Powerdown Control                                 |

| \$1900     | \$AB     | System Clock 1 PLL Configuration                  |

| \$E0C8     | \$AC     | System Clock 1 Reference and Source Configuration |

| \$0E00     | \$AD     | System Clock 2 PLL Configuration                  |

| \$E6C8     | \$AE     | System Clock 2 Reference and Source Configuration |

#### Table 9 – CMX7040 Register Settings - External Digital Clocks

With the default 19,2MHz clock input, a digital clock frequency of 4.096MHz should be observed at the system clock 1 output (TP3) and a frequency of 16.384MHz should be observed at the system clock 2 output (TP2).

Now write 0xC0C8 to either \$AC or \$AE registers, to turn off the system clock 1 or system clock 2 outputs, respectively.

PE0402

# 6.5 Troubleshooting

After loading a Function Image<sup>™</sup> the ES0002xx application writes the activation code that has been typed into the Activation Code edit box to the CMX7040 device. If this code is incorrect for the Function Image<sup>™</sup> that has just been loaded the CMX7040 device will lock up and will not respond to further input from the ES0002xx application. It is recoverable only by closing the ES0002xx application, power cycling the PE0402 and PE0002 cards, and then restarting the application. Keep the power off for at least 10 seconds during this process.

#### 6.5.1 Modification State

The modification state (mod state) of the PE0402 can be determined from the 'Board Mod' box printed on the PCB silkscreen. The highest number in the box that is blacked out gives the mod state. The following examples indicate a mod state of 3.

| E | Board | d Moo | t |   | Board | d Mo |

|---|-------|-------|---|---|-------|------|

| ٠ | ٠     | ٠     | 4 | 3 |       |      |

| 5 | 6     | 7     | 8 | 5 | 6     | 7    |

Figure 9 – Examples of Mod State Identification

# 7 Performance Specification

# 7.1 Electrical Performance

#### 7.1.1 Absolute Maximum Ratings

Exceeding these maximum ratings can result in damage to the Evaluation Kit.

|                                                    | Min. | Max.  | Units |

|----------------------------------------------------|------|-------|-------|

| Supply (+V – 0V)                                   | -0.3 | 9.0   | V     |

| Voltage on any connector pin to V <sub>SS</sub>    | -0.3 | 3.6   | V     |

| Current into or out of +V and V <sub>SS</sub> pins | 0    | +0.45 | А     |

| Current into or out of any other connector pin     | -20  | +20   | mA    |

### 7.1.2 Operating Limits

\_

Correct operation of the Evaluation Kit outside these limits is not implied.

|                          | Notes | Min. | Max.   | Units |

|--------------------------|-------|------|--------|-------|

| Supply $(+V - 0V)$       |       | 4.5  | 5.5    | V     |

| External Clock Frequency |       | 3.0  | 24.576 | MHz   |

#### 7.1.3 Operating Characteristics

For the following conditions unless otherwise specified:

Evaluation Device Clock Frequency = 19.2MHz, +V = 5.0V, Tamb = +25°C.

For CMX7040 parameters, see relevant CMX704x/CMX714x data sheet.

|                      | Notes | Min. | Тур. | Max. | Units |

|----------------------|-------|------|------|------|-------|

| DC Parameters        |       |      |      |      |       |

| I <sub>DD</sub>      | 1, 2  | -    | 15   | -    | mA    |

| +3V3A                |       | 3.15 | 3.3  | 3.45 | V     |

| +3V3D                |       | 3.15 | 3.3  | 3.45 | V     |

| Analogue Parameters  |       |      |      |      |       |

| Output Impedances    |       |      |      |      |       |

| Mod1, Mod2 and Audio | 3     | -    | 100  | -    | kΩ    |

| Buf1out and Buf2out  | 4     | -    | 0.1  | -    | Ω     |

| Input Impedances     |       |      |      |      |       |

| IP1, IP2 and IP3     |       | -    | 50   | -    | kΩ    |

| Buf1in and Buf2in    | 4     | 1    | -    | -    | MΩ    |

| External Clock Input |       |      |      |      |       |

| 'High' pulse width   |       | 21   | -    | -    | ns    |

| 'Low' pulse width    |       | 21   | -    | -    | ns    |

| Input impedance      |       | 10   | -    | -    | MΩ    |

1. PCB current consumption, not current consumption of the CMX7040.

2. Not including any current drawn from pins by external circuitry.

3. Small signal impedance.

4. When configured, as supplied, as unity gain buffers.

$\ensuremath{\textcircled{}^{\circ}}$  2010 CML Microsystems PIc

Notes:

# 7.1.4 Operating Characteristics - Timing Diagrams

Please refer to relevant CMX704x/CMX714x Datasheet for details.

#### About FirmASIC®

CML's proprietary *FirmASIC*® component technology reduces cost, time to market and development risk, with increased flexibility for the designer and end application. *FirmASIC*® combines Analogue, Digital, Firmware and Memory technologies in a single silicon platform that can be focused to deliver the right feature mix, performance and price for a target application family. Specific functions of a *FirmASIC*® device are determined by uploading its Function Image™ during device initialization. New function images may be later provided to supplement and enhance device functions, expanding or modifying end-product features without the need for expensive and time-consuming design changes. *FirmASIC*® devices provide significant time to market and commercial benefits over Custom ASIC, Structured ASIC, FPGA and DSP solutions. They may also be exclusively customised where security or intellectual property issues prevent the use of Application Specific Standard Products (ASSP's).

CML does not assume any responsibility for the use of any circuitry described. No IPR or circuit patent licences are implied. CML reserves the right at any time without notice to change the said circuitry and any part of this product specification. Evaluation kits and demonstration boards are supplied for the sole purpose of demonstrating the operation of CML products and are supplied without warranty. They are intended for use in a laboratory environment only and are not for re-sale, end-use or incorporation into other equipments. Operation of these kits and boards outside a laboratory environment is not permitted within the European Community. All software/firmware is supplied "as is" and is without warranty. It forms part of the product supplied and is licensed for use only with this product, for the purpose of demonstrating the operation of CML products. Whilst all reasonable efforts are made to ensure that software/firmware contained in this product is virus free, CML accepts no responsibility whatsoever for any contamination which results from using this product and the onus for checking that the software/firmware is virus free is placed on the purchaser of this evaluation kit or development board.

| CML Microcircuits<br>(UK) Ltd<br>COMMUNICATION SEMICONDUCTORS                                                                         | CML Microcircuits<br>(USA) Inc.<br>COMMUNICATION SEMICONDUCTORS                                                                                       | CML Microcircuits<br>(Singapore)PteLtd                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Tel:<br>+44 (0)1621 875500<br>Fax:<br>+44 (0)1621 875600<br>Sales:<br>sales@cmlmicro.com<br>Tech Support:<br>techsupport@cmlmicro.com | Tel:<br>+1 336 744 5050<br>800 638 5577<br>Fax:<br>+1 336 744 5054<br>Sales:<br>us.sales@cmImicro.com<br>Tech Support:<br>us.techsupport@cmImicro.com | Tel:<br>+65 67450426<br>Fax:<br>+65 67452917<br>Sales:<br>sg.sales@cmImicro.com<br>Tech Support:<br>sg.techsupport@cmImicro.com |

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Sub-GHz Development Tools category:

Click to view products by CML Microcircuits manufacturer:

Other Similar products are found below :

EVAL-ADF7021DBJZ EVAL-ADF7021-NDBZ2 EVAL-ADF7021-VDB3Z EVAL-ADF7023DB3Z MICRF219A-433 EV MICRF220-433 EV AD6679-500EBZ EVAL-ADF7901EBZ EVAL-ADF790XEBZ 110976-HMC453QS16G STEVAL-IKR002V7D MAX2602EVKIT+ MAX1472EVKIT-315 MAX1479EVKIT-315 STEVAL-IKR002V3D MAX7042EVKIT-315+ MAX2902EVKIT# MAX9947EVKIT+ MAX1470EVKIT-315 SKY66188-11-EK1 SKY66013-11-EVB EVAL-ADF7023DB5Z DRF1200/CLASS-E 1096 1097 1098 MDEV-900-PRO DVK-SFUS-1-GEVK DVK-SFUS-API-1-GEVK US-SIGFOX-GEVB STEVAL-IKR002V2D 107755-HMC454ST89 DM182017-2 110961-HMC453ST89 DM182017-1 3179 DC689A DC1513B-AB 3229 3230 3231 3232 DC1250A-AA DC1513B-AC DC1513B-AD DC1513B-AA TEL0075 RFX1010-EK1 131903-HMC921LP4E EU-SIGFOX-GEVB