# **CT425**

# XtremeSense® TMR Ultra-Low Noise, <1% Total Error Current Sensor

#### **Features**

- Integrated Contact Current Sensing for Low to Medium Current Ranges:

- o 0 A to +20 A

- o -20 A to +20 A

- o 0 A to +30 A

- o -30 A to +30 A

- o 0 A to +50 A

- o -50 A to +50 A

- o 0 A to +65 A

- o -65 A to +65 A

- Integrated Current Carrying Conductor (CCC)

- Linear Analog Output Voltage

- Total Error Output ≤ ±1.0% FS

- 1 MHz Bandwidth

- Response Time: 300 ns

- UL/IEC 62387 Certification

- Rated Isolation Voltage >4 kV<sub>RMS</sub>

- Working Voltage for Basic Isolation >701 V<sub>RMS</sub>

- Working Voltage for Reinforced Isolation >344

V<sub>RMS</sub>

- IEC 61000-4-5 Certification

- Low Noise: 9.0 mA<sub>RMS</sub> to 13.5 mA<sub>RMS</sub> @ f<sub>BW</sub> = 100 kHz

- Supply Voltage: 4.75 to 5.50 V

- Filter Function to Reduce Noise on Output Pin

- Immunity to Common Mode Fields: -54 dB

- AEC-Q100 Grade 1 (Under Qualification)

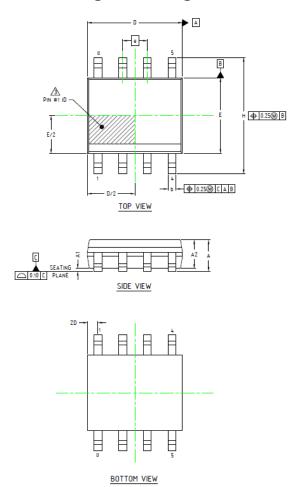

- 8-Lead SOIC Package

## **Applications**

- Solar/Power Inverters

- UPS, SMPS and Telecom Power Supplies

- Battery Management Systems

- Motor Control

- White Goods

- Consumer and Enterprise Electronics

- Over-Current Fault Protection

#### **Product Description**

The CT425 is a high bandwidth and ultra-low noise integrated contact current sensor that uses Crocus Technology's patented XtremeSense® TMR technology to enable high accuracy current measurements for many consumer, enterprise, and industrial applications. It supports eight (8) current ranges where the integrated current carrying conductor (CCC) will handle up to 65 A of current and generates a current measurement as a linear analog output voltage. It achieves a total output error of less than  $\pm 1.0\%$  full-scale (FS).

It has about a 300 ns output response time while the current consumption is about 6.0 mA and is immune to common mode fields. The CT425 has a filter function to reduce the noise on the output pin.

The CT425 is offered in an industry standard 8-lead SOIC package that is "green" and RoHS compliant.

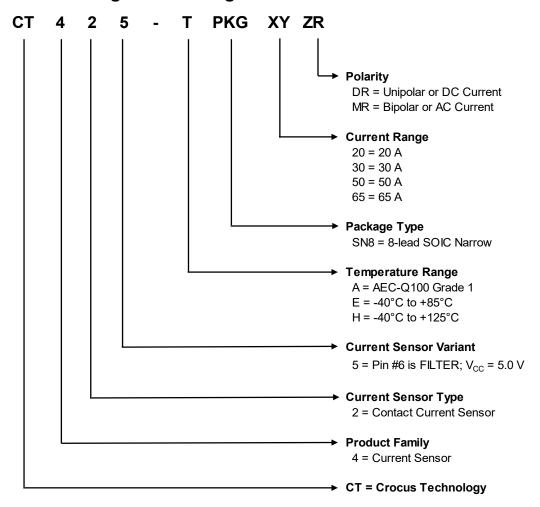

# **Part Ordering Information**

| Part Number    | Auto<br>Grade | Operating Temperature Range       | Current<br>Range | Package                              | Packing<br>Method |             |

|----------------|---------------|-----------------------------------|------------------|--------------------------------------|-------------------|-------------|

| CT425-ESN820DR | -             | -40°C to +85°C                    |                  |                                      |                   |             |

| CT425-HSN820DR | -             | -40°C to +125°C                   | 0 A to +20 A     |                                      |                   |             |

| CT425-ASN820DR | Grade 1       | -40 C t0 +125 C                   |                  |                                      |                   |             |

| CT425-ESN820MR | -             | -40°C to +85°C                    |                  |                                      |                   |             |

| CT425-HSN820MR | -             | -40°C to +125°C                   | -20 A to +20 A   |                                      |                   |             |

| CT425-ASN820MR | Grade 1       | -40 C t0 +125 C                   |                  |                                      |                   |             |

| CT425-ESN830DR | -             | -40°C to +85°C                    |                  |                                      |                   |             |

| CT425-HSN830DR | -             | -40°C to +125°C                   | 0 A to +30 A     |                                      |                   |             |

| CT425-ASN830DR | Grade 1       | -40 C to +125 C                   |                  | 8-lead SOIC<br>4.89 x 6.00 x 1.62 mm |                   |             |

| CT425-ESN830MR | -             | -40°C to +85°C                    |                  |                                      |                   |             |

| CT425-HSN830MR | -             | 40°C to 1405°C                    | -30 A to +30 A   |                                      | 8-lead SOIC       |             |

| CT425-ASN830MR | Grade 1       | -40°C to +125°C                   |                  |                                      |                   | Tane & Root |

| CT425-ESN850DR | -             | -40°C to +85°C<br>-40°C to +125°C | 0 A to +50 A     |                                      | Tape & Reel       |             |

| CT425-HSN850DR | -             |                                   |                  |                                      |                   |             |

| CT425-ASN850DR | Grade 1       | -40 C t0 +125 C                   |                  |                                      |                   |             |

| CT425-ESN850MR | -             | -40°C to +85°C                    |                  |                                      |                   |             |

| CT425-HSN850MR | -             | -40°C to +125°C                   | -50 A to +50 A   |                                      |                   |             |

| CT425-ASN850MR | Grade 1       | -40 C t0 +125 C                   |                  |                                      |                   |             |

| CT425-ESN865DR | -             | -40°C to +85°C                    |                  |                                      |                   |             |

| CT425-HSN865DR | -             | -40°C to +125°C                   | 0 A to +65 A     |                                      |                   |             |

| CT425-ASN865DR | Grade 1       | -40 C t0 +125 C                   |                  | _                                    |                   |             |

| CT425-ESN865MR | -             | -40°C to +85°C                    |                  |                                      |                   |             |

| CT425-HSN865MR | -             | -40°C to +125°C                   | -65 A to +65 A   |                                      |                   |             |

| CT425-ASN865MR | Grade 1       | -40 0 10 + 125 0                  |                  |                                      |                   |             |

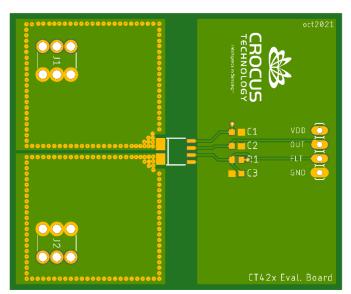

# **Evaluation Board Ordering Information**

| Part Number | Current Range  | Operating Temperature Range |

|-------------|----------------|-----------------------------|

| CTD425-20DC | 0 A to +20 A   |                             |

| CTD425-20AC | -20 A to +20 A |                             |

| CTD425-30DC | 0 A to +30 A   |                             |

| CTD425-30AC | -30 A to +30 A | -40°C to +125°C             |

| CTD425-50DC | 0 A to +50 A   | -40 C t0 +125 C             |

| CTD425-50AC | -50 A to +50 A |                             |

| CTD425-65DC | 0 A to +65 A   |                             |

| CTD425-65AC | -65 A to +65 A |                             |

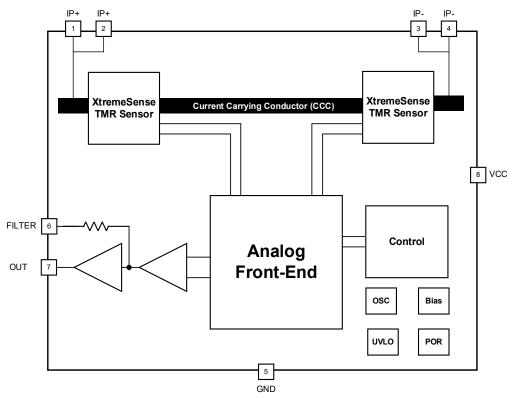

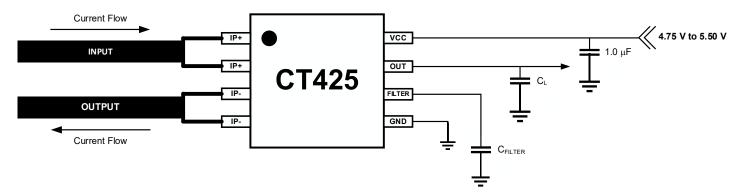

# **Block Diagram**

Figure 1. CT425 Functional Block Diagram for 8-lead SOIC Package

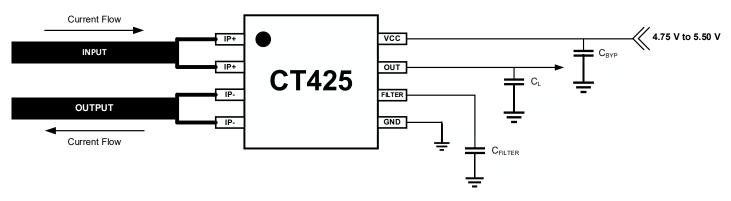

# **Application Diagram**

Figure 2. CT425 Application Block Diagram

**Table 1. Recommended External Components**

| Component | Description               | Vendor & Part Number        | Parameter | Min. | Тур.    | Max. | Unit |

|-----------|---------------------------|-----------------------------|-----------|------|---------|------|------|

| Свур      | 1.0 μF, X5R or<br>Better  | Murata<br>GRM155C81A105KA12 | C1        |      | 1.0     |      | μF   |

| CFILTER   | Various, X5R or<br>Better | Murata                      | C2        |      | Table 2 |      | pF   |

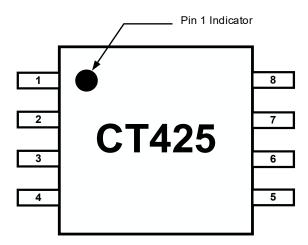

# **CT425 Pin Configuration**

Figure 3. CT425 Pin-out Diagram for 8-lead SOIC Package (Top-Down View)

## **Pin Definition**

| Pin # | Pin Name | Pin Description                                                                                                                                      |  |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | IP+      | Input primary conductor (positivo)                                                                                                                   |  |

| 2     | IFT      | Input primary conductor (positive).                                                                                                                  |  |

| 3     | IP-      | Output primary conductor (pagetive)                                                                                                                  |  |

| 4     | IP-      | Output primary conductor (negative).                                                                                                                 |  |

| 5     | GND      | Ground.                                                                                                                                              |  |

| 6     | FILTER   | Filter pin to improve noise performance by connecting an external capacitor to set the cut-off frequency.  No connect if the FILTER pin is not used. |  |

| 7     | OUT      | Analog output voltage that represents the measured current.                                                                                          |  |

| 8     | VCC      | Supply voltage.                                                                                                                                      |  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the CT425 and may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                | Parameter                                                   |                                                                                  | Min. | Max.                   | Unit |

|-----------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------|------|------------------------|------|

| Vcc                   | Supply Voltage                                              |                                                                                  | -0.3 | 6.0                    | V    |

| V <sub>I/O</sub>      | Analog Input/Output Pins                                    | s Maximum Voltage                                                                | -0.3 | V <sub>CC</sub> + 0.3* | V    |

| I <sub>CCC(MAX)</sub> | Current Carrying Conduc                                     | ctor, T <sub>A</sub> = +25°C                                                     |      | 70                     | Α    |

| Vsurge                | Dielectric Surge<br>Strength Test Voltage                   | IEC 61000-4-5: Tested ±5 Pulses at 2/60 seconds, 1.2 µs (rise) and 50 µs (width) | 6.0  |                        | kV   |

| Isurge                | Surge Strength Test<br>Current                              | Tested $\pm 5$ Pulses at 3/60 seconds, 8.0 $\mu$ s (rise) and 20 $\mu$ s (width) | 3.0  |                        | kA   |

| FCD                   | Electrostatic Discharge                                     | Human Body Model (HBM) per JESD22-A114                                           | ±2.0 |                        | 14/  |

| ESD                   | Protection Level Charged Device Model (CDM) per JESD22-C101 |                                                                                  | ±0.5 |                        | kV   |

| TJ                    | Junction Temperature                                        |                                                                                  | -40  | +150                   | °C   |

| Tstg                  | Storage Temperature                                         |                                                                                  | -65  | +155                   | °C   |

| TL                    | Lead Soldering Tempera                                      | ture, 10 Seconds                                                                 |      | +260                   | °C   |

<sup>\*</sup>The lower of  $V_{CC}$  + 0.3 V or 6.0 V.

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual operation of the CT425. Recommended operating conditions are specified to ensure optimal performance to the specifications. Crocus Technology does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol | Parameter                     |                     | Min. | Тур. | Max. | Unit |

|--------|-------------------------------|---------------------|------|------|------|------|

| Vcc    | Supply Voltage Range          |                     | 4.75 | 5.00 | 5.50 | V    |

| Vout   | OUT Voltage Range             | OUT Voltage Range   |      |      | Vcc  | V    |

| Іоит   | OUT Current                   |                     |      |      | ±1.0 | mA   |

|        |                               | Industrial          | -40  | +25  | +85  |      |

| TA     | Operating Ambient Temperature | Extended Industrial | -40  | +25  | +125 | °C   |

|        |                               | Automotive          | -40  | +25  | +125 |      |

# **Thermal Properties**

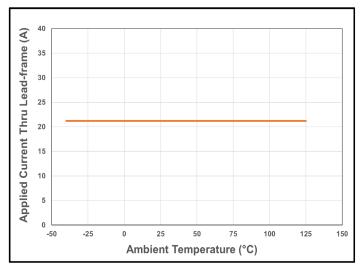

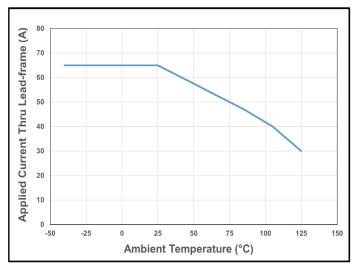

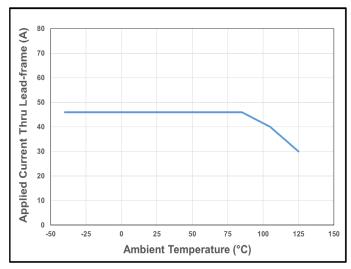

Junction-to-ambient thermal resistance is a function of application and board layout and is determined in accordance to JEDEC standard JESD51 for a four (4) layer 2s2p FR-4 printed circuit board (PCB) with 2 oz. of copper (Cu) and 4 oz. of copper (Cu) or more for 65 A. Special attention must be paid not to exceed junction temperature  $T_{J(MAX)}$  at a given ambient temperature  $T_{A}$ .

| Symbol   | Parameter                                      | Min. | Тур. | Max. | Unit |

|----------|------------------------------------------------|------|------|------|------|

| θJA_SOIC | Junction-to-Ambient Thermal Resistance, SOIC-8 |      | 151  | 176  | °C/W |

| θJC_SOIC | Junction-to-Case Thermal Resistance, SOIC-8    |      | 102  | 128  | °C/W |

# **Isolation Specifications**

| Symbol           | Parameter                  | Conditions                                                                                                      | Rating     | Unit              |

|------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|------------|-------------------|

| V <sub>ISO</sub> | Rated Isolation Voltage    | Agency Tested per IEC 62368* for 60 seconds.  Production Tested at V <sub>ISO</sub> for 1 second per IEC 62368. | 4.0        | kV <sub>RMS</sub> |

|                  |                            | Agency Tested per UL1577 for 60 seconds.  Production Tested at V <sub>ISO</sub> for 1 second per UL1577.        |            | kV <sub>RMS</sub> |

| \/               | Working Voltage for Basic  | Tooted per per IEC 62269*                                                                                       | 991        | V <sub>PK</sub>   |

| Vwork_iso        | Isolation                  | Tested per per IEC 62368*                                                                                       | 701        | V <sub>RMS</sub>  |

| \/               | Working Voltage for        | Tooted per ICC 62260*                                                                                           | 487        | $V_{PK}$          |

| Vwork_ri         | Reinforced Isolation       | Tested per IEC 62368*                                                                                           | 344        | V <sub>RMS</sub>  |

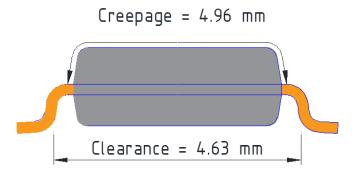

| d <sub>CR</sub>  | Creepage Distance          | Minimum Distance Along Package Body from IP Pins to I/O Pins                                                    | 4.96       | mm                |

| d <sub>CL</sub>  | Clearance Distance         | Minimum Distance Through Air from IP Pins to I/O Pins                                                           | 4.63       | mm                |

| d <sub>ISO</sub> | Distance Through Isolation | Minimum Internal Distance Through Isolation                                                                     | 110        | μm                |

| CTI              | Comparative Tracking Index | Material Group II                                                                                               | 400 to 599 | V                 |

<sup>\*</sup>IEC 62368 is the succeeding standard to IEC 60950-1 (Edition 2) for isolation testing specifications and as such it will be compliant to the latter standard.

# **Electrical Specifications**

#### **General Parameters**

| Symbol              | Parameter                                       | Conditions                                               | Min. | Тур. | Max. | Unit |  |  |

|---------------------|-------------------------------------------------|----------------------------------------------------------|------|------|------|------|--|--|

| Power Supplies      |                                                 |                                                          |      |      |      |      |  |  |

| Icc                 | Supply Current                                  | f <sub>BW</sub> = 1 MHz<br>No load, I <sub>P</sub> = 0 A |      | 6.0  | 9.0  | mA   |  |  |

| Іоит                | OUT Maximum Drive<br>Capability (1)             | OUT covers 10% to 90% of V <sub>CC</sub> span.           | -1.0 |      | +1.0 | mA   |  |  |

| C <sub>L_OUT</sub>  | OUT Capacitive Load (1)                         |                                                          |      |      | 100  | pF   |  |  |

| R <sub>L_</sub> out | OUT Resistive Load (1)                          |                                                          |      | 100  |      | kΩ   |  |  |

| RFILTER             | Internal Filter Resistance (1)                  |                                                          |      | 15   |      | kΩ   |  |  |

| RIP                 | Primary Conductor Resistance                    |                                                          |      | 0.5  |      | mΩ   |  |  |

| PSRR                | Power Supply Rejection Ratio                    |                                                          |      | 35   |      | dB   |  |  |

| SPSRR               | Sensitivity Power Supply<br>Rejection Ratio (1) |                                                          |      | 35   |      | dB   |  |  |

| OPSRR               | Offset Power Supply Rejection Ratio (1)         |                                                          |      | 40   |      | dB   |  |  |

| Analog Ou           | Analog Output (OUT)                             |                                                          |      |      |      |      |  |  |

| Symbol               | Parameter                            | Conditions                                                     | Min.                   | Тур.          | Max. | Unit |

|----------------------|--------------------------------------|----------------------------------------------------------------|------------------------|---------------|------|------|

| Vouт                 | OUT Voltage Linear Range,<br>Typical | V <sub>SIG_AC</sub> = ±2.00 V<br>V <sub>SIG_DC</sub> = +4.00 V | 0.50                   |               | 4.50 | V    |

| V <sub>OUT_SAT</sub> | Output High Saturation<br>Voltage    | V <sub>OUT</sub> , T <sub>A</sub> = +25°C,                     | V <sub>CC</sub> – 0.30 | Vcc -<br>0.25 |      | V    |

| CMFRR                | Common Mode Field Rejection          |                                                                |                        | -54           |      | dB   |

| CIVIFKK              | Ratio (1)                            |                                                                |                        | 0.5           |      | mA/G |

| Timings              |                                      |                                                                |                        |               |      |      |

| ton                  | Power-On Time (1)                    | $V_{CC} \ge 2.50 \text{ V}$                                    |                        | 100           | 200  | μs   |

| t <sub>RISE</sub>    | Rise Time (1)                        | $I_P = I_{RANGE(MAX)},$                                        |                        | 200           |      | ns   |

| tresponse            | Response Time (1)                    | $T_A = +25^{\circ}C$ ,                                         |                        | 300           |      | ns   |

| t <sub>DELAY</sub>   | Propagation Delay (1)                | C <sub>L</sub> = 220 pF                                        |                        | 250           |      | ns   |

| Protection           |                                      |                                                                |                        |               |      |      |

| Vuvlo                | Under-Voltage Lockout                | Rising V <sub>CC</sub>                                         |                        | 2.50          |      | V    |

| VUVLO                | Officer-Voltage Lockout              | Falling Vcc                                                    |                        | 2.45          |      | V    |

| Vuv_HYS              | UVLO Hysteresis                      |                                                                |                        | 50            |      | mV   |

<sup>(1)</sup> Guaranteed by design and characterization; not tested in production.

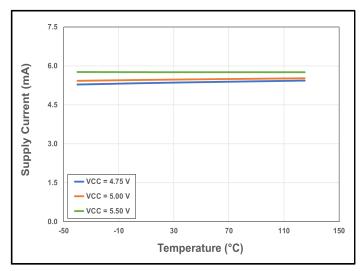

## **Electrical Characteristics**

Figure 4. CT425 Supply Current vs. Temperature vs. Supply Voltage

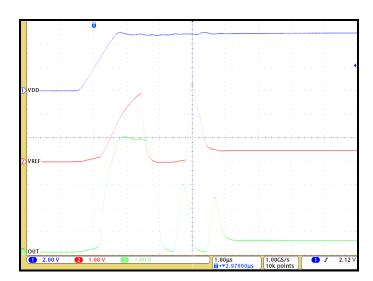

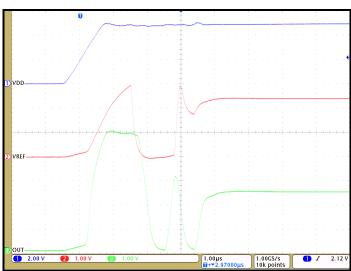

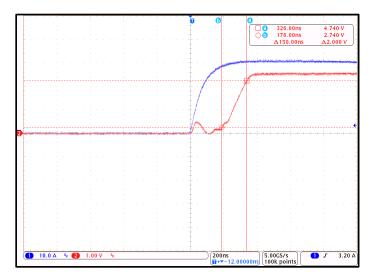

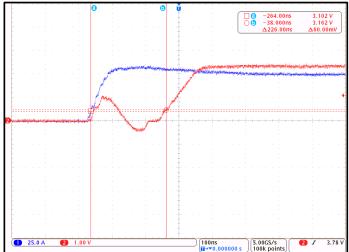

Figure 5. CT425 Startup Waveforms for  $V_{QQ} = 0.50 \text{ V}$  (DC Current)

Figure 6. CT425 Startup Waveforms for  $V_{QQ} = 2.50 \text{ V}$  (AC Current)

# **Electrical Characteristics (continued)**

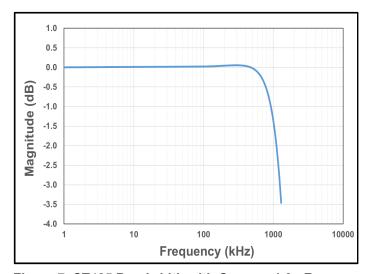

Figure 7. CT425 Bandwidth with  $C_{FILTER} = 1.0 pF$

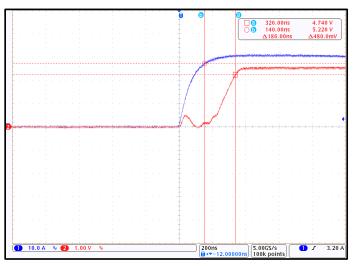

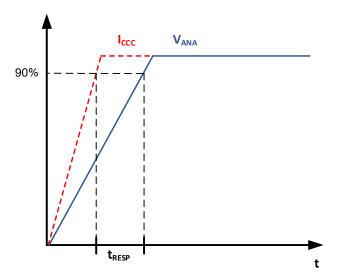

Figure 8. CT425 Response Time;  $I_P$  = 30  $A_{PK}$  and  $C_L$  = 100 pF (Blue =  $I_{CCC}$ , Red =  $V_{OUT}$ )

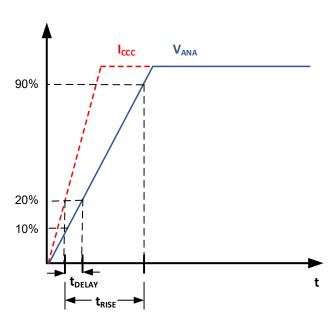

Figure 9. CT425 Rise Time;  $I_P$  = 30  $A_{PK}$  and  $C_L$  = 100 pF (Blue =  $I_{CCC}$ , Red =  $V_{OUT}$ )

Figure 10. CT425 Propagation Delay;  $I_P$  = 30  $A_{PK}$  and  $C_L$  = 100 pF (Blue =  $I_{CCC}$ , Red =  $V_{OUT}$ )

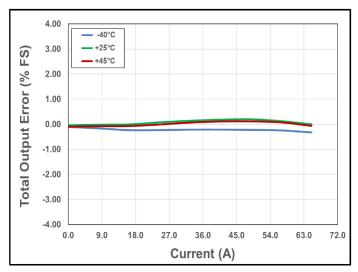

## CT425-xSN820DR: 0 A to +20 A

| Symbol                 | Parameter                                | Conditions                                        | Min.  | Тур.  | Max.  | Unit              |  |  |

|------------------------|------------------------------------------|---------------------------------------------------|-------|-------|-------|-------------------|--|--|

| I <sub>RANGE</sub>     | Current Range                            |                                                   | 0     |       | +20   | Α                 |  |  |

| Voq                    | Voltage Output Quiescent                 | T <sub>A</sub> = +25°C, I <sub>P</sub> = 0 A      | 0.495 | 0.500 | 0.505 | V                 |  |  |

| S                      | Sensitivity                              | $I_{RANGE(MIN)} < I_{P} < I_{RANGE(MAX)}$         |       | 200   |       | mV/A              |  |  |

| f <sub>BW</sub>        | Bandwidth (1)                            | Small Signal = -3 dB                              |       | 1.0   |       | MHz               |  |  |

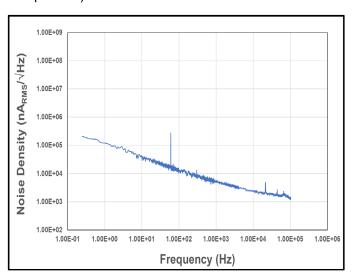

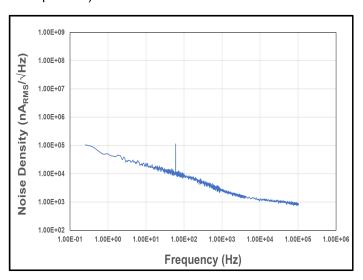

| e <sub>N</sub>         | Noise (1)                                | $T_A = +25^{\circ}C$ , $f_{BW} = 100 \text{ kHz}$ |       | 9.0   |       | mA <sub>RMS</sub> |  |  |

| OUT Accu               | racy Performance                         |                                                   |       |       |       |                   |  |  |

| Еоит                   | Total Output Error                       | $I_P = I_{P(MAX)}$                                |       | ±0.7  | ±1.0  | % FS              |  |  |

| ELIN                   | Non-Linearity Error (1)                  | $I_P = I_{P(MAX)},$<br>$T_A = -40$ °C to +125°C   |       | ±0.2  |       | % FS              |  |  |

| Esens                  | Sensitivity Error (1)                    | $I_P = I_{P(MAX)},$<br>$T_A = -40$ °C to +125°C   |       | ±0.7  |       | % FS              |  |  |

| V                      | Offset Voltage (1)                       | I <sub>P</sub> = 0 A,                             |       | ±21.9 |       | mV                |  |  |

| V <sub>OFFSET</sub>    | Offset Voltage (1)                       | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$    |       | ±0.5  |       | % FS              |  |  |

| Lifetime D             | Lifetime Drift                           |                                                   |       |       |       |                   |  |  |

| E <sub>TOT_DRIFT</sub> | Total Output Error<br>Lifetime Drift (1) | $I_P = I_{P(MAX)}$                                |       | ±1.0  |       | % FS              |  |  |

<sup>(1)</sup> Guaranteed by design and characterization; not tested in production.

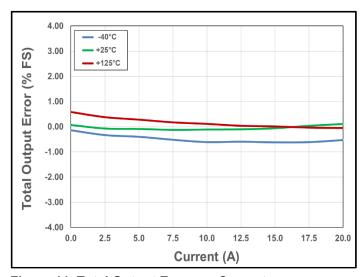

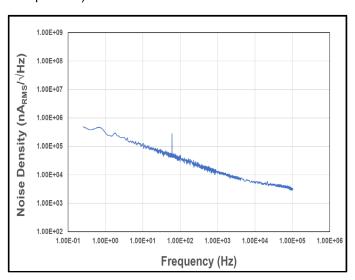

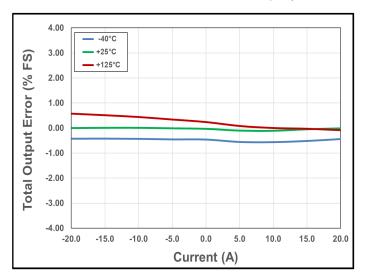

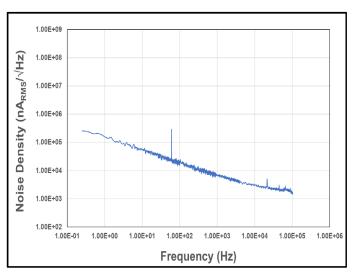

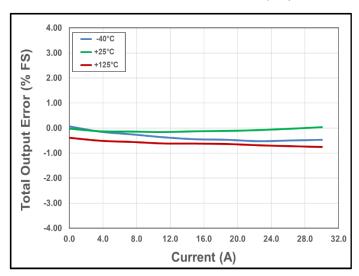

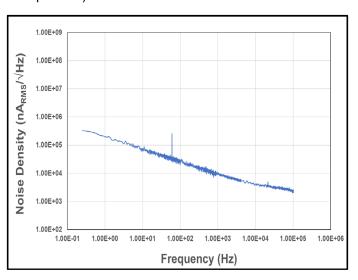

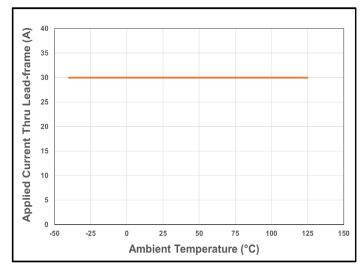

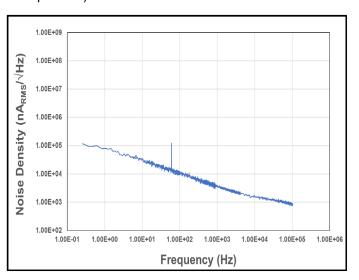

## **Electrical Characteristics for CT425-xSN820DR**

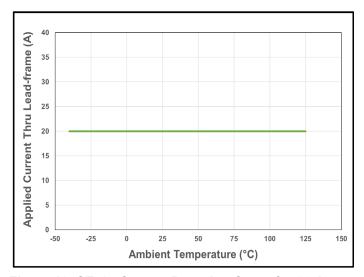

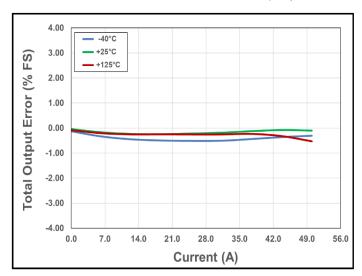

Figure 11. Total Output Error vs. Current vs. Temperature

Figure 12. Noise Density vs. Frequency

Figure 13. CT425 Current De-rating Curve for 20 ADC

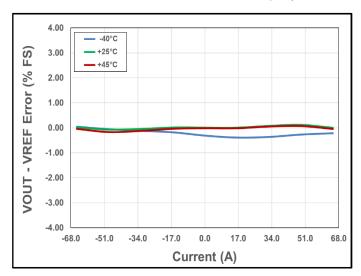

## CT425-xSN820MR: -20 A to +20 A

| Symbol                 | Parameter                                | Conditions                                        | Min.  | Тур.  | Max.  | Unit              |  |  |

|------------------------|------------------------------------------|---------------------------------------------------|-------|-------|-------|-------------------|--|--|

| IRANGE                 | Current Range                            |                                                   | -20   |       | +20   | Α                 |  |  |

| Voq                    | Voltage Output Quiescent                 | T <sub>A</sub> = +25°C, I <sub>P</sub> = 0 A      | 2.495 | 2.500 | 2.505 | V                 |  |  |

| S                      | Sensitivity                              | $I_{RANGE(MIN)} < I_{P} < I_{RANGE(MAX)}$         |       | 100   |       | mV/A              |  |  |

| f <sub>BW</sub>        | Bandwidth (1)                            | Small Signal = -3 dB                              |       | 1.0   |       | MHz               |  |  |

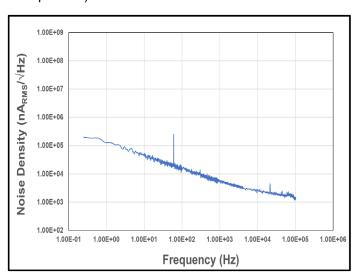

| e <sub>N</sub>         | Noise (1)                                | $T_A = +25^{\circ}C$ , $f_{BW} = 100 \text{ kHz}$ |       | 10.0  |       | mA <sub>RMS</sub> |  |  |

| OUT Accu               | racy Performance                         |                                                   |       |       |       |                   |  |  |

| Еоит                   | Total Output Error                       | $I_P = I_{P(MAX)}$                                |       | ±0.5  | ±1.0  | % FS              |  |  |

| ELIN                   | Non-Linearity Error (1)                  | $I_P = I_{P(MAX)},$<br>$T_A = -40$ °C to +125°C   |       | ±0.1  |       | % FS              |  |  |

| Esens                  | Sensitivity Error (1)                    | $I_P = I_{P(MAX)},$ $T_A = -40$ °C to +125°C      |       | ±0.3  |       | % FS              |  |  |

| V                      | Offset Voltage (1)                       | I <sub>P</sub> = 0 A,                             |       | ±15.2 |       | mV                |  |  |

| V <sub>OFFSET</sub>    | Offset Voltage (1)                       | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$    |       | ±0.4  |       | % FS              |  |  |

| Lifetime D             | Lifetime Drift                           |                                                   |       |       |       |                   |  |  |

| E <sub>TOT_DRIFT</sub> | Total Output Error<br>Lifetime Drift (1) | $I_P = I_{P(MAX)}$                                |       | ±1.0  |       | % FS              |  |  |

<sup>(1)</sup> Guaranteed by design and characterization; not tested in production.

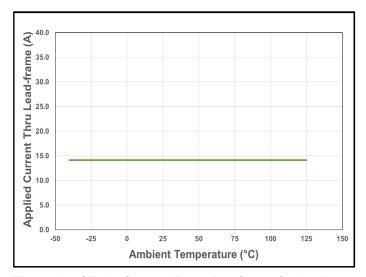

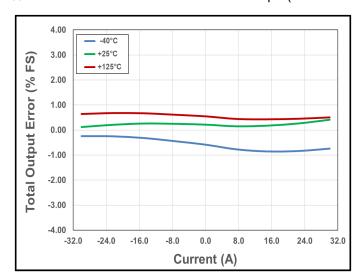

## **Electrical Characteristics for CT425-xSN820MR**

Figure 14. Total Output Error vs. Current vs. Temperature

Figure 15. Noise Density vs. Frequency

Figure 16. CT425 Current De-rating Curve for 20  $A_{\text{PK}}$  (14.1  $A_{\text{DC}})$

## CT425-xSN830DR: 0 A to +30 A

| Symbol                   | Parameter                                | Conditions                                                         | Min.  | Тур.  | Max.  | Unit              |

|--------------------------|------------------------------------------|--------------------------------------------------------------------|-------|-------|-------|-------------------|

| IRANGE                   | Current Range                            |                                                                    | 0     |       | +30   | Α                 |

| Voq                      | Voltage Output Quiescent                 | T <sub>A</sub> = +25°C, I <sub>P</sub> = 0 A                       | 0.495 | 0.500 | 0.505 | V                 |

| S                        | Sensitivity                              | I <sub>RANGE(MIN)</sub> < I <sub>P</sub> < I <sub>RANGE(MAX)</sub> |       | 133.3 |       | mV/A              |

| f <sub>BW</sub>          | Bandwidth <sup>(1)</sup>                 | Small Signal = -3 dB<br>C <sub>FILTER</sub> = 5 pF                 |       | 1.0   |       | MHz               |

| e <sub>N</sub>           | Noise (1)                                | $T_A = +25^{\circ}C$ , $f_{BW} = 100 \text{ kHz}$                  |       | 10.0  |       | mA <sub>RMS</sub> |

| OUT Accuracy Performance |                                          |                                                                    |       |       |       |                   |

| Еоит                     | Total Output Error                       | $I_P = I_{P(MAX)}$                                                 |       | ±0.7  | ±1.0  | % FS              |

| Elin                     | Non-Linearity Error (1)                  | $I_P = I_{P(MAX)},$ $T_A = -40$ °C to +125°C                       |       | ±0.1  |       | % FS              |

| Esens                    | Sensitivity Error (1)                    | $I_P = I_{P(MAX)},$<br>$T_A = -40$ °C to +125°C                    |       | ±0.4  |       | % FS              |

| \/                       | Official Valle are (1)                   | I <sub>P</sub> = 0 A,                                              |       | ±13.3 |       | mV                |

| V <sub>OFFSET</sub>      | Offset Voltage (1)                       | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                     |       | ±0.3  |       | % FS              |

| Lifetime D               | rift                                     |                                                                    |       |       |       |                   |

| E <sub>TOT_DRIFT</sub>   | Total Output Error<br>Lifetime Drift (1) | $I_P = I_{P(MAX)}$                                                 |       | ±1.0  |       | % FS              |

<sup>(1)</sup> Guaranteed by design and characterization; not tested in production.

## **Electrical Characteristics for CT425-xSN830DR**

Figure 17. Total Output Error vs. Current vs. Temperature

Figure 18. Noise Density vs. Frequency

Figure 19. CT425 Current De-rating Curve for 30 A<sub>DC</sub>

## CT425-xSN830MR: -30 A to +30 A

| Symbol                                 | Parameter                                | Conditions                                         | Min.  | Тур.  | Max.  | Unit              |

|----------------------------------------|------------------------------------------|----------------------------------------------------|-------|-------|-------|-------------------|

| IRANGE                                 | Current Range                            |                                                    | -30   |       | +30   | Α                 |

| Voq                                    | Voltage Output Quiescent                 | T <sub>A</sub> = +25°C, I <sub>P</sub> = 0 A       | 2.495 | 2.500 | 2.505 | V                 |

| S                                      | Sensitivity                              | $I_{RANGE(MIN)} < I_{P} < I_{RANGE(MAX)}$          |       | 66.7  |       | mV/A              |

| f <sub>BW</sub>                        | Bandwidth <sup>(1)</sup>                 | Small Signal = -3 dB<br>C <sub>FILTER</sub> = 5 pF |       | 1.0   |       | MHz               |

| en                                     | Noise (1)                                | $T_A = +25^{\circ}C$ , $f_{BW} = 100 \text{ kHz}$  |       | 11.5  |       | mA <sub>RMS</sub> |

| OUT Accu                               | racy Performance                         |                                                    |       |       |       |                   |

| Еоит                                   | Total Output Error                       | $I_P = I_{P(MAX)}$                                 |       | ±0.5  | ±1.0  | % FS              |

| ELIN                                   | Non-Linearity Error (1)                  | $I_P = I_{P(MAX)},$ $T_A = -40$ °C to +125°C       |       | ±0.1  |       | % FS              |

| Esens                                  | Sensitivity Error (1)                    | $I_P = I_{P(MAX)},$<br>$T_A = -40$ °C to +125°C    |       | ±0.4  |       | % FS              |

| V                                      | Offset Voltage (1)                       | I <sub>P</sub> = 0 A,                              |       | ±13.7 |       | mV                |

| V <sub>OFFSET</sub> Offset Voltage (1) |                                          | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$     |       | ±0.3  |       | % FS              |

| Lifetime D                             | rift                                     |                                                    |       |       |       |                   |

| E <sub>TOT_DRIFT</sub>                 | Total Output Error<br>Lifetime Drift (1) | $I_P = I_{P(MAX)}$                                 |       | ±1.0  |       | % FS              |

<sup>(1)</sup> Guaranteed by design and characterization; not tested in production.

## **Electrical Characteristics for CT425-xSN830MR**

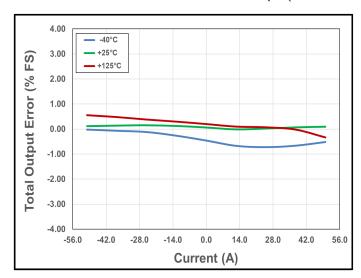

Figure 20. Total Output Error vs. Current vs. Temperature

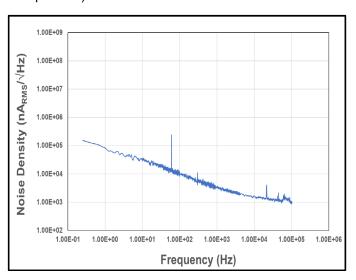

Figure 21. Noise Density vs. Frequency

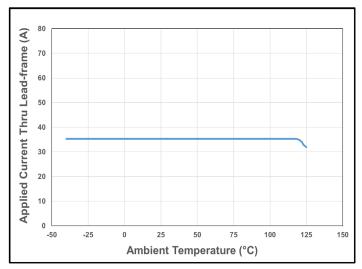

Figure 22. CT425 Current De-rating Curve for 30  $A_{PK}$  (21.2  $A_{DC}$ )

## CT425-xSN850DR: 0 A to +50 A

| Symbol                   | Parameter                                | Conditions                                                         | Min.  | Тур.  | Max.  | Unit              |

|--------------------------|------------------------------------------|--------------------------------------------------------------------|-------|-------|-------|-------------------|

| I <sub>RANGE</sub>       | Current Range                            |                                                                    | 0     |       | +50   | Α                 |

| Voq                      | Voltage Output Quiescent                 | T <sub>A</sub> = +25°C, I <sub>P</sub> = 0 A                       | 0.495 | 0.500 | 0.505 | V                 |

| S                        | Sensitivity                              | $I_{RANGE(MIN)} \le I_{P} \le I_{RANGE(MAX)}$                      |       | 80    |       | mV/A              |

| f <sub>BW</sub>          | Bandwidth (1)                            | Small Signal = -3 dB                                               |       | 1.0   |       | MHz               |

| e <sub>N</sub>           | Noise (1)                                | $T_A = +25^{\circ}C$ , $f_{BW} = 100 \text{ kHz}$                  |       | 10.0  |       | mA <sub>RMS</sub> |

| OUT Accuracy Performance |                                          |                                                                    |       |       |       |                   |

| Еоит                     | Total Output Error                       | $I_P = I_{P(MAX)}$                                                 |       | ±0.7  | ±1.5  | % FS              |

| ELIN                     | Non-Linearity Error (1)                  | $I_P = I_{P(MAX)},$ $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ |       | ±0.2  |       | % FS              |

| Esens                    | Sensitivity Error (1)                    | $I_P = I_{P(MAX)},$<br>$T_A = -40$ °C to +125°C                    |       | ±0.6  |       | % FS              |

| V                        | Offset Voltage (1)                       | I <sub>P</sub> = 0 A,                                              |       | ±12.9 |       | mV                |

| V <sub>OFFSET</sub>      | Offset Voltage (1)                       | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                     |       | ±0.3  |       | % FS              |

| Lifetime D               | Lifetime Drift                           |                                                                    |       |       |       |                   |

| E <sub>TOT_DRIFT</sub>   | Total Output Error<br>Lifetime Drift (1) | $I_P = I_{P(MAX)}$                                                 |       | ±1.0  |       | % FS              |

<sup>(1)</sup> Guaranteed by design and characterization; not tested in production.

## **Electrical Characteristics for CT425-xSN850DR**

Figure 23. Total Output Error vs. Current vs. Temperature

Figure 24. Noise Density vs. Frequency

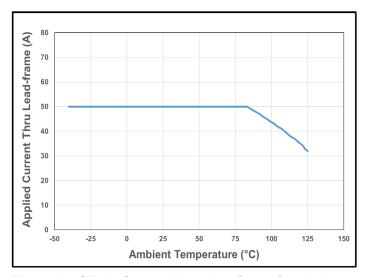

Figure 25. CT425 Current De-rating Curve for 50 A<sub>DC</sub>

## CT425-xSN850MR: -50 A to +50 A

| Symbol                 | Parameter                                | Conditions                                        | Min.  | Тур.  | Max.  | Unit              |

|------------------------|------------------------------------------|---------------------------------------------------|-------|-------|-------|-------------------|

| IRANGE                 | Current Range                            |                                                   | -50   |       | +50   | Α                 |

| Voq                    | Voltage Output Quiescent                 | T <sub>A</sub> = +25°C, I <sub>P</sub> = 0 A      | 2.495 | 2.500 | 2.505 | V                 |

| S                      | Sensitivity                              | $I_{RANGE(MIN)} \le I_{P} \le I_{RANGE(MAX)}$     |       | 40    |       | mV/A              |

| f <sub>BW</sub>        | Bandwidth (1)                            | Small Signal = -3 dB                              |       | 1.0   |       | MHz               |

| e <sub>N</sub>         | Noise (1)                                | $T_A = +25^{\circ}C$ , $f_{BW} = 100 \text{ kHz}$ |       | 14.0  |       | mA <sub>RMS</sub> |

| OUT Accu               | racy Performance                         |                                                   |       |       |       |                   |

| Еоит                   | Total Output Error                       | $I_P = I_{P(MAX)}$                                |       | ±0.5  | ±1.0  | % FS              |

| ELIN                   | Non-Linearity Error (1)                  | $I_P = I_{P(MAX)},$ $T_A = -40$ °C to +125°C      |       | ±0.1  |       | % FS              |

| Esens                  | Sensitivity Error (1)                    | $I_P = I_{P(MAX)},$ $T_A = -40$ °C to +125°C      |       | ±0.5  |       | % FS              |

|                        | Offset Valtage (1)                       | I <sub>P</sub> = 0 A,                             |       | ±10.9 |       | mV                |

| V <sub>OFFSET</sub>    | Offset Voltage (1)                       | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$    |       | ±0.3  |       | % FS              |

| Lifetime D             | rift                                     |                                                   |       |       |       |                   |

| E <sub>TOT_DRIFT</sub> | Total Output Error<br>Lifetime Drift (1) | $I_P = I_{P(MAX)}$                                |       | ±1.0  |       | % FS              |

<sup>(1)</sup> Guaranteed by design and characterization; not tested in production.

## **Electrical Characteristics for CT425-xSN850MR**

Figure 26. Total Output Error vs. Current vs. Temperature

Figure 27. Noise Density vs. Frequency

Figure 28. CT425 Current De-rating Curve for 50  $A_{PK}$  (35.4  $A_{DC}$ )

## CT425-xSN865DR: 0 A to +65 A

| Symbol                 | Parameter                                | Conditions                                                         | Min.  | Тур.  | Max.  | Unit              |

|------------------------|------------------------------------------|--------------------------------------------------------------------|-------|-------|-------|-------------------|

| I <sub>RANGE</sub>     | Current Range                            |                                                                    | 0     |       | +65   | А                 |

| Voq                    | Voltage Output Quiescent                 | T <sub>A</sub> = +25°C, I <sub>P</sub> = 0 A                       | 0.495 | 0.500 | 0.505 | V                 |

| S                      | Sensitivity                              | I <sub>RANGE(MIN)</sub> < I <sub>P</sub> < I <sub>RANGE(MAX)</sub> |       | 61.5  |       | mV/A              |

| f <sub>BW</sub>        | Bandwidth <sup>(1)</sup>                 | Small Signal = -3 dB<br>C <sub>FILTER</sub> = 5 pF                 |       | 1.0   |       | MHz               |

| e <sub>N</sub>         | Noise (1)                                | $T_A = +25^{\circ}C$ , $f_{BW} = 100 \text{ kHz}$                  |       | 10.0  |       | mA <sub>RMS</sub> |

| OUT Accu               | racy Performance                         |                                                                    |       |       |       |                   |

| Еоит                   | Total Output Error                       | $I_P = I_{P(MAX)}$                                                 |       | ±0.7  | ±1.5  | % FS              |

| ELIN                   | Non-Linearity Error (1)                  | $I_P = I_{P(MAX)},$<br>$T_A = -40$ °C to +125°C                    |       | ±0.2  |       | % FS              |

| Esens                  | Sensitivity Error (1)                    | $I_P = I_{P(MAX)},$<br>$T_A = -40$ °C to +125°C                    |       | ±0.2  |       | % FS              |

| V                      | Officet Voltage (1)                      | I <sub>P</sub> = 0 A,                                              |       | ±4.0  |       | mV                |

| V <sub>OFFSET</sub>    | Offset Voltage (1)                       | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                     |       | ±0.1  |       | % FS              |

| Lifetime D             | rift                                     |                                                                    |       |       |       |                   |

| E <sub>TOT_DRIFT</sub> | Total Output Error<br>Lifetime Drift (1) | $I_P = I_{P(MAX)}$                                                 |       | ±1.0  |       | % FS              |

<sup>(1)</sup> Guaranteed by design and characterization; not tested in production.

## **Electrical Characteristics for CT425-xSN865DR**

Figure 29. Total Output Error vs. Current vs. Temperature

Figure 30. Noise Density vs. Frequency

Figure 31. CT425 Current De-rating Curve for 65 ADC

## CT425-xSN865MR: -65 A to +65 A

| Symbol                 | Parameter                                | Conditions                                                         | Min.  | Тур.  | Max.  | Unit              |

|------------------------|------------------------------------------|--------------------------------------------------------------------|-------|-------|-------|-------------------|

| IRANGE                 | Current Range                            |                                                                    | -65   |       | +65   | Α                 |

| Voq                    | Voltage Output Quiescent                 | T <sub>A</sub> = +25°C, I <sub>P</sub> = 0 A                       | 2.495 | 2.500 | 2.505 | V                 |

| S                      | Sensitivity                              | I <sub>RANGE(MIN)</sub> < I <sub>P</sub> < I <sub>RANGE(MAX)</sub> |       | 30.8  |       | mV/A              |

| f <sub>BW</sub>        | Bandwidth <sup>(1)</sup>                 | Small Signal = -3 dB<br>C <sub>FILTER</sub> = 5 pF                 |       | 1.0   |       | MHz               |

| e <sub>N</sub>         | Noise (1)                                | $T_A = +25^{\circ}C$ , $f_{BW} = 100 \text{ kHz}$                  |       | 13.5  |       | mA <sub>RMS</sub> |

| OUT Accu               | racy Performance                         |                                                                    |       |       |       |                   |

| Еоит                   | Total Output Error                       | $I_P = I_{P(MAX)}$                                                 |       | ±0.5  | ±1.0  | % FS              |

| ELIN                   | Non-Linearity Error (1)                  | $I_P = I_{P(MAX)},$ $T_A = -40$ °C to +125°C                       |       | ±0.2  |       | % FS              |

| Esens                  | Sensitivity Error (1)                    | $I_P = I_{P(MAX)},$<br>$T_A = -40$ °C to +125°C                    |       | ±0.2  |       | % FS              |

| V                      | Offset Voltage (1)                       | I <sub>P</sub> = 0 A,                                              |       | ±4.0  |       | mV                |

| V <sub>OFFSET</sub>    | Offset Voltage (1)                       | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                     |       | ±0.1  |       | % FS              |

| Lifetime D             | rift                                     |                                                                    |       |       |       |                   |

| E <sub>TOT_DRIFT</sub> | Total Output Error<br>Lifetime Drift (1) | $I_P = I_{P(MAX)}$                                                 |       | ±1.0  |       | % FS              |

<sup>(1)</sup> Guaranteed by design and characterization; not tested in production.

## **Electrical Characteristics for CT425-xSN865MR**

Figure 32. Total Output Error vs. Current vs. Temperature

Figure 33. Noise Density vs. Frequency

Figure 34. CT425 Current De-rating Curve for 65  $A_{PK}$  (46.0  $A_{DC}$ )

## **Circuit Description**

#### Overview

The CT425 is a very high accuracy contact current sensor with an integrated current carrying conductor (CCC) that handles up to 65 A. It has very high sensitivity and a wide dynamic range with excellent accuracy (very low total output error) across temperature. This current sensor supports eight (8) current ranges:

- 0 A to +20 A

- -20 A to +20 A

- 0 A to +30 A

- -30 A to +30 A

- 0 A to +50 A

- -50 A to +50 A

- 0 A to +65 A

- -65 A to +65 A

When current is flowing through the CCC, the XtemeSense TMR sensors inside the chip senses the field which in turn generates differential voltage signals that then goes through the Analog Front-End (AFE) to output a current measurement with less than ±1.0% full-scale (FS) total output error (Eout).

The chip is designed to enable a very fast response time of 300 ns for the current measurement from the OUT pin as the bandwidth for the CT425 is 1.0 MHz. Even with a high bandwidth, the chip consumes a minimal amount of power.

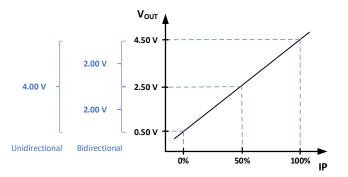

#### **Linear Output Current Measurement**

The CT425 provides a continuous linear analog output voltage which represents the current measurement. The output voltage range of OUT is from 0.50 V to 4.50 V with a  $V_{\text{OQ}}$  of 0.50 V and 2.50 V for unidirectional and bidirectional currents, respectively. Figure 35 illustrates the output voltage range of the OUT pin as a function of the measured current.

Figure 35. Linear Output Voltage Range (OUT) vs. Measured Current (IP)

#### Filter Function (FILTER)

The CT425 has a pin for the FILTER function which will enable it to improve the noise performance by changing the cut-off frequency. The bandwidth of the CT425 is 1.0 MHz however by adding a capacitor to the FILTER pin which will be in series with an internal resistance of approximately 15  $k\Omega$  will set the cut-off frequency to reduce the noise.

Table 2 shows the capacitor values required to achieve four (4) cut-off frequencies.

Table 2. R-C Filter Options for FILTER Pin

| Cut-off<br>Frequency | C <sub>FILTER</sub> (pF) | Capacitor Part<br>Number |

|----------------------|--------------------------|--------------------------|

| 100 kHz              | 91                       | GRM0225C1C910JA02        |

| 250 kHz              | 33                       | GRM0225C1C330JA02        |

| 500 kHz              | 16                       | GRM0225C1C160JA03        |

| 1.0 MHz              | 5                        | GRM0225C1C5R0CA03        |

If the FILTER pin is not used, then it should be left unconnected (No Connect).

## Sensitivity

The Sensitivity (S) is a change in CT425's output in response to a change in 1 A of current flowing through the CCC. It is defined by the product of the magnetic circuit sensitivity (G/A, where 1.0 G = 0.1 mT) and the chip's linear amplifier gain (mV/G). Therefore, the result of this gives a sensitivity unit of mV/A. The CT425 is factory calibrated to optimize the sensitivity for the full scale of the device's dynamic range.

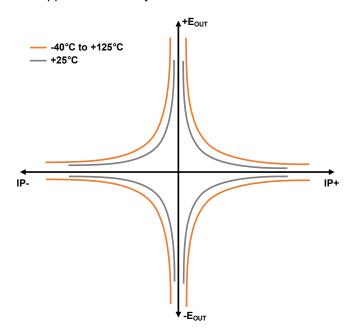

## **Total Output Error**

The Total Output Error is the difference between the current measured by CT425 and the actual current, relative to the actual current. It is equivalent to the ratio between the difference of the ideal and actual voltage to the ideal sensitivity multiplied by the current flowing through the primary conductor (CCC). The following equation defines the Total Output Error ( $E_{OUT}$ ) for the CT425:

$$E_{OUT} = \frac{V_{IOUT\_IDEAL}(I_P) - V_{IOUT}(I_P)}{S_{IDEAL}(I_P) \times I_P}$$

The  $E_{OUT}$  incorporates all sources of error and is a function of the sensed current (I<sub>P</sub>) from CT425. At high current levels, the  $E_{OUT}$  will be dominated by the

sensitivity error whereas at low current, the dominant characteristic is the offset voltage. Figure 36 shows the behavior of  $E_{OUT}$  versus  $I_P$ . When  $I_P$  goes to 0 from both directions, the curves exhibit asymptotic behavior i.e.,  $E_{OUT}$  approaches infinity.

Figure 36. Total Output Error  $(E_{OUT})$  vs. Sensed Current (IP)

The CT425 achieves a total output error ( $E_{\text{OUT}}$ ) that is less than  $\pm 1.0\%$  of Full-Scale (FS) over supply voltage and temperature. It is designed with innovative and proprietary TMR sensors and circuit blocks to provide very accurate current measurements regardless of the operating conditions.

#### **Sensitivity Error**

The sensitivity error (E<sub>SENS</sub>) is the sensitivity temperature drift error for unipolar or DC current. It is calculated using the equation below:

$$E_{SENS} = \left(\frac{S_{MEASURED}}{S} - 1\right) \times 100\%$$

For bipolar or AC current, the  $E_{\text{SENS}}$  is calculated by dividing the equation by 2.

#### Power-On Time (ton)

The Power-On Time ( $t_{ON}$ ) of 100  $\mu s$  is the amount of time required by CT425 to start up, fully power the chip and becoming fully operational from the moment the supply voltage is applied to it. This time includes the ramp up time and the settling time (within 10% of steady-state voltage under an applied magnetic field) after the power supply has reached the minimum  $V_{CC}$ .

## Response Time (tresponse)

The Response Time ( $t_{RESPONSE}$ ) of 300 ns for the CT425 is the time interval between the following terms:

- 1. When the primary current signal reaches 90% of its final value.

- 2. When the chip reaches 90% of its output corresponding to the applied current.

Figure 37. CT425 Response Time Curve

#### Rise Time (t<sub>RISE</sub>)

The CT425's rise time,  $t_{RISE}$ , is the time interval of when it reaches 10% and 90% of the full-scale output voltage. The  $t_{RISE}$  of the CT425 is 200 ns.

## Propagation Delay (tdelay)

The Propagation Delay (t<sub>DELAY</sub>) is the time difference between these two events:

- 1. When the primary current reaches 20% of its final value

- 2. When the chip reaches 20% of its output corresponding to the applied current.

The CT425 has a propagation delay of 250 ns.

Figure 38. CT425 Propagation Delay and Rise Time Curve

#### **Under-Voltage Lockout (UVLO)**

The Under-Voltage Lock-out protection circuitry of the CT425 is activated when the supply voltage (Vcc) falls below 2.45 V. The CT425 remains in a low quiescent state until Vcc rises above the UVLO threshold (2.50 V). In this condition where the Vcc is less than 2.45 V and UVLO is triggered, the output from the CT425 is not valid.

#### Immunity to Common Mode Fields

The CT425 is housed in custom plastic packages that utilize a "U-shaped" lead-frame to reduce the common mode fields generated as current flows through the CCC. With the "U-shaped" lead-frame, the stray fields cancel one another thus reducing electro-magnetic interference (EMI).

Also, good PCB layout of the CT425 will optimize performance and reduce EMI. Please see the Applications Information section in this data sheet for recommendations on PCB layout.

#### Creepage and Clearance

Two important terms as it relates to isolation provided by the package are: creepage and clearance. Creepage is defined as the shortest distance across the surface of the package from one side the leads to the other side of the leads. The definition for clearance is the shortest distance between the leads of opposite side through the air. Figure 39 illustrates the creepage and clearance for the SOIC-8 package of the CT425.

Figure 39. The Creepage and Clearance for the CT425's SOIC-8 package

## **Applications Information**

Figure 40. CT425 Application Block Diagram

#### **Application**

The CT425 is an integrated contact current sensor that can be used in many applications from measuring current in power supplies to motor control to over-current fault protection. It is a plug-and-play solution in that no calibration is required and it outputs to a microcontroller a simple linear analog output voltage which corresponds to a current measurement value.

It is designed to support an operating voltage range of 4.75 V to 5.50 V, but it is ideal to use a 5.0 V power supply where the output tolerance is less than ±5%.

#### **Bypass Capacitor**

A single 1.0  $\mu$ F capacitor is needed for the VCC pin to reduce the noise from the power supply and other circuits. This capacitor should be placed as close as possible to the CT425 to minimize inductance and resistance between the two devices.

#### **Filter Capacitor**

A capacitor may be added to the FILTER pin of the CT425 if there is a requirement to improve the noise performance. The capacitor will be connected to an internal resistor of 15  $k\Omega$  inside the chip to form a R-C filter. This R-C filter produces a cut-off frequency that will reduce the noise over this lower bandwidth.

If the filtering function is not required, then the FILTER pin should be left unconnected (No Connect).

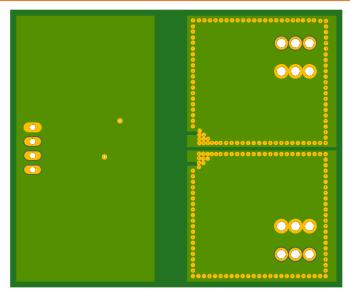

#### **Recommended PCB Layout**

Since the CT425 can measure up to 65 A of current, special care must be taken in the printed circuit board

(PCB) layout of the CT425 and the surrounding circuitry. It is recommended that the CCC pins be connected to as much copper area as possible. It is also recommended that 2 oz. or heavier copper be used for PCB traces when the CT425 is used to measure up to 30 A of current. Additional layers of the PCB should also be used to carry current and be connected using the arrangement of vias. Figure 41 and Figure 42 show the recommended the PCB layout for the 20 A and 30 A variants of CT425. For the 65 A variant, it is recommended that 4 oz. of copper be used for the PCB traces.

Figure 41. Recommended PCB Layout (Top Layer) for the 20 A to 65 A variants of the CT425.

Figure 42. Recommended PCB Layout (Bottom Layer) for the 20 A to 65 A variants of the CT425.

# **SOIC-8 Package Drawing and Dimensions**

#### NOTES

- 1. ALL DIMENSIONS IN MM.

- 2. PACKAGE SURFACE FINISHING:

- 2.1. TOP: MATTE (CHARMILLES #18~30)

- 2.2. BOTTOM: MATTE (CHARMILLES #12~27)

- THE PIN #1 IDENTIFIER MUST BE LOCATED WITHIN THE ZONE INDICATED.

- 4. LEAD COPLANARITY SHOULD BE 0 TO 0.10MM MAX.

- 5. JEDEC REFERENCE : MS-012.

Figure 43. SOIC-8 Package Drawing

Table 3. CT425 SOIC-8 Package Dimensions

| 0      | Dimensions in Millimeters (mm) |          |      |  |  |  |  |

|--------|--------------------------------|----------|------|--|--|--|--|

| Symbol | Min.                           | Тур.     | Max. |  |  |  |  |

| A1     | 0.10                           | 0.18     | 0.25 |  |  |  |  |

| b      | 0.36                           | 0.41     | 0.46 |  |  |  |  |

| С      | 0.19                           | 0.22     | 0.25 |  |  |  |  |

| D      | 4.80                           | 4.89     | 4.98 |  |  |  |  |

| E      | 3.81                           | 3.90     | 3.99 |  |  |  |  |

| е      |                                | 1.27 BSC |      |  |  |  |  |

| Н      | 5.80                           | 6.00     | 6.20 |  |  |  |  |

| h      | 0.25                           | 0.37     | 0.50 |  |  |  |  |

| L      | 0.41                           | -        | 1.27 |  |  |  |  |

| Α      | 1.52                           | 1.62     | 1.72 |  |  |  |  |

| α      | 0°                             | -        | 8°   |  |  |  |  |

| ZD     |                                | 0.53 REF |      |  |  |  |  |

| A2     | 1.37                           | 1.47     | 1.57 |  |  |  |  |

Crocus Technology provides package drawings as a service to customers considering or planning to use Crocus products in their designs. Drawings may change without notice. Please note the revision and date of the data sheet and contact a Crocus Technology representative to verify or obtain the most recent version. The package specifications do not expand the terms of Crocus Technology's worldwide terms and conditions, specifically the warranty therein, which covers Crocus Technology's products.

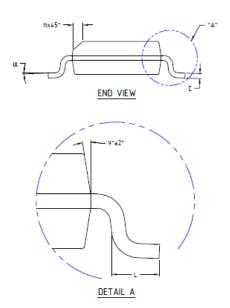

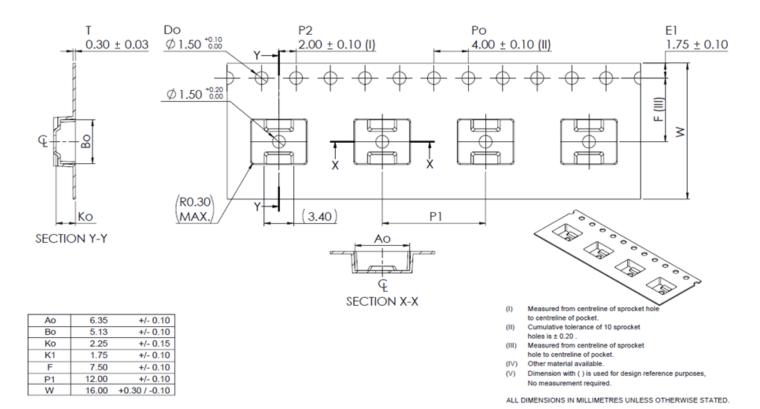

# **SOIC-8 Tape & Pocket Drawing and Dimensions**

Figure 44. SOIC-8 Package Drawing

# **Package Information**

**Table 4. CT425 Package Information**

| Part Number    | Package<br>Type | # of<br>Leads | Quantity<br>per Reel | Lead<br>Finish | MSL<br>Rating (2) | Operating Temperature (3) | Device<br>Marking <sup>(4)</sup> |

|----------------|-----------------|---------------|----------------------|----------------|-------------------|---------------------------|----------------------------------|

| CT425-ESN820DR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +85°C            | CT425<br>S820DR<br>YYWWLL        |

| CT425-HSN820DR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C           | CT425<br>S820DR<br>YYWWLL        |

| CT425-ASN820DR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C           | CT425<br>AS820DR<br>YYWWLL       |

| CT425-ESN820MR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +85°C            | CT425<br>S820MR<br>YYWWLL        |

| CT425-HSN820MR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C           | CT425<br>S820MR<br>YYWWLL        |

| CT425-ASN820MR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C           | CT425<br>AS820MR<br>YYWWLL       |

| CT425-ESN830DR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +85°C            | CT425<br>S830DR<br>YYWWLL        |

| CT425-HSN830DR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C           | CT425<br>S830DR<br>YYWWLL        |

| CT425-ASN830DR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C           | CT425<br>AS830DR<br>YYWWLL       |

| CT425-ESN830MR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +85°C            | CT425<br>S830MR<br>YYWWLL        |

| CT425-HSN830MR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C           | CT425<br>S830MR<br>YYWWLL        |

| CT425-ASN830MR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C           | CT425<br>AS830MR<br>YYWWLL       |

| CT425-ESN850DR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +85°C            | CT425<br>S850DR<br>YYWWLL        |

| Part Number    | Package<br>Type | # of<br>Leads | Quantity<br>per Reel | Lead<br>Finish | MSL<br>Rating (2) | Operating<br>Temperature <sup>(3)</sup> | Device<br>Marking <sup>(4)</sup> |

|----------------|-----------------|---------------|----------------------|----------------|-------------------|-----------------------------------------|----------------------------------|

| CT425-HSN850DR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C                         | CT425<br>S850DR<br>YYWWLL        |

| CT425-ASN850DR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C                         | CT425<br>AS850DR<br>YYWWLL       |

| CT425-ESN850MR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +85°C                          | CT425<br>S850MR<br>YYWWLL        |

| CT425-HSN850MR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C                         | CT425<br>S850MR<br>YYWWLL        |

| CT425-ASN850MR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C                         | CT425<br>AS850MR<br>YYWWLL       |

| CT425-ESN865DR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +85°C                          | CT425<br>S865DR<br>YYWWLL        |

| CT425-HSN865DR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C                         | CT425<br>S865DR<br>YYWWLL        |

| CT425-ASN865DR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C                         | CT425<br>AS865DR<br>YYWWLL       |

| CT425-ESN865MR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +85°C                          | CT425<br>S865MR<br>YYWWLL        |

| CT425-HSN865MR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C                         | CT425<br>S865MR<br>YYWWLL        |

| CT425-ASN865MR | SOIC            | 8             | 2,000                | Sn             | 3                 | -40°C to +125°C                         | CT425<br>AS865MR<br>YYWWLL       |

<sup>(1)</sup> RoHS is defined as semiconductor products that are compliant to the current EU RoHS requirements. It also will meet the requirement that RoHS substances do not exceed 0.1% by weight in homogeneous materials. Green is defined as the content of Chlorine (CI), Bromine (Br) and Antimony Trioxide based flame retardants satisfy JS709B low halogen requirements of ≤ 1,000 ppm.

<sup>(2)</sup> MSL Rating = Moisture Sensitivity Level Rating as defined by JEDEC standard classifications.

<sup>(3)</sup> Package will withstand ambient temperature range of -40°C to +125°C and storage temperature range of -65°C to +150°C.

<sup>(4)</sup> Device Marking for CT425 is defined as CT425 S8xxZR YYWWLL where the first 2 lines = part number, YY = year, WW = work week and LL = lot code.

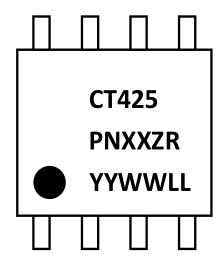

## **Device Marking**

| Row No. | Code                     | Definition             |  |

|---------|--------------------------|------------------------|--|

| 3       | •                        | Pin 1 Indicator        |  |

| 1       | CT425 Crocus Part Number |                        |  |

| 2       | P Package Type           |                        |  |

| 2       | N Number of Pins         |                        |  |

| 2       | XX                       | Maximum Current Rating |  |

| 2       | ZR                       | Current Range          |  |

| 3       | YY                       | Calendar Year          |  |

| 3       | WW                       | Work Week              |  |

| 3       | LL                       | Lot Code               |  |

Figure 45. CT425 Device Marking for 8-lead Package

Table 5. CT425 Device Marking Definition for 8-lead SOIC Package

## **Part Ordering Number Legend**

**Disclaimer:** The contents of this document are provided for informational purposes only. CROCUS TECHNOLOGY, INC. AND CROCUS TECHNOLOGY SA (COLLECTIVELY "CROCUS") MAKE NO REPRESENTATIONS OR WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS HEREIN, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Crocus reserves the right to make changes to the specifications and product descriptions, and/or to discontinue or make changes to its products at any time without notice. Crocus's products have not been designed, tested, or manufactured for use and should not be used in applications where the failure, malfunction or inaccuracy of the Products carries a risk of death or serious bodily injury or damage to tangible property, including, but not limited to, life support systems, nuclear facilities, military, aircraft navigation or communication, emergency systems, harsh environments, or other applications with a similar degree of potential hazard.