date 12/21/2015

**page** 1 of 32

# SERIES: NDM2Z-25 | DESCRIPTION: AUTO COMPENSATED, DIGITAL DC-DC POL CONVERTER

#### **GENERAL CHARACTERISTICS**

- 4.5~14 V input range

- 0.6~3.3 V programmable output

- voltage tracking

- voltage margining

- active current sharing

- Snapshot<sup>™</sup> parametric capture

- voltage/current/temperature monitoring

- synchronization and phase spreading

- remote differential voltage sense

- programmable soft start and soft stop

- fault management

#### **FEATURES**

- pin and function compatible with Architects of Modern Power™ product standards

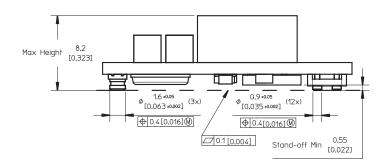

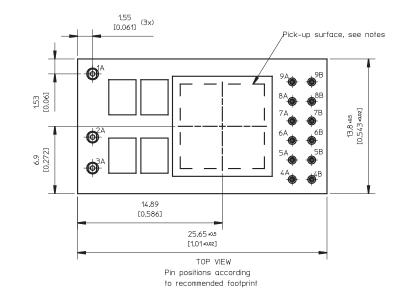

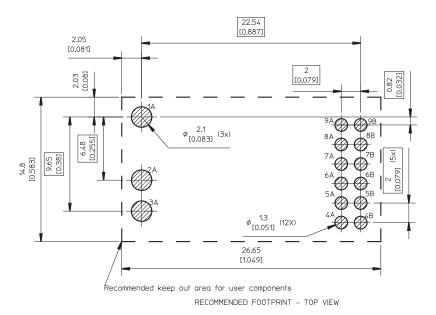

- compact package, horizontal: 25.7 x 13.8 x 8.2 mm

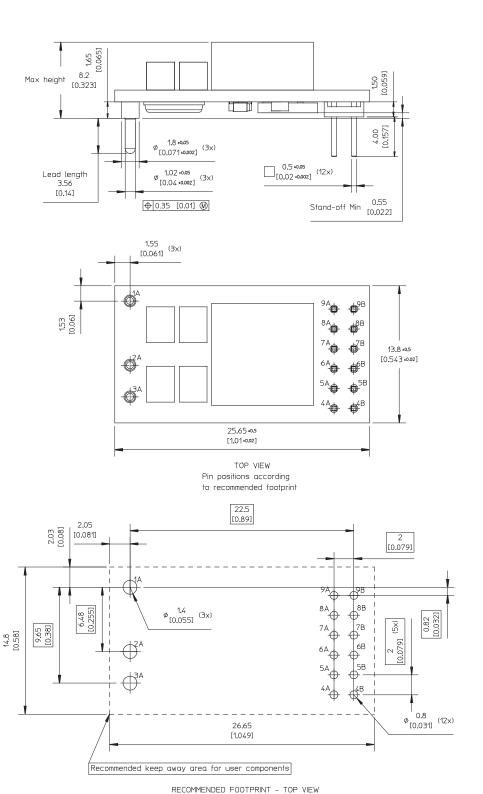

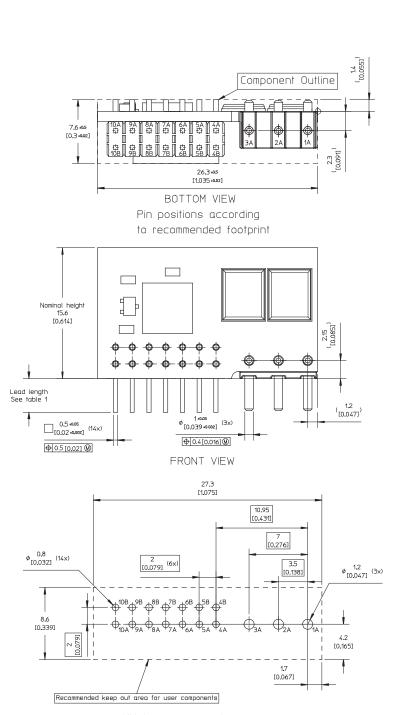

- compact package, vertical: 26.3 x 7.6 x 15.60 mm

- 25 A output

- high efficiency

- auto compensation

- · SMBus interface

- PMBus™ Compatible

| MODEL    | input voltage | output voltage | output current | output wattage |

|----------|---------------|----------------|----------------|----------------|

|          | (Vdc)         | (Vdc)          | max<br>(A)     | max<br>(W)     |

| NDM2Z-25 | 4.5~14        | 0.6~3.3        | 25             | 82.5           |

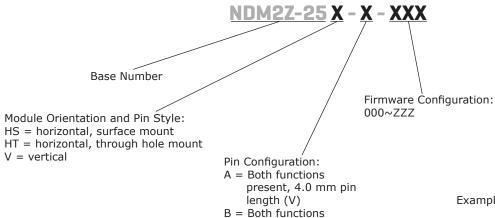

# **PART NUMBER KEY**

Example part number: NDM2Z-25V-A-001

vertical module 4.0 mm pin length firmware configuration 001

present, 5.5 mm pin

length (V)

P = Power Good (H)

V = Voltage Track (H)

<sup>\*</sup> HS and HT modules are delivered on tape and reel

<sup>\*</sup> V modules are delivered in trays

# **ABSOLUTE MAXIMUM RATINGS**

| parameter                                                                                         | conditions/description                                | min  | typ | max | units |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------|------|-----|-----|-------|

| operating temperature (see thermal consideration section) $(T_{P_1})$                             |                                                       | -40  |     | 125 | °C    |

| storage temperature (T <sub>s</sub> )                                                             |                                                       | -40  |     | 125 | °C    |

| input voltage (see operating information section for input and output voltage relations)( $V_I$ ) |                                                       | -0.3 |     | 16  | V     |

| logic I/O voltage                                                                                 | CTRL, SA0, SA1, SALERT, SCL, SDA, VSET, SYNC, DDC, PG | -0.3 |     | 6.5 | V     |

| ground voltage differential                                                                       | -S, PREF, GND                                         | -0.3 |     | 0.3 | V     |

| analog pin voltage                                                                                | V <sub>o</sub> , +S, VTRK                             | -0.3 |     | 6.5 | V     |

Notes:

Stress in excess of Absolute Maximum Ratings may cause permanent damage. Absolute Maximum Ratings, sometimes referred to as no destruction limits, are normally tested with one parameter at a time exceeding the limits in the Electrical Specification. If exposed to stress above these limits, function and performance may degrade in an unspecified manner.

# **Configuration File**

This product is designed with a digital control circuit. The control circuit uses a configuration file which determines the functionality and performance of the product. The Electrical Specification table shows parameter values of functionality and performance with the default configuration file, unless otherwise specified. The default configuration file is designed to fit most application needs with focus on high efficiency. If different characteristics are required it is possible to change the configuration file to optimize certain performance characteristics. Note that current sharing operation requires changed configuration file.

# PRODUCT ELECTRICAL SPECIFICATION, HORIZONTAL

$T_{\rm p_1}$  = -30 to +95 °C,  $V_{\rm I}$  = 4.5 to 14 V,  $V_{\rm I}$  >  $V_{\rm O}$  + 1.0 V Typical values given at:  $T_{\rm p_1}$  = +25 °C,  $V_{\rm I}$  = 12.0 V, max  $I_{\rm O}$ , unless otherwise specified under conditions. External  $C_{\rm IN}$  = 470 μF/10 mΩ,  $C_{\rm OUT}$  = 470 μF/10 mΩ. See Operating Information section for selection of capacitor types. Sense pins are connected to the output pins.

| parameter                                                                                                          | conditions/description                                                                                                  | min  | typ                   | max  | units                            |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|-----------------------|------|----------------------------------|

| input voltage rise time (V <sub>I</sub> )                                                                          | monotonic                                                                                                               |      |                       | 2.4  | V/ms                             |

| output voltage without<br>pin-strap (V <sub>o</sub> )                                                              |                                                                                                                         |      | 1.2                   |      | V                                |

| output voltage adjustment<br>range (V <sub>o</sub> )                                                               |                                                                                                                         | 0.60 |                       | 3.3  | V                                |

| output voltage adjustment<br>including margining (V <sub>o</sub> )                                                 | see note 17                                                                                                             | 0.54 |                       | 3.63 | V                                |

| output voltage set-point<br>resolution (V <sub>o</sub> )                                                           |                                                                                                                         |      | ±0.025                |      | %FS                              |

| output voltage accuracy (V <sub>o</sub> )                                                                          | including line, load, temp see note 14                                                                                  | -1   |                       | 1    | %                                |

|                                                                                                                    | current sharing operation see note 15                                                                                   | -2   |                       | 2    | %                                |

| internal resistance +S/-S to VOUT/GND $(V_0)$                                                                      |                                                                                                                         |      | 47                    |      | Ω                                |

| line regulation (V <sub>o</sub> )                                                                                  | $V_{o} = 0.6 \text{ V}$ $V_{o} = 1.0 \text{ V}$ $V_{o} = 1.8 \text{ V}$                                                 |      | 2<br>2<br>2<br>3      |      | mV<br>mV<br>mV                   |

| load regulation ( $V_o$ ) $I_o = 0 \sim 100\%$                                                                     | $V_{o} = 3.3 \text{ V}$ $V_{o} = 0.6 \text{ V}$ $V_{o} = 1.0 \text{ V}$ $V_{o} = 1.8 \text{ V}$ $V_{o} = 3.3 \text{ V}$ |      | 2<br>2<br>2<br>2<br>3 |      | mV<br>mV<br>mV<br>mV             |

| output ripple & noise (V <sub>oac</sub> )<br>C <sub>o</sub> = 470 µF (minimum external<br>capacitance) see note 11 | $V_{o} = 0.6 \text{ V}$ $V_{o} = 1.0 \text{ V}$ $V_{o} = 1.8 \text{ V}$ $V_{o} = 3.3 \text{ V}$                         |      | 20<br>30<br>40<br>60  |      | mVp-p<br>mVp-p<br>mVp-p<br>mVp-p |

| parameter                                                             | conditions/description                         | 1                                                                       | min | typ          | max    | units    |

|-----------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------|-----|--------------|--------|----------|

| output current (I <sub>o</sub> )                                      |                                                |                                                                         | 0   |              | 25     | Α        |

|                                                                       | $V_0 = 0.6 \text{ V}$                          |                                                                         |     | 1.58         |        | Α        |

| tatic input current at max I <sub>o</sub>                             | $V_0 = 1.0 \text{ V}$                          |                                                                         |     | 2.43         |        | A        |

| $I_s$ )                                                               | $V_0 = 1.8 \text{ V}$<br>$V_0 = 3.3 \text{ V}$ |                                                                         |     | 4.13<br>7.32 |        | A<br>A   |

| current limit threshold (I <sub>lim</sub> )                           | v <sub>o</sub> – 3.3 v                         |                                                                         | 27  | 7.52         | 37.5   | A        |

| current innit threshold (I <sub>lim</sub> )                           |                                                | V = 0.6 V                                                               |     | 8            | 37.3   | A        |

|                                                                       | RMS, hiccup mode,                              | $V_0 = 0.6 V$<br>$V_0 = 1.0 V$                                          |     | 6            |        | A        |

| short circuit current( ${ m I}_{ m sc}$ )                             | see note 3                                     | $V_0 = 1.8 \text{ V}$                                                   |     | 5            |        | A        |

|                                                                       |                                                | $V_0^0 = 3.3 \text{ V}$                                                 |     | 4            |        | Α        |

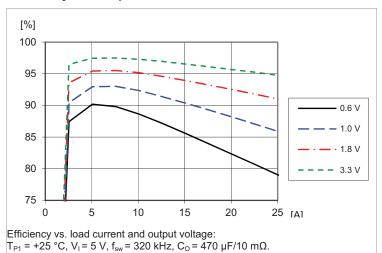

|                                                                       |                                                | $V_0 = 0.6 \text{ V}$                                                   |     | 84.4         |        | %        |

|                                                                       | 50% of max $I_0$                               | $V_0 = 1.0 \text{ V}$                                                   |     | 89.4         |        | %        |

|                                                                       | -0                                             | $V_0 = 1.8 \text{ V}$                                                   |     | 93.1         |        | %        |

| efficiency (η)                                                        |                                                | V <sub>o</sub> = 3.3 V                                                  |     | 95.2         |        | %        |

| , , , ,                                                               |                                                | $V_0 = 0.6 \text{ V}$                                                   |     | 79.2         |        | %        |

|                                                                       | max I <sub>o</sub>                             | $V_0 = 1.0 \text{ V}$                                                   |     | 85.7<br>90.8 |        | %<br>%   |

|                                                                       | · ·                                            | $V_0 = 1.8 \text{ V} $<br>$V_0 = 3.3 \text{ V} $                        |     | 93.9         |        | %        |

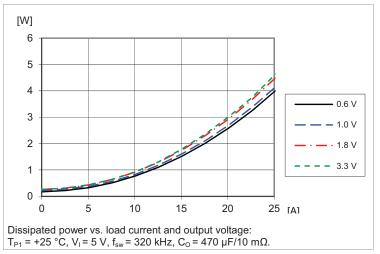

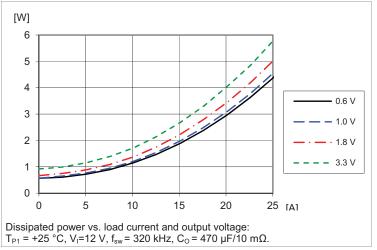

|                                                                       | V <sub>o</sub> = 0.6 V                         | -0                                                                      |     | 3.93         |        | W        |

| diitit I (D)                                                          | $V_0 = 1.0 \text{ V}$                          |                                                                         |     | 4.17         |        | W        |

| power dissipation at max $I_0(P_d)$                                   | $V_0 = 1.8 \text{ V}$                          |                                                                         |     | 4.55         |        | W        |

|                                                                       | $V_0 = 3.3 \text{ V}$                          |                                                                         |     | 5.34         |        | W        |

|                                                                       | default configuration:                         | $V_0 = 0.6 V$                                                           |     | 0.56         |        | W        |

| input idling power (no load)( $P_{ii}$ )                              | continues conduction                           | $V_0 = 1.0 \text{ V}$                                                   |     | 0.57         |        | W        |

|                                                                       | mode, CCM                                      | $V_0^0 = 1.8 \text{ V}$<br>$V_0 = 3.3 \text{ V}$                        |     | 0.67<br>0.92 |        | W        |

|                                                                       |                                                |                                                                         |     | 0.92         |        | VV       |

| nput standby power ( $P_{CTRL}$ )                                     | turned off with CTRL-pin                       | default configuration:<br>monitoring enabled,<br>precise timing enabled |     | 170          |        | mW       |

| internal input capacitance (C <sub>i</sub> )                          |                                                |                                                                         |     | 70           |        | μF       |

| nternal output capacitance (C <sub>o</sub> )                          |                                                |                                                                         |     | 200          |        | μF       |

| cotal external output<br>capacitance (C <sub>out</sub> )              | see note 9                                     |                                                                         | 300 |              | 15,000 | μF       |

| ESR range of capacitors<br>(per single capacitor) (C <sub>out</sub> ) | see note 9                                     |                                                                         | 5   |              | 30     | mΩ       |

|                                                                       | default configuration                          | $V_0 = 0.6 \text{ V}$                                                   |     | 95           |        | mV       |

| load transient peak voltage                                           | $di/dt = 2 A/\mu s C_0 = 470$                  | $V_0 = 0.0 \text{ V}$<br>$V_0 = 1.0 \text{ V}$                          |     | 105          |        | mV       |

| deviation (L to H/H to L) load step 25-75-25% of max $I_0(V_{tr1})$   | μF (minimum external capacitance)              | $V_0 = 1.8 \text{ V}$                                                   |     | 115          |        | mV       |

| step 25 75 25 % of max 1 <sub>0</sub> (v <sub>tr1</sub> )             | see note 12                                    | $V_0 = 3.3 \text{ V}$                                                   |     | 168          |        | mV       |

|                                                                       | default configuration                          | V - 0.6 V                                                               |     | 74           |        |          |

| oad transient recovery time                                           | $di/dt = 2 A/\mu s C_0 = 470$                  | $V_0 = 0.6 V$<br>$V_0 = 1.0 V$                                          |     | 74<br>85     |        | μs<br>μs |

| note 5 (L to H/H to L) load step                                      | μF (minimum external                           | $V_0 = 1.0 \text{ V}$<br>$V_0 = 1.8 \text{ V}$                          |     | 122          |        | μs<br>μs |

| $25-75-25\%$ of max $I_0(t_{tr1})$                                    | capacitance)<br>see note 12                    | $V_0 = 3.3 \text{ V}$                                                   |     | 140          |        | μs       |

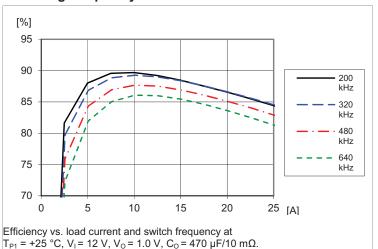

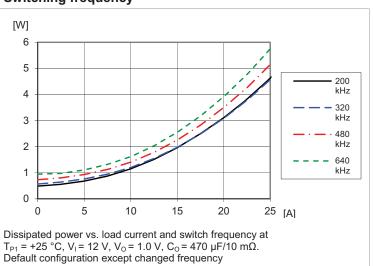

| witching frequency (f <sub>s</sub> )                                  | 550 11010 12                                   |                                                                         |     | 320          |        | kHz      |

| witching frequency range (f <sub>s</sub> )                            | PMBus configurable                             |                                                                         |     | 200-640      |        | kHz      |

| witching frequency set-point accuracy (f <sub>s</sub> )               |                                                |                                                                         | -5  | 200 010      | 5      | %        |

| control circuit PWM duty cycle                                        |                                                |                                                                         | 5   |              | 95     | %        |

| ninimum sync pulse width                                              |                                                |                                                                         | 150 |              |        | ns       |

| nput clock frequency drift                                            |                                                |                                                                         |     |              |        |          |

| colerance                                                             | external clock source                          |                                                                         | -13 |              | 13     | %        |

| parameter                                         | conditions/description      | 1                  | min  | typ              | max          | units    |

|---------------------------------------------------|-----------------------------|--------------------|------|------------------|--------------|----------|

|                                                   | UVLO threshold              |                    |      | 3.85             |              | V        |

|                                                   | UVLO threshold range        | PMBus configurable |      | 3.85-14          |              | V        |

|                                                   | set point accuracy          |                    | -150 |                  | 150          | mV       |

| input under voltage lockout,                      | UVLO hysteresis             |                    |      | 0.35             |              | V        |

| UVLO                                              | UVLO hysteresis range       | PMBus configurable |      | 0-10.15          |              | V        |

|                                                   | delay                       |                    |      | 2.5              |              | μs       |

|                                                   | fault response              | see note 3         |      | automatic re     | start, 70 ms |          |

|                                                   | IOVP threshold              |                    |      | 16               |              | V        |

|                                                   | IOVP threshold range        | PMBus configurable |      | 4.2-16           |              | V        |

|                                                   | set point accuracy          |                    | -150 |                  | 150          | mV       |

| input over voltage protection,                    | IOVP hysteresis             |                    |      | 1                |              | V        |

| IOVP                                              | IOVP hysteresis range       | PMBus configurable |      | 0-11.8           |              | V        |

|                                                   | delay                       |                    |      | 2.5              |              | μs       |

|                                                   | fault response              | see note 3         |      | automatic re     | start, 70 ms |          |

|                                                   | PG threshold                |                    |      | 90               |              | %V       |

| power good, PG, see note 2                        | PG hysteresis               |                    |      | 5                |              | %V       |

|                                                   | PG delay                    |                    |      | direct after DL0 | 3            | ms       |

|                                                   | PG delay range              | PMBus configurable |      | 0-500            |              | S        |

|                                                   | UVP threshold               |                    |      | 85               |              | %V       |

|                                                   | UVP threshold range         | PMBus configurable |      | 0-100            |              | %V       |

|                                                   | UVP hysteresis              |                    |      | 5                |              | %V       |

| output voltage over/under                         | OVP threshold               |                    |      | 115              |              | %V       |

| voltage protection, OVP/UVP                       | OVP threshold range         | PMBus configurable |      | 100-115          |              | %V       |

|                                                   | UVP/OVP response time       |                    |      | 25               |              | μs       |

|                                                   | UVP/OVP response time range | PMBus configurable |      | 5-60             |              | μs       |

|                                                   | fault response              | see note 3         |      | automatic re     | start, 70 ms |          |

|                                                   | OCP threshold               |                    |      | 32               |              | Α        |

|                                                   | OCP threshold range         | PMBus configurable |      | 0-32             |              | Α        |

| over current protection, OCP                      | protection delay            | see note 4         |      | 32               |              | $T_{sw}$ |

|                                                   | protection delay range      | PMBus configurable |      | 1-32             |              | $T_{sw}$ |

|                                                   | fault response              | see note 3         |      | automatic re     | start, 70 ms |          |

|                                                   | OTP threshold               |                    |      | 120              |              | °C       |

|                                                   | OTP threshold range         | PMBus configurable | -40  |                  | 125          | °C       |

| over temperature protection, OTP at P2 see note 8 | OTP hysteresis              |                    |      | 25               |              | °C       |

| OTT GET 2 SECTIONS                                | OTP hysteresis range        | PMBus configurable |      | 0-165            |              | °C       |

|                                                   | fault response              | see note 3         |      | automatic res    | tart, 240 ms |          |

| parameter                                                            | conditions/description                                       | on                                                                                                                 | min         | typ          | max       | units |

|----------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------|--------------|-----------|-------|

| logic input low threshold(V <sub>IL</sub> )                          | CVNC CAO CA1 CCL C                                           | CDA DDC CTDL VCCT                                                                                                  |             |              | 0.8       | V     |

| logic input high threshold $(V_{IH})$                                | SYNC, SA0, SA1, SCL, S                                       | SDA, DDC, CTRL, VSET                                                                                               | 2           |              |           | V     |

| logic input low sink current( $I_{IL}$ )                             | CTRL                                                         |                                                                                                                    |             |              | 0.6       | mA    |

| logic output low signal level (V <sub>OL</sub> )                     |                                                              |                                                                                                                    |             |              | 0.4       | V     |

| logic output high signal level (V <sub>OH</sub> )                    | SYNC, SCL, SDA, SALER                                        |                                                                                                                    | 2.25        |              |           | V     |

| logic output low sink current $(I_{\text{oL}})$                      | STINC, SCL, SDA, SALLE                                       | d, DDC, PG                                                                                                         |             |              | 4         | mA    |

| logic output high source current ( $\mathbf{I}_{\text{OH}}$ )        |                                                              |                                                                                                                    |             |              | 2         | mA    |

| setup time, SMBus(t <sub>set</sub> )                                 | see note 1                                                   |                                                                                                                    | 300         |              |           | ns    |

| hold time, SMBus(t <sub>hold</sub> )                                 | see note 1                                                   |                                                                                                                    | 250         |              |           | ns    |

| bus free time, SMBus(t <sub>free</sub> )                             | see note 1                                                   |                                                                                                                    | 2           |              |           | ms    |

| internal capacitance on logic pins (C <sub>p</sub> )                 |                                                              |                                                                                                                    |             | 10           |           | pF    |

| initialization time                                                  |                                                              | see note 10                                                                                                        |             | 40           |           | ms    |

|                                                                      | delay duration                                               | see note 16                                                                                                        |             | 10           |           | ms    |

| output voltage delay time see<br>note 6                              | delay duration range                                         | PMBus configurable                                                                                                 |             | 5-500,000    |           | ms    |

|                                                                      | delay accuracy turn-on                                       |                                                                                                                    |             | -0.25/+4     |           | ms    |

|                                                                      | delay accuracy turn-off                                      |                                                                                                                    |             | -0.25/+4     |           | ms    |

|                                                                      | ramp duration                                                |                                                                                                                    |             | 10           |           | ms    |

| output voltage ramp time                                             | ramp duration range                                          | PMBus configurable                                                                                                 |             | 0-200        |           | ms    |

| output voltage ramp time<br>see note 13                              |                                                              |                                                                                                                    |             | 100          |           | μs    |

|                                                                      | ramp time accuracy                                           | current sharing operation                                                                                          |             | 20           |           | %     |

| VTRK input bias current                                              | V <sub>VTRK</sub> = 5.5 V                                    |                                                                                                                    |             | 110          | 200       | μΑ    |

| ATDIX has a big a manage of a sure of a                              | 100% tracking, see not                                       | e 7                                                                                                                | -100        |              | 100       | mV    |

| VTRK tracking ramp accuracy<br>(V <sub>o</sub> - V <sub>VTRK</sub> ) | current sharing operation $V_0 = 1.0 \text{ V}$ , 10 ms ramp | on 2 phases, 100% tracking                                                                                         |             | ±100         |           | mV    |

| VTRK regulation accuracy                                             | 100% Tracking                                                |                                                                                                                    | -1          |              | 1         | %     |

| (V <sub>O</sub> - V <sub>VTRK</sub> )                                | current sharing operation                                    | on 100% Tracking                                                                                                   | -2          |              | 2         | %     |

| current difference between products in a current                     | steady state operation                                       |                                                                                                                    | Max 2 x     | READ_IOUT mo | onitoring |       |

| sharing group                                                        | ramp-up                                                      |                                                                                                                    |             | 2            |           | Α     |

| number of products in a current sharing group                        |                                                              |                                                                                                                    |             |              | 7         |       |

|                                                                      | READ_VIN vs V <sub>I</sub>                                   |                                                                                                                    |             | 3            |           | %     |

|                                                                      | READ_VOUT vs V <sub>o</sub>                                  |                                                                                                                    |             | 1            |           | %     |

| monitoring accuracy                                                  | READ_IOUT vs I <sub>o</sub>                                  | $I_{o} = 0-20 \text{ A}, T_{P1} = 0 \text{ to } +9!$<br>$V_{I} = 4.5-14 \text{ V}, V_{O} = 1.0 \text{ V}$          | 5 °C        | ±1.7         |           | А     |

|                                                                      | READ_IOUT vs I <sub>o</sub>                                  | $I_O = 0-20 \text{ A}, T_{P1} = 0 \text{ to } +990 \text{ A}$<br>$V_I = 4.5-14 \text{ V}, V_O = 0.6-3.3 \text{ A}$ | 5 °C<br>3 V | ±3           |           | Α     |

date 12/21/2015 | page 6 of 32

- 1: See section I<sup>2</sup>C/SMBus Setup and Hold Times Definitions.

- 2: Monitorable over PMBus Interface.

- 3: Automatic restart ~70 or 240 ms after fault if the fault is no longer present. Continuous restart attempts if the fault reappear after restart.

- 4:  $T_{sw}$  is the switching period. 5: Within +/-3% of VO

- 6: See section Soft-start Power Up.

- 7: Tracking functionality is designed to follow a VTRK signal with slew rate < 2.4 V/ms. For faster VTRK signals accuracy will depend on the regulator bandwidth. 8: See section Over Temperature Protection (OTP).

- 9: See section External Capacitors.

- 10: See section Initialization Procedure.

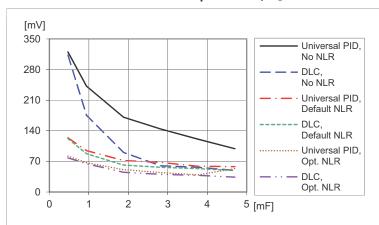

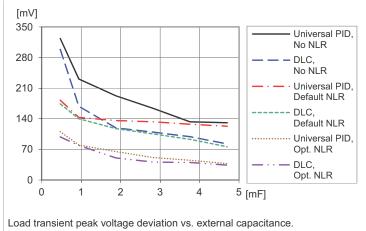

- 11: See graph Output Ripple vs External Capacitance and Operating information section Output Ripple and Noise.

12: See graph Load Transient vs. External Capacitance and Operating information section External Capacitors.

- 13: Time for reaching 100% of nominal Vout.

- 13: The for reaching 100% of nominal yout.

14: For Vout < 1.0 V accuracy is +/-10 mV. For further deviations see section Output Voltage Adjust using PMBus.

15: Accuracy here means deviation from ideal output voltage level given by configured droop and actual load. Includes line, load and temperature variations.

16: For current sharing the Output Voltage Delay Time must be reconfigured to minimum 15 ms.

17: For steady state operation above 1.05 x 3.3 V, please contact your local CUI sales representative.

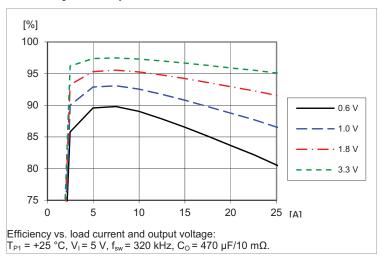

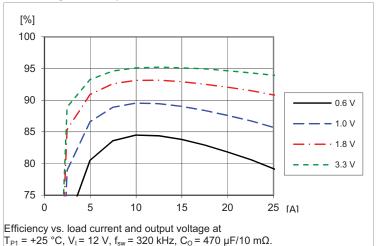

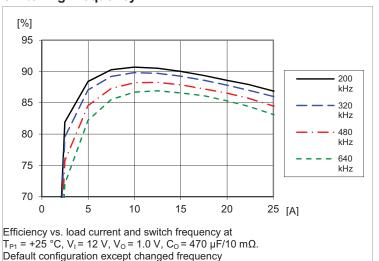

# TYPICAL CHARACTERISTICS, HORIZONTAL (CONTINUED)

# Efficiency vs. Output Current, V<sub>I</sub> = 5 V

# Efficiency vs. Output Current, $V_1 = 12 \text{ V}$

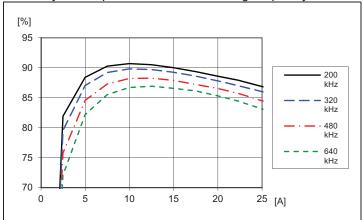

# Efficiency vs. Output Current and **Switching Frequency**

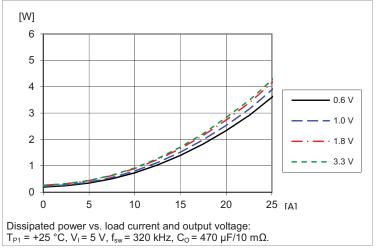

# Power Dissipation vs. Output Current, V<sub>I</sub> = 5 V

## Power Dissipation vs. Output Current, V<sub>I</sub> = 12 V

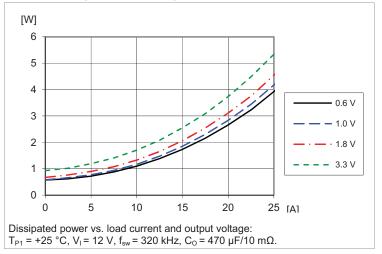

# Power Dissipation vs. Output Current and Switching frequency

# TYPICAL CHARACTERISTICS, HORIZONTAL (CONTINUED)

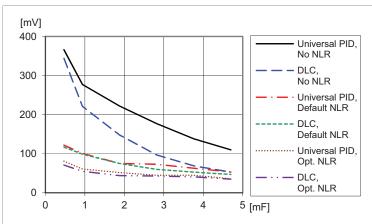

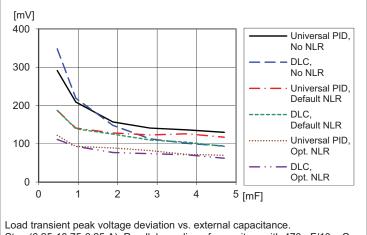

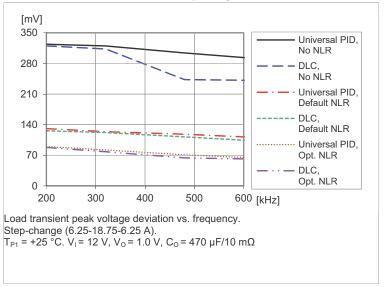

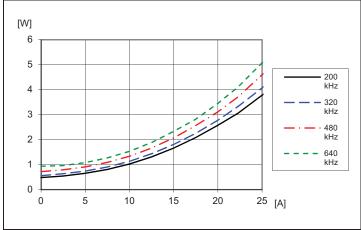

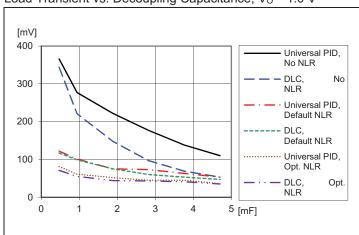

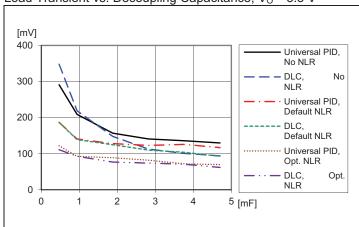

# Load Transient vs. External Capacitance, Vo = 1.0 V

Load transient peak voltage deviation vs. external capacitance. Step (6.25-18.75-6.25 A). Parallel coupling of capacitors with 470  $\mu F/10$  m $\Omega$ ,  $T_{P1}$  = +25 °C,  $V_{I}$  = 12 V,  $V_{O}$  = 1.0 V,  $f_{sw}$  = 320 kHz, di/dt = 2 A/µs

# Load Transient vs. External Capacitance, Vo = 3.3 V

Step (6.25-18.75-6.25 A). Parallel coupling of capacitors with 470  $\mu F/10$  m $\Omega$ ,  $T_{P1} = +25 \,^{\circ}\text{C}$ ,  $V_{I} = 12 \,^{\circ}\text{V}$ ,  $V_{O} = 3.3 \,^{\circ}\text{V}$ ,  $f_{sw} = 320 \,^{\circ}\text{kHz}$ ,  $di/dt = 2 \,^{\circ}\text{A}/\mu s$

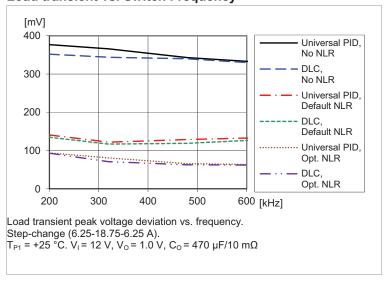

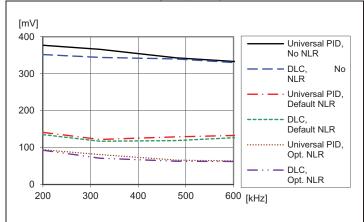

# Load transient vs. Switch Frequency

Note: For Universal PID, see section Dynamic Loop Compensation (DLC).

# CUI Inc | SERIES: NDM2Z-25 | DESCRIPTION: AUTO COMPENSATED, DIGITAL DC-DC POL CONVERTER

# TYPICAL CHARACTERISTICS, HORIZONTAL (CONTINUED)

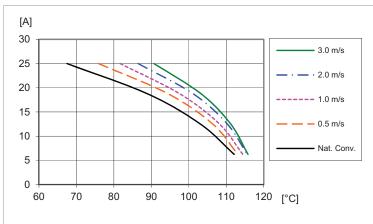

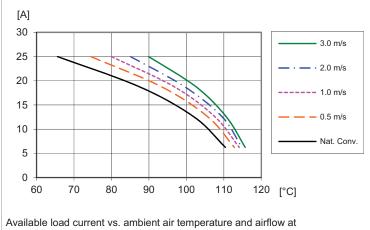

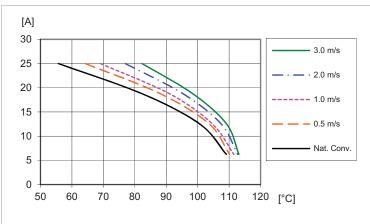

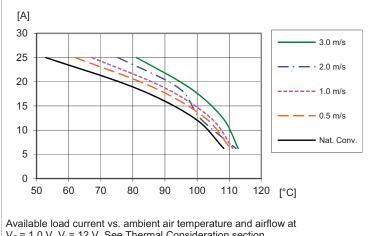

## Output Current Derating, Vo = 0.6 V

Available load current vs. ambient air temperature and airflow at  $V_0 = 0.6 \text{ V}$ ,  $V_1 = 12 \text{ V}$ . See Thermal Consideration section.

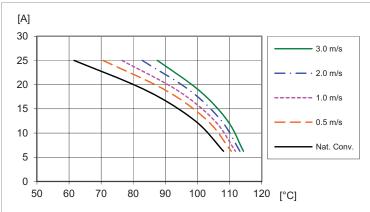

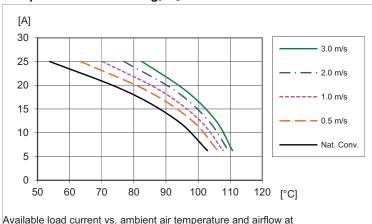

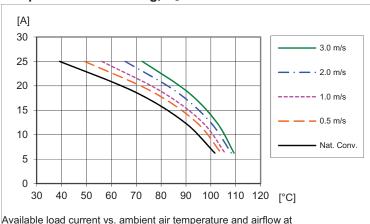

# Output Current Derating, Vo = 1.8 V

Available load current vs. ambient air temperature and airflow at  $V_0 = 1.8 \text{ V}, V_1 = 12 \text{ V}$ . See Thermal Consideration section.

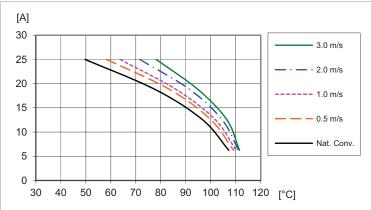

# Output Current Derating, Vo = 1.0 V

$V_0 = 1.0 \text{ V}$ ,  $V_1 = 12 \text{ V}$ . See Thermal Consideration section.

# Output Current Derating, Vo = 3.3 V

Available load current vs. ambient air temperature and airflow at  $V_0 = 3.3 \text{ V}$ ,  $V_1 = 12 \text{ V}$ . See Thermal Consideration section.

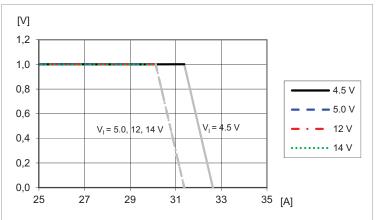

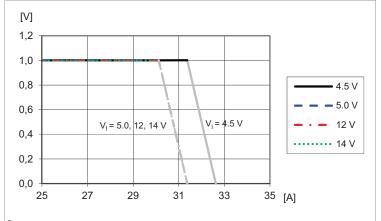

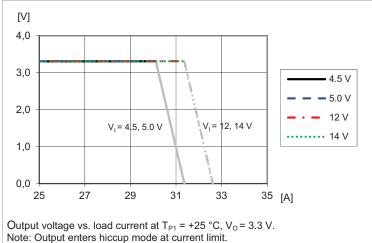

# Current Limit Characteristics, Vo = 1.0 V

Output voltage vs. load current at  $T_{P1}$  = +25 °C,  $V_O$  = 1.0 V. Note: Output enters hiccup mode at current limit.

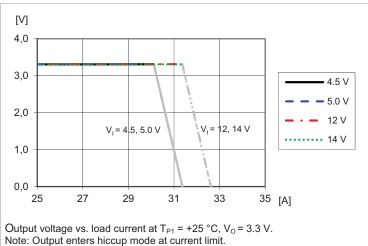

# Current Limit Characteristics, Vo = 3.3 V

# TYPICAL CHARACTERISTICS, HORIZONTAL (CONTINUED)

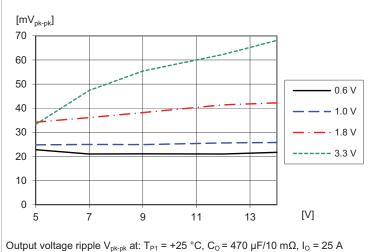

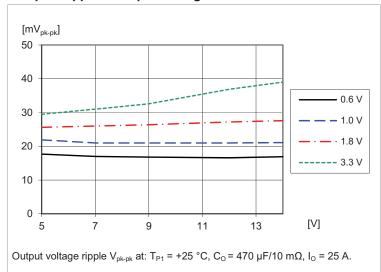

# **Output Ripple vs. Input Voltage**

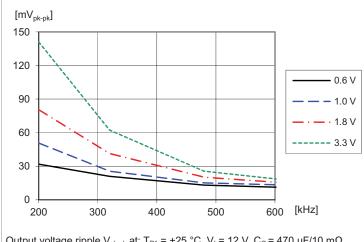

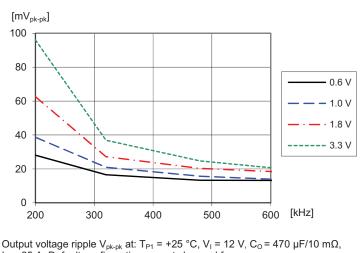

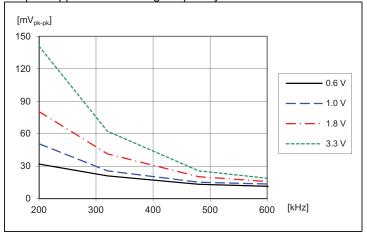

# **Output Ripple vs. Frequency**

Output voltage ripple  $V_{pk-pk}$  at:  $T_{P1}$  = +25 °C,  $V_I$  = 12 V,  $C_O$  = 470  $\mu$ F/10 m $\Omega$ ,  $I_{\odot}$  = 25 A. Default configuration except changed frequency.

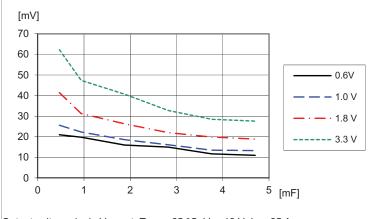

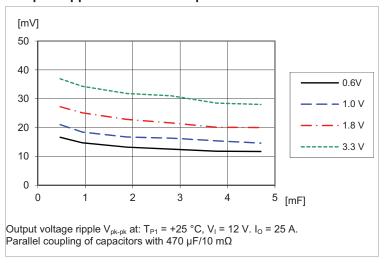

# Output Ripple vs. External Capacitance

Output voltage ripple V<sub>pk-pk</sub> at: T<sub>P1</sub> = +25 °C, V<sub>I</sub> = 12 V. I<sub>O</sub> = 25 A. Parallel coupling of capacitors with 470  $\mu$ F/10 m $\Omega$

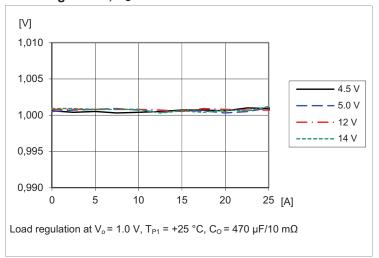

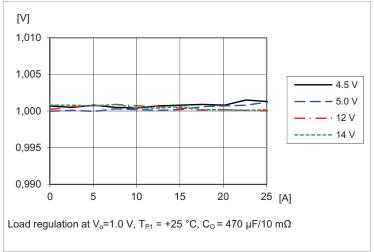

# Load regulation, $V_0 = 1.0 \text{ V}$

# TYPICAL CHARACTERISTICS, HORIZONTAL (CONTINUED)

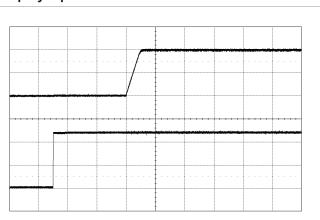

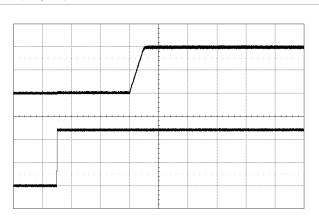

# Start-up by input source

Start-up enabled by connecting V<sub>I</sub> at:  $T_{P1} = +25 \,^{\circ}\text{C}, \, V_{I} = 12 \,^{\circ}\text{V}, \, V_{O} = 1.0 \,^{\circ}\text{V}$  $C_{O}$  = 470  $\mu F/10$   $m\Omega$ ,  $I_{O}$  = 25 A

Top trace: output voltage (0.5 V/div.). Bottom trace: input voltage (5 V/div.). Time scale: (20 ms/div.).

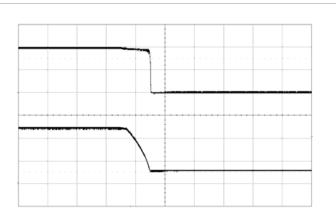

# Shut-down by input source

Shut-down enabled by disconnecting

$T_{P1} = +25 \, ^{\circ}\text{C}, \, V_{I} = 12 \, \text{V}, \, V_{O} = 1.0 \, \text{V}$  $C_0 = 470 \ \mu F/10 \ m\Omega$ ,  $I_0 = 25 \ A$

Top trace: output voltage (0.5 V/div.). Bottom trace: input voltage (5 V/div.). Time scale: (2 ms/div.).

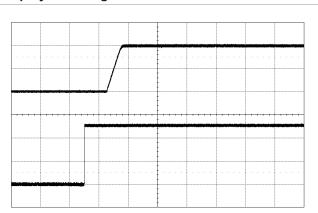

# Start-up by CTRL signal

Start-up by enabling CTRL signal at:  $T_{P1} = +25 \,^{\circ}\text{C}, \, V_{I} = 12 \, \text{V}, \, V_{O} = 1.0 \, \text{V}$  $C_{O}$  = 470  $\mu$ F/10  $m\Omega$ ,  $I_{O}$  = 25 A

Top trace: output voltage (0.5 V/div.). Bottom trace: CTRL signal (2 V/div.). Time scale: (20 ms/div.).

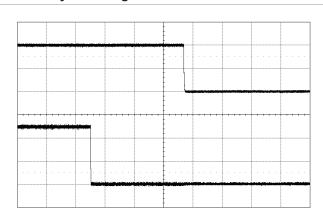

# Shut-down by CTRL signal

Shut-down enabled by disconnecting V<sub>I</sub> at:

$T_{P1}$  = +25 °C,  $V_I$  = 12 V,  $V_O$  = 1.0 V  $C_O = 470 \mu F/10 m\Omega$ ,  $I_O = 25 A$

Top trace: output voltage (0.5 V/div). Bottom trace: CTRL signal (2 V/div.). Time scale: (2 ms/div.).

# PRODUCT ELECTRICAL SPECIFICATION, VERTICAL

$T_{_{P1}}$  = -30 to +95 °C,  $V_{_{I}}$  = 4.5 to 14 V,  $V_{_{I}}$  >  $V_{_{O}}$  + 1.0 V Typical values given at:  $T_{_{P1}}$  = +25 °C,  $V_{_{I}}$  = 12.0 V, max  $I_{_{O}}$ , unless otherwise specified under conditions. External  $C_{_{IN}}$  = 470  $\mu\text{F}/10~\text{m}\Omega$ ,  $C_{_{OUT}}$  = 470  $\mu\text{F}/10~\text{m}\Omega$ . See Operating Information section for selection of capacitor types. Sense pins are connected to the output pins.

| parameter                                                                                           | conditions/description                             | n                                              | min  | typ          | max  | units    |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------|------|--------------|------|----------|

| nput voltage rise time (V <sub>I</sub> )                                                            | monotonic                                          |                                                |      |              | 2.4  | V/ms     |

| output voltage without<br>oin-strap (V <sub>o</sub> )                                               |                                                    |                                                |      | 1.2          |      | V        |

| output voltage adjustment<br>range (V <sub>o</sub> )                                                |                                                    |                                                | 0.60 |              | 3.3  | V        |

| output voltage adjustment<br>including margining (V <sub>o</sub> )                                  | see note 17                                        |                                                | 0.54 |              | 3.63 | V        |

| output voltage set-point<br>resolution (V <sub>o</sub> )                                            |                                                    |                                                |      | ±0.025       |      | %FS      |

| output voltage accuracy (V <sub>o</sub> )                                                           | including line, load, tem                          | p see note 14                                  | -1   |              | 1    | %        |

| output voltage accuracy (v <sub>o</sub> )                                                           | current sharing operation                          | n see note 15                                  | -2   |              | 2    | %        |

| nternal resistance +S/-S to $VOUT/GND (V_0)$                                                        |                                                    |                                                |      | 47           |      | Ω        |

| ·                                                                                                   | V <sub>o</sub> = 0.6 V                             |                                                |      | 2            |      | mV       |

| line regulation (V <sub>o</sub> )                                                                   | $V_0 = 1.0 \text{ V}$                              |                                                |      | 2            |      | mV       |

|                                                                                                     | $V_0 = 1.8 \text{ V}$<br>$V_0 = 3.3 \text{ V}$     |                                                |      | 2<br>3       |      | mV<br>mV |

|                                                                                                     | V <sub>0</sub> = 0.6 V                             |                                                |      | 2            |      | mV       |

| load regulation (V <sub>o</sub> )                                                                   | $V_0 = 1.0 \text{ V}$                              |                                                |      | 2            |      | mV       |

| $I_0 = 0 \sim 100\%$                                                                                | $V_0 = 1.8 \text{ V} $<br>$V_0 = 3.3 \text{ V} $   |                                                |      | 2<br>3       |      | mV<br>mV |

|                                                                                                     | $V_0 = 0.6 \text{ V}$                              |                                                |      | 20           |      | mVp-p    |

| output ripple & noise ( $V_{oac}$ )<br>$C_0 = 470 \mu F$ (minimum external capacitance) see note 11 | $V_0 = 0.0 \text{ V}$<br>$V_0 = 1.0 \text{ V}$     |                                                |      | 30           |      | mVp-r    |

|                                                                                                     | $V_0 = 1.8 \text{ V}$                              |                                                |      | 40           |      | mVp-p    |

| . ,                                                                                                 | V <sub>o</sub> = 3.3 V                             |                                                |      | 60           |      | mVp-p    |

| output current (I <sub>o</sub> )                                                                    |                                                    |                                                | 0    |              | 20   | A        |

| static input current at may I                                                                       | $V_0 = 0.6 \text{ V}$                              |                                                |      | 1.61<br>2.46 |      | A        |

| static input current at max $I_0$                                                                   | $V_0 = 1.0 \text{ V} $<br>$V_0 = 1.8 \text{ V} $   |                                                |      | 4.17         |      | A<br>A   |

| ν-5/                                                                                                | $V_0 = 3.3 \text{ V}$                              |                                                |      | 7.35         |      | Α        |

| current limit threshold $(I_{lim})$                                                                 |                                                    |                                                | 27   |              | 37.5 | Α        |

|                                                                                                     |                                                    | $V_0 = 0.6 V$                                  |      | 8            |      | Α        |

| short circuit current(I <sub>sc</sub> )                                                             | RMS, hiccup mode, see note 3                       | $V_0 = 1.0 \text{ V}$                          |      | 6            |      | A        |

| - 56                                                                                                | see note 3                                         | $V_0 = 1.8 \text{ V}$<br>$V_0 = 3.3 \text{ V}$ |      | 5<br>4       |      | A<br>A   |

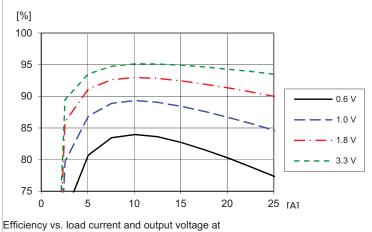

|                                                                                                     |                                                    | V <sub>0</sub> = 0.6 V                         |      | 83.6         |      | %        |

|                                                                                                     | 50% of max $I_o$                                   | $V_0 = 1.0 \text{ V}$                          |      | 89           |      | %        |

|                                                                                                     | 56 % G:ax =0                                       | $V_0 = 1.8 \text{ V}$<br>$V_0 = 3.3 \text{ V}$ |      | 92.8<br>95.1 |      | %<br>%   |

| efficiency (η)                                                                                      |                                                    |                                                |      |              |      |          |

|                                                                                                     |                                                    | $V_{o} = 0.6 V$<br>$V_{o} = 1.0 V$             |      | 77.4<br>84.6 |      | %<br>%   |

|                                                                                                     | $\max I_o$                                         | $V_0^0 = 1.8 \text{ V}$                        |      | 90           |      | %        |

|                                                                                                     |                                                    | $V_0 = 3.3 \text{ V}$                          |      | 93.5         |      | %        |

|                                                                                                     | $V_0 = 0.6 \text{ V}$                              |                                                |      | 4.37         |      | W        |

| power dissipation at max $I_0(P_d)$                                                                 | $V_0^0 = 1.0 \text{ V}$                            |                                                |      | 4.54<br>5.01 |      | W        |

| . 5 t u/                                                                                            | $V_0^0 = 1.8 \text{ V} $<br>$V_0 = 3.3 \text{ V} $ |                                                |      | 5.01<br>5.77 |      | W<br>W   |

|                                                                                                     |                                                    | V <sub>o</sub> = 0.6 V                         |      | 0.56         |      | W        |

| input idling power (no load)(P,)                                                                    | default configuration: continues conduction        | $V_0 = 1.0 \text{ V}$                          |      | 0.57         |      | W        |

| mpacialing power (no load)(F <sub>ii</sub> )                                                        | mode, CCM                                          | $V_{0} = 1.8 \text{ V}$                        |      | 0.67         |      | W        |

|                                                                                                     | •                                                  | $V_0^0 = 3.3 \text{ V}$                        |      | 0.92         |      | W        |

| parameter                                                                                       | conditions/description                                                                                               | <u> </u>                                                                                         | min  | typ                      | max          | units           |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------|--------------------------|--------------|-----------------|

| input standby power (P <sub>CTRL</sub> )                                                        | turned off with CTRL-pin                                                                                             | default configuration:<br>monitoring enabled,<br>precise timing enabled                          |      | 170                      |              | mW              |

| internal input capacitance (C <sub>i</sub> )                                                    |                                                                                                                      |                                                                                                  |      | 70                       |              | μF              |

| internal output capacitance (C <sub>o</sub> )                                                   |                                                                                                                      |                                                                                                  |      | 200                      |              | μF              |

| total external output<br>capacitance (C <sub>OUT</sub> )                                        | see note 9                                                                                                           |                                                                                                  | 300  |                          | 15,000       | μF              |

| ESR range of capacitors<br>(per single capacitor) (C <sub>out</sub> )                           | see note 9                                                                                                           |                                                                                                  | 5    |                          | 30           | mΩ              |

| load transient peak voltage deviation (L to H/H to L) load step 25-75-25% of max $I_o(V_{tr1})$ | default configuration<br>di/dt = $2 \text{ A/µs C}_0 = 470 \text{ µF (minimum external capacitance)}$<br>see note 12 | $V_o = 0.6 \text{ V}$<br>$V_o = 1.0 \text{ V}$<br>$V_o = 1.8 \text{ V}$<br>$V_o = 3.3 \text{ V}$ |      | 115<br>122<br>143<br>174 |              | mV<br>mV<br>mV  |

| load transient recovery time note 5 (L to H/H to L) load step 25-75-25% of max $I_o(t_{tr1})$   | default configuration<br>di/dt = $2 \text{ A/µs C}_0 = 470$<br>µF (minimum external<br>capacitance)<br>see note 12   | $V_o = 0.6 \text{ V}$<br>$V_o = 1.0 \text{ V}$<br>$V_o = 1.8 \text{ V}$<br>$V_o = 3.3 \text{ V}$ |      | 60<br>65<br>115<br>130   |              | µs<br>µs<br>µs  |

| switching frequency (f <sub>s</sub> )                                                           |                                                                                                                      |                                                                                                  |      | 320                      |              | kHz             |

| switching frequency range (f <sub>s</sub> )                                                     | PMBus configurable                                                                                                   |                                                                                                  |      | 200-640                  |              | kHz             |

| switching frequency set-point accuracy (f <sub>s</sub> )                                        |                                                                                                                      |                                                                                                  | -5   |                          | 5            | %               |

| control circuit PWM duty cycle                                                                  |                                                                                                                      |                                                                                                  | 5    |                          | 95           | %               |

| minimum sync pulse width                                                                        |                                                                                                                      |                                                                                                  | 150  |                          |              | ns              |

| input clock frequency drift<br>tolerance                                                        | external clock source                                                                                                |                                                                                                  | -13  |                          | 13           | %               |

|                                                                                                 | UVLO threshold                                                                                                       |                                                                                                  |      | 3.85                     |              | V               |

|                                                                                                 | UVLO threshold range                                                                                                 | PMBus configurable                                                                               |      | 3.85-14                  |              | V               |

|                                                                                                 | set point accuracy                                                                                                   |                                                                                                  | -150 |                          | 150          | mV              |

| input under voltage lockout,                                                                    | UVLO hysteresis                                                                                                      |                                                                                                  |      | 0.35                     |              | V               |

| UVLO                                                                                            | UVLO hysteresis range                                                                                                | PMBus configurable                                                                               |      | 0-10.15                  |              | V               |

|                                                                                                 | delay                                                                                                                |                                                                                                  |      | 2.5                      |              | μs              |

|                                                                                                 | fault response                                                                                                       | see note 3                                                                                       |      | automatic re             | start, 70 ms |                 |

|                                                                                                 | IOVP threshold                                                                                                       |                                                                                                  |      | 16                       |              | V               |

|                                                                                                 | IOVP threshold range                                                                                                 | PMBus configurable                                                                               |      | 4.2-16                   |              | V               |

|                                                                                                 | set point accuracy                                                                                                   |                                                                                                  | -150 |                          | 150          | mV              |

| input over voltage protection,                                                                  | IOVP hysteresis                                                                                                      |                                                                                                  |      | 1                        |              | V               |

| IOVP                                                                                            | IOVP hysteresis range                                                                                                | PMBus configurable                                                                               |      | 0-11.8                   |              | V               |

|                                                                                                 | delay                                                                                                                |                                                                                                  |      | 2.5                      |              | μs              |

|                                                                                                 | fault response                                                                                                       | see note 3                                                                                       |      | automatic re             | start, 70 ms |                 |

|                                                                                                 | PG threshold                                                                                                         |                                                                                                  |      | 90                       |              | %V <sub>0</sub> |

| L DO                                                                                            | PG hysteresis                                                                                                        |                                                                                                  |      | 5                        |              | %V <sub>0</sub> |

| power good, PG, see note 2                                                                      | PG delay                                                                                                             |                                                                                                  |      | direct after DL0         |              | ms              |

|                                                                                                 | PG delay range                                                                                                       | PMBus configurable                                                                               |      | 0-500                    |              | S               |

**date** 12/21/2015 | **page** 14 of 32

| parameter                                            | conditions/description      | n                         | min  | typ           | max           | units           |

|------------------------------------------------------|-----------------------------|---------------------------|------|---------------|---------------|-----------------|

|                                                      | UVP threshold               |                           |      | 85            |               | %V <sub>°</sub> |

|                                                      | UVP threshold range         | PMBus configurable        |      | 0-100         |               | %V <sub>°</sub> |

|                                                      | UVP hysteresis              |                           |      | 5             |               | %V <sub>。</sub> |

| output voltage over/under                            | OVP threshold               |                           |      | 115           |               | %V <sub>。</sub> |

| voltage protection, OVP/UVP                          | OVP threshold range         | PMBus configurable        |      | 100-115       |               | %V <sub>。</sub> |

|                                                      | UVP/OVP response time       |                           |      | 25            |               | μs              |

|                                                      | UVP/OVP response time range | PMBus configurable        |      | 5-60          |               | μs              |

|                                                      | fault response              | see note 3                |      | automatic re  | start, 70 ms  |                 |

|                                                      | OCP threshold               |                           |      | 32            |               | Α               |

|                                                      | OCP threshold range         | PMBus configurable        |      | 0-32          |               | Α               |

| over current protection, OCP                         | protection delay            | see note 4                |      | 32            |               | T <sub>sw</sub> |

|                                                      | protection delay range      | PMBus configurable        |      | 1-32          |               | T <sub>sw</sub> |

|                                                      | fault response              | see note 3                |      | automatic re  | start, 70 ms  |                 |

|                                                      | OTP threshold               |                           |      | 120           |               | °C              |

|                                                      | OTP threshold range         | PMBus configurable        | -40  |               | 125           | °C              |

| over temperature protection,<br>OTP at P2 see note 8 | OTP hysteresis              |                           |      | 25            |               | °C              |

|                                                      | OTP hysteresis range        | PMBus configurable        |      | 0-165         |               | °C              |

|                                                      | fault response              | see note 3                |      | automatic res | start, 240 ms |                 |

| ogic input low threshold(V <sub>IL</sub> )           | CVNC CAO CA1 CCL C          | DA DDC CTDL VCET          |      |               | 0.8           | V               |

| ogic input high threshold $(V_{IH})$                 | SYNC, SA0, SA1, SCL, S      | DA, DDC, CIRL, VSEI       | 2    |               |               | V               |

| logic input low sink current( ${ m I_{IL}}$ )        | CTRL                        |                           |      |               | 0.6           | mA              |

| ogic output low signal level<br>(V <sub>oL</sub> )   |                             |                           |      |               | 0.4           | V               |

| ogic output high signal level<br>(V <sub>он</sub> )  | SYNC, SCL, SDA, SALER       | T DDC BG                  | 2.25 |               |               | V               |

| ogic output low sink current $(I_{OL})$              | STINE, SEL, SDA, SALLK      | 1, DDC, FG                |      |               | 4             | mA              |

| ogic output high source current $(I_{OH})$           |                             |                           |      |               | 2             | mA              |

| setup time, SMBus(t <sub>SET</sub> )                 | see note 1                  |                           | 300  |               |               | ns              |

| nold time, SMBus(t <sub>hold</sub> )                 | see note 1                  |                           | 250  |               |               | ns              |

| ous free time, SMBus(t <sub>free</sub> )             | see note 1                  |                           | 2    |               |               | ms              |

| internal capacitance on logic pins $(C_p)$           |                             |                           |      | 10            |               | pF              |

| initialization time                                  |                             | see note 10               |      | 40            |               | ms              |

|                                                      | delay duration              | see note 16               |      | 10            |               | ms              |

| output voltage delay time see                        | delay duration range        | PMBus configurable        |      | 5-500,000     |               | ms              |

| note 6                                               | delay accuracy turn-on      |                           |      | -0.25/+4      |               | ms              |

|                                                      | delay accuracy turn-off     |                           |      | -0.25/+4      |               | ms              |

|                                                      | ramp duration               |                           |      | 10            |               | ms              |

| autaut voltago rama timo                             | ramp duration range         | PMBus configurable        |      | 0-200         |               | ms              |

| output voltage ramp time<br>see note 13              |                             |                           |      | 100           |               | μs              |

|                                                      | ramp time accuracy          | current sharing operation |      | 20            |               | %               |

# PRODUCT ELECTRICAL SPECIFICATION, VERTICAL (CONTINUED)

| parameter                                        | conditions/descriptio                                        | n                                                                                                            | min     | typ                     | max       | units |

|--------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------|-------------------------|-----------|-------|

| VTRK input bias current                          | V <sub>VTRK</sub> = 5.5 V                                    |                                                                                                              |         | 110                     | 200       | μΑ    |

| VTDV has alsing an area of account of            | 100% tracking, see note                                      | e 7                                                                                                          | -100    |                         | 100       | mV    |

| VTRK tracking ramp accuracy $(V_o - V_{VTRK})$   | current sharing operation $V_0 = 1.0 \text{ V}$ , 10 ms ramp | nn 2 phases, 100% tracking                                                                                   |         | ±100                    |           | mV    |

| VTRK regulation accuracy                         | 100% Tracking                                                |                                                                                                              | -1      |                         | 1         | %     |

| $(V_O - V_{VTRK})$                               | current sharing operation                                    | on 100% Tracking                                                                                             | -2      |                         | 2         | %     |

| current difference between products in a current | steady state operation                                       |                                                                                                              | Max 2 x | READ_IOUT m<br>accuracy | onitoring |       |

| sharing group                                    | ramp-up                                                      |                                                                                                              |         | 2                       |           | А     |

| number of products in a current sharing group    |                                                              |                                                                                                              |         |                         | 7         |       |

|                                                  | READ_VIN vs V <sub>I</sub>                                   |                                                                                                              |         | 3                       |           | %     |

|                                                  | READ_VOUT vs V <sub>0</sub>                                  |                                                                                                              |         | 1                       |           | %     |

| monitoring accuracy                              | READ_IOUT vs I <sub>o</sub>                                  | $I_{o} = 0-20 \text{ A}, T_{p_{1}} = 0 \text{ to } +95$<br>$V_{I} = 4.5-14 \text{ V}, V_{o} = 1.0 \text{ V}$ | °C      | ±1.7                    |           | А     |

|                                                  | READ_IOUT vs I <sub>o</sub>                                  | $I_0 = 0-20 \text{ A}, T_{p_1} = 0 \text{ to } +95$<br>$V_1 = 4.5-14 \text{ V}, V_0 = 0.6-3.3$               | °C<br>V | ±3                      |           | А     |

Notes:

- 1: See section  $I^2C/\mathsf{SMBus}$  Setup and Hold Times Definitions. 2: Monitorable over PMBus Interface.

- 3: Automatic restart  $\sim$ 70 or 240 ms after fault if the fault is no longer present. Continuous restart attempts if the fault reappear after restart.

- 5: Automatic Festal Control of 240 in a ster fault in the fault is no longer present. Continuous restal attempts in the fault reappear after restal.

5: Within +/-3% of VO

6: See section Soft-start Power Up.

7: Tracking functionality is designed to follow a VTRK signal with slew rate < 2.4 V/ms. For faster VTRK signals accuracy will depend on the regulator bandwidth.

- 8: See section Over Temperature Protection (OTP). 9: See section External Capacitors.

- 10: See section Initialization Procedure.

- 11: See graph Output Ripple vs External Capacitance and Operating information section Output Ripple and Noise.

12: See graph Load Transient vs. External Capacitance and Operating information section External Capacitors.

- 13: Time for reaching 100% of nominal Vout.

- 14: For Vout < 1.0 V accuracy is +/-10 mV. For further deviations see section Output Voltage Adjust using PMBus.

- 15: Accuracy here means deviation from ideal output voltage level given by configured droop and actual load. Includes line, load and temperature variations.

16: For current sharing the Output Voltage Delay Time must be reconfigured to minimum 15 ms.

17: For steady state operation above 1.05 x 3.3 V, please contact your local CUI sales representative.

# Efficiency vs. Output Current, V<sub>I</sub> = 5 V

# Efficiency vs. Output Current, V<sub>I</sub> = 12 V

# $T_{P1} = +25$ °C, $V_{I}$ =12 V, $f_{sw}$ = 320 kHz, $C_{O}$ = 470 $\mu$ F/10 m $\Omega$ .

# Efficiency vs. Output Current and **Switching Frequency**

Default configuration except changed frequency

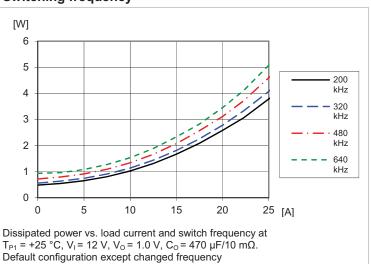

# Power Dissipation vs. Output Current, V<sub>I</sub> = 5 V

# Power Dissipation vs. Output Current, V<sub>I</sub> = 12 V