## CY2077

High-Accuracy One-Time Programmable Single-PLL Clock Generator

### Features

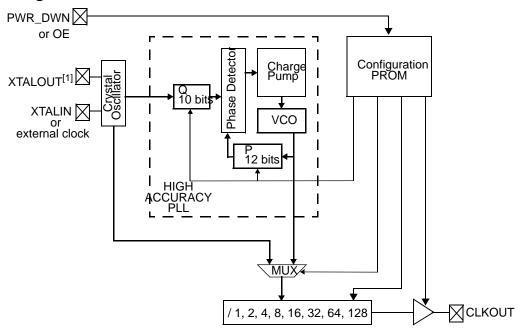

- High-accuracy PLL with 12-bit multiplier and 10-bit divider

- One-time programmability

- 3.3 V or 5 V operation

- Operating frequency

390 kHz–133 MHz at 5 V

390 kHz–100 MHz at 3.3 V

- Reference input from either a 10 MHz–30 MHz fundamental toned crystal or a 1 MHz–75 MHz external clock

- PROM selectable TTL or CMOS duty cycle levels

- Sixteen selectable post-divide options, using either PLL or reference oscillator/external clock

- Programmable PWR\_DWN or OE pin, with asynchronous or synchronous modes

- Low jitter outputs typically □ 80 ps at 3.3 V/5 V

- Controlled rise and fall times and output slew rate

- Available in both commercial and industrial temperature ranges

- Factory programmable device options

### **Functional Description**

For a complete list of related documentation, click here.

### Logic Block Diagram

Note

1. When using an external clock source, leave XTALOUT floating.

198 Champion Court

## Contents

| Pinouts                                | 3  |

|----------------------------------------|----|

| Pin Definitions                        | 3  |

| Functional Overview                    | 4  |

| PROM Configuration Block               | 4  |

| PLL Output Frequency                   | 4  |

| Power Management Features              | 4  |

| Absolute Maximum Ratings               | 5  |

| Operating Conditions                   | 5  |

| Electrical Characteristics             | 6  |

| Output Clock Switching Characteristics |    |

| - Commercial                           | 7  |

| Operating Conditions                   | 8  |

| Electrical Characteristics             | 9  |

| Output Clock Switching Characteristics |    |

| - Industrial                           | 10 |

|                                        |    |

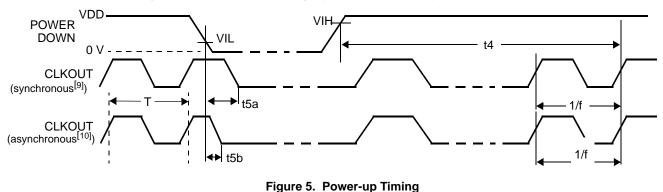

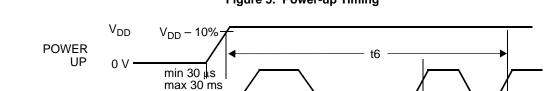

| Switching Waveforms                     | 12 |

|-----------------------------------------|----|

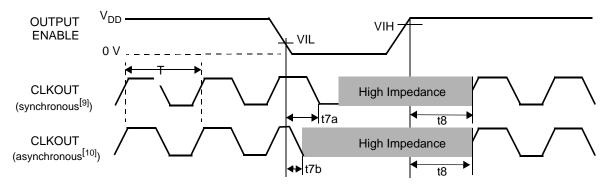

| Typical Rise/Fall Time Trends           | 13 |

| Typical Duty Cycle Trends               |    |

| Typical Jitter Trends                   |    |

| Programming Procedures                  |    |

| Ordering Information                    |    |

| Package Diagrams                        | 17 |

| Document History Page                   |    |

| Sales, Solutions, and Legal Information | 20 |

| Worldwide Sales and Design Support      |    |

| Products                                | 20 |

| PSoC® Solutions                         |    |

| Cypress Developer Community             |    |

| Technical Support                       |    |

|                                         |    |

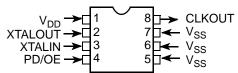

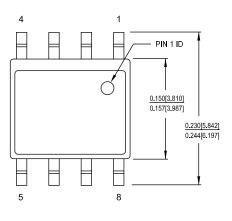

## **Pinouts**

### Figure 1. 8-pin SOIC pinout (Top View)

## **Pin Definitions**

8-pin SOIC

| Pin Name        | Pin     | Pin Description                                                                                                |

|-----------------|---------|----------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> | 1       | Voltage supply                                                                                                 |

| V <sub>SS</sub> | 5, 6, 7 | Ground (all the pins must be grounded)                                                                         |

| X <sub>D</sub>  | 2       | Crystal output (leave this pin floating when external reference is used)                                       |

| X <sub>G</sub>  | 3       | Crystal input or external input reference                                                                      |

| PWR_DWN / OE    | 4       | One-time programmable power-down or output enable pin. PWR_DWN is active low. OE is active high. Weak pull-up. |

| CLKOUT          | 8       | Clock output. Weak pull-down                                                                                   |

### **Functional Overview**

CY2077 is an one-time programmable, high-accuracy, general-purpose, PLL-based design for use in applications such as modems, disk drives, CD-ROM drives, video CD players, DVD players, games, set-top boxes, and data/telecommunications.

CY2077 can generate a clock output up to 133 MHz at 5 V or 100 MHz at 3.3 V. It has been designed to give the customer a very accurate and stable clock frequency with little to zero PPM error. CY2077 contains a 12-bit feedback counter divider and 10-bit reference counter divider to obtain a very high resolution to meet the needs of stringent design specifications. Furthermore, there are eight output divide options of /1, /2, /4, /8, /16, /32, /64, and /128. The output divider can select between the PLL and crystal oscillator output/external clock, providing a total of 16 different options to add more flexibility in designs. TTL or CMOS duty cycles can be selected.

Power management with the CY2077 is also very flexible. The user can choose either a PWR\_DWN, or an OE feature with which both have integrated pull up resistors. PWR\_DWN and OE signals can be programmed to have asynchronous and synchronous timing with respect to the output signal. There is a weak pull down on the output that pulls CLKOUT LOW when either the PWR\_DWN or OE signal is LOW. This weak pull down can easily be overridden by another clock signal in designs where multiple clock signals share a signal path.

Multiple options for output selection, better power distribution layout, and controlled rise and fall times enable the CY2077 to be used in applications that require low jitter and accurate reference frequencies.

### PROM Configuration Block

#### Table 1. PROM Adjustable Features

| PROM Adjustable Features              |                                                       |  |  |  |  |

|---------------------------------------|-------------------------------------------------------|--|--|--|--|

| Adjust                                | Feedback counter value (P)                            |  |  |  |  |

| Freq.                                 | Reference counter value (Q)                           |  |  |  |  |

|                                       | Output divider selection                              |  |  |  |  |

|                                       | Duty cycle levels (TTL or CMOS)                       |  |  |  |  |

| Power management mode (OE or PWR_DWN) |                                                       |  |  |  |  |

| Power man                             | Power management timing (synchronous or asynchronous) |  |  |  |  |

#### Table 2. Device Functionality: Output Frequencies

| Symbol | Description      | Condition                     | Min  | Мах | Unit |

|--------|------------------|-------------------------------|------|-----|------|

| Fo     | Output frequency | V <sub>DD</sub> = 4.5 V–5.5 V | 0.39 | 133 | MHz  |

|        |                  | V <sub>DD</sub> = 3.0 V–3.6 V | 0.39 | 100 | MHz  |

#### Note

### PLL Output Frequency

CY2077 contains a high-resolution PLL with 12-bit multiplier and 10-bit divider<sup>[2]</sup>. The output frequency of the PLL is determined by the following formula:

$$\mathsf{F}_{\mathsf{PLL}} = \frac{2 \bullet (\mathsf{P} + 5)}{(\mathsf{Q} + 2)} \bullet \mathsf{F}_{\mathsf{REF}}$$

where P is the feedback counter value and Q is the reference counter value. P and Q are One-Time programmable values.

The calculation of P and Q values for a given PLL output frequency is handled by the CyberClocks<sup>™</sup> software. Refer to Programming Procedures on page 16 for details.

#### **Power Management Features**

PWR\_DWN and OE options are configurable by PROM programming for the CY2077. In PWR\_DWN mode, all active circuits are powered down when the control pin is set LOW. When the control pin is set back HIGH, both the PLL and oscillator circuit must relock. In the case of OE, the output is three-stated and weakly pulled down when the control pin is set LOW. The oscillator and PLL are still active in this state, which leads to a quick clock output return when the control pin is set back HIGH.

Additionally, PWR\_DWN and OE can be configured to occur asynchronously or synchronously with respect to CLKOUT. In asynchronous mode, PWR\_DWN or OE disables CLKOUT immediately (allowing for logic delays), without respect to the current state of CLKOUT. Synchronous mode prevents output glitches by waiting for the next falling edge of CLKOUT after PWR\_DWN, or OE becomes asserted. In either asynchronous or synchronous setting, the output is always enabled synchronously by waiting for the next falling edge of CLKOUT.

<sup>2.</sup> When using CyClocks, note that the PLL frequency range is from 50 MHz to 250 MHz for 5 V V<sub>DD</sub> supply, and 50 MHz to 180 MHz for 3 V V<sub>DD</sub> supply. The output frequency is determined by the selected output divider.

## **Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested. Supply voltage ......-0.5 to +7.0 V

| Input voltage                                           | –0.5 V to V <sub>DD</sub> +0.5 V |

|---------------------------------------------------------|----------------------------------|

| Storage temperature (non-con                            | densing) –55°C to +150°C         |

| Junction temperature                                    | 150°C                            |

| Static discharge voltage<br>(per MIL-STD-883, method 30 | 15)≥ 2000 V                      |

## **Operating Conditions**

For Commercial Temperature Device

| Parameter         | Description                                                                                                       | Min  | Max | Unit |

|-------------------|-------------------------------------------------------------------------------------------------------------------|------|-----|------|

| V <sub>DD</sub>   | Supply voltage                                                                                                    | 3.0  | 5.5 | V    |

| Τ <sub>Α</sub>    | Operating temperature, ambient                                                                                    | 0    | +70 | °C   |

| C <sub>TTL</sub>  | Max. capacitive load on outputs for TTL levels<br>V <sub>DD</sub> = 4.5 V–5.5 V, output frequency = 1 MHz–40 MHz  | _    | 50  | pF   |

|                   | V <sub>DD</sub> = 4.5 V–5.5 V, output frequency = 40 MHz–125 MHz                                                  | _    | 25  | pF   |

|                   | V <sub>DD</sub> = 4.5 V–5.5 V, output frequency = 125 MHz–133 MHz                                                 | _    | 15  | pF   |

| C <sub>CMOS</sub> | Max. capacitive load on outputs for CMOS levels<br>V <sub>DD</sub> = 4.5 V–5.5 V, output frequency = 1 MHz–40 MHz | _    | 50  | pF   |

|                   | V <sub>DD</sub> = 4.5 V–5.5 V, output frequency = 40 MHz–125 MHz                                                  | _    | 25  | pF   |

|                   | V <sub>DD</sub> = 4.5 V–5.5 V, output frequency = 125 MHz–133 MHz                                                 | _    | 15  | pF   |

|                   | V <sub>DD</sub> = 3.0 V–3.6 V, output frequency = 1 MHz–40 MHz                                                    | _    | 30  | pF   |

|                   | V <sub>DD</sub> = 3.0 V–3.6 V, output frequency = 40 MHz–100 MHz                                                  | _    | 15  | pF   |

| X <sub>REF</sub>  | Reference frequency, input crystal with C <sub>load</sub> = 10 pF                                                 | 10   | 30  | MHz  |

|                   | Reference frequency, external clock source                                                                        | 1    | 75  | MHz  |

| t <sub>PU</sub>   | Power-up time for all VDD's to reach minimum specified voltage (power ramps must be monotonic)                    | 0.05 | 50  | ms   |

## **Electrical Characteristics**

## $T_A = 0 \ ^{\circ}C \ to +70 \ ^{\circ}C$

| Parameter                       | Description                          | Test Conditions                                                                     | Min                   | Тур | Max                   | Unit |

|---------------------------------|--------------------------------------|-------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| V <sub>IL</sub>                 | Low-level input voltage              | V <sub>DD</sub> = 4.5 V–5.5 V                                                       | -                     | _   | 0.8                   | V    |

|                                 |                                      | V <sub>DD</sub> = 3.0 V–3.6 V                                                       | -                     | _   | 0.2 × V <sub>DD</sub> | V    |

| V <sub>IH</sub>                 | High-level input voltage             | V <sub>DD</sub> = 4.5 V–5.5 V                                                       | 2.0                   | _   | -                     | V    |

|                                 |                                      | V <sub>DD</sub> = 3.0 V–3.6 V                                                       | $0.7 \times V_{DD}$   | _   | -                     | V    |

| V <sub>OL</sub>                 | Low-level output voltage             | V <sub>DD</sub> = 4.5 V–5.5 V, I <sub>OL</sub> = 16 mA                              | -                     | -   | 0.4                   | V    |

|                                 |                                      | V <sub>DD</sub> = 3.0 V–3.6 V, I <sub>OL</sub> = 8 mA                               | -                     | -   | 0.4                   | V    |

| V <sub>OHCMOS</sub>             | High-level output voltage CMOS       | V <sub>DD</sub> = 4.5 V–5.5 V, I <sub>OH</sub> = –16 mA                             | V <sub>DD</sub> - 0.4 | _   | -                     | V    |

|                                 | levels                               | V <sub>DD</sub> = 3.0 V–3.6 V, I <sub>OH</sub> = –8 mA                              | V <sub>DD</sub> - 0.4 | -   | -                     | V    |

| V <sub>OHTTL</sub>              | High-level output voltage TTL levels | V <sub>DD</sub> = 4.5 V–5.5 V, I <sub>OH</sub> = –8 mA                              | 2.4                   | -   | -                     | V    |

| IIL                             | Input low current                    | V <sub>IN</sub> = 0 V                                                               | -                     | _   | 10                    | μΑ   |

| I <sub>IH</sub>                 | Input high current                   | $V_{IN} = V_{DD}$                                                                   | -                     | _   | 5                     | μΑ   |

| I <sub>DD</sub>                 | Power supply current Unloaded        | $V_{DD} = 4.5 V-5.5 V,$<br>output frequency $\leq 133 MHz$                          | -                     | _   | 45                    | mA   |

|                                 |                                      | $V_{DD} = 3.0 V-3.6 V,$<br>output frequency $\leq 100 MHz$                          | -                     | -   | 25                    | mA   |

| I <sub>DDS</sub> <sup>[3]</sup> | Stand-by current (PD = 0)            | V <sub>DD</sub> = 4.5 V–5.5 V                                                       | -                     | 25  | 100                   | μΑ   |

|                                 |                                      | V <sub>DD</sub> = 3.0 V–3.6 V                                                       | -                     | 10  | 50                    | μΑ   |

| R <sub>UP</sub>                 | Input pull-up resistor               | $V_{DD} = 4.5 \text{ V} - 5.5 \text{ V}, \text{ V}_{IN} = 0 \text{ V}$              | 1.1                   | 3.0 | 8.0                   | MΩ   |

|                                 |                                      | $V_{DD} = 4.5 \text{ V} - 5.5 \text{ V}, \text{ V}_{IN} = 0.7 \times \text{V}_{DD}$ | 50                    | 100 | 200                   | kΩ   |

| I <sub>OE_CLKOUT</sub>          | CLKOUT pull-down current             | V <sub>DD</sub> = 5.0 V                                                             | -                     | 20  | -                     | μΑ   |

# **Output Clock Switching Characteristics - Commercial**

Over the Operating Range <sup>[4]</sup>

| Parameter       | Description                                                | Test Conditions                                                                                     | Min | Тур | Max    | Unit |

|-----------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----|-----|--------|------|

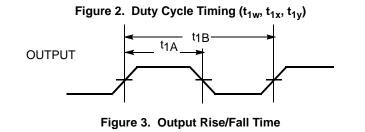

| t <sub>1w</sub> | Output duty cycle at 1.4 V,                                | 1 MHz–40 MHz, C <sub>L</sub> <u>≤</u> 50 pF                                                         | 45  | -   | 55     | %    |

|                 | $V_{DD} = 4.5 V - 5.5 V,$<br>$t_{1w} = t_{1A} \div t_{1B}$ | 40 MHz–125 MHz, C <sub>L</sub> <u>≤</u> 25 pF                                                       | 45  | -   | 55     | %    |

|                 |                                                            | 125 MHz–133 MHz, C <sub>L</sub> <u>≤</u> 15 pF                                                      | 45  | -   | 55     | %    |

| t <sub>1x</sub> | Output duty cycle at V <sub>DD</sub> /2,                   | 1 MHz–40 MHz, C <sub>L</sub> <u>≤</u> 50 pF                                                         | 45  | -   | 55     | %    |

|                 | $V_{DD} = 4.5 V - 5.5 V,$<br>$t_{1x} = t_{1A} \div t_{1B}$ | 40 MHz–125 MHz, C <sub>L</sub> <u>≤</u> 25 pF                                                       | 45  | -   | 55     | %    |

|                 |                                                            | 125 MHz–133 MHz, C <sub>L</sub> <u>≤</u> 15 pF                                                      | 45  | -   | 55     | %    |

| t <sub>1y</sub> | Output duty cycle at V <sub>DD</sub> /2,                   | 1 MHz–40 MHz, C <sub>L</sub> <u>≤</u> 30 pF                                                         | 45  | -   | 55     | %    |

|                 | $V_{DD} = 3.0 V - 3.6 V,$<br>$t_{1y} = t_{1A} \div t_{1B}$ | 40 MHz–100 MHz, C <sub>L</sub> ≤ 15 pF                                                              | 40  | _   | 60     | %    |

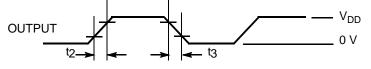

| t <sub>2</sub>  | Output clock rise time                                     | Between 0.8 V–2.0 V,<br>V <sub>DD</sub> = 4.5 V–5.5 V, C <sub>L</sub> = 50 pF                       | -   | _   | 1.8    | ns   |

|                 |                                                            | Between 0.8 V–2.0 V,<br>V <sub>DD</sub> = 4.5 V–5.5 V, C <sub>L</sub> = 25 pF                       | -   | _   | 1.2    | ns   |

|                 |                                                            | Between 0.8 V–2.0 V,<br>V <sub>DD</sub> = 4.5 V–5.5 V, C <sub>L</sub> = 15 pF                       | -   | -   | 0.9    | ns   |

|                 |                                                            | Between 0.2 × $V_{DD}$ to 0.8 × $V_{DD}$ ,<br>$V_{DD}$ = 4.5 V–5.5 V, $C_L$ = 50 pF                 | -   | -   | 3.4    | ns   |

|                 |                                                            | Between 0.2 × $V_{DD}$ to 0.8 × $V_{DD}$ ,<br>V <sub>DD</sub> = 3.0 V-3.6 V, C <sub>L</sub> = 30 pF | _   | -   | 4.0    | ns   |

|                 |                                                            | Between 0.2 × $V_{DD}$ to 0.8 × $V_{DD}$ ,<br>V <sub>DD</sub> = 3.0 V–3.6 V, C <sub>L</sub> = 15 pF | _   | -   | 2.4    | ns   |

| t <sub>3</sub>  | Output clock fall time                                     | Between 0.8 V –2.0 V,<br>V <sub>DD</sub> = 4.5 V–5.5 V, C <sub>L</sub> = 50 pF                      | _   | -   | 1.8    | ns   |

|                 |                                                            | Between 0.8 V – 2.0 V,<br>V <sub>DD</sub> = 4.5 V–5.5 V, C <sub>L</sub> = 25 pF                     | _   | -   | 1.2    | ns   |

|                 |                                                            | Between 0.8 V–2.0 V,<br>V <sub>DD</sub> = 4.5 V–5.5 V, C <sub>L</sub> = 15 pF                       | _   | -   | 0.9    | ns   |

|                 |                                                            | Between 0.2 × $V_{DD}$ to 0.8 × $V_{DD}$ ,<br>$V_{DD}$ = 4.5 V–5.5 V, C <sub>L</sub> = 50 pF        | _   | -   | 3.4    | ns   |

|                 |                                                            | Between 0.2 × $V_{DD}$ to 0.8 × $V_{DD}$ ,<br>$V_{DD}$ = 3.0 V–3.6 V, C <sub>L</sub> = 30 pF        | _   | -   | 4.0    | ns   |

|                 |                                                            | Between 0.2 × $V_{DD}$ to 0.8 × $V_{DD}$ ,<br>$V_{DD}$ = 3.0 V-3.6 V, C <sub>L</sub> = 15 pF        | _   | -   | 2.4    | ns   |

| t <sub>4</sub>  | Startup time out of power-down                             | PWR_DWN pin LOW to HIGH <sup>[5]</sup>                                                              | _   | 1   | 2      | ms   |

| t <sub>5a</sub> | Power-down delay time<br>(synchronous setting)             | PWR_DWN pin LOW to output LOW<br>(T = period of output CLK)                                         | _   | T/2 | T + 10 | ns   |

| t <sub>5b</sub> | Power-down delay time<br>(asynchronous setting)            | PWR_DWN pin LOW to output LOW                                                                       | _   | 10  | 15     | ns   |

| t <sub>6</sub>  | Power-up time                                              | From power-on <sup>[5]</sup>                                                                        | -   | 1   | 2      | ms   |

#### Notes

4. Not all parameters measured in production testing.

5. Oscillator start time can not be guaranteed for all crystal types. This specification is for operation with AT cut crystals with ESR < 70 Ω.</li>

## Output Clock Switching Characteristics - Commercial (continued)

## Over the Operating Range <sup>[4]</sup>

| Parameter       | Description                                       | Test Conditions                                                                       | Min | Тур  | Max               | Unit         |

|-----------------|---------------------------------------------------|---------------------------------------------------------------------------------------|-----|------|-------------------|--------------|

| t <sub>7a</sub> | Output disable time<br>(synchronous setting)      | OE pin LOW to output high-Z<br>(T = period of output CLK)                             | -   | T/2  | T + 10            | ns           |

| t <sub>7b</sub> | Output disable time<br>(asynchronous setting)     | OE pin LOW to output high-Z                                                           | -   | 10   | 15                | ns           |

| t <sub>8</sub>  | Output enable time<br>(always synchronous enable) | OE pin LOW to HIGH<br>(T = period of output CLK)                                      | -   | Т    | (1.5 × T) +<br>25 | ns           |

| t <sub>9</sub>  | Peak-to-peak period jitter                        | V <sub>DD</sub> = 3.0 V–3.6 V, 4.5 V–5.5 V,<br>Fo > 33 MHz, V <sub>CO</sub> > 100 MHz | -   | 80   | 150               | ps           |

|                 |                                                   | V <sub>DD</sub> = 3.0 V–5.5 V, Fo < 33 MHz                                            | _   | 0.3% | 1%                | % of $F_{O}$ |

## **Operating Conditions**

### For Industrial Temperature Device

| Parameter         | Description                                                                                                       | Min  | Мах | Unit |

|-------------------|-------------------------------------------------------------------------------------------------------------------|------|-----|------|

| V <sub>DD</sub>   | Supply voltage                                                                                                    | 3.0  | 5.5 | V    |

| T <sub>A</sub>    | Operating temperature, ambient                                                                                    | -40  | +85 | °C   |

| C <sub>TTL</sub>  | Max. capacitive load on outputs for TTL levels<br>V <sub>DD</sub> = 4.5 V–5.5 V, output frequency = 1 MHz–40 MHz  | _    | 35  | pF   |

|                   | V <sub>DD</sub> = 4.5 V–5.5 V, output frequency = 40 MHz–125 MHz                                                  | -    | 15  | pF   |

|                   | V <sub>DD</sub> = 4.5 V–5.5 V, output frequency = 125 MHz–133 MHz                                                 | -    | 10  | pF   |

| C <sub>CMOS</sub> | Max. capacitive load on outputs for CMOS levels<br>V <sub>DD</sub> = 4.5 V–5.5 V, output frequency = 1 MHz–40 MHz | _    | 35  | pF   |

|                   | V <sub>DD</sub> = 4.5 V–5.5 V, output frequency = 40 MHz–125 MHz                                                  | -    | 15  | pF   |

|                   | V <sub>DD</sub> = 4.5 V–5.5 V, output frequency = 125 MHz–133 MHz                                                 | -    | 10  | pF   |

|                   | V <sub>DD</sub> = 3.0 V–3.6 V, output frequency = 1 MHz–40 MHz                                                    | -    | 20  | pF   |

|                   | V <sub>DD</sub> = 3.0 V–3.6 V, output frequency = 40 MHz–100 MHz                                                  | -    | 10  | pF   |

| X <sub>REF</sub>  | Reference frequency, input crystal with C <sub>load</sub> = 10 pF                                                 | 10   | 30  | MHz  |

|                   | Reference frequency, external clock source                                                                        | 1    | 75  | MHz  |

| t <sub>PU</sub>   | Power-up time for all VDD's to reach minimum specified voltage (power ramps must be monotonic)                    | 0.05 | 50  | ms   |

## **Electrical Characteristics**

## $T_A = -40 \text{ °C to } +85 \text{ °C}$

| Parameter                       | Description                              | Test Conditions                                                                     | Min                   | Тур | Max                   | Unit |

|---------------------------------|------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| V <sub>IL</sub>                 | Low-level input voltage                  | V <sub>DD</sub> = 4.5 V–5.5 V                                                       | -                     | _   | 0.8                   | V    |

|                                 |                                          | V <sub>DD</sub> = 3.0 V–3.6 V                                                       | -                     | _   | 0.2 × V <sub>DD</sub> | V    |

| V <sub>IH</sub>                 | High-level input voltage                 | V <sub>DD</sub> = 4.5 V–5.5 V                                                       | 2.0                   | _   | -                     | V    |

|                                 |                                          | V <sub>DD</sub> = 3.0 V–3.6 V                                                       | $0.7 \times V_{DD}$   | _   | -                     | V    |

| V <sub>OL</sub>                 | Low-level output voltage                 | V <sub>DD</sub> = 4.5 V–5.5 V, I <sub>OL</sub> = 16 mA                              | -                     | -   | 0.4                   | V    |

|                                 |                                          | V <sub>DD</sub> = 3.0 V–3.6 V, I <sub>OL</sub> = 8 mA                               | -                     | -   | 0.4                   | V    |

| V <sub>OHCMOS</sub>             | DS High-level output voltage,            | V <sub>DD</sub> = 4.5 V–5.5 V, I <sub>OH</sub> = –16 mA                             | V <sub>DD</sub> - 0.4 | _   | -                     | V    |

|                                 | CMOS levels                              | V <sub>DD</sub> = 3.0 V–3.6 V, I <sub>OH</sub> = –8 mA                              | V <sub>DD</sub> - 0.4 | -   | -                     | V    |

| V <sub>OHTTL</sub>              | High-level output voltage,<br>TTL levels | V <sub>DD</sub> = 4.5 V–5.5 V, I <sub>OH</sub> = –8 mA                              | 2.4                   | -   | -                     | V    |

| IIL                             | Input low current                        | V <sub>IN</sub> = 0 V                                                               | -                     | _   | 10                    | μΑ   |

| I <sub>IH</sub>                 | Input high current                       | $V_{IN} = V_{DD}$                                                                   | -                     | _   | 5                     | μΑ   |

| I <sub>DD</sub>                 | Power supply current, Unloaded           | $V_{DD} = 4.5 V-5.5 V,$<br>output frequency $\leq 133 \text{ MHz}$                  | -                     | -   | 45                    | mA   |

|                                 |                                          | $V_{DD} = 3.0 V-3.6 V,$<br>output frequency $\leq 100 MHz$                          | -                     | -   | 25                    | mA   |

| I <sub>DDS</sub> <sup>[6]</sup> | Stand-by current (PD = 0)                | V <sub>DD</sub> = 4.5 V–5.5 V                                                       | -                     | 25  | 100                   | μΑ   |

|                                 |                                          | V <sub>DD</sub> = 3.0 V–3.6 V                                                       | -                     | 10  | 50                    |      |

| R <sub>UP</sub>                 | Input pull-up resistor                   | V <sub>DD</sub> = 4.5 V–5.5 V, V <sub>IN</sub> = 0 V                                | 1.1                   | 3.0 | 8.0                   | MΩ   |

|                                 |                                          | $V_{DD} = 4.5 \text{ V} - 5.5 \text{ V}, \text{ V}_{IN} = 0.7 \times \text{V}_{DD}$ | 50                    | 100 | 200                   | kΩ   |

| I <sub>OE_CLKOUT</sub>          | CLKOUT pull-down current                 | V <sub>DD</sub> = 5.0 V                                                             | -                     | 20  | -                     | μΑ   |

# **Output Clock Switching Characteristics - Industrial**

Over the Operating Range [7]

| Parameter       | Description                                                | Test Conditions                                                                              | Min | Тур | Max    | Unit |

|-----------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----|-----|--------|------|

| t <sub>1w</sub> | Output duty cycle at 1.4 V,                                | 1 MHz–40 MHz, C <sub>L</sub> <u>≤</u> 35 pF                                                  | 45  | -   | 55     | %    |

|                 | $V_{DD} = 4.5 V - 5.5 V,$<br>$t_{1w} = t_{1A} \div t_{1B}$ | 40 MHz–125 MHz, C <sub>L</sub> <u>≤</u> 15 pF                                                | 45  | -   | 55     | %    |

|                 |                                                            | 125 MHz–133 MHz, C <sub>L</sub> <u>≤</u> 10 pF                                               | 45  | -   | 55     | %    |

| t <sub>1x</sub> | Output duty cycle at V <sub>DD</sub> /2,                   | 1 MHz–40 MHz, C <sub>L</sub> <u>≤</u> 35 pF                                                  | 45  | -   | 55     | %    |

|                 | $V_{DD} = 4.5 V - 5.5 V,$<br>$t_{1x} = t_{1A} \div t_{1B}$ | 40 MHz–125 MHz, C <sub>L</sub> <u>≤</u> 15 pF                                                | 45  | -   | 55     | %    |

|                 |                                                            | 125 MHz–133 MHz, C <sub>L</sub> <u>&lt;</u> 10 pF                                            | 45  | -   | 55     | %    |

| t <sub>1y</sub> | Output duty cycle at $V_{DD}/2$ ,                          | 1 MHz–40 MHz, C <sub>L</sub> <u>≤</u> 20 pF                                                  | 45  | -   | 55     | %    |

|                 | $V_{DD} = 3.0 V - 3.6 V,$<br>$t_{1y} = t_{1A} \div t_{1B}$ | 40 MHz–100 MHz, C <sub>L</sub> <u>≤</u> 10 pF                                                | 40  | _   | 60     | %    |

| t <sub>2</sub>  | Output clock rise time                                     | Between 0.8 V–2.0 V,<br>V <sub>DD</sub> = 4.5 V–5.5 V, C <sub>L</sub> = 35 pF                | _   | _   | 1.8    | ns   |

|                 |                                                            | Between 0.8 V– 2.0 V,<br>V <sub>DD</sub> = 4.5 V–5.5 V, C <sub>L</sub> = 15 pF               | _   | -   | 1.2    | ns   |

|                 |                                                            | Between 0.8 V–2.0 V,<br>V <sub>DD</sub> = 4.5 V–5.5 V, C <sub>L</sub> = 10 pF                | -   | -   | 0.9    | ns   |

|                 |                                                            | Between 0.2 × $V_{DD}$ to 0.8 × $V_{DD}$ ,<br>$V_{DD}$ = 4.5 V–5.5 V, C <sub>L</sub> = 35 pF | -   | -   | 3.4    | ns   |

|                 |                                                            | Between 0.2 × $V_{DD}$ to 0.8 × $V_{DD}$ ,<br>$V_{DD}$ = 3.0 V–3.6 V, C <sub>L</sub> = 20 pF | -   | -   | 4.0    | ns   |

|                 |                                                            | Between 0.2 × $V_{DD}$ to 0.8 × $V_{DD}$ ,<br>$V_{DD}$ = 3.0 V-3.6 V, C <sub>L</sub> = 10 pF | _   | -   | 2.4    | ns   |

| t <sub>3</sub>  | Output clock fall time                                     | Between 0.8 V–2.0 V,<br>V <sub>DD</sub> = 4.5 V–5.5 V, C <sub>L</sub> = 35 pF                | _   | -   | 1.8    | ns   |

|                 |                                                            | Between 0.8 V–2.0 V,<br>V <sub>DD</sub> = 4.5 V–5.5 V, C <sub>L</sub> = 15 pF                | _   | -   | 1.2    | ns   |

|                 |                                                            | Between 0.8 V–2.0 V,<br>V <sub>DD</sub> = 4.5 V–5.5 V, C <sub>L</sub> = 10 pF                | _   | -   | 0.9    | ns   |

|                 |                                                            | Between 0.2 × $V_{DD}$ to 0.8 × $V_{DD}$ ,<br>$V_{DD}$ = 4.5 V–5.5 V, C <sub>L</sub> = 35 pF | -   | -   | 3.4    | ns   |

|                 |                                                            | Between 0.2 × $V_{DD}$ to 0.8 × $V_{DD}$ ,<br>$V_{DD}$ = 3.0 V–3.6 V, C <sub>L</sub> = 20 pF | -   | -   | 4.0    | ns   |

|                 |                                                            | Between 0.2 × $V_{DD}$ to 0.8 × $V_{DD}$ ,<br>$V_{DD}$ = 3.0 V–3.6 V, C <sub>L</sub> = 10 pF | _   | -   | 2.4    | ns   |

| t <sub>4</sub>  | Startup time out of Power-down                             | PWR_DWN pin LOW to HIGH <sup>[8]</sup>                                                       | _   | 1   | 2      | ms   |

| t <sub>5a</sub> | Power-down delay time<br>(synchronous setting)             | PWR_DWN pin LOW to output LOW<br>(T = period of output clk)                                  | _   | T/2 | T + 10 | ns   |

| t <sub>5b</sub> | Power-down delay time<br>(asynchronous setting)            | PWR_DWN pin LOW to output LOW                                                                | _   | 10  | 15     | ns   |

| t <sub>6</sub>  | Power-up time                                              | From power on <sup>[8]</sup>                                                                 | -   | 1   | 2      | ms   |

#### Notes

Not all parameters measured in production testing.

Oscillator start time can not be guaranteed for all crystal types. This specification is for operation with AT cut crystals with ESR < 70Ω.</li>

## Output Clock Switching Characteristics - Industrial (continued)

Over the Operating Range <sup>[7]</sup>

| Parameter       | Description                                       | Test Conditions                                                                       | Min | Тур  | Max               | Unit       |

|-----------------|---------------------------------------------------|---------------------------------------------------------------------------------------|-----|------|-------------------|------------|

| t <sub>7a</sub> | Output Disable time<br>(synchronous setting)      | OE pin LOW to output high-Z<br>(T = period of output clk)                             | -   | T/2  | T + 10            | ns         |

| t <sub>7b</sub> | Output Disable time<br>(asynchronous setting)     | OE pin LOW to output high-Z                                                           | -   | 10   | 15                | ns         |

| t <sub>8</sub>  | Output Enable time<br>(always synchronous enable) | OE pin LOW to HIGH<br>(T = period of output clk)                                      | -   | Т    | (1.5 × T) +<br>25 | ns         |

| t <sub>9</sub>  | Peak-to-peak period jitter                        | V <sub>DD</sub> = 3.0 V–3.6 V, 4.5 V–5.5 V,<br>Fo > 33 MHz, V <sub>CO</sub> > 100 MHz | -   | 80   | 150               | ps         |

|                 |                                                   | V <sub>DD</sub> = 3.0 V – 5.5 V, Fo < 33 MHz                                          | _   | 0.3% | 1%                | % of $F_O$ |

## **Switching Waveforms**

Figure 4. Power-down Timing (synchronous and asynchronous modes)

Figure 6. Output Enable Timing (synchronous and asynchronous modes)

#### Notes

In synchronous mode, the power-down or output three-state is not initiated until the next falling edge of the output clock.

In asynchronous mode, the power-down or output three-state occurs within 25 ns regardless of position in the output clock cycle.

CLKOUT

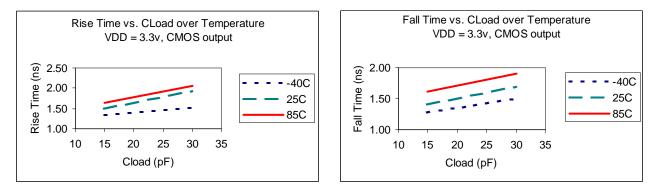

## **Typical Rise/Fall Time Trends**

For CY2077 [11]

Figure 7. Rise/Fall Time vs. VDD over Temperatures

Figure 8. Rise/Fall Time vs. Output Loads over Temperatures

#### Note

11. Rise/Fall time for CMOS output is measured between 1.2  $V_{DD}$  and 0.8 x  $V_{DD}$ . Rise/Fall time for TTL output is measured between 0.8 V and 2.0 V.

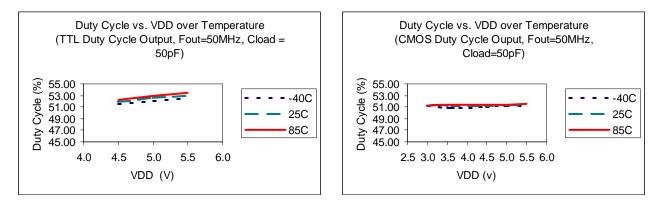

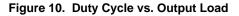

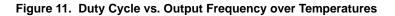

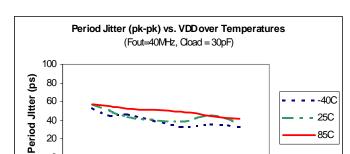

## **Typical Duty Cycle Trends**

For CY2077 [12]

Figure 9. Duty Cycle vs. V<sub>DD</sub> over Temperatures

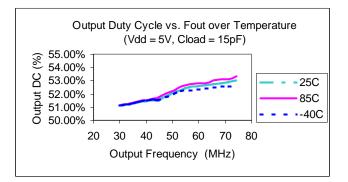

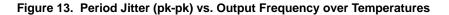

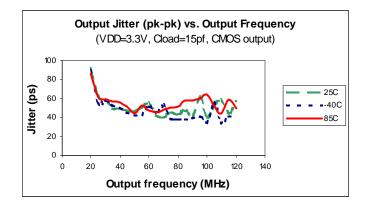

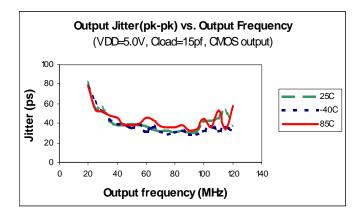

## **Typical Jitter Trends**

For CY2077

40

20 0 2.5

3.0

3.5

4.0

VDD(V)

- 25C

6.0

85C

Figure 12. Period Jitter (pk-pk) vs.  $V_{\text{DD}}$  over Temperatures

4.5

5.0

5.5

### **Programming Procedures**

Currently the CY2077 is available only as a field-programmable device, as indicated by an "F" in the ordering code.

Devices may be programmed using the CY3672-USB programmer, or through programmers available from third party programmer manufacturers such as Hi-Lo Systems and BP Micro. Programming services are also available from third parties, including some Cypress distribution partners.

To generate a JEDEC format programming file, customers must use CyClocks software. This software automatically calculates

the output frequencies that can be generated by CY2077 devices. The CyClocks software is a subset of the larger software tool CyberClocks, which is available free of charge from the Cypress web site (http://www.cypress.com). CyberClocks is installed on a PC and must not be confused with the web-based application CyberClocks Online.

For high volume designs, factory programming of customer-specific configurations is available on other 8-pin devices such as the CY22180, CY22801 and CY22381. Factory programming is no longer offered for new designs using the CY2077.

### **Ordering Information**

| Ordering Code <sup>[14]</sup> | Package Name                                                   | Package Type               | Operating Temperature Range                          | Operating Voltage |  |  |  |

|-------------------------------|----------------------------------------------------------------|----------------------------|------------------------------------------------------|-------------------|--|--|--|

| Pb-Free                       | ²b-Free                                                        |                            |                                                      |                   |  |  |  |

| CY2077FSXC                    | S8                                                             | 8-pin SOIC                 | Commercial (T = 0 °C to 70 °C)                       | 3.3 V or 5 V      |  |  |  |

| CY2077FSXCT                   | S8                                                             | 8-pin SOIC –Tape and Reel  | Commercial (T = 0 °C to 70 °C)                       | 3.3 V or 5 V      |  |  |  |

| CY2077FZZ                     | Z8                                                             | 8-pin TSSOP                | Commercial (T = 0 °C to 70 °C)                       | 3.3 V or 5 V      |  |  |  |

| CY2077FZXI                    | Z8                                                             | 8-pin TSSOP                | Industrial (T = $-40 \text{ °C to } 85 \text{ °C}$ ) | 3.3 V or 5 V      |  |  |  |

| CY2077FZXIT                   | Z8                                                             | 8-pin TSSOP –Tape and Reel | Industrial (T = $-40 \text{ °C to } 85 \text{ °C}$ ) | 3.3 V or 5 V      |  |  |  |

| Programmer                    |                                                                |                            |                                                      |                   |  |  |  |

| CY3672-USB                    | Programming Kit                                                |                            |                                                      |                   |  |  |  |

| CY3696                        | Socket adapter board, for programming CY2077FS (SOIC Package)  |                            |                                                      |                   |  |  |  |

| CY3697                        | Socket adapter board, for programming CY2077FZ (TSSOP Package) |                            |                                                      |                   |  |  |  |

#### Table 3. Obsolete or Not For New Designs

|                        | Original Device                          | Replacement Device |                           |  |

|------------------------|------------------------------------------|--------------------|---------------------------|--|

| Ordering Code [13, 14] | Description                              | Ordering Code      | Description               |  |

| CY2077SC-xxx           |                                          | none               |                           |  |

| CY2077SC-xxxT          |                                          | none               |                           |  |

| CY2077SI-xxx           |                                          | none               |                           |  |

| CY2077SI-xxxT          |                                          | none               |                           |  |

| CY2077SXC-xxx          |                                          | none               |                           |  |

| CY2077SXC-xxxT         |                                          | none               |                           |  |

| CY2077ZC-xxx           |                                          | none               |                           |  |

| CY2077ZC-xxxT          |                                          | none               |                           |  |

| CY2077ZI-xxx           |                                          | none               |                           |  |

| CY2077ZI-xxxT          |                                          | none               |                           |  |

| CY2077ZXC-xxx          |                                          | none               |                           |  |

| CY2077ZXC-xxxT         |                                          | none               |                           |  |

| CY2077FSI              | SOIC, Industrial (T = $-40$ °C to 85 °C) | CY2077FSXC         | Pb-free SOIC, Commercial  |  |

| CY2077FZ               | TSSOP, Commercial (T = 0 °C to 70 °C)    | CY2077FZZ          | Pb-free TSSOP, Commercial |  |

| CY2077FZI              | TSSOP, Industrial (T = -40 °C to 85 °C)  | CY2077FZXI         | Pb-free TSSOP, Industrial |  |

#### Notes

<sup>13.</sup> The CY2077SC-xxx(T), CY2077SI-xxx(T), CY2077SXC-xxx(T), CY2077ZC-xxx(T), CY2077ZI-xxx(T) and CY2077ZXC-xxx(T), are factory programmed configurations. Factory programming is available for high-volume design opportunities. For more details, contact your local Cypress FAE or Cypress Sales Representative.

<sup>14.</sup> The CY2077F are field programmable. For more details, contact your local Cypress FAE or Cypress Sales Representative.

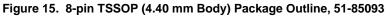

## **Package Diagrams**

### Figure 14. 8-pin SOIC (150 Mils) Package Outline, 51-85066

- 1. DIMENSIONS IN INCHES[MM] MIN. MAX.

- 2. PIN 1 ID IS OPTIONAL, ROUND ON SINGLE LEADFRAME RECTANGULAR ON MATRIX LEADFRAME

- 3. REFERENCE JEDEC MS-012

- 4. PACKAGE WEIGHT 0.07gms

| PART #  |               |  |

|---------|---------------|--|

| S08.15  | STANDARD PKG  |  |

| SZ08.15 | LEAD FREE PKG |  |

| SW8.15  | LEAD FREE PKG |  |

51-85066 \*H

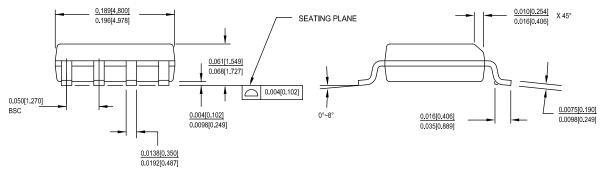

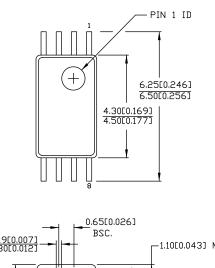

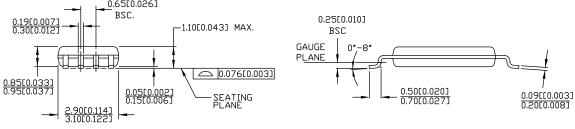

### Package Diagrams (continued)

DIMENSIONS IN MMEINCHES] MIN. MAX.

REFERENCE JEDEC MD-153

|          | PART #         |

|----------|----------------|

| Z08.173  | STANDARD PKG.  |

| ZZ08.173 | LEAD FREE PKG. |

51-85093 \*E

## **Document History Page**

| Revision | ECN     | Orig. of<br>Change | Sumbission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 111727  | DSG                | 02/07/02           | Convert from Spec number: 38-01009 to 38-07210                                                                                                                                                                                                                                                                                                                                                                                          |

| *A       | 114938  | CKN                | 07/24/02           | Added table and notes to page 11                                                                                                                                                                                                                                                                                                                                                                                                        |

| *В       | 121843  | RBI                | 12/14/02           | Power up requirements added to Operating Conditions Information                                                                                                                                                                                                                                                                                                                                                                         |

| *C       | 2104546 | PYG/KVM<br>/AESA   | See ECN            | Updated Ordering Information table<br>Replaced the "Custom Configuration Request Procedure" section with<br>"Programming Procedures"<br>Updated package diagrams                                                                                                                                                                                                                                                                        |

| *D       | 2631183 | KVM /<br>AESA      | 01/06/09           | CY2077FS removed from the active part number table.<br>Added CY2077FZXI and CY2077FZXIT to the Ordering Information table.<br>Corrected wording on p. 2 about when the weak output pull-down is active.<br>Added to Table 1 to indicate that PWR_DWN is active low and OE is active<br>high.<br>Updated to new template.                                                                                                                |

| *E       | 2905892 | СХQ                | 04/07/10           | Updated Ordering Information:<br>Updated Table 3:<br>Removed inactive part CY2077FS.<br>Updated Package Diagrams:<br>spec 51-85066 – Changed revision from *C to *D.<br>spec 51-85093 – Changed revision from *A to *B.                                                                                                                                                                                                                 |

| *F       | 3388539 | MNSB /<br>PURU     | 09/29/11           | Updated Programming Procedures:<br>Replaced "CY3670" with "CY3672-USB".<br>Updated Ordering Information:<br>Updated part numbers.<br>Updated Package Diagrams:<br>spec 51-85066 – Changed revision from *D to *E.<br>spec 51-85093 – Changed revision from *B to *C.                                                                                                                                                                    |

| *G       | 3514611 | PURU               | 02/01/2012         | Removed Benefits.<br>Updated Package Diagrams:<br>spec 51-85093 – Changed revision from *C to *D.                                                                                                                                                                                                                                                                                                                                       |

| *H       | 4575273 | PURU               | 11/20/2014         | Updated Functional Description:<br>Added "For a complete list of related documentation, click here." at the enc<br>Updated Package Diagrams:<br>spec 51-85066 – Changed revision from *E to *F.<br>spec 51-85093 – Changed revision from *D to *E.                                                                                                                                                                                      |

| *        | 4694396 | TAVA               | 03/20/2015         | Updated Package Diagrams:<br>spec 51-85066 – Changed revision from *F to *G.<br>Updated to new template.                                                                                                                                                                                                                                                                                                                                |

| *Ј       | 5766130 | PSR                | 06/07/2017         | Updated Document Title to read as "CY2077, High-Accuracy One-Time<br>Programmable Single-PLL Clock Generator".<br>Replaced "EPROM Programmable" with "One-time Programmable" in all<br>instances across the document.<br>Replaced "EPROM" with "PROM" in all instances across the document.<br>Updated Logic Block Diagram.<br>Updated Package Diagrams:<br>spec 51-85066 – Changed revision from *G to *H.<br>Updated to new template. |

### Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

### Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

### **PSoC<sup>®</sup> Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2002–2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and other countries thereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software is not accompanied by a license products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware solely for use with Cypress hardware solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuctitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

#### Document Number: 38-07210 Rev. \*J

#### Revised June 7, 2017

Page 20 of 20

PSoC Designer<sup>™</sup> is a trademark and PSoC® and CapSense® are registered trademarks of Cypress Semiconductor Corporation. Purchase of I<sup>2</sup>C components from Cypress or one of its sublicensed Associated Companies conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips. As from October 1st, 2006 Philips Semiconductors has a new trade name - NXP Semiconductors.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Phase Locked Loops - PLL category:

Click to view products by Cypress manufacturer:

Other Similar products are found below :

HMC700LP4TR CPLL58-2400-2500 MB15E07SLPFV1-G-BND-6E1 PI6C2409-1HWEX BA4116FV-E2 HMC820LP6CETR HMC828LP6CETR LMX2430TMX/NOPB HMC837LP6CETR HMC831LP6CETR NB3N5573DTG ADF4153ABCPZ PI6C2405A-1LE CD74HC4046AM CPLL66-2450-2450 NJM567D CY23S05SXI-1 STW81200T ADF4208BRUZ ADF4218LBRUZ ADF4355-3BCPZ ADF5355BCPZ ADF4355BCPZ ADF4169WCCPZ ADF4360-7BCPZ ADF4360-6BCPZ ADF4360-5BCPZRL7 ADF4360-5BCPZ ADF4360-4BCPZRL7 ADF4360-4BCPZ ADF4360-3BCPZ ADF4360-2BCPZRL7 ADF4252BCPZ ADF4159CCPZ ADF4169CCPZ ADF4252BCPZ-R7 ADF4360-0BCPZ ADF4360-1BCPZ ADF4360-1BCPZRL7 ADF4360-2BCPZRL7 ADF4360-2BCPZRL7 ADF4360-3BCPZRL7 ADF4360-7BCPZRL7 ADF4360-8BCPZ ADF4360-8BCPZRL7 ADF4360-9BCPZ ADF4360-9BCPZRL7 ADF4159CCPZ-RL7 ADF4159WCCPZ ADF4360-0BCPZRL7 AD9901KPZ