# 2.5 V or 3.3 V, 10 MHz–220 MHz, Low Jitter, Nine-Output Zero Delay Buffer

#### **Features**

- 10 MHz to 220 MHz maximum operating range

- Zero input-output propagation delay, adjustable by loading on CLKOUT pin

- Multiple low-skew outputs

- □ 45 ps typical output-output skew

- □ One input drives nine outputs, grouped as 4 + 4 + 1

- 25 ps typical cycle-to-cycle jitter

- 15 ps typical period jitter

- Standard and High drive strength options

- Available in space-saving 16-pin 150-mil small outline integrated circuit (SOIC) or 4.4 mm thin shrunk small outline package (TSSOP) packages

- 3.3 V or 2.5 V operation

- Industrial temperature available

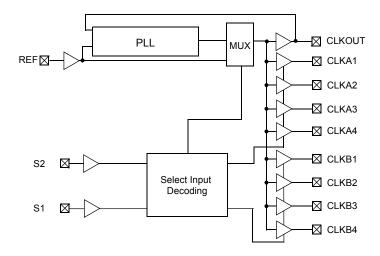

#### **Functional Description**

The CY23EP09 is a 2.5 V or 3.3 V zero delay buffer designed to distribute high-speed clocks and is available in a 16-pin SOIC or TSSOP package. The -1H version operates up to 220 (200) MHz frequencies at 3.3 V (2.5 V), and has higher drive than the -1 devices. All parts have on-chip PLLs that lock to an input clock on the REF pin. The phase-locked loop (PLL) feedback is on-chip and is obtained from the CLKOUT pad.

There are two banks of four outputs each, which can be controlled by the Select inputs as shown in the Select Input Decoding on page 4. If all output clocks are not required, BankB can be three-stated. The select inputs also allow the input clock to be directly applied to the outputs for chip and system testing purposes.

The PLL enters a power-down mode when there are no rising edges on the REF input (less than  $\sim$ 2 MHz). In this state, the outputs are three-stated and the PLL is turned off, resulting in less than 25  $\mu$ A of current draw.

In the special case when S2:S1 is 1:0, the PLL is bypassed and REF is output from DC to the maximum allowable frequency. The part behaves like a non-zero delay buffer in this mode, and the outputs are not tri-stated.

The CY23EP09 is available in different configurations, as shown in the Ordering Information table. The CY23EP09-1 is the base part. The CY23EP09-1H is the high-drive version of the -1, and its rise and fall times are much faster than the -1.

These parts are not intended for 5 V input-tolerant applications For a complete list of related documentation, click here.

#### **Block Diagram**

#### **Contents**

| Pin Configuration                   | 3 |

|-------------------------------------|---|

| Pin Definitions                     |   |

| Select Input Decoding               | 4 |

| Zero Delay and Skew Control         |   |

| Absolute Maximum Conditions         | 5 |

| Operating Conditions                | 5 |

| Electrical Specifications           |   |

| Electrical Specifications           |   |

| Thermal Resistance                  |   |

| Test Circuits                       |   |

| Electrical Specifications           |   |

| Switching Waveforms                 |   |

| Supplemental Parametric Information |   |

| Ordering Information                    | 15 |

|-----------------------------------------|----|

| Ordering Code Definitions               |    |

| Package Diagrams                        |    |

| Acronyms                                | 17 |

| Document Conventions                    | 17 |

| Units of Measure                        | 17 |

| Document History Page                   | 18 |

| Sales, Solutions, and Legal Information | 19 |

| Worldwide Sales and Design Support      | 19 |

| Products                                | 19 |

| PSoC®Solutions                          | 19 |

| Cypress Developer Community             | 19 |

| Technical Support                       |    |

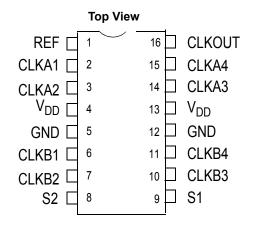

### **Pin Configuration**

Figure 1. 16-pin SOIC or TSSOP pinout (Top View)

### **Pin Definitions**

| Pin No. | Signal               | Description                                    |

|---------|----------------------|------------------------------------------------|

| 1       | REF [1]              | Input reference frequency                      |

| 2       | CLKA1 [2]            | Buffered clock output, Bank A                  |

| 3       | CLKA2 <sup>[2]</sup> | Buffered clock output, Bank A                  |

| 4       | $V_{DD}$             | 3.3 V or 2.5 V supply                          |

| 5       | GND                  | Ground                                         |

| 6       | CLKB1 [2]            | Buffered clock output, Bank B                  |

| 7       | CLKB2 <sup>[2]</sup> | Buffered clock output, Bank B                  |

| 8       | S2 <sup>[3]</sup>    | Select input, bit 2                            |

| 9       | S1 <sup>[3]</sup>    | Select input, bit 1                            |

| 10      | CLKB3 <sup>[2]</sup> | Buffered clock output, Bank B                  |

| 11      | CLKB4 <sup>[2]</sup> | Buffered clock output, Bank B                  |

| 12      | GND                  | Ground                                         |

| 13      | $V_{DD}$             | 3.3 V or 2.5 V supply                          |

| 14      | CLKA3 <sup>[2]</sup> | Buffered clock output, Bank A                  |

| 15      | CLKA4 <sup>[2]</sup> | Buffered clock output, Bank A                  |

| 16      | CLKOUT [2]           | Buffered output, internal feedback on this pin |

#### Notes

- 1. Weak pull-down.

- 2. Weak pull-down on all outputs.

- 3. Weak pull-ups on these inputs.

#### **Select Input Decoding**

| S2 | S1 | CLOCK A1-A4 | CLOCK B1-B4 | CLKOUT [4] | Output Source | PLL Shutdown |

|----|----|-------------|-------------|------------|---------------|--------------|

| 0  | 0  | Three-state | Three-state | Driven     | PLL           | N            |

| 0  | 1  | Driven      | Three-state | Driven     | PLL           | N            |

| 1  | 0  | Driven      | Driven      | Driven     | Reference     | Y            |

| 1  | 1  | Driven      | Driven      | Driven     | PLL           | N            |

#### **Zero Delay and Skew Control**

All outputs should be uniformly loaded to achieve Zero Delay between the input and output. Since the CLKOUT pin is the internal feedback to the PLL, its relative loading can adjust the input-output delay.

The output driving the CLKOUT pin will be driving a total load of 5 pF (internal load) plus any additional load externally connected to this pin. For applications requiring zero input-output delay, the total load on each output pin (including CLKOUT) must be the

same. For example, if there is no external load on CLKOUT pin, add 5 pF to each of the remaining outputs to match the internal load on CLKOUT pin. If input-output delay adjustments are required, the CLKOUT load may be changed to vary the delay between the REF input and remaining outputs.

For zero output-output skew, be sure to load all outputs equally. For further information refer to the application note titled "AN1234 – Understanding Cypress's Zero Delay Buffers".

#### Note

Document Number: 38-07760 Rev. \*G Page 4 of 19

<sup>4.</sup> This output is driven and has an internal feedback for the PLL. The load on this output can be adjusted to change the skew between the reference and output.

### **Absolute Maximum Conditions**

Supply voltage to ground potential .....-0.5 V to 4.6 V DC input voltage ...... $V_{SS}$  – 0.5 V to 4.6 V

| Storage temperature            | –65 °C to 150 °C |

|--------------------------------|------------------|

| Junction temperature           | 150 °C           |

| Static discharge voltage       |                  |

| (per MIL-STD-883, Method 3015) | > 2000 V         |

# **Operating Conditions**

| Parameter                     | Description                                                                                    | Min  | Max | Unit |

|-------------------------------|------------------------------------------------------------------------------------------------|------|-----|------|

| V <sub>DD3.3</sub>            | 3.3 V supply voltage                                                                           | 3.0  | 3.6 | V    |

| V <sub>DD2.5</sub>            | 2.5 V supply voltage                                                                           | 2.3  | 2.7 | V    |

| T <sub>A</sub>                | Operating temperature (ambient temperature) – Commercial                                       | 0    | 70  | °C   |

|                               | Operating temperature (ambient temperature) – Industrial                                       | -40  | 85  | °C   |

| C <sub>L</sub> <sup>[5]</sup> | Load capacitance, <100 MHz, 3.3 V                                                              | _    | 30  | pF   |

|                               | Load capacitance, <100 MHz, 2.5 V with High drive                                              | -    | 30  | pF   |

|                               | Load capacitance, <133.3 MHz, 3.3 V                                                            | -    | 22  | pF   |

|                               | Load capacitance, <133.3 MHz, 2.5 V with High drive                                            | -    | 22  | pF   |

|                               | Load capacitance, <133.3 MHz, 2.5 V with Standard drive                                        | -    | 15  | pF   |

|                               | Load capacitance, >133.3 MHz, 3.3 V                                                            | -    | 15  | pF   |

|                               | Load capacitance, >133.3 MHz, 2.5 V with High drive                                            | -    | 15  | pF   |

| C <sub>IN</sub>               | Input capacitance <sup>[6]</sup>                                                               | -    | 5   | pF   |

| BW                            | Closed-loop bandwidth (typical), 3.3 V                                                         | 1–   | 1.5 | MHz  |

|                               | Closed-loop bandwidth (typical), 2.5 V                                                         | 0    | .8  | MHz  |

| R <sub>OUT</sub>              | Output impedance (typical), 3.3 V High drive                                                   | 2    | 9   | Ω    |

|                               | Output impedance (typical), 3.3 V Standard drive                                               | 4    | 1   | Ω    |

|                               | Output impedance (typical), 2.5 V High drive                                                   | 3    | 7   | Ω    |

|                               | Output impedance (typical), 2.5 V Standard drive                                               |      | 1   | Ω    |

| t <sub>PU</sub>               | Power-up time for all VDD's to reach minimum specified voltage (power ramps must be monotonic) | 0.01 | 50  | ms   |

#### Notes

<sup>5.</sup> Applies to Test Circuit #1.6. Applies to both REF Clock and internal feedback path on CLKOUT.

# **Electrical Specifications**

3.3 V DC

| Parameter                 | Description               | Test Conditions                          | Min | Max                   | Unit |

|---------------------------|---------------------------|------------------------------------------|-----|-----------------------|------|

| $V_{DD}$                  | Supply voltage            |                                          | 3.0 | 3.6                   | V    |

| V <sub>IL</sub>           | Input LOW voltage         |                                          | _   | 0.8                   | V    |

| V <sub>IH</sub>           | Input HIGH voltage        |                                          | 2.0 | V <sub>DD</sub> + 0.3 | V    |

| I <sub>IL</sub>           | Input leakage current     | 0 < V <sub>IN</sub> < V <sub>IL</sub>    | _   | ±10                   | μΑ   |

| I <sub>IH</sub>           | Input HIGH current        | $V_{IN} = V_{DD}$                        | _   | 100                   | μΑ   |

| $V_{OL}$                  | Output LOW voltage        | I <sub>OL</sub> = 8 mA (standard drive)  | _   | 0.4                   | V    |

|                           |                           | I <sub>OL</sub> = 12 mA (High drive)     | _   | 0.4                   | V    |

| V <sub>OH</sub>           | Output HIGH voltage       | I <sub>OH</sub> = –8 mA (standard drive) | 2.4 | _                     | V    |

|                           |                           | I <sub>OH</sub> = –12 mA (High drive)    | 2.4 | _                     | V    |

| I <sub>DD</sub> (PD mode) | Power down supply current | REF = 0 MHz (Commercial)                 | _   | 12                    | μΑ   |

|                           |                           | REF = 0 MHz (Industrial)                 | _   | 25                    | μΑ   |

| I <sub>DD</sub>           | Supply current            | Unloaded outputs, 66-MHz REF             | _   | 30                    | mA   |

# **Electrical Specifications**

2.5 V DC

| Parameter                 | Description               | Test Conditions                          | Min                   | Max                   | Unit |

|---------------------------|---------------------------|------------------------------------------|-----------------------|-----------------------|------|

| $V_{DD}$                  | Supply voltage            |                                          | 2.3                   | 2.7                   | V    |

| V <sub>IL</sub>           | Input LOW voltage         |                                          | _                     | 0.7                   | V    |

| V <sub>IH</sub>           | Input HIGH voltage        |                                          | 1.7                   | V <sub>DD</sub> + 0.3 | V    |

| I <sub>IL</sub>           | Input leakage current     | 0 <v<sub>IN &lt; V<sub>DD</sub></v<sub>  | _                     | 10                    | μА   |

| I <sub>IH</sub>           | Input HIGH current        | $V_{IN} = V_{DD}$                        | _                     | 100                   | μА   |

| V <sub>OL</sub>           | Output LOW voltage        | I <sub>OL</sub> = 8 mA (Standard drive)  | _                     | 0.5                   | V    |

|                           |                           | I <sub>OL</sub> = 12 mA (High drive)     | _                     | 0.5                   | V    |

| V <sub>OH</sub>           | Output HIGH voltage       | I <sub>OH</sub> = –8 mA (Standard drive) | V <sub>DD</sub> – 0.6 | -                     | V    |

|                           |                           | I <sub>OH</sub> = -12 mA (High drive)    | V <sub>DD</sub> – 0.6 | -                     | V    |

| I <sub>DD</sub> (PD mode) | Power down supply current | REF = 0 MHz (Commercial)                 | _                     | 12                    | μА   |

|                           |                           | REF = 0 MHz (Industrial)                 | _                     | 25                    | μΑ   |

| I <sub>DD</sub>           | Supply current            | Unloaded outputs, 66-MHz REF             | _                     | 45                    | mA   |

### **Thermal Resistance**

| Parameter [7] | Description                           | Test Conditions                                                           | 16-pin SOIC | 16-pin TSSOP | Unit |

|---------------|---------------------------------------|---------------------------------------------------------------------------|-------------|--------------|------|

| - 3/1         | ,                                     | Test conditions follow standard test methods and procedures for measuring |             | 111          | °C/W |

| - 30          | Thermal resistance (junction to case) | thermal impedance, in accordance with EIA/JESD51.                         | 53          | 26           | °C/W |

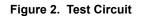

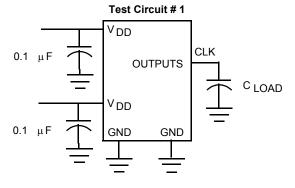

### **Test Circuits**

Note

7. These parameters are guaranteed by design and are not tested.

# **Electrical Specifications**

#### 3.3 V and 2.5 V AC

| Parameter                       | Description                               | Test Conditions                                                           | Min  | Тур | Max  | Unit |

|---------------------------------|-------------------------------------------|---------------------------------------------------------------------------|------|-----|------|------|

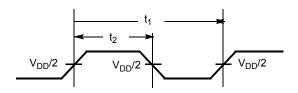

| 1/t <sub>1</sub>                | Maximum frequency [8]                     | 3.3 V High drive                                                          | 10   | _   | 220  | MHz  |

|                                 | (input/output)                            | 3.3 V Standard drive                                                      | 10   | _   | 167  | MHz  |

|                                 |                                           | 2.5 V High drive                                                          | 10   | -   | 200  | MHz  |

|                                 |                                           | 2.5 V Standard drive                                                      | 10   | -   | 133  | MHz  |

| T <sub>IDC</sub>                | Input duty cycle                          | <133.3 MHz                                                                | 25   | -   | 75   | %    |

|                                 |                                           | >133.3 MHz                                                                | 40   | _   | 60   | %    |

| t <sub>2</sub> ÷ t <sub>1</sub> | Output duty cycle [9]                     | <133.3 MHz                                                                | 47   | _   | 53   | %    |

|                                 |                                           | >133.3 MHz                                                                | 45   | _   | 55   | %    |

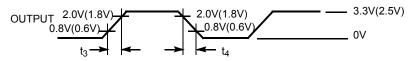

| t <sub>3,</sub> t <sub>4</sub>  | Rise, fall time (3.3 V) [9]               | Std drive, CL = 30 pF, <100 MHz                                           | _    | _   | 1.6  | ns   |

|                                 |                                           | Std drive, CL = 22 pF, <133.3 MHz                                         | _    | _   | 1.6  | ns   |

|                                 |                                           | Std drive, CL = 15 pF, <167 MHz                                           | _    | _   | 0.6  | ns   |

|                                 |                                           | High drive, CL = 30 pF, <100 MHz                                          | _    | -   | 1.2  | ns   |

|                                 |                                           | High drive, CL = 22 pF, <133.3 MHz                                        | _    | _   | 1.2  | ns   |

|                                 |                                           | High drive, CL = 15 pF, >133.3 MHz                                        | _    | _   | 0.5  | ns   |

| t <sub>3,</sub> t <sub>4</sub>  | Rise, fall time (2.5 V) <sup>[9]</sup>    | Std drive, CL = 15 pF, <133.33 MHz                                        | _    | _   | 1.5  | ns   |

|                                 |                                           | High drive, CL = 30 pF, <100 MHz                                          | _    | _   | 2.1  | ns   |

|                                 |                                           | High drive, CL = 22 pF, <133.3 MHz                                        | _    | _   | 1.3  | ns   |

|                                 |                                           | High drive, CL = 15 pF, >133.3 MHz                                        | _    | _   | 1.2  | ns   |

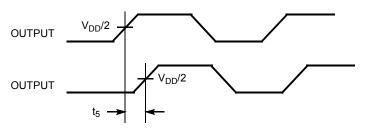

| t <sub>5</sub>                  | Output to output skew [9]                 | All outputs equally loaded,<br>3.3 V supply,<br>2.5 supply standard drive | -    | 45  | 100  | ps   |

|                                 |                                           | All outputs equally loaded,<br>2.5 V supply high drive                    | _    | _   | 110  | ps   |

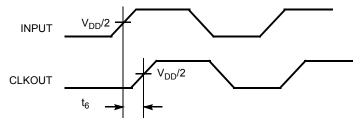

| t <sub>6</sub>                  | Delay,                                    | PLL Bypass mode                                                           | 1.5  | -   | 4.4  | ns   |

|                                 | REF rising edge to CLKOUT rising edge [9] | PLL enabled @ 3.3 V                                                       | -100 | -   | 100  | ps   |

|                                 | inemig sugs                               | PLL enabled @2.5 V                                                        | -200 | -   | 200  | ps   |

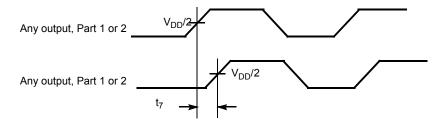

| t <sub>7</sub>                  | Part to part skew <sup>[9]</sup>          | Measured at V <sub>DD</sub> /2.<br>Any output to any output, 3.3 V supply | -    | _   | ±150 | ps   |

|                                 |                                           | Measured at V <sub>DD</sub> /2.<br>Any output to any output, 2.5 V supply | -    | _   | ±300 | ps   |

| t <sub>LOCK</sub>               | PLL lock time <sup>[9]</sup>              | Stable power supply, valid clocks presented on REF and CLKOUT pins        | -    | _   | 1.0  | ms   |

<sup>Notes

8. For the given maximum loading conditions. See C<sub>L</sub> in Operating Conditions Table.

9. Parameter is guaranteed by design and characterization. Not 100% tested in production.</sup>

### **Electrical Specifications** (continued)

#### 3.3 V and 2.5 V AC

| Parameter                            | Description                 | Test Conditions                                 | Min | Тур | Max | Unit |

|--------------------------------------|-----------------------------|-------------------------------------------------|-----|-----|-----|------|

| T <sub>JCC</sub> <sup>[10, 11]</sup> | Cycle-to-cycle jitter, peak | 3.3 V supply, >66 MHz, <15 pF                   | _   | 25  | 55  | ps   |

|                                      |                             | 3.3 V supply, >66 MHz, <30 pF, standard drive   | _   | 65  | 125 | ps   |

|                                      |                             | 3.3 V supply, >66 MHz, <30 pF, high drive       | _   | 53  | 100 | ps   |

|                                      |                             | 2.5 V supply, >66 MHz, <15 pF, standard drive   | _   | 35  | 95  | ps   |

|                                      |                             | 2.5 V supply, >66 MHz, <15 pF, high drive       | -   | 30  | 65  | ps   |

|                                      |                             | 2.5 V supply, >66 MHz, <30 pF, high drive       | _   | 75  | 145 | ps   |

|                                      |                             | S2:S1 = 1:0 mode, 3.3 V, <15 pF, standard drive | -   | 16  | _   | ps   |

|                                      |                             | S2:S1 = 1:0 mode, 3.3 V, <15 pF, high drive     | _   | 14  | _   | ps   |

|                                      |                             | S2:S1 = 1:0 mode, 2.5 V, <15 pF, standard drive | -   | 23  | -   | ps   |

|                                      |                             | S2:S1 = 1:0 mode, 2.5 V, <15 pF, high drive     | -   | 22  | _   | ps   |

| T <sub>PER</sub> <sup>[10, 11]</sup> | Period jitter, peak         | 3.3 V supply, 66–100 MHz, <15 pF                | -   | 20  | 75  | ps   |

|                                      |                             | 3.3 V supply, >100 MHz, <15 pF                  | _   | 15  | 45  | ps   |

|                                      |                             | 3.3 V supply, >66 MHz, <30 pF, standard drive   | _   | 40  | 100 | ps   |

|                                      |                             | 3.3 V supply, >66 MHz, <30 pF, high drive       | _   | 30  | 70  | ps   |

|                                      |                             | 2.5 V supply, >66 MHz, <15 pF, standard drive   | _   | 25  | 60  | ps   |

|                                      |                             | 2.5 V supply, 66–100 MHz, <15 pF, high drive    | _   | 25  | 60  | ps   |

|                                      |                             | 2.5 V supply, >100 MHz, <15 pF, high drive      | _   | 15  | 45  | ps   |

|                                      |                             | S2:S1 = 1:0 mode, 3.3 V, <15 pF, standard drive | _   | 28  | _   | ps   |

|                                      |                             | S2:S1 = 1:0 mode, 3.3 V, <15 pF, high drive     | _   | 24  | _   | ps   |

|                                      |                             | S2:S1 = 1:0 mode, 2.5 V, <15 pF, standard drive | _   | 40  | _   | ps   |

|                                      |                             | S2:S1 = 1:0 mode, 2.5 V, <15 pF, high drive     | _   | 37  | _   | ps   |

#### Notes

Parameter is guaranteed by design and characterization. Not 100% tested in production.

Parameter is guaranteed by design and characterization. Not 100% tested in production.

Typical jitter is measured at 3.3 V or 2.5 V, 29 °C, with all outputs driven into the maximum specified load. Further information regarding jitter specifications may be found in the application note "Understanding Data Sheet Jitter Specifications for Cypress Clock Products."

### **Switching Waveforms**

Figure 3. Duty Cycle Timing

Figure 4. All Outputs Rise/Fall Time

Figure 5. Output-Output Skew

Figure 6. Input-Output Propagation Delay

Figure 7. Part-Part Skew

#### **Supplemental Parametric Information**

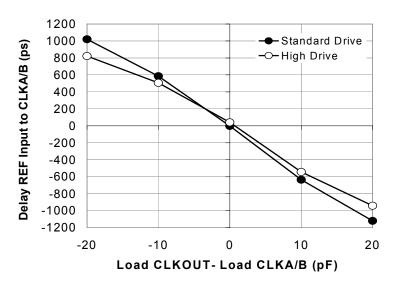

Figure 8. 2.5 V Typical Room Temperature Graph for REF Input to CLKA/CLKB Delay Versus Loading Difference between CLKOUT and CLKA/CLKB

Data is shown for 66 MHz. Delay is a weak function of frequency.

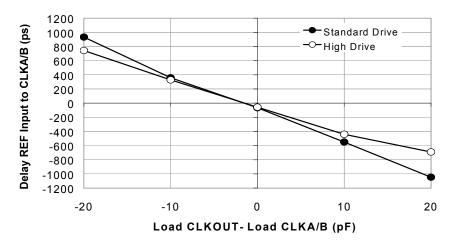

Figure 9. 3.3 V Typical Room Temperature Graph for REF Input to CLKA/CLKB Delay Versus Loading Difference between CLKOUT and CLKA/CLKB

Data is shown for 66 MHz. Delay is a weak function of frequency.

#### **Supplemental Parametric Information** (continued)

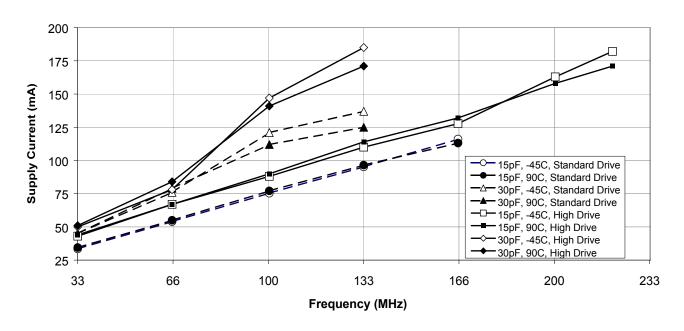

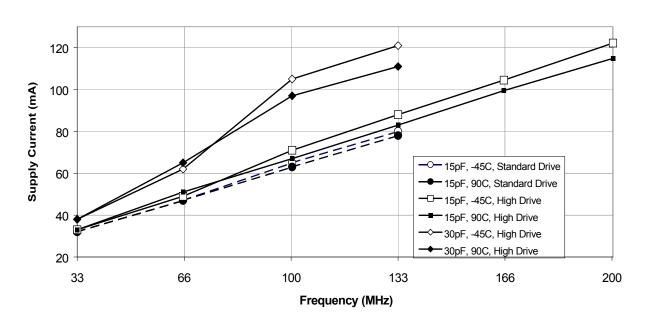

Figure 10. 3.6 V Measured Supply Current versus Frequency, Drive Strength, Loading, and Temperature

Note that the 30-pF data above 100 MHz is beyond the data sheet specification of 22 pF.

Figure 11. 2.7 V Measured Supply Current Versus Frequency, Drive Strength, Loading, and Temperature

Note that the 30-pF high-drive data above 100bMHz is beyond the data sheet specification of 22 pF.

#### **Supplemental Parametric Information** (continued)

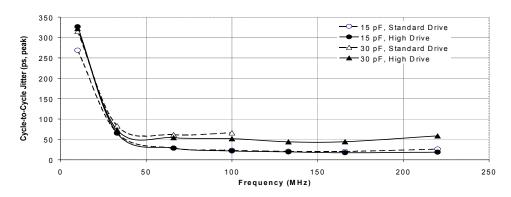

Figure 12. Typical 3.3 V Measured Cycle-to-cycle Jitter at 29 °C, versus Frequency, Drive Strength, and Loading

Figure 13. Typical 2.5 V Measured Cycle-to-cycle Jitter at 29 °C, versus Frequency, Drive Strength, and Loading

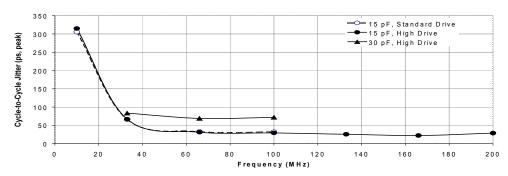

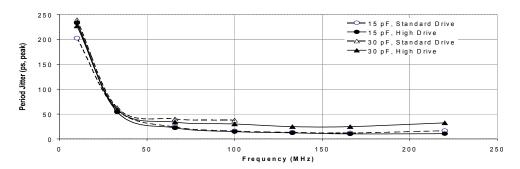

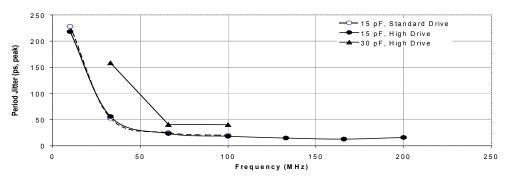

Figure 14. Typical 3.3 V Measured Period Jitter at 29 °C, versus Frequency, Drive Strength, and Loading

Figure 15. Typical 2.5 V Measured Period Jitter at 29 °C, versus Frequency, Drive Strength, and Loading

Document Number: 38-07760 Rev. \*G Page 13 of 19

### **Supplemental Parametric Information** (continued)

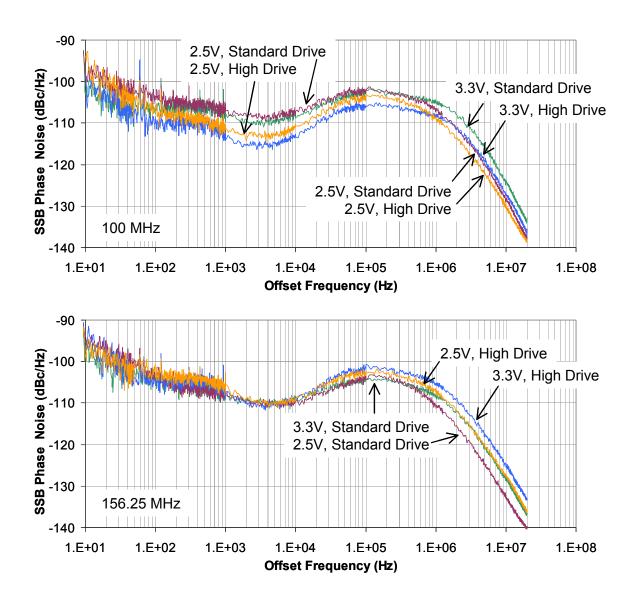

Figure 16. Typical Phase-noise Data at 100 MHz (top) and 156.25 MHz (bottom) across V<sub>DD</sub> and Drive Strength <sup>[12]</sup>

#### Note

<sup>12.</sup> Typical jitter is measured at 3.3 V or 2.5 V, 29 °C, with all outputs driven into the maximum specified load. Further information regarding jitter specifications may be found in the application note "Understanding Data Sheet Jitter Specifications for Cypress Clock Products."

### **Ordering Information**

| Ordering Code   | Package Type                 | Operating Range |

|-----------------|------------------------------|-----------------|

| Pb-free         |                              |                 |

| CY23EP09SXC-1   | 16-pin SOIC                  | Commercial      |

| CY23EP09SXC-1T  | 16-pin SOIC – Tape and Reel  | Commercial      |

| CY23EP09SXI-1   | 16-pin SOIC                  | Industrial      |

| CY23EP09SXI-1T  | 16-pin SOIC – Tape and Reel  | Industrial      |

| CY23EP09SXC-1H  | 16-pin SOIC                  | Commercial      |

| CY23EP09SXC-1HT | 16-pin SOIC – Tape and Reel  | Commercial      |

| CY23EP09SXI-1H  | 16-pin SOIC                  | Industrial      |

| CY23EP09SXI-1HT | 16-pin SOIC – Tape and Reel  | Industrial      |

| CY23EP09ZXC-1H  | 16-pin TSSOP                 | Commercial      |

| CY23EP09ZXC-1HT | 16-pin TSSOP – Tape and Reel | Commercial      |

| CY23EP09ZXI-1H  | 16-pin TSSOP                 | Industrial      |

| CY23EP09ZXI-1HT | 16-pin TSSOP – Tape and Reel | Industrial      |

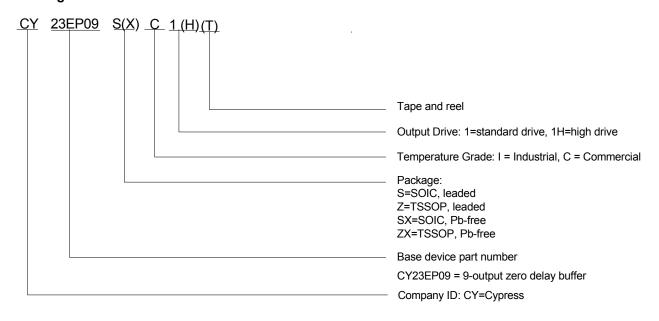

### **Ordering Code Definitions**

#### **Package Diagrams**

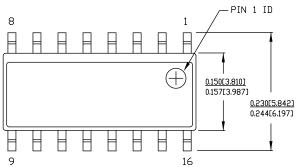

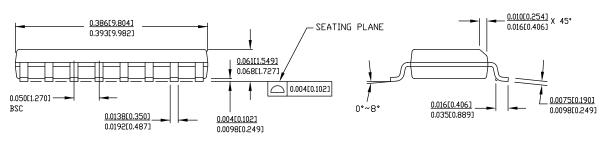

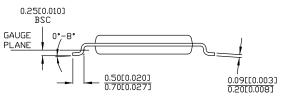

Figure 17. 16-pin SOIC (150 Mils) S16.15/SZ16.15 Package Outline, 51-85068

NOTE:

- 1. DIMENSIONS IN INCHES[MM] MANK.

- 2. REFERENCE JEDEC MS-012

- 3. PACKAGE WEIGHT: refer to PMDD spec. 001-04308

| PART #  |                |  |  |  |

|---------|----------------|--|--|--|

| \$16.15 | STANDARD PKG.  |  |  |  |

| SZ16.15 | LEAD FREE PKG. |  |  |  |

51-85068 \*E

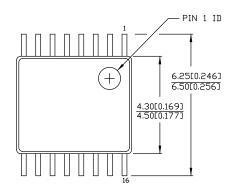

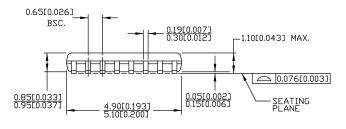

Figure 18. 16-pin TSSOP (4.40 mm Body) Z16.173/ZZ16.173 Package Outline, 51-85091

DIMENSIONS IN MMEINCHES) MIN. MAX.

REFERENCE JEDEC MO-153

PACKAGE WEIGHT 0.05gms

| PART #   |                |  |  |  |  |

|----------|----------------|--|--|--|--|

| Z16.173  | STANDARD PKG.  |  |  |  |  |

| ZZ16.173 | LEAD FREE PKG. |  |  |  |  |

51-85091 \*E

### **Acronyms**

| Acronym               | Description                             |  |  |

|-----------------------|-----------------------------------------|--|--|

| PCI                   | Personal Computer Interconnect          |  |  |

| PLL                   | Phase Locked Loop                       |  |  |

| SDRAM                 | Synchronous Dynamic Random Access Memor |  |  |

| SOIC                  | OIC Small Outline Integrated Circuit    |  |  |

| TSSOP                 | TSSOP Thin-Shrink Small Outline Package |  |  |

| ZDB Zero Delay Buffer |                                         |  |  |

### **Document Conventions**

#### **Units of Measure**

| Symbol | Units of Measure |  |  |

|--------|------------------|--|--|

| °C     | degree Celsius   |  |  |

| MHz    | megahertz        |  |  |

| μΑ     | microampere      |  |  |

| mA     | milliampere      |  |  |

| ms     | millisecond      |  |  |

| ns     | nanosecond       |  |  |

| pF     | picofarad        |  |  |

| ps     | picosecond       |  |  |

| V      | volt             |  |  |

# **Document History Page**

| Rev. | ECN No. | Issue Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                         |

|------|---------|------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 345446  | See ECN    | RGL                | New data sheet.                                                                                                                                                                                                                                                                                                                                               |

| *A   | 355777  | See ECN    | RGL                | Updated Electrical Specifications: Updated values of t <sub>7</sub> parameter (to agree with latest char results).                                                                                                                                                                                                                                            |

| *B   | 401036  | See ECN    | RGL                | Changed status from Preliminary to Final. Updated Electrical Specifications: Updated details in "Test Conditions" column corresponding to T <sub>JCC</sub> and T <sub>PER</sub> parameters. Updated Supplemental Parametric Information: Added Figure 8. Added Figure 16.                                                                                     |

| *C   | 3270178 | 06/01/2011 | BASH               | Updated Package Diagrams. Added Acronyms and Units of Measure. Updated to new template.                                                                                                                                                                                                                                                                       |

| *D   | 4400992 | 06/10/2014 | AJU                | Updated Operating Conditions: Updated values of Theta Ja and Theta Jc parameters (corresponding to 16-pin TSSOP package). Updated Package Diagrams: spec 51-85068 – Changed revision from *C to *E. spec 51-85091 – Changed revision from *C to *D. Updated to new template. Completing Sunset Review.                                                        |

| *E   | 4580603 | 11/26/2014 | AJU                | Updated Functional Description: Added "For a complete list of related documentation, click here." at the end. Updated Package Diagrams.                                                                                                                                                                                                                       |

| *F   | 5243008 | 04/26/2016 | PSR                | Updated Zero Delay and Skew Control: Updated description. Updated Operating Conditions: Removed "Theta Ja", "Theta Jc" parameters and their details. Removed Note "Theta Ja, EIA JEDEC 51 test board conditions, 2S2P; Theta Jc Mil-Spec 883E Method 1012.1." and its reference. Added Thermal Resistance. Updated to new template. Completing Sunset Review. |

| *G   | 5993917 | 12/14/2017 | AESATMP8           | Updated logo and Copyright.                                                                                                                                                                                                                                                                                                                                   |

#### Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

Wireless Connectivity

ARM® Cortex® Microcontrollers

Automotive

Clocks & Buffers

Interface

Internet of Things

cypress.com/arm

cypress.com/automotive

cypress.com/clocks

cypress.com/interface

cypress.com/iot

Internet of Things cypress.com/iot

Memory cypress.com/memory

Microcontrollers cypress.com/mcu

Microcontrollers cypress.com/mcu

PSoC cypress.com/psoc

Power Management ICs cypress.com/pmic

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

cypress.com/wireless

#### PSoC<sup>®</sup>Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2010-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 38-07760 Rev. \*G Revised December 14, 2017 Page 19 of 19

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Phase Locked Loops - PLL category:

Click to view products by Cypress manufacturer:

Other Similar products are found below:

HMC700LP4TR CPLL58-2400-2500 MB15E07SLPFV1-G-BND-6E1 PI6C2409-1HWEX BA4116FV-E2 HMC820LP6CETR

HMC828LP6CETR LMX2430TMX/NOPB HMC837LP6CETR HMC831LP6CETR NB3N5573DTG ADF4153ABCPZ PI6C2405A-1LE

CD74HC4046AM CPLL66-2450-2450 NJM567D CY23S05SXI-1 STW81200T ADF4208BRUZ ADF4218LBRUZ ADF4355-3BCPZ

ADF5355BCPZ ADF4355BCPZ ADF4169WCCPZ ADF4360-7BCPZ ADF4360-6BCPZ ADF4360-5BCPZRL7 ADF4360-5BCPZRL7 ADF4360-5BCPZ

ADF4360-4BCPZRL7 ADF4360-4BCPZ ADF4360-3BCPZ ADF4360-2BCPZRL7 ADF4252BCPZ ADF4159CCPZ ADF4169CCPZ

ADF4252BCPZ-R7 ADF4360-0BCPZ ADF4360-1BCPZ ADF4360-1BCPZRL7 ADF4360-2BCPZ ADF4360-3BCPZRL7 ADF43607BCPZRL7 ADF4360-8BCPZ ADF4360-8BCPZRL7 ADF4360-9BCPZ ADF4360-9BCPZRL7 ADF4159CCPZ-RL7 ADF4159WCCPZ

ADF4360-0BCPZRL7 AD9901KPZ