# Rambus<sup>®</sup> XDR™ Clock Generator with Zero SDA Hold Time

### **Features**

- Meets Rambus<sup>®</sup> Extended Data Rate (XDR<sup>™</sup>) clocking requirements

- 25 ps typical cycle-to-cycle jitter

□ -135 dBc/Hz typical phase noise at 20 MHz offset

- 100 or 133 MHz differential clock input

- 300–667 MHz high speed clock support

- Quad (open drain) differential output drivers

- Supports frequency multipliers: 3, 4, 5, 6, 9/2 and 15/4

- Spread Aware<sup>™</sup>

- 2.5 V operation

- 28-pin TSSOP package

## **Device Comparison**

| CY24271                                          | CY24272                                                |

|--------------------------------------------------|--------------------------------------------------------|

|                                                  | SDA hold time = 0 ns (I <sup>2</sup> C compliant)      |

| $R_{RC}$ = 200 Ω typical (Rambus standard drive) | $R_{RC}$ = 295 $\Omega$ minimum (Reduced output drive) |

# **Functional Description**

For a complete list of related documentation, click here.

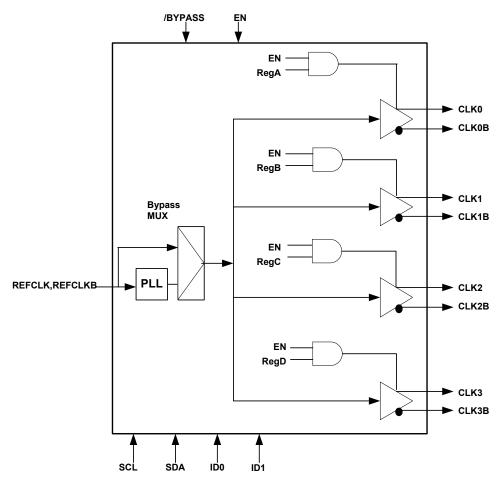

# **Logic Block Diagram**

### Contents

| Pin Configuration                  | 3  |

|------------------------------------|----|

| Pin Definitions                    |    |

| Functional Overview                | 4  |

| PLL Multiplier                     | 4  |

| Input Clock Signal                 | 4  |

| Modes of Operation                 | 5  |

| Device ID and SMBus Device Address | 6  |

| SMBus Protocol                     | 6  |

| SMBus Data Byte Definitions        | 6  |

| Absolute Maximum Conditions        | 8  |

| DC Operating Conditions            | 9  |

| DC Electrical Specifications       | 10 |

| Thermal Resistance                 | 10 |

| AC Operating Conditions            | 11 |

| AC Electrical Specifications       |    |

| SMBus Timing Specification         | 13 |

| Test and Measurement Setup              | 14             |

|-----------------------------------------|----------------|

| Signal Waveforms                        | 1              |

| Jitter                                  | 10             |

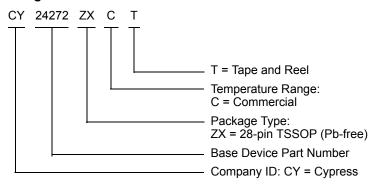

| Ordering Information                    | 17             |

| Ordering Code Definitions               | 17             |

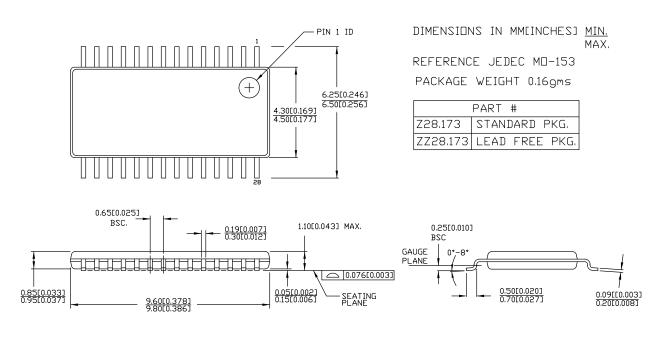

| Package Drawing and Dimension           | 18             |

| Acronyms                                | 19             |

| Document Conventions                    | 19             |

| Units of Measure                        | 19             |

| Document History Page                   | 20             |

| Sales, Solutions, and Legal Information | 2 <sup>,</sup> |

| Worldwide Sales and Design Support      | 2 <sup>2</sup> |

| Products                                | 2 <sup>-</sup> |

| PSoC®Solutions                          | 2 <sup>-</sup> |

| Cypress Developer Community             | 2 <sup>-</sup> |

| Technical Support                       |                |

|                                         |                |

# **Pin Configuration**

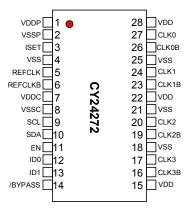

Figure 1. 28-pin TSSOP pinout

# **Pin Definitions**

28-pin TSSOP

| Pin No. | Name    | I/O | Description                                             |

|---------|---------|-----|---------------------------------------------------------|

| 1       | VDDP    | PWR | 2.5 V power supply for phased lock loop (PLL)           |

| 2       | VSSP    | GND | Ground                                                  |

| 3       | ISET    | I   | Set clock driver current (external resistor)            |

| 4       | VSS     | GND | Ground                                                  |

| 5       | REFCLK  | I   | Reference clock input (connect to clock source)         |

| 6       | REFCLKB | I   | Complement of reference clock (connect to clock source) |

| 7       | VDDC    | PWR | 2.5 V power supply for core                             |

| 8       | VSSC    | GND | Ground                                                  |

| 9       | SCL     | I   | SMBus clock (connect to SMBus)                          |

| 10      | SDA     | I   | SMBus data (connect to SMBus)                           |

| 11      | EN      | I   | Output Enable (CMOS signal)                             |

| 12      | ID0     | I   | Device ID (CMOS signal)                                 |

| 13      | ID1     |     | Device ID (CMOS signal)                                 |

| 14      | /BYPASS | I   | REFCLK bypassing PLL (CMOS signal)                      |

| 15      | VDD     | PWR | Power supply for outputs                                |

| 16      | CLK3B   | 0   | Complement clock output                                 |

| 17      | CLK3    | 0   | Clock output                                            |

| 18      | VSS     | GND | Ground                                                  |

| 19      | CLK2B   | 0   | Complement clock output                                 |

| 20      | CLK2    | 0   | Clock output                                            |

| 21      | VSS     | GND | Ground                                                  |

| 22      | VDD     | PWR | Power supply for outputs                                |

| 23      | CLK1B   | 0   | Complement clock output                                 |

| 24      | CLK1    | 0   | Clock output                                            |

| 25      | VSS     | GND | Ground                                                  |

### Pin Definitions (continued)

28-pin TSSOP

| Pin No. | Name  | I/O | Description              |

|---------|-------|-----|--------------------------|

| 26      | CLK0B | 0   | Complement clock output  |

| 27      | CLK0  | 0   | Clock output             |

| 28      | VDD   | PWR | Power supply for outputs |

### **Functional Overview**

### **PLL Multiplier**

Table 1 shows the frequency multipliers in the PLL, selectable by programming the SMBus registers MULT0, MULT1, and MULT2. Default multiplier at power up is 4.

Table 1. PLL Multiplier Selection

| Register |       | Frequency Multiplier | Output Frequency (MHz) |                                  |                                  |  |

|----------|-------|----------------------|------------------------|----------------------------------|----------------------------------|--|

| MULT2    | MULT1 | MULT0                | r requericy munipher   | REFCLK = 100 MHz [1], REFSEL = 0 | REFCLK = 133 MHz [1], REFSEL = 1 |  |

| 0        | 0     | 0                    | 3                      | 300                              | 400                              |  |

| 0        | 0     | 1                    | 4                      | 400 [2]                          | -                                |  |

| 0        | 1     | 0                    | 5                      | 500                              | 667                              |  |

| 0        | 1     | 1                    | 6                      | 600                              | -                                |  |

| 1        | 0     | 0                    | Reserved               | -                                | -                                |  |

| 1        | 0     | 1                    | 9/2                    | 450                              | 600                              |  |

| 1        | 1     | 0                    | Reserved               | -                                | -                                |  |

| 1        | 1     | 1                    | 15/4                   | 375                              | 500                              |  |

### Input Clock Signal

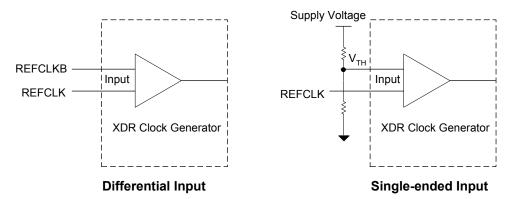

The XCG receives either a differential (REFCLK/REFCLKB) or a single-ended reference clocking input (REFCLK).

When the reference input clock is from a different clock source, it must meet the voltage levels and timing requirements listed in DC Operating Conditions on page 9 and AC Operating Conditions on page 11.

For a single-ended clock input, an external voltage divider and a supply voltage, as shown in Figure 2, provide a reference voltage  $V_{TH}$  at the REFCLKB pin. This determines the proper trip point of REFCLK. For the range of  $V_{TH}$  specified in DC Operating Conditions on page 9, the outputs also meet the DC and AC Operating Conditions tables.

Figure 2. Differential and Single-Ended Clock Inputs

### Notes

- Output frequencies shown in Table 1 are based on nominal input frequencies of 100 MHz and 133.3 MHz. The PLL multipliers are applicable to spread spectrum modulated input clock with maximum and minimum input cycle time. The REFSEL bit in SMBus 81h is set correctly as shown.

- 2. Default PLL multiplier at power up.

### **Modes of Operation**

The modes of operation are determined by the logic signals applied to the EN and /BYPASS pins and the values in the five SMBus Registers: RegTest, RegA, RegB, RegC, and RegD. Table 3 on page 6 shows selection from one to all four of the outputs, the Outputs Disabled Mode (EN = low), and Bypass

Mode (EN = high, /BYPASS = low). There is an option reserved for vendor test. Disabled outputs are set to High Z.

At power up, the SMBus registers default to the last entry in Table 4 on page 7. The value at RegTest is 0. The values at RegA, RegB, RegC, and RegD are all '1'. Thus, all outputs are controlled by the logic applied to EN and /BYPASS.

Table 2. SMBus Device Addresses for CY24272

| XC     | XCG       |             | 8-bit SMBus Device Address Including Operation |   |   |     |     |     |          |   |

|--------|-----------|-------------|------------------------------------------------|---|---|-----|-----|-----|----------|---|

| Device | Operation | Hex Address | Five Most Significant Bits                     |   |   | its | ID1 | ID0 | WR# / RD |   |

| 0      | Write     | D8          |                                                |   |   |     |     | 0   | 0        | 0 |

|        | Read      | D9          |                                                |   |   | 0 1 | 1   |     |          | 1 |

| 1      | Write     | DA          |                                                |   |   |     |     | 0   |          | 0 |

| '      | Read      | DB          | 1                                              | 1 | 0 |     |     |     |          | 1 |

| 2      | Write     | DC          | '                                              |   | ' | .   | 1   | 0   | 0        |   |

| 2      | Read      | DD          |                                                |   |   |     |     | !   |          | 1 |

| 3      | Write     | DE          |                                                |   |   |     |     | 1   | 1        | 0 |

| 3      | Read      | DF          |                                                |   |   |     |     |     |          | 1 |

Table 3. Modes of Operation for CY24272

| EN | /BYPASS | RegTest          | RegA             | RegB             | RegC             | RegD             | CLK0/CLK0B                        | CLK1/CLK1B         | CLK2/CLK2B         | CLK3/CLK3B         |

|----|---------|------------------|------------------|------------------|------------------|------------------|-----------------------------------|--------------------|--------------------|--------------------|

| L  | Х       | Х                | Х                | Х                | Х                | Х                | High Z                            | High Z             | High Z             | High Z             |

| Н  | Х       | 1                | Х                | Х                | Х                | Х                |                                   | Reserved for       | Vendor Test        |                    |

| Н  | L       | 0                | Х                | Х                | Х                | Х                | REFCLK/<br>REFCLKB <sup>[3]</sup> | REFCLK/<br>REFCLKB | REFCLK/<br>REFCLKB | REFCLK/<br>REFCLKB |

| Н  | Н       | 0                | 0                | 0                | 0                | 0                | High Z                            | High Z             | High Z             | High Z             |

| Н  | Н       | 0                | 0                | 0                | 0                | 1                | High Z                            | High Z             | High Z             | CLK/CLKB           |

| Н  | Н       | 0                | 0                | 0                | 1                | 0                | High Z                            | High Z             | CLK/CLKB           | High Z             |

| Н  | Н       | 0                | 0                | 0                | 1                | 1                | High Z                            | High Z             | CLK/CLKB           | CLK/CLKB           |

| Н  | Н       | 0                | 0                | 1                | 0                | 0                | High Z                            | CLK/CLKB           | High Z             | High Z             |

| Н  | Н       | 0                | 0                | 1                | 0                | 1                | High Z                            | CLK/CLKB           | High Z             | CLK/CLKB           |

| Н  | Н       | 0                | 0                | 1                | 1                | 0                | High Z                            | CLK/CLKB           | CLK/CLKB           | High Z             |

| Н  | Н       | 0                | 0                | 1                | 1                | 1                | High Z                            | CLK/CLKB           | CLK/CLKB           | CLK/CLKB           |

| Н  | Н       | 0                | 1                | 0                | 0                | 0                | CLK/CLKB                          | High Z             | High Z             | High Z             |

| Н  | Н       | 0                | 1                | 0                | 0                | 1                | CLK/CLKB                          | High Z             | High Z             | CLK/CLKB           |

| Н  | Н       | 0                | 1                | 0                | 1                | 0                | CLK/CLKB                          | High Z             | CLK/CLKB           | High Z             |

| Н  | Н       | 0                | 1                | 0                | 1                | 1                | CLK/CLKB                          | High Z             | CLK/CLKB           | CLK/CLKB           |

| Н  | Н       | 0                | 1                | 1                | 0                | 0                | CLK/CLKB                          | CLK/CLKB           | High Z             | High Z             |

| Н  | Н       | 0                | 1                | 1                | 0                | 1                | CLK/CLKB                          | CLK/CLKB           | High Z             | CLK/CLKB           |

| Н  | Н       | 0                | 1                | 1                | 1                | 0                | CLK/CLKB                          | CLK/CLKB           | CLK/CLKB           | High Z             |

| Н  | Н       | 0 <sup>[4]</sup> | 1 <sup>[4]</sup> | 1 <sup>[4]</sup> | 1 <sup>[4]</sup> | 1 <sup>[4]</sup> | CLK/CLKB                          | CLK/CLKB           | CLK/CLKB           | CLK/CLKB           |

### **Device ID and SMBus Device Address**

The device ID (ID0 and ID1) is a part of the SMBus device 8-bit address. The least significant bit of the address designates a write or read operation. Table 2 on page 5 shows the addresses for four CY24272 devices on the same SMBus.

### **SMBus Protocol**

The CY24272 is a slave receiver supporting operations in the word and byte modes described in sections 5.5.4 and 5.5.5 of the SMBus Specification 2.0.

DC specifications are modified to Rambus standard to support 1.8, 2.5, and 3.3 volt devices. Time out detection and packet error protocol SMBus features are not supported.

Hold time for SDA is reduced relative to the CY24271, so that it is compatible with  $I^2C$ .

### **SMBus Data Byte Definitions**

Three data bytes are defined for the CY24272. Byte 0 is for programming the PLL multiplier registers and clock output registers.

The definition of Byte 2 is shown in Table 4 on page 7, Table 5 on page 7, and Table 6 on page 7. The upper five bits are the revision numbers of the device and the lower three bits are the ID numbers assigned to the vendor by Rambus.

### Notes

- 3. Bypass Mode: REFCLK bypasses the PLL to the output drivers.

- Default mode of operation is at power up.

Table 4. Command Code 80h [5]

| Bit | Register | POD | Туре | Description                                         |

|-----|----------|-----|------|-----------------------------------------------------|

| 7   | Reserved | 0   | RW   | Reserved (no internal function)                     |

| 6   | MULT2    | 0   | RW   | PLL Multiplier Select (reference Table 1 on page 4) |

| 5   | MULT1    | 0   | RW   |                                                     |

| 4   | MULT0    | 1   | RW   |                                                     |

| 3   | RegA     | 1   | RW   | Clock 0 Output Select                               |

| 2   | RegB     | 1   | RW   | Clock 1 Output Select                               |

| 1   | RegC     | 1   | RW   | Clock 2 Output Select                               |

| 0   | RegD     | 1   | RW   | Clock 3 Output Select                               |

# Table 5. Command Code 81h [5]

| Bit | Register | POD | Туре | Description                                              |  |

|-----|----------|-----|------|----------------------------------------------------------|--|

| 7   | Reserved | 0   | RW   | Reserved (no internal function)                          |  |

| 6   | Reserved | 0   | RW   |                                                          |  |

| 5   | Reserved | 0   | RW   |                                                          |  |

| 4   | Reserved | 0   | RW   |                                                          |  |

| 3   | Reserved | 1   | RW   | Reserved (must be set to '1' for proper operation)       |  |

| 2   | REFSEL   | 0   | RW   | Reference Frequency Select (reference Table 1 on page 4) |  |

| 1   | Reserved | 0   | RW   | Reserved (must be set to '0' for proper operation)       |  |

| 0   | RegTest  | 0   | RW   | Reserved (must be set to '0' for proper operation)       |  |

# Table 6. Command Code 82h [5]

| Bit | Register   | POD | Туре | Description                                             |

|-----|------------|-----|------|---------------------------------------------------------|

| 7   | Device     | ?   | RO   | Contact factory for Device Revision Number information. |

| 6   | Revision ? | RO  |      |                                                         |

| 5   | Number     | ?   | RO   |                                                         |

| 4   |            | ?   | RO   |                                                         |

| 3   | ?          | ?   | RO   |                                                         |

| 2   | Vendor ID  | 0   | RO   | Rambus assigned Vendor ID Code                          |

| 1   |            | 1   | RO   |                                                         |

| 0   |            | 0   | RO   |                                                         |

Document Number: 001-42414 Rev. \*D

Note

5. RW = Read and Write, RO = Read Only, POD = Power on default. See Table 1 on page 4 for PLL multipliers and Table 3 on page 6 for clock output selections.

# **Absolute Maximum Conditions**

| Parameter          | Description                       | Condition                   | Min  | Max                   | Unit |

|--------------------|-----------------------------------|-----------------------------|------|-----------------------|------|

| $V_{DD}$           | Clock Buffer Supply Voltage       |                             | -0.5 | 4.6                   | V    |

| $V_{DDC}$          | Core Supply Voltage               |                             | -0.5 | 4.6                   | V    |

| $V_{DDP}$          | PLL Supply Voltage                |                             | -0.5 | 4.6                   | V    |

| V <sub>IN</sub>    | Input Voltage (SCL and SDA)       | Relative to V <sub>SS</sub> | -0.5 | 4.6                   | V    |

|                    | Input Voltage<br>(REFCLK/REFCLKB) | Relative to V <sub>SS</sub> | -0.5 | V <sub>DD</sub> + 1.0 | V    |

|                    | Input Voltage                     | Relative to V <sub>SS</sub> | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| T <sub>S</sub>     | Temperature, Storage              | Non-functional              | -65  | 150                   | °C   |

| T <sub>A</sub>     | Temperature, Operating Ambient    | Functional                  | 0    | 70                    | °C   |

| T <sub>J</sub>     | Temperature, Junction             | Functional                  | _    | 150                   | °C   |

| ESD <sub>HBM</sub> | ESD Protection (Human Body Model) | MIL-STD-883, Method 3015    | 2000 | _                     | V    |

# **DC Operating Conditions**

| Parameter                          | Description                                             | Condition  | Min                   | Max                   | Unit |

|------------------------------------|---------------------------------------------------------|------------|-----------------------|-----------------------|------|

| $V_{\mathrm{DDP}}$                 | Supply Voltage for PLL                                  | 2.5 V ± 5% | 2.375                 | 2.625                 | V    |

| $V_{DDC}$                          | Supply Voltage for Core                                 | 2.5 V ± 5% | 2.375                 | 2.625                 | V    |

| $V_{DD}$                           | Supply Voltage for Clock Buffers                        | 2.5 V ± 5% | 2.375                 | 2.625                 | V    |

| V <sub>IHCLK</sub>                 | Input High Voltage,<br>REFCLK/REFCLKB                   |            | 0.6                   | 0.95                  | V    |

| V <sub>ILCLK</sub>                 | Input Low Voltage,<br>REFCLK/REFCLKB                    |            | -0.15                 | +0.15                 | V    |

| V <sub>IXCLK</sub> <sup>[6]</sup>  | Crossing Point Voltage,<br>REFCLK/REFCLKB               |            | 200                   | 550                   | mV   |

| ΔV <sub>IXCLK</sub> <sup>[6]</sup> | Difference in Crossing Point Voltage, REFCLK/REFCLKB    |            | -                     | 150                   | mV   |

| V <sub>IH</sub>                    | Input Signal High Voltage at ID0, ID1, EN, and /BYPASS  |            | 1.4                   | 2.625                 | V    |

| V <sub>IL</sub>                    | Input Signal Low Voltage at ID0, ID1, EN, and /BYPASS   |            | -0.15                 | 0.8                   | V    |

| V <sub>IH,SM</sub>                 | Input Signal High Voltage at SCL and SDA <sup>[7]</sup> |            | 1.4                   | 3.465                 | V    |

| $V_{\rm IL,SM}$                    | Input Signal Low Voltage at SCL and SDA                 |            | -0.15                 | 0.8                   | V    |

| V <sub>TH</sub> <sup>[8]</sup>     | Input Threshold Voltage for single-ended REFCLK         |            | 0.35                  | 0.5 × V <sub>DD</sub> | V    |

| V <sub>IH,SE</sub>                 | Input Signal High Voltage for single-ended REFCLK       |            | V <sub>TH</sub> + 0.3 | 2.625                 | V    |

| $V_{IL,SE}$                        | Input Signal Low Voltage for single-ended REFCLK        |            | -0.15                 | V <sub>TH</sub> – 0.3 | V    |

| T <sub>A</sub>                     | Ambient Operating Temperature                           |            | 0                     | 70                    | °C   |

<sup>Notes

6. Not 100% tested except V<sub>IXCLK</sub> and ΔV<sub>IXCLK</sub>. Parameters guaranteed by design and characterizations, not 100% tested in production.

7. This range of SCL and SDA input high voltage enables the CY24272 for use with 3.3 V, 2.5 V, or 1.8 V SMBus voltages.

8. Single-ended operation guaranteed only when 0.8 < (V<sub>IH,SE</sub> – V<sub>TH</sub>)/(V<sub>TH</sub> – V<sub>IL,SE</sub>) < 1.2.</li></sup>

# **DC Electrical Specifications**

| Parameter                         | Description                                                                                | Min  | Тур  | Max  | Unit |

|-----------------------------------|--------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>OX</sub> <sup>[9]</sup>    | Differential output crossing point voltage <sup>[10]</sup>                                 | _    | 1.08 | _    | V    |

| V <sub>COS</sub> <sup>[9]</sup>   | Output voltage swing (peak-to-peak single-ended) <sup>[11]</sup>                           | _    | 400  | _    | mV   |

| V <sub>OL,ABS</sub>               | Absolute output low voltage at CLK[3:0], CLK[3:0]B <sup>[12]</sup>                         | 0.85 | -    | -    | V    |

| V <sub>ISET</sub>                 | Reference voltage for swing controlled current, I <sub>REF</sub>                           | 0.98 | 1.0  | 1.02 | V    |

| I <sub>DD</sub> <sup>[13]</sup>   | Power Supply Current at 2.625V, f <sub>ref</sub> = 100 MHz, and f <sub>out</sub> = 300 MHz | -    | _    | 85   | mA   |

| I <sub>DD</sub> <sup>[13]</sup>   | Power Supply Current at 2.625V, f <sub>ref</sub> = 133 MHz, and f <sub>out</sub> = 667 MHz |      | _    | 125  | mA   |

| I <sub>OL/</sub> I <sub>REF</sub> | Ratio of output low current to reference current <sup>[14]</sup>                           |      | 7.0  | 7.2  |      |

| I <sub>OL,ABS</sub>               | Minimum current at V <sub>OL,ABS</sub> <sup>[15]</sup>                                     | 25   | _    | _    | mA   |

| V <sub>OL,SDA</sub>               | SDA output low voltage at test condition of SDA output low current = 4 mA                  | -    | -    | 0.4  | V    |

| I <sub>OL,SDA</sub>               | SDA output low voltage at test condition of SDA voltage = 0.8 V                            | 6    | _    | -    | mA   |

| I <sub>OZ</sub>                   | Current during High Z per pin at CLK[3:0], CLK[3:0]B                                       | _    | _    | 10   | μА   |

| Z <sub>OUT</sub>                  | Output dynamic impedance when clock output signal is at $V_{OL}$ = 0.9 V <sup>[16]</sup>   | 1000 | _    | -    | Ω    |

### **Thermal Resistance**

| Parameter [17] | Description                           | Test Conditions                                                                                 | 28-pin TSSOP | Unit |

|----------------|---------------------------------------|-------------------------------------------------------------------------------------------------|--------------|------|

| - 3/4          | ,                                     | Test conditions follow standard test methods and procedures for measuring thermal impedance, in | -            | °C/W |

| - 30           | Thermal resistance (junction to case) | accordance with EIA/JESD51.                                                                     | 17           | °C/W |

- Notes

9. Not 100% tested except V<sub>IXCLK</sub> and ΔV<sub>IXCLK</sub>. Parameters guaranteed by design and characterizations, not 100% tested in production.

10. V<sub>OX</sub> is measured on external divider network.

11. V<sub>COS</sub> = (clock output high voltage clock output low voltage), measured on the external divider network.

12. V<sub>OL\_ABS</sub> is measured at the clock output pins of the package.

13. This range of SCL and SDA input high voltage enables the CY24272 for use with 3.3 V, 2.5 V, or 1.8 V SMBus voltages.

14. I<sub>REF</sub> is equal to V<sub>ISET</sub>/R<sub>RC</sub>.

15. Minimum I<sub>OL,ABS</sub> is measured at the clock output pin with R<sub>RC</sub> = 266 ohms or less.

16. Z<sub>OUT</sub> is defined at the output pins as (0.94 V 0.90 V)/(I<sub>0.94</sub> I<sub>0.90</sub>) under conditions specified for I<sub>OL,ABS</sub>.

17. These parameters are guaranteed by design and are not tested.

# **AC Operating Conditions**

The AC operating conditions follow. [18]

| Parameter                            | Description                                                       | Condition                                                          | Min | Max                 | Unit               |

|--------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------|-----|---------------------|--------------------|

| t <sub>CYCLE,IN</sub>                | REFCLK, REFCLKB input cycle                                       | REFSEL = 0, /BYPASS = High                                         | 9   | 11                  | ns                 |

|                                      | time                                                              | REFSEL = 1, /BYPASS = High                                         | 7   | 8                   | ns                 |

|                                      |                                                                   | /BYPASS = Low                                                      | 4   | _                   | ns                 |

| t <sub>JIT,IN(cc)</sub>              | Input Cycle to Cycle Jitter <sup>[19]</sup>                       |                                                                    | _   | 185                 | ps                 |

| t <sub>DCIN</sub> <sup>[20]</sup>    | Input Duty Cycle                                                  | Over 10,000 cycles                                                 | 40% | 60%                 | t <sub>CYCLE</sub> |

| t <sub>RIN</sub> / t <sub>FIN</sub>  | Rise and Fall Times                                               | Measured at 20%–80% of input voltage for REFCLK and REFCLKB inputs | 175 | 700                 | ps                 |

| Δt <sub>RIN</sub> / t <sub>FIN</sub> | Rise and Fall Times Difference                                    |                                                                    | _   | 150                 | ps                 |

| p <sub>MIN</sub> <sup>[21]</sup>     | Modulation Index for triangular modulation                        |                                                                    | -   | 0.6                 | %                  |

|                                      | Modulation Index for non-triangular modulation                    |                                                                    | _   | 0.5 <sup>[22]</sup> | %                  |

| f <sub>MIN</sub> <sup>[21]</sup>     | Input Frequency Modulation                                        |                                                                    | 30  | 33                  | kHz                |

| t <sub>SR,IN</sub>                   | Input Slew Rate (measured at 20%–80% of input voltage) for REFCLK |                                                                    | 1   | 4                   | V/ns               |

| C <sub>IN,REF</sub>                  | Capacitance at REFCLK inputs                                      |                                                                    | _   | 7                   | pF                 |

| C <sub>IN,CMOS</sub>                 | Capacitance at CMOS inputs                                        |                                                                    | _   | 10                  | pF                 |

| f <sub>SCL</sub>                     | SMBus clock frequency input in SCL pin                            |                                                                    | DC  | 100                 | kHz                |

Notes

Not 100% tested except V<sub>IXCLK</sub> and ΔV<sub>IXCLK</sub>. Parameters guaranteed by design and characterizations, not 100% tested in production.

Jitter measured at crossing points and is the absolute value of the worst case deviation.

Measured at crossing points.

If input modulation is used; input modulation is allowed but not required.

The amount of allowed spreading for any non-triangular modulation is determined by the induced downstream tracking skew that cannot exceed the skew generated by the specified 0.6% triangular modulation. Typically, the amount of allowed non-triangular modulation is about 0.5%.

# **AC Electrical Specifications**

The AC Electrical specifications follow. [23]

| Parameter                        | Description                                                                                                                                                                                                                                                                          | Min  | Тур  | Max  | Unit               |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------------------|

| t <sub>CYCLE</sub>               | Clock Cycle time <sup>[24]</sup>                                                                                                                                                                                                                                                     | 1.25 | _    | 3.34 | ns                 |

| t <sub>JIT(cc)</sub>             | Jitter over 1-6 clock cycles at 400–635 MHz <sup>[25]</sup>                                                                                                                                                                                                                          | _    | 25   | 40   | ps                 |

|                                  | Jitter over 1-6 clock cycles at 638–667 MHz                                                                                                                                                                                                                                          | -    | 25   | 30   | ps                 |

| L <sub>20</sub>                  | Phase noise SSB spectral purity L(f) at 20 MHz offset: $400-500$ MHz (In addition, device must not exceed L(f) = $10\log[1+(50\times10^6/f)^{2.4}] -138$ for f = 1 MHz to $100$ MHz except for the region near f = REFCLK/Q where Q is the value of the internal reference divider.) | -    | -135 | -128 | dBC/Hz             |

| t <sub>JIT(hper,cc)</sub>        | Cycle-to-cycle duty cycle error at 400–635 MHz                                                                                                                                                                                                                                       | -    | 25   | 40   | ps                 |

|                                  | Cycle-to-cycle duty cycle error at 636–667 MHz                                                                                                                                                                                                                                       | -    | 25   | 30   | ps                 |

| Δt <sub>SKEW</sub>               | Drift in t <sub>SKEW</sub> when ambient temperature varies between 0 °C and 70 °C and supply voltage varies between 2.375 V and 2.625 V. <sup>[26]</sup>                                                                                                                             |      | _    | 15   | ps                 |

| DC                               | Long term average output duty cycle                                                                                                                                                                                                                                                  | 45%  | 50   | 55%  | t <sub>CYCLE</sub> |

| t <sub>EER,SCC</sub>             | PLL output phase error when tracking SSC                                                                                                                                                                                                                                             | -100 | _    | 100  | ps                 |

| t <sub>CR</sub> ,t <sub>CF</sub> | Output rise and fall times at 400–667 MHz (measured at 20%–80% of output voltage)                                                                                                                                                                                                    |      | 150  | _    | ps                 |

| t <sub>CR,CF</sub>               | Difference between output rise and fall times on the same pin of the single device (20%–80%) of 400–667 MHz <sup>[27]</sup>                                                                                                                                                          |      | -    | 100  | ps                 |

<sup>Notes

23. Not 100% tested except V<sub>IXCLK</sub> and ΔV<sub>IXCLK</sub>. Parameters guaranteed by design and characterizations, not 100% tested in production.

24. Max and min output clock cycle times are based on nominal outputs frequency of 300 and 667 MHz, respectively. For spread spectrum modulated differential or single-ended REFCLK, the output clock tracks the modulation of the input.

25. Output short term jitter spec is the absolute value of the worst case deviation.

26. t<sub>SKEW</sub> is the timing difference between any two of the four differential clocks and is measured at common mode voltage. Δt<sub>SKEW</sub> is the change in t<sub>SKEW</sub> when the operating temperature and supply voltage change.

27. t<sub>CR,CF</sub> applies only when appropriate R<sub>RC</sub> and output resistor network resistor values are selected to match pull up and pull down currents.</sup>

# **SMBus Timing Specification**

| Parameter | Description                                                                                  | Min | Max  | Units                              |

|-----------|----------------------------------------------------------------------------------------------|-----|------|------------------------------------|

| FSMB      | SMBus Operating Frequency                                                                    | 10  | 100  | kHz                                |

| TBUF      | Bus free time between Stop and Start Condition                                               | 4.7 | -    | μS                                 |

| THD:STA   | Hold time after (Repeated) Start Condition. After this period, the first clock is generated. | 4.0 | _    | μS                                 |

| TSU:STA   | Repeated Start Condition setup time                                                          | 4.7 | -    | μS                                 |

| TSU:STO   | Stop Condition setup time                                                                    | 4.0 | -    | μS                                 |

| THD:DAT   | Data Hold time                                                                               | 0   | -    | ns                                 |

| TSU:DAT   | Data Setup time                                                                              | 250 | -    | ns                                 |

| TTIMEOUT  | Detect clock low timeout                                                                     | -   | -    | Not supported                      |

| TLOW      | Clock low period                                                                             | 4.7 | -    | μS                                 |

| THIGH     | Clock high period                                                                            | 4.0 | 50   | μS                                 |

| TLOW:SEXT | Cumulative clock low extend time (slave device)                                              | -   | 25   | ms<br>CY24272<br>doesn't<br>extend |

| TLOW:MEXT | Cumulative clock low extend time (master device)                                             |     | 10   | ms                                 |

| TF        | Clock/Data Fall Time                                                                         | _   | 300  | ns                                 |

| TR        | Clock/Data Rise Time                                                                         | _   | 1000 | ns                                 |

| TPOR      | Time in which a device must be operational after power on reset                              | _   | 500  | ms                                 |

# **Test and Measurement Setup**

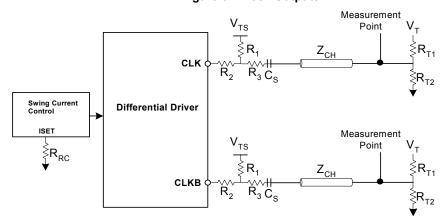

Figure 3. Clock Outputs

Table 7. Example External Resistor Values and Termination Voltages for a 50  $\Omega$  Channel

| Parameter       | Value | Unit |

|-----------------|-------|------|

| R <sub>1</sub>  | 33.0  | Ω    |

| $R_2$           | 18.0  | Ω    |

| R <sub>3</sub>  | 17.0  | Ω    |

| R <sub>T1</sub> | 60.4  | Ω    |

Table 7. Example External Resistor Values and Termination Voltages for a 50  $\Omega$  Channel (continued)

| Parameter       | Value | Unit |

|-----------------|-------|------|

| R <sub>T2</sub> | 301   | Ω    |

| C <sub>S</sub>  | 2700  | pF   |

| R <sub>RC</sub> | 432   | Ω    |

| V <sub>TS</sub> | 2.5   | V    |

| V <sub>T</sub>  | 1.2   | V    |

# **Signal Waveforms**

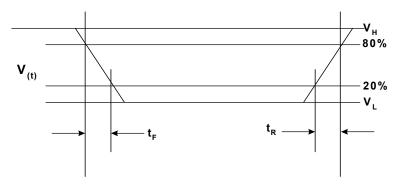

A physical signal that appears at the pins of a device is deemed valid or invalid depending on its voltage and timing relations with other signals. Input and output voltage waveforms are defined as shown in Figure 4 on page 15. Both rise and fall times are defined between the 20% and 80% points of the voltage swing, with the swing defined as  $V_H\!\!-\!\!V_L$ .

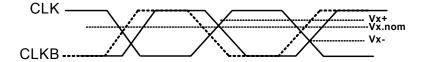

Figure 5 on page 15 shows the definition of the output crossing point. The nominal crossing point between the complementary outputs is defined as the 50% point of the DC voltage levels. There are two crossing points defined: Vx+ at the rising edge of CLK and Vx– at the falling edge of CLK. For some waveforms, both Vx+ and Vx– are below Vx,nom (for example, if  $t_{CR}$  is larger than  $t_{CF}$ ).

Figure 4. Input and Output Waveforms

Figure 5. Crossing Point Voltage

### **Jitter**

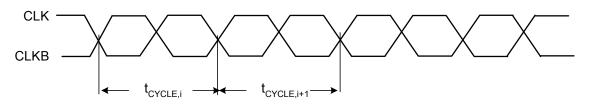

This section defines the specifications that relate to timing uncertainty (or jitter) of the input and output waveforms. Figure 6 on page 16 shows the definition of cycle-to-cycle jitter with respect to the falling edge of the CLK signal. Cycle-to-cycle jitter is the difference between cycle times of adjacent cycles. Equal

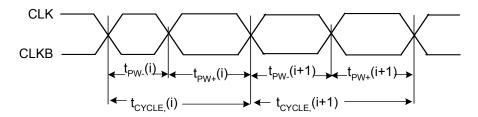

requirements apply rising edges of the CLK signal. Figure 7 on page 16 shows the definition of cycle-to-cycle duty cycle error ( $t_{DC,ERR}$ ). Cycle-to-cycle duty cycle is defined as the difference between  $t_{PW+}$  (high times) of adjacent differential clock cycles. Equal requirements apply to  $t_{PW-}$ , low times of the differential click cycles.

Figure 6. Cycle-to-cycle Jitter

$t_{J} = t_{CYCLE,i} - t_{CYCLE,i+1 \text{ over } 10,000 \text{ consecutive cycles}}$

Figure 7. Cycle-to-cycle Duty-cycle Error

$t_{DC,ERR} = t_{PW}(i) - t_{PW}(i+1)$  and  $t_{PW}(i+1) - t_{PW}(i+1)$

# **Ordering Information**

| Part Number | Package Type                 | Product Flow              |

|-------------|------------------------------|---------------------------|

| Pb-free     |                              |                           |

| CY24272ZXC  | 28-pin TSSOP                 | Commercial, 0 °C to 70 °C |

| CY24272ZXCT | 28-pin TSSOP – Tape and Reel | Commercial, 0 °C to 70 °C |

# **Ordering Code Definitions**

# **Package Drawing and Dimension**

Figure 8. 28-pin TSSOP (4.40 mm Body) Z28.173/ZZ28.173 Package Outline, 51-85120

51-85120 \*D

# **Acronyms**

| Acronym | Description                             |  |

|---------|-----------------------------------------|--|

| CMOS    | Complementary Metal Oxide Semiconductor |  |

| ESD     | Electrostatic Discharge                 |  |

| PLL     | Phase Locked Loop                       |  |

| TSSOP   | Thin Shrunk Small Outline Package       |  |

| XDR     | Extended Data Rate                      |  |

# **Document Conventions**

# **Units of Measure**

| Symbol | Unit of Measure |  |  |  |

|--------|-----------------|--|--|--|

| °C     | degree Celsius  |  |  |  |

| Hz     | hertz           |  |  |  |

| kHz    | kilohertz       |  |  |  |

| MHz    | megahertz       |  |  |  |

| μs     | microsecond     |  |  |  |

| μΑ     | microampere     |  |  |  |

| mA     | milliampere     |  |  |  |

| ms     | millisecond     |  |  |  |

| mV     | millivolt       |  |  |  |

| ns     | nanosecond      |  |  |  |

| Ω      | ohm             |  |  |  |

| %      | percent         |  |  |  |

| pF     | picofarad       |  |  |  |

| ps     | picosecond      |  |  |  |

| V      | volt            |  |  |  |

| W      | watt            |  |  |  |

# **Document History Page**

|      | Document Title: CY24272, Rambus <sup>®</sup> XDR™ Clock Generator with Zero SDA Hold Time<br>Document Number: 001-42414 |            |                    |                                                                                                                                                                                                      |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------|------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Rev. | ECN No.                                                                                                                 | Issue Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                |  |  |  |

| **   | 1749003                                                                                                                 | See ECN    | KVM /<br>AESA      | New data sheet.                                                                                                                                                                                      |  |  |  |

| *A   | 3175899                                                                                                                 | 02/17/2011 | BASH               | Added Ordering Code Definitions under Ordering Information. Updated Package Drawing and Dimension. Added Acronyms and Units of Measure. Updated to new template.                                     |  |  |  |

| *B   | 4299246                                                                                                                 | 03/05/2014 | CINM               | Updated Package Drawing and Dimension:<br>spec 51-85120 – Changed revision from *B to *C.<br>Updated to new template.<br>Completing Sunset Review.                                                   |  |  |  |

| *C   | 4581659                                                                                                                 | 11/28/2014 | AJU                | Updated Functional Description: Added "For a complete list of related documentation, click here." at the end. Updated Package Drawing and Dimension: spec 51-85120 – Changed revision from *C to *D. |  |  |  |

| *D   | 5279278                                                                                                                 | 06/07/2016 | PSR                | Updated Absolute Maximum Conditions: Removed $\emptyset_{JA}$ parameter and its details. Added Thermal Resistance. Updated to new template.                                                          |  |  |  |

# Sales, Solutions, and Legal Information

### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

cypress.com/usb

cypress.com/wireless

### **Products**

Wireless/RF

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Lighting & Power Control cypress.com/powerpsoc Memory cypress.com/memory **PSoC** cypress.com/psoc Touch Sensing cypress.com/touch **USB Controllers**

### **PSoC®Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

### **Cypress Developer Community**

Forums | Projects | Video | Blogs | Training | Components

### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2007-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or are not designed, intended in the activities of the activities of the devices of systems, including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United ates and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Generators & Support Products category:

Click to view products by Cypress manufacturer:

Other Similar products are found below:

CV183-2TPAG 82P33814ANLG/W 8T49N241-002NLGI 950810CGLF 9DBV0741AKILF 9VRS4420DKLF CY25404ZXI226

CY25422SXI-004 MPC9893AE NB3H5150-01MNTXG PL602-20-K52TC PI6LC48P0101LIE 82P33814ANLG 840021AGLF

MAX3674ECM+ ZL30244LFG7 PI6LC48C21LE ZL30245LFG7 PI6LC48P0405LIE PI6LC48P03LE MAX24505EXG+ ZL30163GDG2

ZL30673LFG7 MAX24188ETK2 ZL30152GGG2 PI6C557-01BZHIEX PI6LC48C21LIE PI6C557-03AQEX 5P35023-106NLGI

ZL30121GGG2V2 ZL30282LDG1 ZL30102QDG1 ZL30159GGG2 ZL30145GGG2 ZL30312GKG2 MAX24405EXG2 ZL30237GGG2

SY100EL34LZG 9FGV1002BQ506LTGI AD9518-4ABCPZ MX852BB0030 PI6LC4840ZHE AD9516-0BCPZ-REEL7 PL602-21TC-R

ZL30105QDG1 ZL30100QDG1 ZL30250LDG1 DSC557-0334FI1 DSC557-0343FI1 6V49205BNLGI