# Single-PLL General Purpose EPROM Programmable Clock Generator

### **Features**

- Single phase locked loop (PLL) architecture

- EPROM programmability

- Factory programmable (CY2907) or field programmable (CY2907F) device options

- Up to two configurable outputs

- Low skew, low jitter, high accuracy outputs

- Power management (power-down, OE)

- Frequency select option

- Configurable 5 V or 3.3 V Operation

- 8-pin SOIC package

### **Benefits**

- Generates a custom frequency from an external source

- Easy customization and fast turnaround

- Programming support available for all opportunities

- Provides clocking requirements from a single device

- Meets critical industry standard timing requirements

- Supports low power applications

- Up to 16 user selectable frequencies

- Supports industry standard design platforms

- Industry standard packaging saves on board space

# **Functional Description**

For a complete list of related documentation, click here.

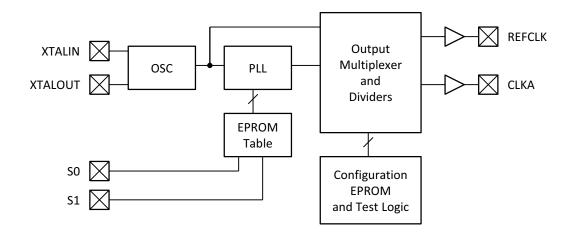

# **Logic Block Diagram**

# **Contents**

| Pin Configurations             | . 3 |

|--------------------------------|-----|

| Pin Description                | . 3 |

| Functional Overview            | 4   |

| Device Programming             | 4   |

| CyberClocks™ Software          | 4   |

| Cypress CY3670 Programming Kit | 4   |

| Maximum Ratings                |     |

| Operating Conditions           |     |

| Electrical Characteristics     | 6   |

| Electrical Characteristics     | 6   |

| Switching Characteristics      | . 7 |

| Switching Characteristics      |     |

| Switching Waveforms            |     |

| _                              | 9   |

| Ordering Information                    |    |

|-----------------------------------------|----|

| Ordering Code Definitions               | 10 |

| Package Characteristics                 | 10 |

| Package Diagrams                        | 11 |

| Acronyms                                | 12 |

| Document Conventions                    | 12 |

| Units of Measure                        | 12 |

| Document History Page                   | 13 |

| Sales, Solutions, and Legal Information | 15 |

| Worldwide Sales and Design Support      | 15 |

| Products                                | 15 |

| PSoC® Solutions                         | 15 |

| Cypress Developer Community             | 15 |

| Technical Support                       | 15 |

# **Pin Configurations**

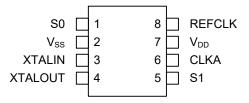

Figure 1. 8-pin SOIC pinout (Top View)

# **Pin Description**

| Name           | Pin Number | Description                                                             |  |

|----------------|------------|-------------------------------------------------------------------------|--|

| Name           | 8-pin SOIC | Description                                                             |  |

| S1             | 5          | Frequency select (CLKA) (internal pull-up resistor to V <sub>DD</sub> ) |  |

| $V_{SS}$       | 2          | Ground                                                                  |  |

| XTALIN [1]     | 3          | Reference crystal input                                                 |  |

| XTALOUT [1, 2] | 4          | Reference crystal feedback                                              |  |

| CLKA           | 6          | ock output                                                              |  |

| $V_{DD}$       | 7          | Voltage supply                                                          |  |

| REFCLK         | 8          | Reference clock output (default, can be driven by PLL if desired)       |  |

| S0             | 1          | Frequency select (CLKA) (internal pull-up resistor to V <sub>DD</sub> ) |  |

### **Functional Overview**

The CY2907 is a general purpose clock generator designed for use in a wide variety of applications — from graphics to PC peripherals to disk drives. It generates selectable system clock frequencies from a single reference input (crystal or reference clock). The CY2907 is configured with an EPROM array, similar to the other devices in the Cypress EPROM Programmable Clock family, making it easy to customize for any application. Furthermore, the CY2907 is compatible with all industry standard 9107 and 9108 clock synthesizers.

# **Device Programming**

Two versions of the CY2907 are available - Field Programmable and Factory Programmable. Field programmable devices must be programmed before being installed in an application. They are one-time-programmable (OTP). Customers can program small quantities in-house using the Cypress CY3670 programmer. Production quantities are available through Cypress's value-added distribution partners, or by using third party programmers from BP Microsystems, Hi-Lo Systems, and others.

For high volume orders, devices can be factory programmed by Cypress. All requests must be submitted to the local Cypress Field Application Engineer (FAE) or sales representative. After the request is processed, you receive a new part number, samples, and a data sheet with the programmed values. This part number is used for additional sample requests and production orders.

# CyberClocks™ Software

CyberClocks is an easy-to-use software application that enables the user to configure any one of the EPROM Programmable Clocks offered by Cypress. You may specify the input frequency, PLL and output frequencies, and different functional options. Note the output frequency ranges in this data sheet when specifying them in CyberClocks to make sure that you stay within the limits. After a configuration is established, you can print the configuration and save programming files in ENT and JED formats.

CyberClocks runs on PCs running the Windows™ operating system, and is available for free download on the Cypress Semiconductor website at www.cypress.com.

Within the CyberClocks application, the CY2907 is found in the CyClocks™ section. Note that the standalone CyberClocks software should not be confused with the CyberClocks Online software, which is a web-based application that is used to configure other programmable clock devices.

## **Cypress CY3670 Programming Kit**

Cypress's CY3670 is a portable programmer that connects to a PC serial port and enables users of CyClocks software to quickly and easily program any of the CY2291F, CY2292F, CY2071AF, and CY2907F devices. An adapter is also required and is ordered separately. The CY3097 is the adapter for the CY2907F8.

# **Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

Supply voltage .....-0.5 to +7.0 V Input voltage .....-0.5 V to V<sub>DD</sub> + 0.5 V

| Storage temperature (non-condensing)65 °C to            | +150 °C  |

|---------------------------------------------------------|----------|

| Max soldering temperature (10 sec)                      | +260 °C  |

| Junction temperature                                    | +150 °C  |

| Static discharge voltage (per MIL-STD-883, method 3015) | > 2000 V |

# **Operating Conditions**

| Parameter [3]    | Description                                | Min  | Max  | Unit |

|------------------|--------------------------------------------|------|------|------|

| $V_{DD}$         | Supply voltage, 5 V operation              |      | 5.5  | V    |

|                  | Supply voltage, 3.3 V operation            | 3.0  | 3.6  | V    |

| T <sub>A</sub>   | Commercial operating temperature, Ambient  | 0    | 70   | °C   |

| C <sub>L</sub>   | Maximum capacitive load                    | 1    | 15   | pF   |

| f <sub>REF</sub> | External reference crystal                 | 10.0 | 25.0 | MHz  |

|                  | External reference clock <sup>[4, 5]</sup> | 1.0  | 30.0 | MHz  |

### Notes

Document Number: 38-07137 Rev. \*K

Electrical parameters are guaranteed with these operating conditions.

Guaranteed by design, not 100% tested in production.

Load = max typical configuration, f<sub>REF</sub> = 14.318 MHz. Specific configurations may vary. A close approximation of I<sub>DD</sub> can be derived by the following formula: I<sub>DD</sub> (mA) = V<sub>DD</sub> × (6.25 + (0.055 × F<sub>REF</sub>) + (0.0017 × C<sub>LOAD</sub> × (F<sub>CLKA</sub> + REFCLK))). C<sub>LOAD</sub> is specified in pF and F is specified in MHz.

# **Electrical Characteristics**

At 5.0 V Commercial (V<sub>DD</sub> = 4.5 V to 5.5 V,  $T_A$  = 0 °C to +70 °C)

| Parameter                      | Description               | Test Conditions                                                      | Min | Max | Unit |

|--------------------------------|---------------------------|----------------------------------------------------------------------|-----|-----|------|

| V <sub>IH</sub>                | High-level input voltage  | Except crystal inputs                                                | 2.0 | _   | V    |

| V <sub>IL</sub>                | Low-level input voltage   | Except crystal inputs                                                | _   | 0.8 | V    |

| V <sub>OH</sub> <sup>[6]</sup> | High-level output voltage | V <sub>DD</sub> = V <sub>DD</sub> Min. I <sub>OH</sub> = -30 mA CLKA | 2.4 | _   | V    |

| V <sub>OL</sub> <sup>[6]</sup> | Low-level output voltage  | V <sub>DD</sub> = V <sub>DD</sub> Min. I <sub>OL</sub> = 10 mA CLKA  | _   | 0.4 | V    |

| I <sub>OH</sub> <sup>[6]</sup> | Output high current       | V <sub>OH</sub> = 2.0 V                                              | _   | -35 | mA   |

| I <sub>OL</sub> <sup>[6]</sup> | Output low current        | V <sub>OL</sub> = 0.8 V                                              | 22  | _   | mA   |

| I <sub>IH</sub>                | Input high current        | $V_{IH} = V_{DD}$                                                    | -2  | 2   | μA   |

| I <sub>IL</sub>                | Input low current         | V <sub>IL</sub> = 0 V                                                | _   | 20  | μA   |

| I <sub>DD</sub> <sup>[7]</sup> | Power supply current      | PD HIGH, CLKA = 50 MHz                                               | _   | 42  | mA   |

| I <sub>DD</sub>                | Power supply current      | PD LOW, Logic inputs LOW                                             | _   | 100 | μA   |

| I <sub>DD</sub>                | Power supply current      | PD LOW, Logic inputs HIGH                                            | _   | 40  | μA   |

| R <sub>PU</sub> <sup>[6]</sup> | Pull-up resistor          | $V_{IN} = V_{DD} - 1.0 \text{ V}$                                    | _   | 700 | kΩ   |

### **Electrical Characteristics**

At 3.3 V Commercial (V<sub>DD</sub> = 3.0 V to 3.6 V,  $T_A$  = 0 °C to +70 °C)

| Parameter                      | Description               | Test Conditions               | Min                    | Max                   | Unit |

|--------------------------------|---------------------------|-------------------------------|------------------------|-----------------------|------|

| V <sub>IH</sub>                | High-level input voltage  | Except crystal inputs         | 0.7 × V <sub>DD</sub>  | _                     | V    |

| $V_{IL}$                       | Low-level input voltage   | Except crystal inputs         | -                      | 0.2 × V <sub>DD</sub> | V    |

| V <sub>OH</sub> <sup>[6]</sup> | High-level output voltage | CLKA, I <sub>OH</sub> = –5 mA | 0.85 × V <sub>DD</sub> | _                     | V    |

| V <sub>OL</sub> <sup>[6]</sup> | Low-level output voltage  | CLKA, I <sub>OL</sub> = 6 mA  | -                      | 0.1 × V <sub>DD</sub> | V    |

| I <sub>OH</sub> <sup>[6]</sup> | Output high current       | $V_{OH} = 0.7 \times V_{DD}$  | -                      | -10                   | mA   |

| I <sub>OL</sub> <sup>[6]</sup> | Output low current        | $V_{OL} = 0.2 \times V_{DD}$  | 15                     | -                     | mA   |

| I <sub>IH</sub>                | Input high current        | $V_{IH} = V_{DD}$             | -2                     | 2                     | μA   |

| I <sub>IL</sub>                | Input low current         | V <sub>IL</sub> = 0 V         | -                      | 10                    | μA   |

| I <sub>DD</sub> <sup>[7]</sup> | Power supply current      | PD HIGH, CLKA = 50 MHz        | -                      | 40                    | mA   |

| I <sub>DD</sub>                | Power supply current      | PD LOW, Logic inputs LOW      | -                      | 40                    | μA   |

| I <sub>DD</sub>                | Power supply current      | PD LOW, Logic inputs HIGH     | -                      | 12                    | μA   |

| R <sub>PU</sub> <sup>[6]</sup> | Pull-up resistor          | $V_{IN} = V_{DD} - 0.5 V$     | _                      | 900                   | kΩ   |

Document Number: 38-07137 Rev. \*K Page 6 of 15

<sup>6.</sup> Guaranteed by design, not 100% tested in production.

7. Load = max. typical configuration, f<sub>REF</sub> = 14.318 MHz. Specific configurations may vary. A close approximation of I<sub>DD</sub> can be derived by the following formula: I<sub>DD</sub> (mA) = V<sub>DD</sub> × (6.25 + (0.055 × F<sub>REF</sub>) + (0.0017 × C<sub>LOAD</sub> × (F<sub>CLKA</sub> + REFCLK))). C<sub>LOAD</sub> is specified in pF and F is specified in MHz.

# **Switching Characteristics**

### At 5.0 V Commercial

| Parameter [8]    | Output [9] | Description                     | Test Conditions                      | Min  | Max   | Unit |

|------------------|------------|---------------------------------|--------------------------------------|------|-------|------|

| t <sub>R</sub>   | CLKA       | Output rise time 0.8 V to 2.0 V | 15 pF load                           | _    | 1.40  | ns   |

| t <sub>F</sub>   | CLKA       | Output fall time 2.0 V to 0.8 V | 15 pF load                           | _    | 1.00  | ns   |

| t <sub>R</sub>   | CLKA       | Output rise time 20% to 80%     | 15 pF load                           | _    | 3.5   | ns   |

| t <sub>F</sub>   | CLKA       | Output fall time 80% to 20%     | 15 pF load                           | _    | 2.5   | ns   |

| t <sub>D</sub>   | CLKA       | Duty cycle                      | 15 pF load at 1.4 V                  | 45.0 | 55.0  | %    |

| F <sub>I</sub>   | XTALIN     | Input frequency                 | Crystal oscillator                   | 10   | 25    | MHz  |

| F <sub>I</sub>   | XTALIN     | Input frequency                 | External input clock <sup>[10]</sup> | 1    | 30    | MHz  |

| F <sub>O</sub>   | CLKA       | Output frequency                | CY2907, 15 pF load                   | 0.5  | 130.0 | MHz  |

|                  |            |                                 | CY2907F, 15 pF load                  | 0.5  | 100.0 | MHz  |

| t <sub>JIS</sub> | CLKA       | Jitter (one sigma)              | 20 MHz to 130 MHz                    | _    | 150   | ps   |

| t <sub>JIS</sub> | CLKA       | Jitter (one sigma)              | 14 MHz to 20 MHz                     | _    | 200   | ps   |

| t <sub>JIS</sub> | CLKA       | Jitter (one sigma)              | Less than 14 MHz                     | _    | 1     | %    |

| t <sub>JAB</sub> | CLKA       | Jitter (absolute)               | 20 MHz to 130 MHz                    | -250 | + 250 | ps   |

| t <sub>JAB</sub> | CLKA       | Jitter (absolute)               | 14 MHz to 20 MHz                     | -500 | + 500 | ps   |

| t <sub>JAB</sub> | CLKA       | Jitter (absolute)               | Less than 14 MHz                     | _    | 3     | %    |

| t <sub>PU</sub>  |            | Power-up time                   |                                      | -    | 18    | ms   |

| t <sub>FT</sub>  | CLKA       | Transition time                 | 8 MHz to 66.6 MHz                    | _    | 13    | ms   |

Notes

8. Guaranteed by design, not 100% tested in production.

9. REFCLK output can also be configured to be driven by the PLL. In that case these characteristics are also valid.

10. Refer to the application note *Crystal Oscillator Topics* when using an external reference clock as an input frequency source.

# **Switching Characteristics**

### At 3.3 V Commercial

| Parameter [11]   | Output [12] | Description                 | Test Conditions                      | Min  | Max   | Unit |

|------------------|-------------|-----------------------------|--------------------------------------|------|-------|------|

| t <sub>R</sub>   | CLKA        | Output rise time 20% to 80% | 15 pF Load                           | _    | 3.5   | ns   |

| t <sub>F</sub>   | CLKA        | Output fall time 80% to 20% | 15 pF Load                           | _    | 2.5   | ns   |

| t <sub>D</sub>   | CLKA        | Duty cycle                  | 15 pF Load at 1.4 V                  | 40.0 | 53.0  | %    |

| F <sub>I</sub>   | XTALIN      | Input frequency             | Crystal Oscillator                   | 10   | 25    | MHz  |

| F <sub>I</sub>   | XTALIN      | Input frequency             | External Input Clock <sup>[13]</sup> | 1    | 30    | MHz  |

| F <sub>O</sub>   | CLKA        | Output frequency            | CY2907, 15 pF Load                   | 0.5  | 100.0 | MHz  |

|                  |             |                             | CY2907F, 15 pF Load                  | 0.5  | 80.0  | MHz  |

| t <sub>JIS</sub> | CLKA        | Jitter (one sigma)          | 25 MHz to 100 MHz                    | _    | 150   | ps   |

| t <sub>JIS</sub> | CLKA        | Jitter (one sigma)          | 14 MHz to 25 MHz                     | _    | 200   | ps   |

| t <sub>JIS</sub> | CLKA        | Jitter (one sigma)          | Less than 14 MHz                     | _    | 1     | %    |

| t <sub>JAB</sub> | CLKA        | Jitter (absolute)           | 25 MHz to 120 MHz                    | -250 | +250  | ps   |

| t <sub>JAB</sub> | CLKA        | Jitter (absolute)           | 14 MHz to 25 MHz                     | -500 | +500  | ps   |

| t <sub>JAB</sub> | CLKA        | Jitter (absolute)           | Less than 14 MHz                     | _    | 3     | %    |

| t <sub>PU</sub>  |             | Power-up time               |                                      | _    | 18    | ms   |

| t <sub>FT</sub>  | CLKA        | Transition time             | 8 MHz to 66.6 MHz                    | _    | 13    | ms   |

Notes

11. Guaranteed by design, not 100% tested in production.

12. REFCLK output can also be configured to be driven by the PLL. In that case these characteristics are also valid.

13. Refer to the application note *Crystal Oscillator Topics* when using an external reference clock as an input frequency source.

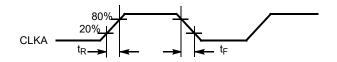

# **Switching Waveforms**

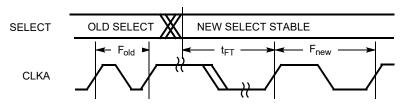

Figure 2. Frequency Select Change (Transition Time)

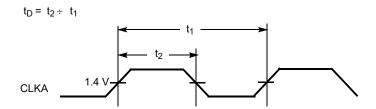

Figure 3. Duty Cycle Timing

Figure 4. All Outputs Rise/Fall Time

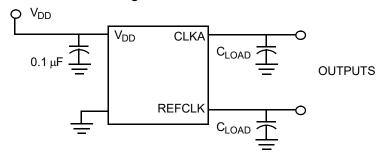

# **Test Circuit**

Figure 5. Test Circuit

Note: All capacitors should be placed as close to each pin as possible.

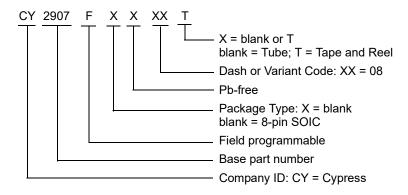

# **Ordering Information**

| Ordering Code   | Package Type               | Operating Range                                |

|-----------------|----------------------------|------------------------------------------------|

| Pb-free         |                            |                                                |

| CY2907FX8 [14]  | 8-pin SOIC                 | 5.0 V/3.3 V, Commercial,<br>Field programmable |

| CY2907FX8T [14] | 8-pin SOIC - Tape and Reel | 5.0 V/3.3 V, Commercial,<br>Field programmable |

# **Ordering Code Definitions**

# **Package Characteristics**

| Package    | θ <sub>JA</sub> (C/W) | θ <sub>JC</sub> (C/W) | Transistor Count |

|------------|-----------------------|-----------------------|------------------|

| 8-pin SOIC | 170                   | 35                    | 5436             |

### Note

Document Number: 38-07137 Rev. \*K

<sup>14.</sup> Not for new designs. New designs should use a device other than the CY2907.

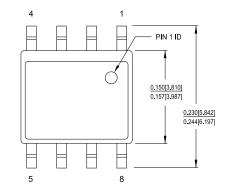

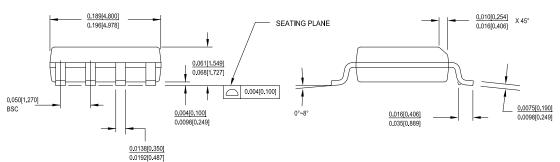

# **Package Diagrams**

Figure 6. 8-pin SOIC (150 Mils) S0815/SZ815/SW815 Package Outline, 51-85066

- 1. DIMENSIONS IN INCHES[MM] MIN.

- PIN 1 ID IS OPTIONAL,

ROUND ON SINGLE LEADFRAME

RECTANGULAR ON MATRIX LEADFRAME

- 3. REFERENCE JEDEC MS-012

- 4. PACKAGE WEIGHT 0.07gms

| PART#   |               |  |

|---------|---------------|--|

| S08.15  | STANDARD PKG  |  |

| SZ08.15 | LEAD FREE PKG |  |

| SW8.15  | LEAD FREE PKG |  |

51-85066 \*I

# **Acronyms**

| Acronym | Description                            |  |  |  |  |

|---------|----------------------------------------|--|--|--|--|

| EPROM   | Erasable Programmable Read Only Memory |  |  |  |  |

| OE      | Output Enable                          |  |  |  |  |

| PLL     | Phase-Locked Loop                      |  |  |  |  |

| SOIC    | Small-Outline Integrated Circuit       |  |  |  |  |

| TSSOP   | Thin-Shrink Small Outline Package      |  |  |  |  |

# **Document Conventions**

# **Units of Measure**

| Symbol | Unit of Measure   |  |  |  |

|--------|-------------------|--|--|--|

| °C     | degree Celsius    |  |  |  |

| kΩ     | kilohm            |  |  |  |

| MHz    | megahertz         |  |  |  |

| μA     | microampere       |  |  |  |

| mA     | milliampere       |  |  |  |

| ms     | millisecond       |  |  |  |

| mW     | milliwatt         |  |  |  |

| ns     | nanosecond        |  |  |  |

| ppm    | parts per million |  |  |  |

| %      | percent           |  |  |  |

| pF     | picofarad         |  |  |  |

| ps     | picosecond        |  |  |  |

| V      | volt              |  |  |  |

# **Document History Page**

| Document Title: CY2907, Single-PLL General Purpose EPROM Programmable Clock Generator Document Number: 38-07137 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Revision                                                                                                        | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                  |  |  |  |

| **                                                                                                              | 110246  | SZV                | 12/18/2001         | Changed from Spec number: 38-00505 to 38-07137.                                                                                                                                                                                                                                                                                        |  |  |  |

| *A                                                                                                              | 1088524 | KVM /<br>KKVTMP    | 05/21/2007         | Added Device Programming. Updated Ordering Information: Updated part numbers. Updated to new template.                                                                                                                                                                                                                                 |  |  |  |

| *B                                                                                                              | 2715646 | KVM /<br>AESA      | 06/10/2009         | Removed Industrial Temperature Range related information in all instances across the document. Removed Selector Guide. Updated Ordering Information: Updated part numbers. Added Note 14 and referred the same note in all MPNs except CY3670. Completing Sunset Review.                                                               |  |  |  |

| *C                                                                                                              | 2948496 | KVM                | 06/09/2010         | Updated Ordering Information: Updated part numbers. Updated Package Diagrams: spec 51-85066 – Changed revision from *C to *D. spec 51-85067 – Changed revision from *B to *C. Completing Sunset Review.                                                                                                                                |  |  |  |

| *D                                                                                                              | 3051170 | BASH               | 10/07/2010         | Updated Ordering Information: Updated part numbers. Added Ordering Code Definitions. Added Acronyms and Units of Measure. Minor edits.                                                                                                                                                                                                 |  |  |  |

| *E                                                                                                              | 3155189 | BASH               | 01/27/2011         | Minor Change: Post to external web.                                                                                                                                                                                                                                                                                                    |  |  |  |

| *F                                                                                                              | 3402027 | BASH               | 10/11/2011         | Updated Ordering Information: Updated part numbers. Updated Package Diagrams: spec 51-85066 – Changed revision from *D to *E. spec 51-85067 – Changed revision from *C to *D.                                                                                                                                                          |  |  |  |

| *G                                                                                                              | 4047640 | CINM               | 07/02/2013         | Updated Package Diagrams: spec 51-85066 – Changed revision from *E to *F. Completing Sunset Review.                                                                                                                                                                                                                                    |  |  |  |

| *H                                                                                                              | 4399810 | AJU                | 06/05/2014         | Added watermark "Not Recommended for New Designs". Updated to new template.                                                                                                                                                                                                                                                            |  |  |  |

| *                                                                                                               | 4587350 | AJU                | 12/05/2014         | Removed watermark "Not Recommended for New Designs". Updated Functional Description: Added "For a complete list of related documentation, click here." at the end. Updated Ordering Information: Updated part numbers.                                                                                                                 |  |  |  |

| *J                                                                                                              | 5366091 | TAVA               | 07/22/2016         | Removed 14-pin SOIC package related information in all instances across the document. Updated Logic Block Diagram. Updated Cypress CY3670 Programming Kit: Updated description. Updated Package Diagrams: spec 51-85066 – Changed revision from *F to *H. Removed spec 51-85067 *D. Updated to new template. Completing Sunset Review. |  |  |  |

# **Document History Page** (continued)

| Document Title: CY2907, Single-PLL General Purpose EPROM Programmable Clock Generator Document Number: 38-07137 |         |                    |                    |                                                                                                          |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

| Revision                                                                                                        | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                    |  |  |  |  |

| *K                                                                                                              | 6074874 | PAWK               |                    | Updated Package Diagrams:<br>spec 51-85066 – Changed revision from *H to *I.<br>Updated to new template. |  |  |  |  |

# Sales, Solutions, and Legal Information

### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

cypress.com/usb

cypress.com/wireless

### **Products**

USB Controllers

Wireless Connectivity

Arm® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Internet of Things cypress.com/iot Memory cypress.com/memory Microcontrollers cypress.com/mcu **PSoC** cypress.com/psoc Power Management ICs cypress.com/pmic Touch Sensing cypress.com/touch

### PSoC® Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

### **Cypress Developer Community**

Community | Projects | Video | Blogs | Training | Components

### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2001-2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 38-07137 Rev. \*K Revised February 19, 2018 Page 15 of 15

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Phase Locked Loops - PLL category:

Click to view products by Cypress manufacturer:

Other Similar products are found below:

HMC700LP4TR CPLL58-2400-2500 MB15E07SLPFV1-G-BND-6E1 PI6C2409-1HWEX BA4116FV-E2 HMC820LP6CETR

HMC828LP6CETR LMX2430TMX/NOPB HMC837LP6CETR HMC831LP6CETR NB3N5573DTG ADF4153ABCPZ PI6C2405A-1LE

CD74HC4046AM CPLL66-2450-2450 NJM567D CY23S05SXI-1 STW81200T ADF4208BRUZ ADF4218LBRUZ ADF4355-3BCPZ

ADF5355BCPZ ADF4355BCPZ ADF4169WCCPZ ADF4360-7BCPZ ADF4360-6BCPZ ADF4360-5BCPZRL7 ADF4360-5BCPZRL7 ADF4360-5BCPZ

ADF4360-4BCPZRL7 ADF4360-4BCPZ ADF4360-3BCPZ ADF4360-2BCPZRL7 ADF4252BCPZ ADF4159CCPZ ADF4169CCPZ

ADF4252BCPZ-R7 ADF4360-0BCPZ ADF4360-1BCPZ ADF4360-1BCPZRL7 ADF4360-2BCPZ ADF4360-3BCPZRL7 ADF43607BCPZRL7 ADF4360-8BCPZ ADF4360-8BCPZRL7 ADF4360-9BCPZRL7 ADF4360-9BCPZRL7 ADF4159CCPZ-RL7 ADF4159WCCPZ

ADF4360-0BCPZRL7 AD9901KPZ