# 2.5 V or 3.3 V, 200 MHz, 1:12 Clock Distribution Buffer

#### **Features**

- 2.5 V or 3.3 V operation

- 200 MHz clock support

- LVPECL or LVCMOS/LVTTL clock input

- LVCMOS-/LVTTL-compatible inputs

- 12 clock outputs: drive up to 24 clock lines

- Synchronous Output Enable

- Output three-state control

- 150 ps typical output-to-output skew

- Pin compatible with MPC948, MPC948L, MPC9448

- Available in Commercial and Industrial temp. range

- 32-pin TQFP package

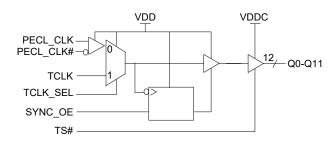

# **Functional Description**

The CY29948 is a low-voltage 200 MHz clock distribution buffer with the capability to select either a differential LVPECL or a LVCMOS/LVTTL compatible input clock. The two clock sources can be used to provide for a test clock as well as the primary system clock. All other control inputs are LVCMOS/LVTTL compatible. The 12 outputs are LVCMOS or LVTTL compatible and can drive 50  $\Omega$  series or parallel terminated transmission lines. For series terminated transmission lines, each output can drive one or two traces giving the device an effective fanout of 1:24. The outputs can also be three-stated via the three-state input TS#. Low output-to-output skews make the CY29948 an ideal clock distribution buffer for nested clock trees in the most demanding of synchronous systems.

The CY29948 also provides a synchronous output enable input for enabling or disabling the output clocks. Since this input is internally synchronized to the input clock, potential output glitching or runt pulse generation is eliminated.

For a complete list of related documentation, click here.

# **Block Diagram**

### **Contents**

| Pin Configuration         | 3 |

|---------------------------|---|

| Pin Description           |   |

| Output Enable/Disable     |   |

| Maximum Ratings           | 5 |

| DC Parameters             | 5 |

| Thermal Resistance        | 6 |

| AC Parameters             | 6 |

| Ordering Information      | 9 |

| Ordering Code Definitions | 9 |

| Package Diagrams          |   |

| Acronyms                                | 1              |

|-----------------------------------------|----------------|

| Document Conventions                    | 1 <sup>-</sup> |

| Units of Measure                        | 1 <sup>-</sup> |

| Document Revision History               | 12             |

| Sales, Solutions, and Legal Information | 13             |

| Worldwide Sales and Design Support      | 13             |

| Products                                | 13             |

| PSoC® Solutions                         | 13             |

| Cypress Developer Community             | 13             |

| Technical Support                       | 1:             |

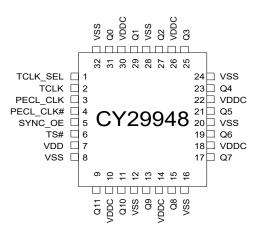

# **Pin Configuration**

Figure 1. 32-pin TQFP pinout

# **Pin Description**

| -                                                   |           |      |                                                                                                                              |                                                                                                                                   |  |

|-----------------------------------------------------|-----------|------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| Pin                                                 | Name      | PWR  | I/O <sup>[1]</sup>                                                                                                           | Description                                                                                                                       |  |

| 3                                                   | PECL_CLK  | -    | I, PU                                                                                                                        | PECL Input Clock                                                                                                                  |  |

| 4                                                   | PECL_CLK# | -    | I, PD                                                                                                                        | PECL Input Clock                                                                                                                  |  |

| 2                                                   | TCLK      | -    | I, PU External Reference/Test Clock Input                                                                                    |                                                                                                                                   |  |

| 9, 11, 13, 15,<br>17, 19, 21, 23,<br>25, 27, 29, 31 | Q(11:0)   | VDDC | O Clock Outputs                                                                                                              |                                                                                                                                   |  |

| 1                                                   | TCLK_SEL  | -    | I, PU                                                                                                                        | Clock Select Input. When LOW, PECL clock is selected. When HIGH TCLK is selected.                                                 |  |

| 5                                                   | SYNC_OE   | _    | I, PU  Output Enable Input. When asserted HIGH, the outputs are enable When set LOW the outputs are disabled in a LOW state. |                                                                                                                                   |  |

| 6                                                   | TS#       | -    | I, PU                                                                                                                        | Three-state Control Input. When asserted LOW, the output buffers are three-stated. When set HIGH, the output buffers are enabled. |  |

| 10, 14, 18, 22,<br>26, 30                           | VDDC      | -    | 2.5 V or 3.3 V Power Supply for Output Clock Buffers                                                                         |                                                                                                                                   |  |

| 7                                                   | VDD       | -    | - 2.5 V or 3.3 V Power Supply                                                                                                |                                                                                                                                   |  |

| 8, 12, 16, 20,<br>24, 28, 32                        | VSS       | -    | _                                                                                                                            | Common Ground                                                                                                                     |  |

Document Number: 38-07288 Rev. \*J

Note

1. PD = Internal pull-down, PU = Internal pull-up.

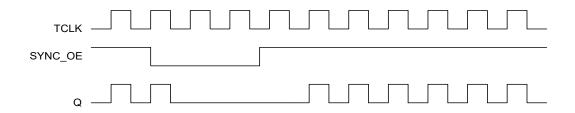

# **Output Enable/Disable**

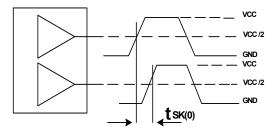

The CY29948 features a control input to enable or disable the outputs. This data is latched on the falling edge of the input clock. When SYNC\_OE is asserted LOW, the outputs are disabled in a LOW state. When SYNC\_OE is set HIGH, the outputs are enabled as shown in Figure 2.

Figure 2. SYNC\_OE Timing Diagram

# **Maximum Ratings**

Exceeding maximum ratings [2] may shorten the useful life of the device. User guidelines are not tested.

| Maximum Input Voltage Relative to $V_{\text{SS}}$             | $V_{SS} - 0.3 V$        |

|---------------------------------------------------------------|-------------------------|

| Maximum Input Voltage Relative to $V_{\mbox{\scriptsize DD}}$ | V <sub>DD</sub> + 0.3 V |

| Storage Temperature                                           | –65 °C to + 150 °C      |

| Operating Temperature                                         | –40 °C to +85 °C        |

| Maximum ESD protection                                        | 2 kV                    |

| Maximum Power Supply  | 5.5 V  |

|-----------------------|--------|

| Maximum Input Current | ±20 mA |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, V<sub>in</sub> and V<sub>out</sub> should be constrained to the range:

$$V_{SS} < (V_{in} \text{ or } V_{out}) < V_{DD}$$

Unused inputs must always be tied to an appropriate logic voltage level (either V<sub>SS</sub> or V<sub>DD</sub>).

### **DC Parameters**

$V_{DD}$  =  $V_{DDC}$  = 3.3 V ± 10% or 2.5 V ± 5%, over the specified temperature range.

| Parameter        | Description                         | Conditions                                                            | Min                   | Тур | Max            | Unit |

|------------------|-------------------------------------|-----------------------------------------------------------------------|-----------------------|-----|----------------|------|

| V <sub>IL</sub>  | Input Low Voltage                   | V <sub>DD</sub> = 3.3 V, PECL_CLK single ended                        | 1.49                  | 1   | 1.825          | V    |

|                  |                                     | V <sub>DD</sub> = 2.5 V, PECL_CLK single ended                        | 1.10                  | -   | 1.45           |      |

|                  |                                     | All other inputs                                                      | V <sub>SS</sub>       | -   | 0.8            |      |

| V <sub>IH</sub>  | Input High Voltage                  | V <sub>DD</sub> = 3.3 V, PECL_CLK single ended                        | 2.135                 | -   | 2.42           | V    |

|                  |                                     | V <sub>DD</sub> = 2.5 V, PECL_CLK single ended                        | 1.75                  | -   | 2.0            |      |

|                  |                                     | All other inputs                                                      | 2.0                   | -   | $V_{DD}$       |      |

| I <sub>IL</sub>  | Input Low Current [3]               |                                                                       | _                     | -   | -100           | μΑ   |

| I <sub>IH</sub>  | Input High Current [3]              |                                                                       | _                     | -   | 100            |      |

| V <sub>PP</sub>  | Peak-to-Peak Input Voltage PECL_CLK |                                                                       | 300                   | -   | 1000           | mV   |

| $V_{CMR}$        | Common Mode Range [4]               | V <sub>DD</sub> = 3.3 V                                               | V <sub>DD</sub> – 2.0 | 1   | $V_{DD} - 0.6$ | V    |

|                  | PECL_CLK                            | V <sub>DD</sub> = 2.5 V                                               | V <sub>DD</sub> – 1.2 | 1   | $V_{DD} - 0.6$ |      |

| V <sub>OL</sub>  | Output Low Voltage [5]              | I <sub>OL</sub> = 20 mA                                               | _                     | 1   | 0.4            | V    |

| V <sub>OH</sub>  | Output High Voltage [5]             | I <sub>OH</sub> = -20 mA, V <sub>DD</sub> = 3.3 V                     | 2.5                   | ı   | _              | V    |

|                  |                                     | $I_{OH} = -20 \text{ mA}, V_{DD} = 2.5 \text{ V}$                     | 1.8                   | ı   | _              |      |

| I <sub>DDQ</sub> | Quiescent Supply Current            |                                                                       | _                     | 5   | 7              | mA   |

| I <sub>DD</sub>  | Dynamic Supply Current              | V <sub>DD</sub> = 3.3 V, Outputs @ 100 MHz,<br>C <sub>L</sub> = 30 pF | -                     | 180 | _              | mA   |

|                  |                                     | V <sub>DD</sub> = 3.3 V, Outputs @ 160 MHz,<br>C <sub>L</sub> = 30 pF | -                     | 270 | _              |      |

|                  |                                     | V <sub>DD</sub> = 2.5 V, Outputs @ 100 MHz,<br>C <sub>L</sub> = 30 pF | -                     | 125 | _              |      |

|                  |                                     | V <sub>DD</sub> = 2.5 V, Outputs @ 160 MHz,<br>C <sub>L</sub> = 30 pF | -                     | 190 | _              |      |

| Z <sub>out</sub> | Output Impedance                    | V <sub>DD</sub> = 3.3 V                                               | 12                    | 15  | 18             | Ω    |

|                  |                                     | V <sub>DD</sub> = 2.5 V                                               | 14                    | 18  | 22             |      |

| C <sub>in</sub>  | Input Capacitance                   |                                                                       | _                     | 4   | _              | pF   |

- 2. Multiple Supplies: The voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is not required.

- 3. Inputs have pull-up/pull-down resistors that effect input current.

- The V<sub>CMR</sub> is the difference from the most positive side of the differential input signal. Normal operation is obtained when the "High" input is within the V<sub>CMR</sub> range and the input lies within the V<sub>PP</sub> specification.

Driving series or parallel terminated 50 Ω (or 50 Ω to V<sub>DD</sub>/2) transmission lines.

Document Number: 38-07288 Rev. \*J

### **Thermal Resistance**

| Parameter [6] | Description                           | Test Conditions                                                                                 | 32-pin TQFP | Unit |

|---------------|---------------------------------------|-------------------------------------------------------------------------------------------------|-------------|------|

| $\theta_{JA}$ |                                       | Test conditions follow standard test methods and procedures for measuring thermal impedance, in |             | °C/W |

| 30            | Thermal resistance (junction to case) | accordance with EIA/JESD51.                                                                     | 12          | °C/W |

# **AC Parameters**

$V_{DD}$  =  $V_{DDC}$  = 3.3 V ± 10% or 2.5 V ± 5%, over the specified operating range.

| Parameter [7]                       | Description                       | Conditions                              | Min  | Тур | Max  | Unit |

|-------------------------------------|-----------------------------------|-----------------------------------------|------|-----|------|------|

| F <sub>max</sub>                    | Input Frequency [8]               | V <sub>DD</sub> = 3.3 V                 | _    | _   | 200  | MHz  |

|                                     |                                   | V <sub>DD</sub> = 2.5 V                 | _    | _   | 170  |      |

| T <sub>pd</sub>                     | PECL_CLK to Q Delay [8]           | V <sub>DD</sub> = 3.3 V                 | 4.0  | _   | 8.0  | ns   |

|                                     | TCLK to Q Delay [8]               |                                         | 4.4  | _   | 8.9  |      |

|                                     | PECL_CLK to Q Delay [8]           | V <sub>DD</sub> = 2.5 V                 | 6.0  | _   | 10.0 |      |

|                                     | TCLK to Q Delay <sup>[8]</sup>    |                                         | 6.4  | _   | 10.9 |      |

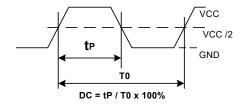

| F <sub>outDC</sub>                  | Output Duty Cycle [8, 9, 10]      | Measured at V <sub>DD</sub> /2          | 45   | _   | 55   | %    |

| t <sub>pZL</sub> , t <sub>pZH</sub> | Output Enable Time (all outputs)  |                                         | 2    | _   | 10   | ns   |

| t <sub>pLZ</sub> , t <sub>pHZ</sub> | Output Disable Time (all outputs) |                                         | 2    | _   | 10   | ns   |

| T <sub>skew</sub>                   | Output-to-Output Skew [8, 10]     |                                         | _    | 150 | 250  | ps   |

| T <sub>skew(pp)</sub>               | Part-to-Part Skew <sup>[11]</sup> | PECL_CLK to Q                           | _    | _   | 1.5  | ns   |

|                                     |                                   | TCLK to Q                               | _    | _   | 2.0  |      |

| T <sub>s</sub>                      | Set-up Time <sup>[8, 12]</sup>    | SYNC_OE to PECL_CLK                     | 1.0  | _   | _    | ns   |

|                                     |                                   | SYNC_OE to TCLK                         | 0.0  | _   | _    |      |

| T <sub>h</sub>                      | Hold Time <sup>[8, 12]</sup>      | PECL_CLK to SYNC_OE                     | 0.0  | -   | _    | ns   |

|                                     |                                   | TCLK to SYNC_OE                         | 1.0  | -   | _    |      |

| T <sub>r</sub> /T <sub>f</sub>      | Output Clocks Rise/Fall Time [10] | 0.8 V to 2.0 V, V <sub>DD</sub> = 3.3 V | 0.20 | _   | 1.0  | ns   |

|                                     |                                   | 0.6 V to 1.8 V, V <sub>DD</sub> = 2.5 V | 0.20 | -   | 1.3  |      |

- Notes

6. These parameters are guaranteed by design and are not tested.

7. Parameters are guaranteed by design and characterization. Not 100% tested in production. All parameters specified with loaded outputs.

8. Outputs driving 50Ω transmission lines.

9. 50% input duty cycle.

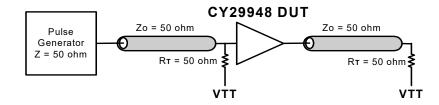

10. See Figure 3 on page 7 and Figure 4 on page 7.

11. Part-to-Part skew at a given temperature and voltage.

12. Setup and hold times are relative to the falling edge of the input clock.

Document Number: 38-07288 Rev. \*J

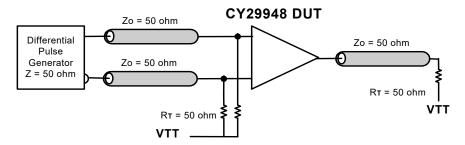

Figure 3. LVCMOS\_CLK CY29948 Test Reference for  $V_{CC}$  = 3.3 V and  $V_{CC}$  = 2.5 V

Figure 4. PECL\_CLK CY29948 Test Reference for  $\rm V_{CC}$  = 3.3 V and  $\rm V_{CC}$  = 2.5 V

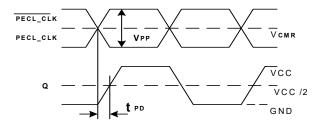

Figure 5. Propagation Delay (t<sub>PD</sub>) Test Reference

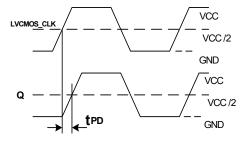

Figure 6. LVCMOS Propagation Delay (tpD) Test Reference

Figure 7. Output Duty Cycle ( $F_{outDC}$ )

Figure 8. Output-to-Output Skew tsk(0)

# **Ordering Information**

| Part Number | Package Type                                             | Production Flow            |

|-------------|----------------------------------------------------------|----------------------------|

| Pb-free     |                                                          |                            |

| CY29948AXC  | 32-pin TQFP Commercial, 0 °C to +70 °C                   |                            |

| CY29948AXCT | 32-pin TQFP – Tape and Reel                              | Commercial, 0 °C to +70 °C |

| CY29948AXI  | 32-pin TQFP Industrial, –40 °C to +85 °C                 |                            |

| CY29948AXIT | 32-pin TQFP – Tape and Reel Industrial, –40 °C to +85 °C |                            |

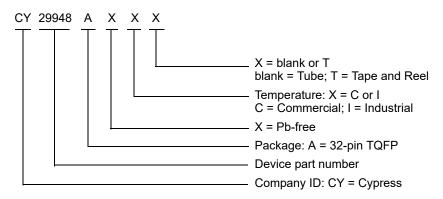

# **Ordering Code Definitions**

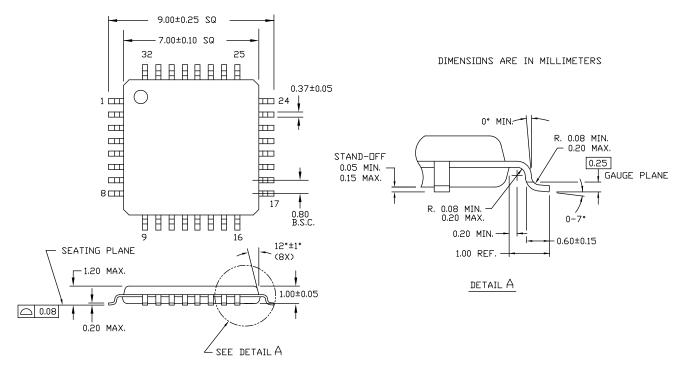

# **Package Diagrams**

Figure 9. 32-pin TQFP (7 × 7 × 1.0 mm) Package Outline, 51-85063

51-85063 \*E

# **Acronyms**

| Acronym | Description                                         |  |

|---------|-----------------------------------------------------|--|

| CMOS    | Complementary Metal Oxide Semiconductor             |  |

| ESD     | Electrostatic Discharge                             |  |

| I/O     | Input/Output                                        |  |

| LVCMOS  | Low Voltage Complementary Metal Oxide Semiconductor |  |

| LVPECL  | Low Voltage Positive Emitter Coupled Logic          |  |

| LVTTL   | Low Voltage Transistor-Transistor Logic             |  |

| PLL     | Phase Locked Loop                                   |  |

| TQFP    | Thin Quad Flat Pack                                 |  |

# **Document Conventions**

# **Units of Measure**

| Symbol | Unit of Measure |  |

|--------|-----------------|--|

| °C     | degree Celsius  |  |

| kV     | kilovolt        |  |

| MHz    | megahertz       |  |

| μA     | microampere     |  |

| mA     | milliampere     |  |

| mm     | millimeter      |  |

| mV     | millivolt       |  |

| ns     | nanosecond      |  |

| Ω      | ohm             |  |

| %      | percent         |  |

| pF     | picofarad       |  |

| ps     | picosecond      |  |

| V      | volt            |  |

# **Document Revision History**

| Document Title: CY29948, 2.5 V or 3.3 V, 200 MHz, 1:12 Clock Distribution Buffer<br>Document Number: 38-07288 |         |                    |                    |                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev.                                                                                                          | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                             |

| **                                                                                                            | 111099  | BRK                | 02/13/2002         | New data sheet.                                                                                                                                                                   |

| *A                                                                                                            | 116782  | HWT                | 08/14/2002         | Added Commercial Temperature Range related information in all instances across the document. Updated Ordering Information: Updated part numbers.                                  |

| *B                                                                                                            | 122880  | RBI                | 12/22/2002         | Updated Maximum Ratings:<br>Added Note 2 and referred the same note in "maximum ratings".                                                                                         |

| *C                                                                                                            | 428221  | RGL                | 02/21/2006         | Updated Ordering Information: Updated part numbers. Updated to new template.                                                                                                      |

| *D                                                                                                            | 2904731 | CXQ                | 04/05/2010         | Updated Ordering Information: Updated part numbers. Updated Package Diagrams: spec 51-85063 – Changed revision from *B to *C. Updated to new template.                            |

| *E                                                                                                            | 3246222 | CXQ                | 05/02/2011         | Updated Ordering Information: No change in part numbers. Added Ordering Code Definitions. Added Acronyms and Units of Measure. Updated to new template. Completing Sunset Review. |

| *F                                                                                                            | 3859773 | AJU                | 01/07/2013         | Updated Ordering Information: Updated part numbers. Updated Package Diagrams: spec 51-85063 – Changed revision from *C to *D.                                                     |

| *G                                                                                                            | 4345036 | XHT                | 04/14/2014         | Updated to new template. Completing Sunset Review.                                                                                                                                |

| *H                                                                                                            | 4586288 | XHT                | 12/03/2014         | Updated Functional Description: Added "For a complete list of related documentation, click here." at the end.                                                                     |

| *                                                                                                             | 5275785 | PSR                | 05/18/2016         | Added Thermal Resistance. Updated Package Diagrams: spec 51-85063 – Changed revision from *D to *E. Updated to new template.                                                      |

| *J                                                                                                            | 6142409 | XHT                | 04/17/2018         | Updated to new template. Completing Sunset Review.                                                                                                                                |

## Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

cypress.com/usb

cypress.com/wireless

#### **Products**

**USB Controllers**

Wireless Connectivity

Arm® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Internet of Things cypress.com/iot Memory cypress.com/memory Microcontrollers cypress.com/mcu **PSoC** cypress.com/psoc Power Management ICs cypress.com/pmic Touch Sensing cypress.com/touch

### PSoC® Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

#### **Cypress Developer Community**

Community | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2002-2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure: Therefore, despite security measures implemented in Cypress hardware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document, but not in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, unclear installations, life-support devices or system endical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or properly damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in par

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 38-07288 Rev. \*J Revised April 17, 2018 Page 13 of 13

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Buffer category:

Click to view products by Cypress manufacturer:

Other Similar products are found below:

PL133-27GI 9DBV0541AKLF 9DBV0941AKLF MPC962309EJ-1H NB3M8304CDG NB4N121KMNG NB7VQ58MMNG P5P2305AF1H08SR 8T39S11ANLGI 8T73S1802NLGI 9DBV0941AKILF MC10E111FNG MK2308S-1HILF 5PB1216NDGK 6V31024NLG

P5I2305AF-1H08SR PL133-27GI-R 9DBV0941AKILFT NB3L02FCT2G NB3L03FCT2G NB7VQ58MMNHTBG ZL40203LDG1

ZL40200LDG1 9DMV0141AKILFT ZL40205LDG1 ZL40212LDG1 ZL40201LDG1 9DBV0541AKILF PI49FCT32807QE 552-02SPGGI

9FG1200DF-1LF MDB1900ZCQY 9ZXL1530DKILF 8SLVP1102ANLGI/W ZL40223LDG1 5PB1203NTGK8 9FG1001BGLF

MDB1900ZBQY 5PB1214CMGK ZL40202LDG1 8L30205NLGI8 5PB1204CMGK 5PB1214CMGK8 5PB1203NTGK 5PB1206NDGK

PI49FCT20802QE MAX9317AECJ+ SL2305SC-1T PI6C10810HE 5P1103A517NLGI