# Crystal to LVPECL Clock Generator

### **Features**

- One LVPECL output pair

- Selectable frequency multiplication: × 2.5 or × 5

- External crystal frequency: 25.0 MHz

- Output frequency: 62.5 MHz or 125 MHz

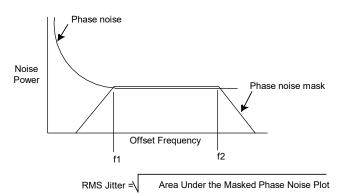

- Low RMS phase jitter at 125 MHz, using 25 MHz crystal (1.875 MHz to 20 MHz): 0.4 ps (typical)

- Phase noise at 125 MHz (typical):

| Offset  | Noise Power |

|---------|-------------|

| 1 kHz   | –117 dBc/Hz |

| 10 kHz  | –126 dBc/Hz |

| 100 kHz | –131 dBc/Hz |

| 1 MHz   | –131 dBc/Hz |

- Pb-free 8-pin TSSOP package

- Supply voltage: 3.3 V or 2.5 V

- Commercial and Industrial temperature range

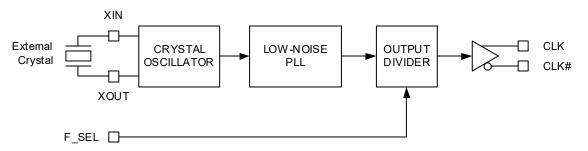

### Logic Block Diagram

### Functional Description

The CY2XP22 is a PLL (Phase Locked Loop) based high performance clock generator that uses an external reference crystal. It is specifically targeted at FibreChannel and Gigabit Ethernet applications. It produces a selectable output frequency that is 2.5 or 5 times the crystal frequency. With a 25 MHz crystal, the user can select either a 62.5 MHz or 125 MHz output. It uses Cypress's low noise VCO technology to achieve less than 1 ps typical RMS phase jitter. The CY2XP22 has a crystal oscillator interface input and one LVPECL output pair.

For a complete list of related documentation, click here.

## Contents

| 3 |

|---|

| 3 |

| 3 |

| 4 |

| 4 |

| 4 |

| 4 |

| 5 |

| 5 |

| 6 |

| 7 |

| 7 |

| 8 |

|   |

| 10 |

|----|

| 10 |

| 11 |

| 12 |

| 12 |

| 12 |

| 13 |

| 15 |

| 15 |

| 15 |

| 15 |

| 15 |

| 15 |

|    |

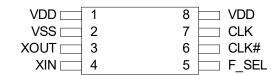

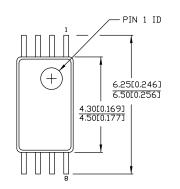

# Pinouts

#### Figure 1. 8-pin TSSOP pinout

# **Pin Definitions**

8-pin TSSOP

| Pin Number | Pin Name  | I/О Туре              | Description                           |

|------------|-----------|-----------------------|---------------------------------------|

| 1, 8       | VDD       | Power                 | 3.3 V or 2.5 V power supply           |

| 2          | VSS       | Power                 | Ground                                |

| 3, 4       | XOUT, XIN | XTAL output and input | Parallel resonant crystal interface   |

| 5          | F_SEL     | CMOS input            | Frequency Select: see Frequency Table |

| 6, 7       | CLK#, CLK | LVPECL output         | Differential clock output             |

# **Frequency Table**

| Inputs                  |       | PLL Multiplier Value | Output Frequency (MHz) |  |

|-------------------------|-------|----------------------|------------------------|--|

| Crystal Frequency (MHz) | F_SEL |                      | Output Frequency (MHZ) |  |

| 25                      | 0     | 5                    | 125                    |  |

|                         | 1     | 2.5                  | 62.5                   |  |

### **Application Information**

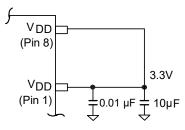

#### **Power Supply Filtering Techniques**

As in any high speed analog circuitry, noise at the power supply pins can degrade performance. To achieve optimum jitter performance, use good power supply isolation practices. Figure 2 illustrates a typical filtering scheme. Since all the current flows through pin 1, the resistance and inductance between this pin and the supply is minimized. A 0.01 or 0.1  $\mu$ F ceramic chip capacitor is also located close to this pin to provide a short and low impedance AC path to ground. A 1 to 10  $\mu$ F ceramic or tantalum capacitor is located in the general vicinity of this device and may be shared with other devices.

#### Figure 2. Power Supply Filtering

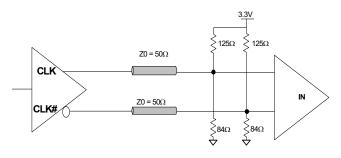

#### Termination for LVPECL Output

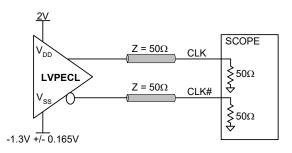

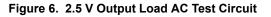

The CY2XP22 implements its LVPECL driver with a current steering design. For proper operation, it requires a 50 ohm dc termination on each of the two output signals. For 3.3 V operation, this data sheet specifies output levels for termination to  $V_{DD} - 2.0$  V. This same termination voltage can also be used for  $V_{DD} = 2.5$  V operation, or it can be terminated to  $V_{DD} - 1.5$  V. Note that it is also possible to terminate with 50 ohms to ground (V<sub>SS</sub>), but the high and low signal levels differ from the data sheet values. Termination resistors are best located close to the destination device. To avoid reflections, trace characteristic impedance (Z<sub>0</sub>) should match the termination impedance. Figure 3 shows a standard termination scheme.

#### Figure 3. LVPECL Output Termination

#### **Crystal Interface**

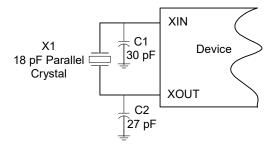

The CY2XP22 is characterized with 18 pF parallel resonant crystals. The capacitor values shown in Figure 4 are determined using a 25 MHz 18 pF parallel resonant crystal and are chosen to minimize the ppm error. Note that the optimal values for C1 and C2 depend on the parasitic trace capacitance and are thus layout dependent.

#### Figure 4. Crystal Input Interface

### **Absolute Maximum Conditions**

| Parameter                      | Description                         | Conditions                  | Min  | Max                   | Unit |

|--------------------------------|-------------------------------------|-----------------------------|------|-----------------------|------|

| V <sub>DD</sub>                | Supply Voltage                      |                             | -0.5 | 4.4                   | V    |

| V <sub>IN</sub> <sup>[1]</sup> | Input Voltage, DC                   | Relative to V <sub>SS</sub> | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| Τ <sub>S</sub>                 | Temperature, Storage                | Non operating               | -65  | 150                   | °C   |

| Tj                             | Temperature, Junction               |                             | -    | 135                   | °C   |

| ESD <sub>HBM</sub>             | ESD Protection, Human Body<br>Model | JEDEC STD 22-A114-B         | 2000 | -                     | V    |

| UL-94                          | Flammability Rating                 | At 1/8 in.                  | V-0  |                       |      |

| $\Theta_{JA}^{[2]}$            |                                     | 0 m/s airflow               | 1(   | 00                    | °C/W |

|                                | Ambient                             | 1 m/s airflow               | 9    | 1                     |      |

|                                |                                     | 2.5 m/s airflow             | 8    | 7                     |      |

# **Operating Conditions**

| Parameter       | Description                                                                                         |       | Мах   | Unit |

|-----------------|-----------------------------------------------------------------------------------------------------|-------|-------|------|

| V <sub>DD</sub> | 3.3 V Supply Voltage                                                                                | 3.135 | 3.465 | V    |

|                 | 2.5 V Supply Voltage                                                                                | 2.375 | 2.625 | V    |

| T <sub>A</sub>  | Ambient Temperature, Commercial                                                                     |       | 70    | °C   |

|                 | Ambient Temperature, Industrial                                                                     |       | 85    | °C   |

| T <sub>PU</sub> | Power up time for all $V_{DD}$ to reach minimum specified voltage (ensure power ramps is monotonic) | 0.05  | 500   | ms   |

Notes

The voltage on any input or IO pin cannot exceed the power pin during power up.

Simulated using Apache Sentinel TI software. The board is derived from the JEDEC multilayer standard. It measures 76 x 114 x 1.6 mm and has 4-layers of copper (2/1/1/2 oz.). The internal layers are 100% copper planes, while the top and bottom layers have 50% metalization. No vias are included in the model.

# **DC Electrical Characteristics**

| Parameter                       | Description                                                                 | Test Conditions                                                                   | Min                    | Тур | Max                     | Unit |

|---------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------|-----|-------------------------|------|

| I <sub>DD</sub>                 | Operating Supply Current with<br>output unterminated                        | V <sub>DD</sub> = 3.465 V, F <sub>OUT</sub> = 125 MHz,<br>output unterminated     | -                      | _   | 125                     | mA   |

|                                 |                                                                             | V <sub>DD</sub> = 2.625 V, F <sub>OUT</sub> = 125 MHz,<br>output unterminated     | _                      | -   | 120                     | mA   |

| I <sub>DDT</sub>                | Operating Supply Current with<br>output terminated                          | V <sub>DD</sub> = 3.465 V, F <sub>OUT</sub> = 125 MHz,<br>output terminated       | _                      | -   | 150                     | mA   |

|                                 |                                                                             | V <sub>DD</sub> = 2.625 V, F <sub>OUT</sub> = 125 MHz,<br>output terminated       | _                      | -   | 145                     | mA   |

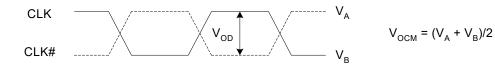

| V <sub>OH</sub>                 | LVPECL Output High Voltage                                                  | $V_{DD}$ = 3.3 V or 2.5 V,<br>R <sub>TERM</sub> = 50 Ω to V <sub>DD</sub> – 2.0 V | V <sub>DD</sub> – 1.15 | -   | V <sub>DD</sub> – 0.75  | V    |

| V <sub>OL</sub>                 | LVPECL Output Low Voltage                                                   | $V_{DD}$ = 3.3 V or 2.5 V,<br>R <sub>TERM</sub> = 50 Ω to V <sub>DD</sub> – 2.0 V | V <sub>DD</sub> – 2.0  | -   | V <sub>DD</sub> – 1.625 | V    |

| V <sub>OD1</sub>                | LVPECL Peak-to-Peak Output<br>Voltage Swing                                 | $V_{DD}$ = 3.3 V or 2.5 V,<br>R <sub>TERM</sub> = 50 Ω to V <sub>DD</sub> – 2.0 V | 600                    | -   | 1000                    | mV   |

| V <sub>OD2</sub>                | LVPECL Output Voltage Swing $(V_{OH} - V_{OL})$                             | $V_{DD}$ = 2.5 V,<br>R <sub>TERM</sub> = 50 Ω to V <sub>DD</sub> – 1.5 V          | 500                    | -   | 1000                    | mV   |

| V <sub>OCM</sub>                | LVPECL Output Common Mode<br>Voltage (V <sub>OH</sub> + V <sub>OL</sub> )/2 | $V_{DD}$ = 2.5 V,<br>R <sub>TERM</sub> = 50 Ω to V <sub>DD</sub> – 1.5 V          | 1.2                    | -   | _                       | V    |

| V <sub>IH</sub>                 | Input High Voltage, F_SEL                                                   |                                                                                   | 0.7 × V <sub>DD</sub>  | -   | V <sub>DD</sub> + 0.3   | V    |

| V <sub>IL</sub>                 | Input Low Voltage, F_SEL                                                    |                                                                                   | -0.3                   | -   | 0.3 × V <sub>DD</sub>   | V    |

| IIH                             | Input High Current, F_SEL                                                   | F_SEL = V <sub>DD</sub>                                                           | -                      | _   | 115                     | μA   |

| IIL                             | Input Low Current, F_SEL                                                    | F_SEL = V <sub>SS</sub>                                                           | -50                    | _   | _                       | μA   |

| C <sub>IN</sub> <sup>[3]</sup>  | Input Capacitance, F_SEL                                                    |                                                                                   | -                      | 15  | -                       | pF   |

| C <sub>INX</sub> <sup>[3]</sup> | Pin Capacitance, XIN & XOUT                                                 |                                                                                   | _                      | 4.5 | -                       | pF   |

# **AC Electrical Characteristics**

| Parameter <sup>[4]</sup>        | Description               | Conditions                                                                           | Min  | Тур | Max | Unit |

|---------------------------------|---------------------------|--------------------------------------------------------------------------------------|------|-----|-----|------|

| F <sub>OUT</sub>                | Output Frequency          |                                                                                      | 62.5 | -   | 125 | MHz  |

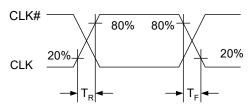

| T <sub>R</sub> , T <sub>F</sub> | Output Rise or Fall Time  | 20% to 80% of full output swing                                                      | -    | 0.5 | 1.0 | ns   |

| T <sub>Jitter(\u00f6)</sub>     | RMS Phase Jitter (Random) | 125 MHz, (1.875–20 MHz)                                                              | -    | 0.4 | -   | ps   |

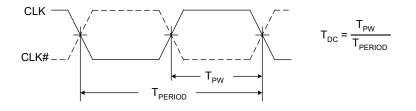

| T <sub>DC</sub>                 | Output Duty Cycle         | Measured at zero crossing point                                                      | 48   | 50  | 52  | %    |

| T <sub>LOCK</sub>               | Startup Time              | Time for CLK to reach valid frequency measured from the time $V_{DD} = V_{DD}(min.)$ | _    | -   | 5   | ms   |

| T <sub>LFS</sub>                | Re-lock Time              | Time for CLK to reach valid<br>frequency from F_SEL pin change                       | -    | -   | 1   | ms   |

# **Recommended Crystal Specifications**

| Parameter <sup>[5]</sup> | Description                     | Min | Max    | Unit |

|--------------------------|---------------------------------|-----|--------|------|

| Mode                     | Mode of Oscillation Fundamental |     | mental |      |

| F                        | Frequency                       | 25  | 25     | MHz  |

| ESR                      | Equivalent Series Resistance    |     | 50     | Ω    |

| C <sub>0</sub>           | Shunt Capacitance               | -   | 7      | pF   |

Notes

Not 100% tested, guaranteed by design and characterization.

Characterized using an 18 pF parallel resonant crystal.

### **Parameter Measurements**

#### Figure 5. 3.3 V Output Load AC Test Circuit

Figure 7. Output DC Parameters

Figure 8. Output Rise and Fall Time

### Parameter Measurements (continued)

Figure 10. Output Duty Cycle

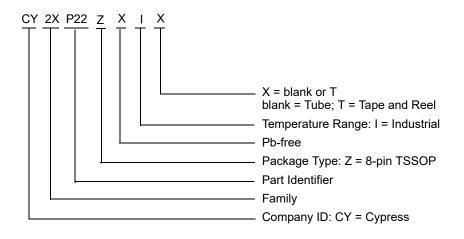

## **Ordering Information**

| Part Number | Package Type                | Product Flow                |  |

|-------------|-----------------------------|-----------------------------|--|

| CY2XP22ZXI  | 8-pin TSSOP                 | Industrial, –40 °C to 85 °C |  |

| CY2XP22ZXIT | 8-pin TSSOP – Tape and Reel | Industrial, –40 °C to 85 °C |  |

#### **Ordering Code Definitions**

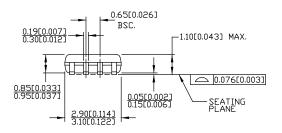

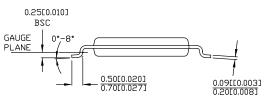

# Package Diagram

Figure 11. 8-pin TSSOP (4.40 mm Body) Package Outline, 51-85093

DIMENSIONS IN MMEINCHESS MIN. MAX.

REFERENCE JEDEC MD-153

| PART #   |                |  |

|----------|----------------|--|

| Z08.173  | STANDARD PKG.  |  |

| ZZ08.173 | LEAD FREE PKG. |  |

51-85093 \*E

# Acronyms

| Acronym | Description                                |  |  |  |  |

|---------|--------------------------------------------|--|--|--|--|

| CLKOUT  | Clock Output                               |  |  |  |  |

| CMOS    | Complementary Metal Oxide Semiconductor    |  |  |  |  |

| DPM     | Die Pick Map                               |  |  |  |  |

| EPROM   | Erasable Programmable Read Only Memory     |  |  |  |  |

| LVDS    | Low-Voltage Differential Signaling         |  |  |  |  |

| LVPECL  | Low-Voltage Positive Emitter Coupled Logic |  |  |  |  |

| NTSC    | National Television System Committee       |  |  |  |  |

| OE      | Output Enable                              |  |  |  |  |

| PAL     | Phase Alternate Line                       |  |  |  |  |

| PD      | Power-Down                                 |  |  |  |  |

| PLL     | Phase Locked Loop                          |  |  |  |  |

| TTL     | Transistor-Transistor Logic                |  |  |  |  |

# **Document Conventions**

#### **Units of Measure**

| Symbol | Unit of Measure             |  |  |  |

|--------|-----------------------------|--|--|--|

| °C     | degree Celsius              |  |  |  |

| kHz    | kilohertz                   |  |  |  |

| kΩ     | kilohm                      |  |  |  |

| MHz    | megahertz                   |  |  |  |

| MΩ     | megaohm                     |  |  |  |

| μA     | microampere                 |  |  |  |

| μs     | microsecond                 |  |  |  |

| μV     | microvolt                   |  |  |  |

| μVrms  | microvolts root-mean-square |  |  |  |

| mA     | milliampere                 |  |  |  |

| mm     | millimeter                  |  |  |  |

| ms     | millisecond                 |  |  |  |

| mV     | millivolt                   |  |  |  |

| nA     | nanoampere                  |  |  |  |

| ns     | nanosecond                  |  |  |  |

| nV     | nanovolt                    |  |  |  |

| Ω      | ohm                         |  |  |  |

| ppm    | parts per million           |  |  |  |

| V      | volt                        |  |  |  |

# **Document History Page**

| Document Title: CY2XP22, Crystal to LVPECL Clock Generator<br>Document Number: 001-10229 |                               |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ECN                                                                                      | Orig. of<br>Change            | Submission<br>Date                                                                                                   | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 506262                                                                                   | RGL                           | 09/27/2006                                                                                                           | New data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 838060                                                                                   | RGL                           | 03/12/2007                                                                                                           | Changed status from Advance to Preliminary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 838060                                                                                   | KVM /<br>PYRS                 | 03/12/2007<br>04/30/2009                                                                                             | Changed status from Advance to Preliminary<br>Updated Features:<br>Updated Peatures:<br>Updated Pinouts:<br>Replaced VCC with VDD.<br>Replaced VCC with VDD.<br>Updated Pin Definitions:<br>Replaced VCC with VDD.<br>Replaced VCE with VSS.<br>Updated details in "I/O Type" and "Description" columns for all pins.<br>Updated Frequency Table:<br>Added a column "PLL Multiplier Value" and added details in that column.<br>Updated Application Information:<br>Updated Application Information:<br>Updated Power Supply Filtering Techniques:<br>Updated feigure 2.<br>Updated description.<br>Removed "Termination for 3.3V LVPECL Output".<br>Added account "PLL Multiplier Value" and added details in that column.<br>Updated description.<br>Removed "Termination for 3.3V LVPECL Output".<br>Added Crystal Interface:<br>Updated Absolute Maximum Conditions:<br>Replaced V <sub>CC</sub> , V <sub>CC</sub> with V <sub>DD</sub> .<br>Changed maximum value of T <sub>J</sub> parameter from 125 °C to 135 °C.<br>Added Operating Conditions:<br>Replaced V <sub>CC</sub> , V <sub>CCA</sub> with V <sub>DD</sub> .<br>Added Industrial Temperature Range corresponding to T <sub>A</sub> parameter.<br>Removed "Electrical Characteristics for LVPECL".<br>Added DC Electrical Characteristics.<br>Updated AC Electrical Characteristics.<br>Updated AC Electrical Characteristics.<br>Removed Note "Refer to Figure 2 on page 4" and its reference.<br>Removed Note "Refer to Figure 2 on page 4" and its reference.<br>Removed Note "Refer to Figure 3 on page 4" and its reference.<br>Updated details in "Min", "Typ" and "Max" columns corresponding to T <sub>DC</sub> parameter.<br>Added T <sub>LOCK</sub> parameter and its details.<br>Updated Recommended Crystal Specifications:<br>Removed Resonance Type" parameter and its details. |  |

|                                                                                          | ECN       506262       838060 | Number: 001-10229       ECN     Orig. of<br>Change       506262     RGL       838060     RGL       2700242     KVM / | Number: 001-10229       ECN     Orig. of<br>Change     Submission<br>Date       506262     RGL     09/27/2006       838060     RGL     03/12/2007       2700242     KVM /     04/30/2009                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

# Document History Page (continued)

| Revision   | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|---------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *B (cont.) | 2700242 | KVM /<br>PYRS      | 04/30/2009         | Updated Parameter Measurements:<br>Removed figure "Output Load Test Circuit".<br>Removed figure "Output Duty Cycle/Pulse Width/Period".<br>Removed figure "Output Rise/Fall Time and Peak-PeakVoltage Swing".<br>Added Figure 5.<br>Added Figure 6.<br>Added Figure 7.<br>Added Figure 8.<br>Added Figure 8.<br>Added Figure 10.<br>Updated Ordering Information:<br>Updated part numbers.<br>Updated to new template.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| *C         | 2718898 | WWZ                | 06/15/2009         | Minor Change:<br>Post to external web.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| *D         | 2767298 | KVM                | 09/22/2009         | Updated DC Electrical Characteristics:<br>Replaced I <sub>DD</sub> with I <sub>DDT</sub> in "Parameter" column (for terminated outputs).<br>Add I <sub>DD</sub> parameter and its details (for unterminated outputs).<br>Removed Note "I <sub>DD</sub> includes approximately 24 mA of current that is dissipated<br>externally in the output termination resistors." and its reference.<br>Added Note 3 and referred the same note in C <sub>IN</sub> and C <sub>INX</sub> parameters.<br>Updated AC Electrical Characteristics:<br>Added 1.0 ns under "Max" column corresponding to T <sub>R</sub> , T <sub>F</sub> parameter.<br>Updated details in "Test Conditions" column corresponding to T <sub>LOCK</sub><br>parameter.<br>Changed maximum value of T <sub>LOCK</sub> parameter from 10 ms to 5 ms.<br>Added T <sub>LFS</sub> parameter and its details. |

| *E         | 2896121 | KVM                | 03/19/2010         | Updated Package Diagram:<br>spec 51-85093 – Changed revision from *A to *B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| *F         | 3219081 | BASH               | 04/07/2011         | Changed status from Preliminary to Final.<br>Updated Ordering Information:<br>No change in part numbers.<br>Added Ordering Code Definitions.<br>Updated Package Diagram:<br>spec 51-85093 – Changed revision from *B to *C.<br>Added Acronyms and Units of Measure.<br>Updated to new template.<br>Completing Sunset Review.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| *G         | 4336622 | ХНТ                | 05/02/2014         | Updated Package Diagram:<br>spec 51-85093 – Changed revision from *C to *D.<br>Updated to new template.<br>Completing Sunset Review.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| *H         | 4570097 | ХНТ                | 11/14/2014         | Updated Functional Description:<br>Added "For a complete list of related documentation, click here." at the end.<br>Updated Ordering Information:<br>Updated part numbers.<br>Updated Package Diagram:<br>spec 51-85093 – Changed revision from *D to *E.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| *          | 6135134 | XHT                | 04/12/2018         | Updated to new template.<br>Completing Sunset Review.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| Arm <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

### PSoC<sup>®</sup> Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

Cypress Developer Community Community | Projects | Video | Blogs | Training | Components

Technical Support cypress.com/support

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or system could cause personal injury, death, or properly damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 001-10229 Rev. \*I

<sup>©</sup> Cypress Semiconductor Corporation, 2006-2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Phase Locked Loops - PLL category:

Click to view products by Cypress manufacturer:

Other Similar products are found below :

ADF4152HVBCPZ-RL7 HMC440QS16GTR LC72135MA-Q-AE SL28EB725ALI HMC699LP5ETR HMC700LP4TR LC7185-8750-E MB15E07SLPFV1-G-BND-6E1 XRT8001ID-F ATA8404C-6DQY-66 PI6C2409-1HWE ATA8405C-6DQY-66 MAX2870ETJ+T PI6C2409-1HWEX CYW170-01SXC HMC764LP6CETR HMC767LP6CETR HMC820LP6CETR HMC828LP6CETR HMC834LP6GETR ispPAC-CLK5410D-01SN64C SI4113-D-GM 82V3002APVG PI6C2405A-1WE CY22050KFI CY25200KFZXC CY29973AXI CY2XP22ZXI W232ZXC-10 CDCE937QPWRQ1 CY2077FZXI CY2546FC CY2XF23FLXIT CYISM560BSXC LMX2430TMX/NOPB HMC837LP6CETR HMC831LP6CETR ATA8404C-6DQY-66 ADF4155BCPZ-RL7 MB15E07SRPFT-G-BNDE1 NB3N5573DTG MAX2660EUT+T SI4123-D-GT SI4112-D-GM NB4N441MNR2G ADF4116BRUZ-REEL7 ADF4153ABCPZ MAX2682EUT+T Si5376B-A-GL SI5347A-A-GM