## CY8CKIT-062-WiFi-BT

# PSoC® 6 WiFi-BT Pioneer Kit Guide

Doc. # 002-22677 Rev. \*B

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 www.cypress.com

#### Copyrights

© Cypress Semiconductor Corporation, 2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice.

Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# Contents

| Safety Information 5 |          |                                                                     |    |  |

|----------------------|----------|---------------------------------------------------------------------|----|--|

| 1.                   | Introdu  | ction                                                               | 6  |  |

|                      | 1.1      | Kit Contents                                                        | 7  |  |

|                      | 1.2      | Hardware Introduction                                               |    |  |

|                      |          | 1.2.1 CY8CKIT-062-WiFi-BT Board Details                             |    |  |

|                      |          | 1.2.2 CY8CKIT-028-TFT Board Details                                 | 10 |  |

|                      | 1.3      | Software Introduction                                               | 11 |  |

|                      |          | 1.3.1 PSoC Creator Overview                                         | 11 |  |

|                      |          | 1.3.2 WICED Studio Development System Overview                      | 12 |  |

|                      | 1.4      | Getting Started                                                     | 15 |  |

|                      | 1.5      | Additional Learning Resources                                       | 15 |  |

|                      | 1.6      | Technical Support                                                   | 15 |  |

|                      | 1.7      | Documentation Conventions                                           | 16 |  |

|                      | 1.8      | Acronyms                                                            | 16 |  |

| 2.                   | PSoC C   | reator                                                              | 18 |  |

|                      | 2.1      | Before You Begin                                                    | 18 |  |

|                      | 2.2      | Install Kit Software                                                |    |  |

|                      | 2.3      | Programming and Debugging using PSoC Creator                        |    |  |

|                      | 2.4      | Kit Code Examples                                                   |    |  |

|                      |          | 2.4.1 Using the Kit Code Examples Built in PSoC Creator             | 21 |  |

| 3.                   | WICED    |                                                                     | 24 |  |

|                      | 3.1      | Introduction                                                        | 24 |  |

|                      | 3.2      | Before You Begin                                                    | 24 |  |

|                      | 3.3      | Install WICED                                                       | 24 |  |

|                      | 3.4      | Programming and Debugging in WICED                                  | 25 |  |

|                      |          | 3.4.1 Building and Programming a Project for CY8CKIT-062-WiFi-BT in |    |  |

|                      |          | WICED Studio IDE                                                    |    |  |

|                      | 0.5      | 3.4.2 Debugging a Project using Breakpoints                         |    |  |

|                      | 3.5      | Kit Code Example                                                    |    |  |

|                      |          | 3.5.1 Building and Programming a Project in the WICED Studio IDE    | 33 |  |

| 4.                   | Kit Hard |                                                                     | 38 |  |

|                      | 4.1      | CY8CKIT-062-WiFi-BT Details                                         |    |  |

|                      | 4.2      | CY8CKIT-028-TFT Details                                             |    |  |

|                      |          | 4.2.1 CY8CKIT-028-TFT Display Shield                                |    |  |

|                      | 4.3      | KitProg2                                                            |    |  |

|                      |          | 4.3.1 Introduction                                                  |    |  |

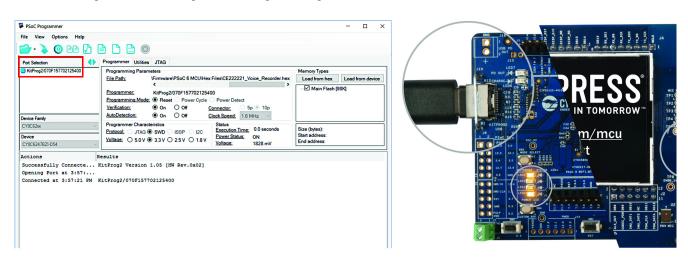

|                      |          | 4.3.2 Programming using PSoC Programmer                             |    |  |

|                      |          | 4.3.3 Kit Enumeration and Programming Modes of KitProg2             | 53 |  |

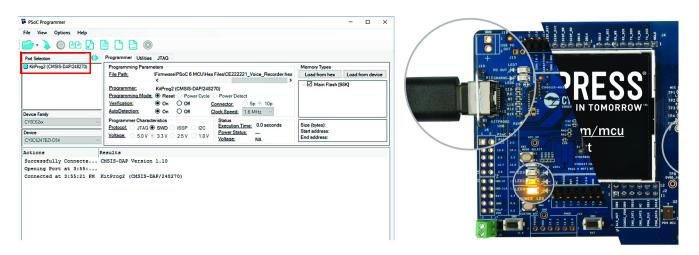

|    |          | 4.3.4 USB-UART Bridge                                             | 54 |

|----|----------|-------------------------------------------------------------------|----|

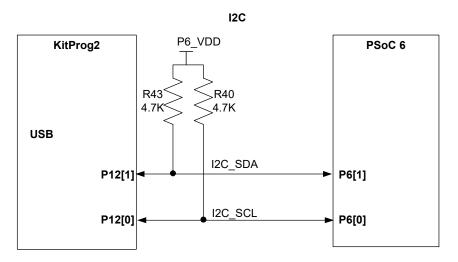

|    |          | 4.3.5 USB-I2C Bridge                                              | 55 |

|    |          | 4.3.6 USB-SPI Bridge                                              | 55 |

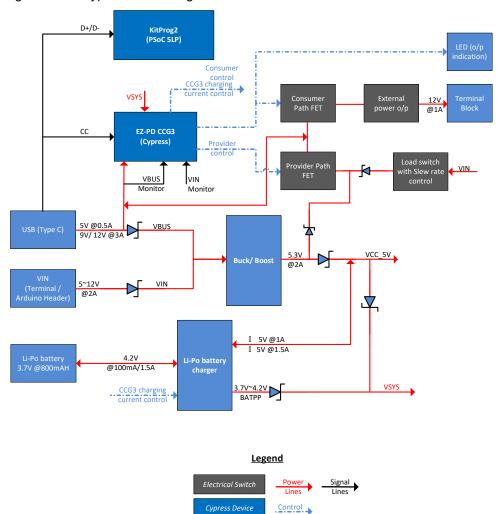

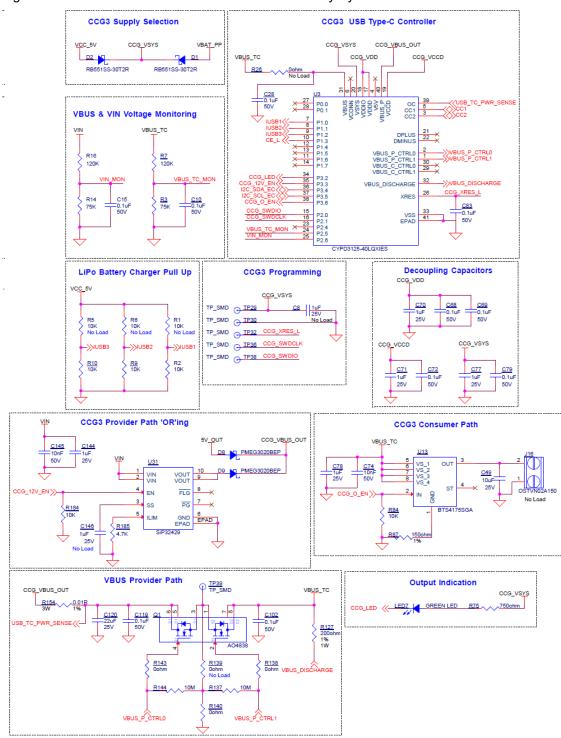

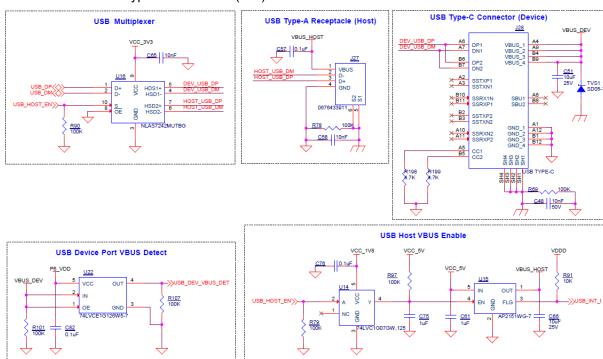

|    | 4.4      | EZ-PD CCG3 Type-C Power Delivery                                  |    |

| _  |          |                                                                   |    |

| Α. | Append   | ix                                                                | 58 |

|    | A.1      | Schematics                                                        | 58 |

|    | A.2      | Hardware Functional Description                                   | 58 |

|    |          | A.2.1 PSoC 6 MCU (U1)                                             | 58 |

|    |          | A.2.2 PSoC 5LP (U2)                                               |    |

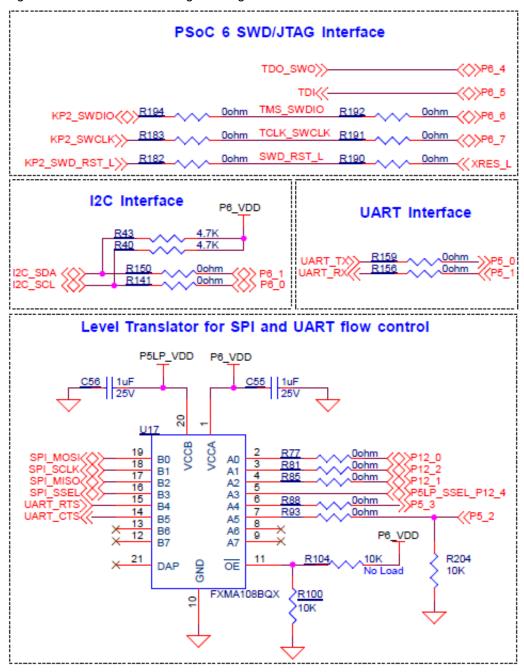

|    |          | A.2.3 Serial Interconnection between PSoC 5LP and PSoC 6 MCU      | 59 |

|    |          | A.2.4 EZ-PD CCG3 Power Delivery System                            | 60 |

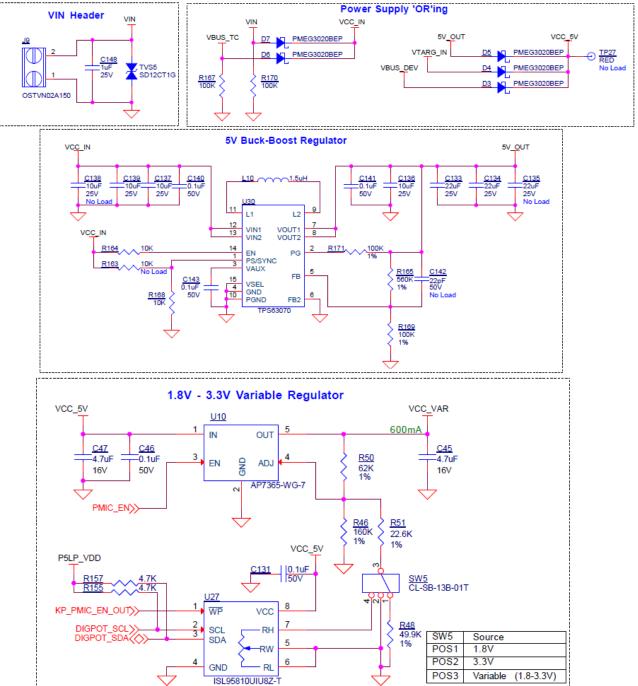

|    |          | A.2.5 Power Supply System                                         | 61 |

|    |          | A.2.6 Expansion Connectors                                        | 64 |

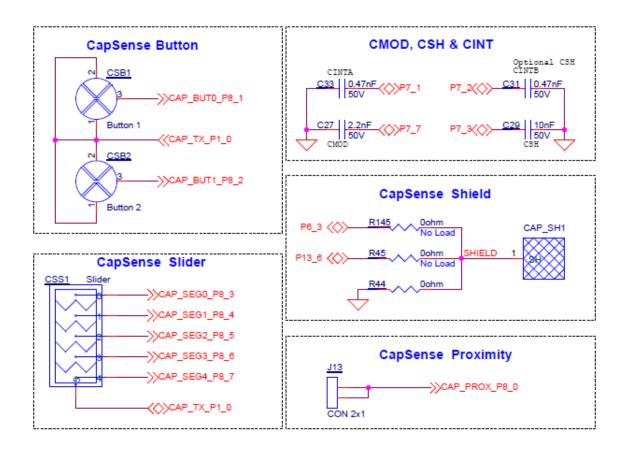

|    |          | A.2.7 CapSense Circuit                                            | 65 |

|    |          | A.2.8 LEDs                                                        | 65 |

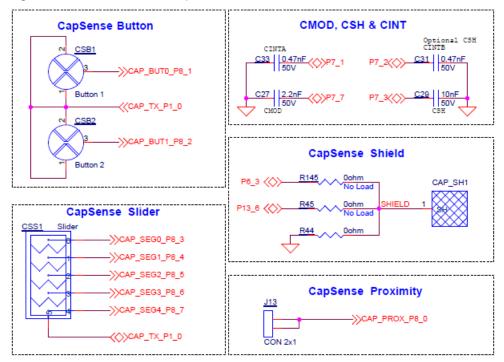

|    |          | A.2.9 Push Buttons                                                | 66 |

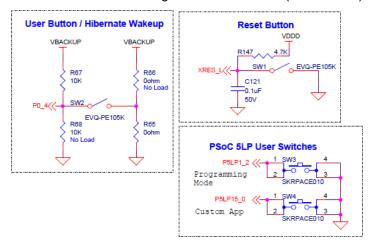

|    |          | A.2.10 Cypress NOR Flash                                          | 66 |

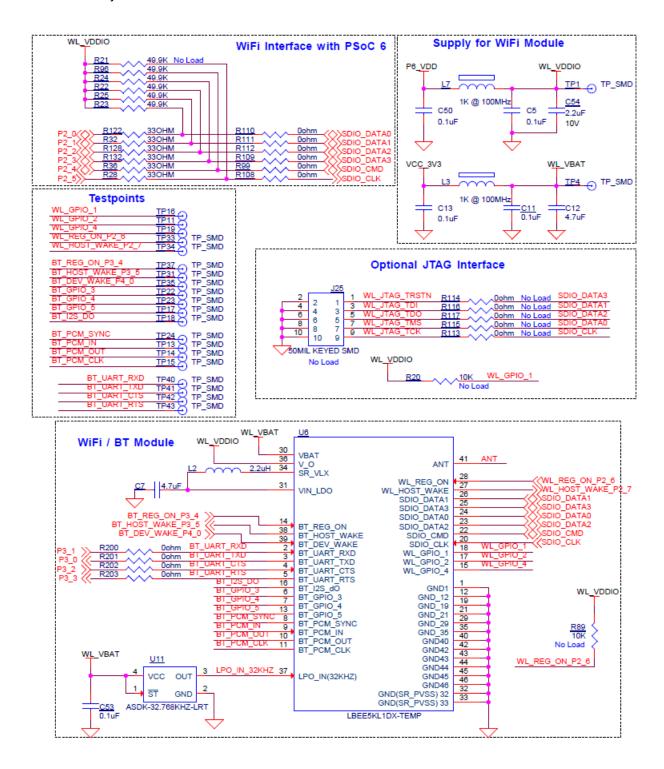

|    |          | A.2.11 WiFi and Bluetooth Module                                  |    |

|    |          | A.2.12 USB Host and USB Device Connections                        | 68 |

|    | A.3      | PSoC 6 WiFi-BT Pioneer Board Reworks                              | 69 |

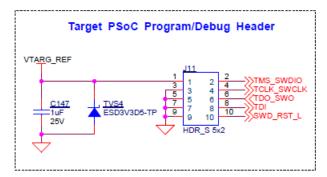

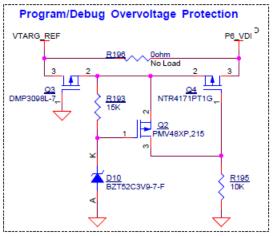

|    |          | A.3.1 Bypass Protection Circuit on Program and Debug Header (J11) | 69 |

|    |          | A.3.2 PSoC 6 MCU User Button (SW2)                                | 70 |

|    |          | A.3.3 SWD Connector Receptacle (J29)                              | 70 |

|    |          | A.3.4 CapSense Shield                                             | 71 |

|    |          | A.3.5 CSH                                                         | 71 |

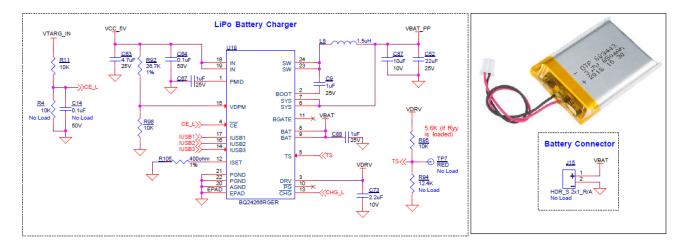

|    |          | A.3.6 LiPo Battery Charger                                        | 73 |

|    |          | A.3.7 Multiplexed GPIOs                                           | 73 |

|    | A.4      | Bill of Materials                                                 | 73 |

|    | A.5      | WICED Configuration                                               | 74 |

|    | A.6      | Frequently Asked Questions                                        | 80 |

| Re | vision H | istory                                                            | 85 |

## Safety Information

## **Regulatory Compliance**

The CY8CKIT-062-WiFi-BT PSoC 6 WiFi-BT Pioneer Kit is intended for use as a development platform for hardware or software in a laboratory environment. The board is an open-system design, which does not include a shielded enclosure. This may cause interference to other electrical or electronic devices in close proximity. In a domestic environment, this product may cause radio interference. In such cases, you may be required to take adequate preventive measures. In addition, this board should not be used near any medical equipment or RF devices.

Attaching additional wiring to this product or modifying the product operation from the factory default may affect its performance and cause interference with other apparatus in the immediate vicinity. If such interference is detected, suitable mitigating measures should be taken.

The PSoC 6 WiFi-BT Pioneer Kit contains electrostatic discharge (ESD) sensitive devices. Electrostatic charges readily accumulate on the human body and any equipment, and can discharge without detection. Permanent damage may occur on devices subjected to high-energy discharges. Proper ESD precautions are recommended to avoid performance degradation or loss of functionality. Store unused PSoC 6 WiFi-BT Pioneer Kits in the protective shipping package.

#### End-of-Life/Product Recycling

The end-of life for this kit is five years from the date of manufacture mentioned as a bar code on the back of the kit box. Contact your nearest recycler for information on discarding the kit.

## **General Safety Instructions**

#### **ESD Protection**

ESD can damage boards and associated components. Cypress recommends that you perform procedures only at an ESD workstation. If an ESD workstation is unavailable, use appropriate ESD protection by wearing an anti-static wrist strap attached to a grounded metal object.

## **Handling Boards**

The PSoC 6 WiFi-BT Pioneer Kit is sensitive to ESD. Hold the board only by its edges. After removing the board from its box, place it on a grounded, static-free surface. Use a conductive foam pad, if available. Do not slide the board over any surface.

## 1. Introduction

Thank you for your interest in the CY8CKIT-062-WiFi-BT PSoC 6 WiFi-BT Pioneer Kit. The PSoC 6 WiFi-BT Pioneer Kit enables you to evaluate and develop your applications using the PSoC 6 MCU.

The PSoC 6 MCU is Cypress' latest, ultra-low-power PSoC specifically designed for wearables and loT products. It is a programmable embedded system-on-chip, integrating a 150-MHz Arm<sup>®</sup> Cortex<sup>®</sup>-M4 as the primary application processor, a 100-MHz CM0+ that supports low-power operations, up to 1 MB Flash and 288 KB SRAM, CapSense<sup>®</sup> touch-sensing, and programmable analog and digital peripherals that allow higher flexibility, in-field tuning of the design, and faster time-to-market.

The PSoC 6 WiFi-BT Pioneer board offers compatibility with Arduino™ shields. The board features a PSoC 6 MCU, a 512-Mb NOR flash, an onboard programmer/debugger (KitProg2), a 2.4-GHz WLAN and Bluetooth functionality module (CYW4343W), a USB Type-C power delivery system (EZ-PD™ CCG3), a five-segment CapSense slider, two CapSense buttons, one CapSense proximity sensing header, an RGB LED, two user LEDs, USB host and device features, and one push button. The board supports operating voltages from 1.8 V to 3.3 V for the PSoC 6 MCU.

The CY8CKIT-062-WiFi-BT package includes a CY8CKIT-028-TFT Display Shield that contains a 2.4-inch TFT display, a motion sensor, ambient light sensor, a 32-bit audio codec, and a PDM microphone.

This is the first kit that enables development of PSoC 6 MCU + WiFi applications. To develop a PSoC 6 MCU + WiFi application, WICED™ Studio 6.1 or later must be used. WICED Studio is Cypress' integrated development environment (IDE) for developing WiFi applications. If you are not adding WiFi to your design then you can develop and debug PSoC 6 MCU project using PSoC Creator™. PSoC Creator supports exporting your designs to other third-party firmware development tools.

## 1.1 Kit Contents

The CY8CKIT-062-WiFi-BT package has the following contents, as shown in Figure 1-1.

- PSoC 6 WiFi-BT Pioneer Board

- CY8CKIT-028-TFT Display Shield

- USB Type-A to Type-C cable

- Four jumper wires (4 inches each)

- Two proximity sensor wires (5 inches each)

- Quick Start Guide

Figure 1-1. Kit Contents

Inspect the contents of the kit; if you find any part missing, contact your nearest Cypress sales office for help: www.cypress.com/support.

### 1.2 Hardware Introduction

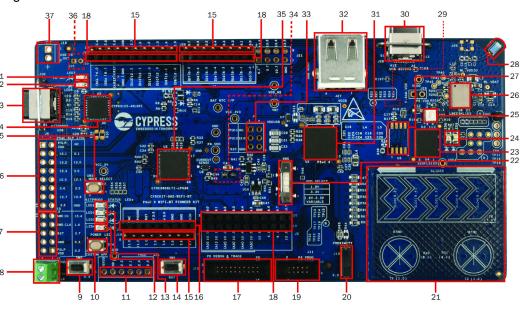

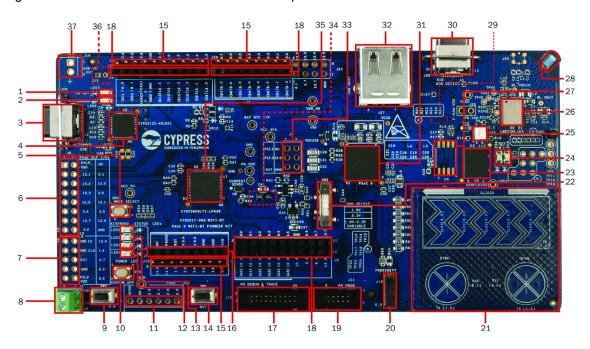

#### 1.2.1 CY8CKIT-062-WiFi-BT Board Details

Figure 1-2 shows the Pioneer board, which has the following features:

- PSoC 6 MCU

- Expansion headers that are compatible with Arduino Uno 3.3-V shields<sup>1</sup> and Digilent<sup>®</sup> Pmod<sup>™</sup> modules

- Type 1DX ultra-small 2.4-GHz WLAN and Bluetooth functionality module

- 512-Mbit external quad-SPI NOR flash that provides a fast, expandable memory for data and code

- KitProg2 onboard programmer/debugger with mass storage programming, USB to UART/I2C/ SPI bridge functionality, and custom applications support

- EZ-PD CCG3 USB Type-C power delivery (PD) system with rechargeable lithium-ion polymer (Li-Po) battery support<sup>2</sup>

- CapSense touch-sensing slider (five elements) and two buttons, all of which are capable of both self-capacitance (CSD) and mutual-capacitance (CSX) operation, and a CSD proximity sensor that allows you to evaluate Cypress' fourth-generation CapSense technology

- 1.8-V to 3.3-V operation of PSoC 6 MCU is supported. An additional 330-mF super-capacitor is provided for backup domain supply (VBACKUP)

- Two user LEDs, an RGB LED, a user button, and a reset button for PSoC 6 MCU.

- Two buttons and three LEDs for KitProg2.

<sup>1. 5-</sup>V shields are not supported

<sup>2.</sup> Battery and power-delivery capable USB Type-C to Type-C cable are not included in the kit package and should be purchased separately.

Figure 1-2. Pioneer Board

- 1. USB PD output voltage availability indicator (LED7)

- 1. USB PD output voltage availability indicator (LED7)

- 2. Battery charging indicator (LED6)

- 3. KitProg2 USB Type-C connector (J10)

- 4. Cypress EZ-PD™ CCG3 Type-C Port Controller with PD (CYPD3125-40LQXI, U3)

- 5. KitProg2 programming mode selection button (SW3)

- 6. KitProg2 I/O header (J6)1

- 7. KitProg2 programming/custom application header (J7)1

- 8. External power supply connector (J9)

- 9. PSoC 6 user button (SW2)

- 10. KitProg2 application selection button (SW4)

- 11. Digilent<sup>®</sup> Pmod™ compatible I/O header (J14)1

- 12. Power LED (LED4)

- 13. KitProg2 status LEDs (LED1, LED2, and LED3)

- 14. PSoC 6 reset button (SW1)

- 15. PSoC 6 I/O header (J18, J19 and J20)

- 16. Arduino™ Uno R3 compatible power header (J1)

- 17. PSoC 6 debug and trace header (J12)

- 18. Arduino Uno R3 compatible PSoC 6 I/O header (J2, J3 and J4)

- 19. PSoC 6 program and debug header (J11)

- 20. CapSense proximity header (J13)

- 00 00 00 00 00 000

21. CapSense slider and buttons

- 22. PSoC 6 VDD selection switch (SW5)

- 23. Cypress 512-Mbit serial NOR Flash memory (S25-FL512S, U4)

- 24. PSoC 6 user LEDs (LED8 and LED9)

- 25. RGB LED (LED5)

- 26. WiFi/BT module (LBEE5KL 1DX, U6)

- 27. Cypress serial Ferroelectric RAM (U5)1

- 28. WiFi-BT Antenna

- 29. VBACKUP and PMIC control selection switch (SW7)2

- 30. PSoC 6 USB device Type-C connector (J28)

- 31. Cypress PSoC 6 (CY8C6247BZI-D54, U1)

- 32. PSoC 6 USB Host Type-A connector (J27)

- 33. Arduino Uno R3 compatible ICSP header (J5)1

- 34. PSoC 6 power monitoring jumper (J8)2

- 35. KitProg2 (PSoC 5LP) programmer and debugger (CY8C5868LTI-LP039, U2)

- 36. Battery connector (J15)1,2

- 37. USB PD output voltage (9V/12V) connector (J16)1

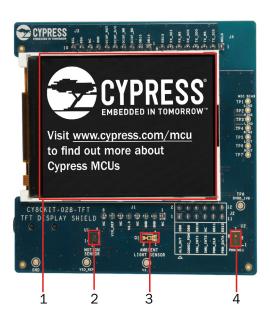

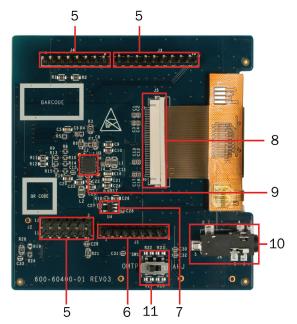

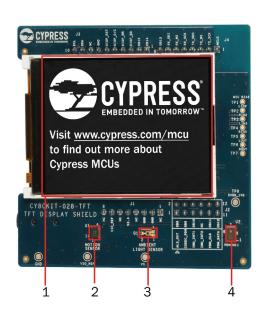

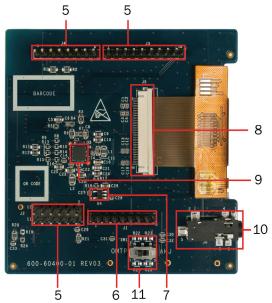

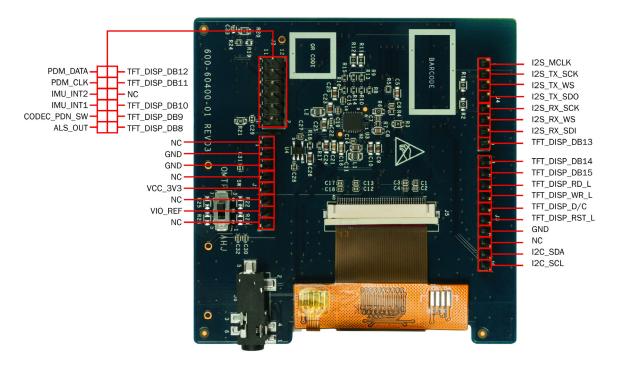

#### 1.2.2 CY8CKIT-028-TFT Board Details

Figure 1-3 shows the TFT display shield that has the following features:

- A 2.4-inch Thin-Film Transistor (TFT) LCD module with 240x320 pixel resolution.

- A three-axis acceleration and three-axis gyroscopic motion sensor.

- A PDM microphone for voice input.

- A 32-bit stereo codec with microphone, headphone, and speaker amplifier capability.

- An audio jack with a provision of connecting both AHJ and OMTP headphones. The headset standard can be set by an onboard switch.

- An ambient light sensor IC made of an NPN phototransistor.

- An LDO that converts 3.3 V to 1.8 V for the digital supply of the audio codec.

Figure 1-3. TFT Display Shield

- 1. 2.4-inch TFT display

- 2. Motion Sensor (U1)

- 3. Ambient Light Sensor (Q1)

- 4. PDM microphone (U2)

- 5. Ardunio compatible I/O headers (J2, J3, J4)

- 6. Ardunio compatible power header (J1)

- 7. TFT display power control load switch (U4)

- 8. TFT display connector (J5)

- 9. Audio CODEC (U3)

- 10. Audio Jack (J6)

- 11. Audio Jack Selection (OMTP/AHJ) Switch (SW1)

### 1.3 Software Introduction

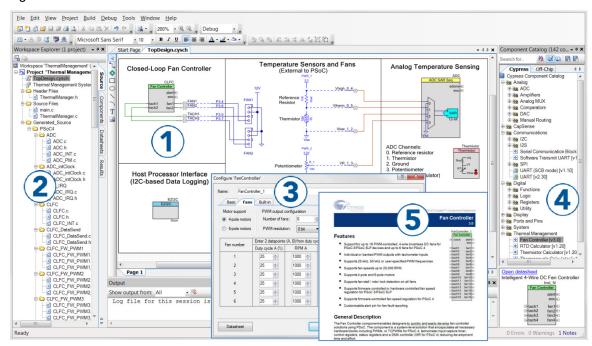

#### 1.3.1 PSoC Creator Overview

PSoC Creator is a state-of-the-art, easy-to-use IDE. It uses revolutionary hardware and software codesign, powered by a library of fully verified and characterized PSoC Components<sup>™</sup> and peripheral driver libraries (PDL), as shown in Figure 1-4. With PSoC Creator, you can:

- 1. Drag and drop Components to build your hardware system design in the main design workspace.

- 2. Co-design your application firmware with the PSoC hardware.

- 3. Configure Components using configuration tools or PDL.

- 4. Explore the library of 100+ Components.

- 5. Access Component datasheets.

- 6. Export your design to third-party firmware development tools.

Figure 1-4. PSoC Creator Features

PSoC Creator also enables you to tap into an entire tool ecosystem with integrated compiler chains and production programmers for PSoC devices. Use PSoC Creator for all PSoC 6 MCU designs that do not require WiFi connectivity. If WiFi connectivity is required, use WICED Studio 6.1 or higher.

### 1.3.1.1 PSoC Creator Code Examples

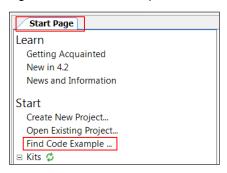

PSoC Creator includes a large number of code examples. These examples are accessible from the PSoC Creator Start Page, as shown in Figure 1-5 or from the menu **File > Code Example**.

Code examples can speed up your design process by starting you off with a complete design. The code examples also show how to use PSoC Creator Components for various applications. Code examples and documentation are included.

In the **Find Code Example** dialog, you have several options:

- Filter for examples based on device family or keyword.

- Select from the list of examples offered based on the Filter Options.

- View the project documentation for the selection (on the **Documentation** tab).

- View the code for the selection on the **Sample Code** tab. You can also copy and paste code from this window to your project, which can help speed up code development.

- Create a new workspace for the code example or add to your existing workspace. This can speed up your design process by starting you off with a complete, basic design. You can then adapt that design to your application.

Figure 1-5. Code Examples in PSoC Creator

#### 1.3.1.2 Kit Code Examples

You can access the installed kit code examples from the PSoC Creator Start Page. To access these examples, expand the Kits under the section Examples and Kits; then, expand the specific kit to see the code examples. To work with the code examples using this kit, see PSoC Creator chapter on page 18.

#### 1.3.1.3 PSoC Creator Help

Launch PSoC Creator and navigate to the following items:

- Quick Start Guide: Choose Help > Documentation > Quick Start Guide. This guide gives you the basics for developing PSoC Creator projects.

- Simple Component Code Examples: Choose File > Code Example. These examples demonstrate how to configure and use PSoC Creator Components. To access examples related to a specific Component, right-click the Component in the schematic or in the Component Catalog. Select the Find Code Example option in the context menu that appears.

- System Reference Guide: Choose Help > System Reference Guide. This guide lists and describes the system functions provided by PSoC Creator.

- Component Datasheets: Right-click a Component and select Open Datasheet.

### 1.3.2 WICED Studio Development System Overview

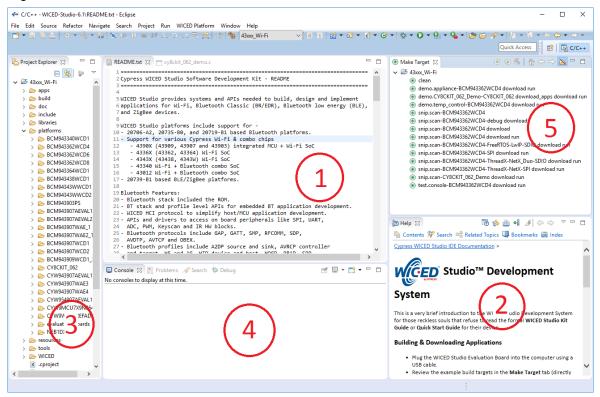

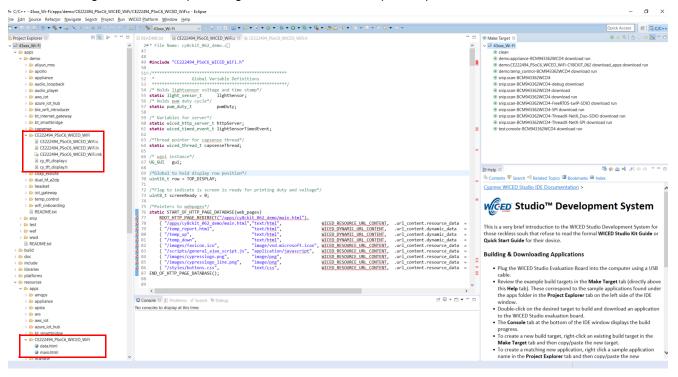

WICED Studio 6.1 (or later) supports WiFi and Bluetooth application development using the CY8CKIT-062-WiFi-BT kit. Tabs and their location in the WICED IDE are as shown in Figure 1-6.

Figure 1-6 illustrates the following:

- 1. Edit your application firmware.

- 2. Help Window that contains instructions on building and downloading applications.

- 3. Explore existing applications/firmware and library of the Software Development Kit (SDK).

- 4. View Build messages in the Console window.

- 5. Create and edit Make Targets for the platform to build your application/project.

Figure 1-6. WICED IDE

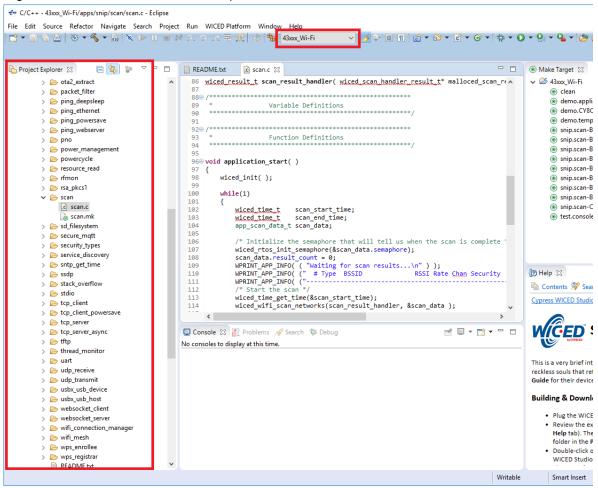

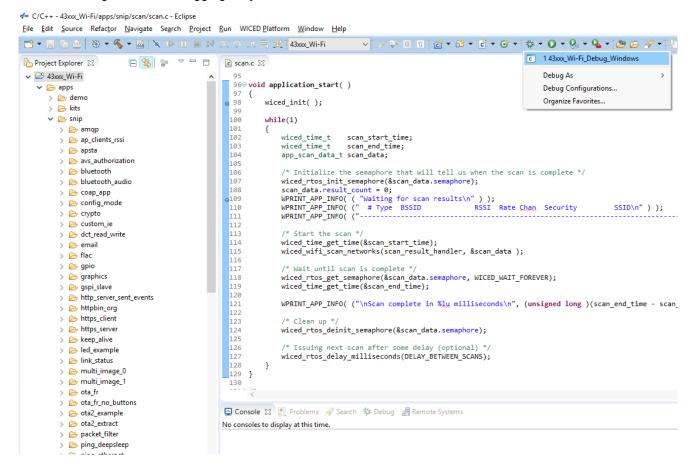

### 1.3.2.1 WICED Studio Code Examples

WICED Studio includes libraries and code examples supporting both Bluetooth and WiFi platforms. Selecting the 43xxx\_Wi-fi Filter will show only WiFi platform related files in the project explorer as shown in Figure 1-7.

Application examples can speed up the design process by serving as templates for development. Code examples are located under the *apps* category (in the Project Explorer window), as shown in Figure 1-8. Code examples under *apps* are further grouped into *demo*, *snip*, *test*, *waf* (WICED application framework), and *wwd* (WICED WiFi Driver Application) directories.

The *demo* directory contains applications that combine various WICED features into a single application. The *snip* directory contains application snippets that demonstrate how to use various WICED libraries and API functions. The <code>test</code> directory contains applications that are used for simple test and utility. The *waf* directory contains applications that are part of WICED application framework, for instance, the bootloader. The *wwd* directory contains applications that are developed using the low level <code>wwd</code> API calls and do not rely on higher level WICED APIs. Located within each subdirectory in the *apps* folder is a *README.txt* that lists and summarizes the applications located within the folder. Note that not all applications are supported in all platforms. The *snip* directory contains a *README.txt* with a matrix on what applications are supported in what platforms. For more details on the WICED software stack and APIs, review the application notes and documents available in the doc folder <*WICED SDK installation folder*>/WICED-Studio-6.1/43xxx\_Wi-Fi/doc. WICED-QSG.pdf, available in the same path, is a good document to start with.

Figure 1-7. Filter for WiFi Code Example in WICED Studio

Figure 1-8. Code Examples under apps Category

```

€ C/C++ - 43xxx_Wi-Fi/apps/snip/scan/scan.c - Eclipse

File Edit Source Refactor Navigate Search Project Run WICED Platform Window Help

Project Explorer ⋈ 🕒 🥞 🦻 🔻 🗖 🗎 README.txt

€ scan.c 🛭

86 wiced_result_t_scan_result_handler( wiced_scan_handler_result_t* malloced_scan A

apps

demo

Variable Definitions

> 🌦 snip

90

> 🗁 test

> 🗁 waf

929 /

94

README.txt

96⊖ void application_start( )

> 🇁 doc

> 🌦 include

98

wiced init():

99

> 🍃 libraries

while(1)

> 🗁 platforms

101

> 🗁 resources

wiced_time_t scan_start_time;

> 🎘 tools

wiced_time_t scan_end_t:

app_scan_data_t scan_data;

103

scan end time:

> 🍃 WICED

105

x .cproject

/* Initialize the semaphore that will tell us when the scan is complet

106

gdbinit .

107

wiced_rtos_init_semaphore(&scan_data.semaphore);

WPRINT_APP_INFO((" # Type BSSID RSSI Rate Chan Securit

WPRINT_APP_INFO((" # Type BSSID RSSI Rate Chan Securit

gdbinit_attach

<

108

x .project

(2) H

API_updates.txt

110

CHANGELOG.txt

ħ

generated_mac_address.txt

wiced_time_get_time(&scan_start_time);

Cyr

LICENSE.txt

wiced_wifi_scan_networks(scan_result_handler, &scan_data );

114

make

```

## 1.4 Getting Started

This guide will help you to get acquainted with the PSoC 6 WiFi-BT Pioneer Kit:

- The PSoC Creator chapter on page 18 describes the installation of the kit software. The kit software includes the PSoC Creator IDE and PDL to develop and debug the applications, the PSoC Programmer to program the .hex files on to the device.

- The WICED chapter on page 24 describes the installation of WICED and getting started guidelines of the WICED-based example project of the kit.

- The Kit Hardware chapter on page 38 describes the CY8CKIT-062-WiFi-BT base board and CY8CKIT-028-TFT shield hardware features and functionalities.

- The Appendix on page 58 provides a detailed hardware description, methods to use the onboard components, kit schematics, the bill of materials (BOM), and an FAQ.

## 1.5 Additional Learning Resources

Cypress provides a wealth of data at www.cypress.com/psoc6 to help you to select the right PSoC device for your design and to help you to quickly and effectively integrate the device into your design.

## 1.6 Technical Support

For assistance, visit Cypress Support or contact customer support at +1(800) 541-4736 Ext. 3 (in the USA) or +1 (408) 943-2600 Ext. 3 (International).

You can also use the following support resources if you need quick assistance:

- Self-help (Technical Documents)

- Local Sales Office Locations

## 1.7 **Documentation Conventions**

Table 1-1. Document Conventions for Guides

| Convention         | Usage                                                                                                                                               |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Courier New        | Displays user entered text and source code:                                                                                                         |

| Italics            | Displays file locations, file names, and reference documentation: Read about the <i>sourcefile.hex</i> file in the <i>PSoC Creator User Guide</i> . |

| [Bracketed, Bold]  | Displays keyboard commands in procedures: [Enter] or [Ctrl] [C]                                                                                     |

| File > Open        | Represents menu paths: File > Open > New Project                                                                                                    |

| Bold               | Displays commands, menu paths, and icon names in procedures:<br>Click the <b>File</b> icon and then click <b>Open</b> .                             |

| Times New Roman    | Displays an equation: $2+2=4$                                                                                                                       |

| Text in gray boxes | Describes cautions or unique functionality of the product.                                                                                          |

## 1.8 Acronyms

Table 1-2. Acronyms Used in this Document

| Acronym          | Definition                          |

|------------------|-------------------------------------|

| ADC              | analog-to-digital converter         |

| ВОМ              | bill of materials                   |

| ВТ               | Bluetooth                           |

| CINT             | integration capacitor               |

| CMOD             | modulator capacitor                 |

| CPU              | central processing unit             |

| CSD              | CapSense sigma delta                |

| CTANK            | shield tank capacitor               |

| DC               | direct current                      |

| Del-Sig          | delta-sigma                         |

| ECO              | external crystal oscillator         |

| ESD              | electrostatic discharge             |

| F-RAM            | Ferroelectric Random Access Memory  |

| FPC              | flexible printed circuit            |

| GPIO             | general-purpose input/output        |

| HID              | human interface device              |

| I <sup>2</sup> C | Inter-Integrated Circuit            |

| IC               | integrated circuit                  |

| ICSP             | in-circuit serial programming       |

| IDAC             | current digital-to-analog converter |

| IDE              | integrated development environment  |

| LED              | light-emitting diode                |

Table 1-2. Acronyms Used in this Document (continued)

| Acronym | Definition                                  |

|---------|---------------------------------------------|

| PC      | personal computer                           |

| PCM     | pulse code modulation                       |

| PD      | power delivery                              |

| PDM     | pulse density modulation                    |

| PTC     | positive temperature coefficient            |

| PSoC    | Programmable System-on-Chip                 |

| PWM     | pulse width modulation                      |

| RGB     | red green blue                              |

| SAR     | successive approximation register           |

| SMIF    | serial memory interfac                      |

| SPI     | serial peripheral interface                 |

| SRAM    | serial random access memory                 |

| SWD     | serial wire debug                           |

| TFT     | thin-film transistor                        |

| UART    | universal asynchronous receiver transmitter |

| USB     | Universal Serial Bus                        |

| WCO     | watch crystal oscillator                    |

## 2. PSoC Creator

This chapter describes the steps to install PSoC Creator and the packages required to use the PSoC 6 WiFi-BT Pioneer Kit, for non WiFi applications. This includes the IDE on which the projects will be built and used for programming. For developing WiFi applications, WICED Studio 6.1 or later must be used (see the WICED chapter on page 24).

## 2.1 Before You Begin

To install Cypress software, you will require administrator privileges. However, they are not required to run the software that is already installed. Before you install the kit software, close any other Cypress software that is currently running.

### 2.2 Install Kit Software

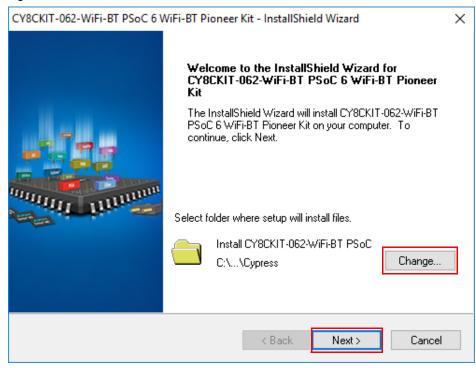

Follow these steps to install the PSoC 6 WiFi-BT Pioneer Kit software:

- Download and run the CY8CKIT-062-WiFi-BT PSoC 6 WiFi-BT Pioneer Kit software from www.cypress.com/CY8CKIT-062-WiFi-BT. The kit software is available in two different formats for download.

- a. CY8CKIT-062-WiFi-BT Kit Complete Setup: This installation package contains the files related to the kit including PSoC Creator, PSoC Programmer, and PDL. However, it does not include the Windows Installer or Microsoft .NET framework packages. If these packages are not on your computer, the installer will direct you to download and install them from the Internet.

- b. **CY8CKIT-062-WiFi-BT Kit Only**: This executable file installs only the kit contents, which include kit code examples, hardware files, and user documents. This package can be used if all the software prerequisites (listed in step 3) are installed on your PC.

- 2. Select the folder in which you want to install the PSoC 6 WiFi-BT Pioneer Kit-related files. Choose the directory and click **Next**.

Figure 2-1. Kit Installer Screen

- 3. When you click **Next**, the installer automatically installs the required software, if it is not present on your computer. Following are the required software:

- a. PSoC Creator 4.2: This software is available for download separately at www.cypress.com/psoccreator. PSoC Creator 4.2 installer automatically installs the following additional software:

PSoC Programmer 3.27.0

Peripheral Driver Library 2.1.0

Peripheral Driver Library 3.0.1

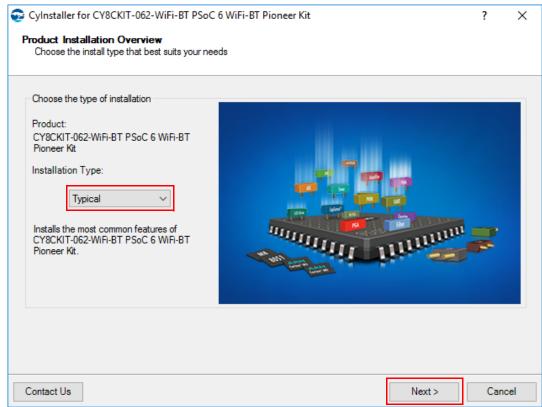

4. Choose the **Typical**, **Custom**, or **Complete** installation type (select **Typical** if you do not know which one to select) in the Product Installation Overview window, as shown in Figure 2-2. Click **Next** after selecting the installation type.

Figure 2-2. Product Installation Overview

- 5. Read the License agreement and select **I accept the terms in the license agreement** to continue with installation. Click **Next**.

- 6. When the installation begins, a list of packages appears on the installation page. A green check mark appears next to each package after successful installation.

- Enter your contact information or select the check box Continue Without Contact Information.

Click Finish to complete the CY8CKIT-062-WiFi-BT PSoC 6 WiFi-BT Pioneer Kit software installation.

- 8. After the installation is complete, the kit contents are available at the following location: <Install\_Directory>\CY8CKIT-062-WiFi-BT PSoC 6 WiFi-BT Pioneer Kit

Default location:

Windows 7 (64-bit): C:\Program Files (x86)\Cypress\CY8CKIT-062-WiFi-BT PSoC 6 WiFi-BT Pioneer Kit

Windows 7 (32-bit): C:\Program Files\Cypress\CY8CKIT-062-WiFi-BT PSoC 6 WiFi-BT Pioneer Kit

**Note:** For Windows 7/8/8.1/10 users, the installed files and the folder are read-only. To use the installed code examples, create an editable copy of the example in a path that you choose, so that the original installed example is not modified. These steps will create an editable copy of the example in a path that you choose, so the original installed example is not modified.

## 2.3 Programming and Debugging using PSoC Creator

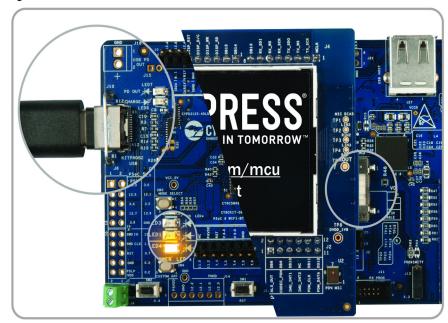

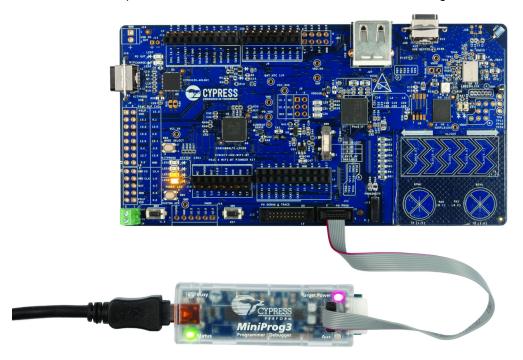

1. Connect the PSoC 6 WiFi-BT Pioneer Kit to the PC using the USB cable, as shown in Figure 2-3. The kit enumerates as a composite device if you are connecting it to your PC for the first time. See section 4.3.3 Kit Enumeration and Programming Modes of KitProg2 to know whether the kit is successfully enumerated or not.

Figure 2-3. Connect USB Cable to USB Connector on the Kit

- 2. Open the desired project in PSoC Creator. To do this, go to **File > Open > Project/Workspace**. This provides the option to browse and open your saved project.

- 3. Select the option **Build > Build Project** or pressing [Shift] [F6] to build the project.

- 4. If there are no errors during build, select **Debug > Program** or press **[Ctrl] [F5]**. This programs the device on the PSoC 6 WiFi-BT Pioneer Kit.

PSoC Creator has an integrated debugger. You can start the debugger by selecting **Debug** > **Debug** or by pressing **[F5]**. For more details, see the "Debugging Using PSoC Creator" section in the Kit-Prog2 User Guide.

## 2.4 Kit Code Examples

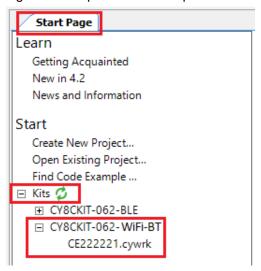

The PSoC 6 WiFi-BT Pioneer Kit includes two code examples. One of these two code examples is developed in PSoC Creator. To access this code example, first download and install the PSoC 6 WiFi-BT Pioneer Kit setup file from <a href="https://www.cypress.com/CY8CKIT-062-WiFi-BT">www.cypress.com/CY8CKIT-062-WiFi-BT</a>. After the kit package is installed on your PC, the PSoC Creator-based code examples will be available from <a href="https://www.cypress.com/CY8CKIT-062-WiFi-BT">Start</a> > Kits on the PSoC Creator Start Page. This code example can be accessed in the following directory: <a href="https://www.cypress.com/CY8CKIT-062-WiFi-BT">LINSTALL Directory</a> \CY8CKIT-062-WiFi-BT PSoC 6 WiFi-BT Pioneer Kit\</a> <a href="https://www.cypress.com/CY8CKIT-062-WiFi-BT">WiFi-BT PSoC 6 WiFi-BT PSoC 6 Wi

#### 2.4.1 Using the Kit Code Examples Built in PSoC Creator

Follow these steps to open and use the code examples:

Launch PSoC Creator from Start > All Programs > Cypress > PSoC Creator <version> >

PSoC Creator <version>.

- 2. On the Start Page, click **CY8CKIT-062-WiFi-BT** under **Start** > **Kits**. A list of code examples appears, as shown in Figure 2-4.

- 3. Click the desired code example, select a location to save the project, and click **OK**.

Figure 2-4. Open Code Example from PSoC Creator

- 4. Build the code example by choosing **Build > Build <Project Name>**. After the build process is successful, a .hex file is generated.

- 5. Connect PSoC 6 WiFi-BT Pioneer Kit to the PC using the USB cable, as shown in Figure 2-3 on page 21, to program the kit with the code example.

- 6. Choose **Debug > Program** in PSoC Creator.

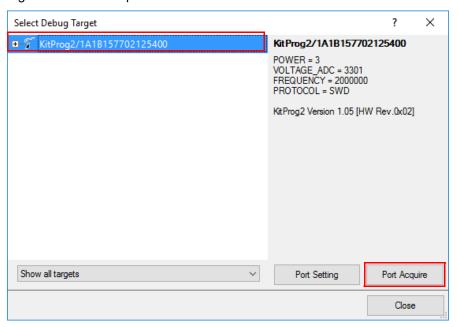

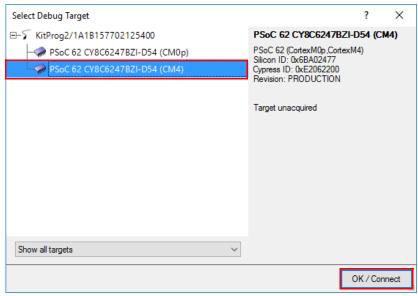

- 7. If the device is already acquired, programming will complete automatically the result will appear in the PSoC Creator status bar at the bottom left side of the screen. If the device is yet to be acquired, the Select Debug Target window will appear. Select KitProg2/<serial\_number> and click Port Acquire, as shown in Figure 2-5.

Figure 2-5. Port Acquire

8. After the device is acquired, it is shown in a tree structure below the KitProg2/<serial\_number>. Click Connect and then OK to exit the window and start programming, as shown in Figure 2-6. Note: PSoC 6 MCUs have both CM0+ and CM4 CPUs. To program, select one of them and click Connect. To debug, select the CPU that needs to be debugged.

Figure 2-6. Connect Device from PSoC Creator and Program

9. After programming is successful, the code example is ready to use.

Table 2-1 shows the code example, developed in PSoC Creator, which can be used with this kit.

Table 2-1. Code Example in PSoC Creator

| Project                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE222221_TFT_VoiceRecorder | This code example shows how PSoC 6 MCU can be used to record audio data, store it, and play it back. It uses a digital microphone with the PDM/PCM hardware block. All the audio data captured by the microphone is stored in an external flash memory. After the recording is completed, you can play the audio data over I2S, which interfaces with an audio codec. You can record/play/pause/resume with CapSense buttons. You control the audio volume with a CapSense slider. The TFT LCD displays the current state of the voice recorder, the volume, and the time of the record/play. |

## 3. WICED

#### 3.1 Introduction

This chapter describes the steps to install the WICED software tools and packages required to use the PSoC 6 WiFi-BT Pioneer Kit for developing WiFi applications. This chapter describes basic quick start guidelines of the WICED-based example project that can be used for further development purposes.

## 3.2 Before You Begin

To install Cypress software, you will require administrator privileges. However, they are not required to run the software that is already installed. Before you install the kit software, close any other Cypress software that is currently running.

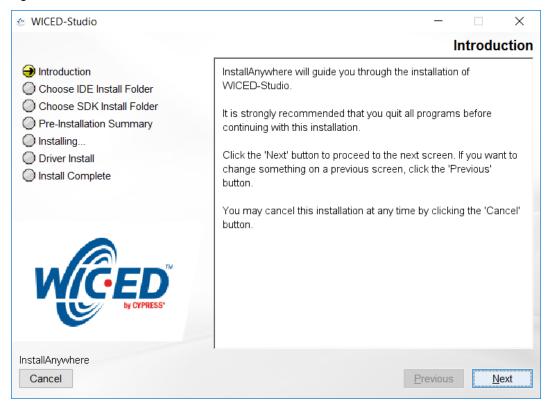

### 3.3 Install WICED

The CY8CKIT-062-WiFi-BT kit needs the WICED 6.1 (or later) software to be installed in your system. WICED 6.1 needs separate download and installation.

- Download and install WICED Studio 6.1 (or later) from www.cypress.com/products/wiced-software.

- 2. Select two folders, one for the IDE and the other for the SDK. The SDK folder contains the Framework for developing WiFi applications.

- 3. The installer will ask to select between WiFi and Bluetooth platforms. Select **43xxx\_Wi-Fi** as the default.

Figure 3-1. Installer Window Screenshot

## 3.4 Programming and Debugging in WICED

## 3.4.1 Building and Programming a Project for CY8CKIT-062-WiFi-BT in WICED Studio IDE

To build and program a project for CY8CKIT-062-WiFi-BT, perform the following steps:

- To open the WICED IDE on the Windows PC, go to Start > All Programs > Cypress > WICED-Studio.

- 2. Select **43xxx\_Wi-Fi** in the WICED Target selector drop-down box as shown in Figure 1-7. Building a project requires a corresponding make target, located in the Make Target window. All applications go under the *apps* directory. The make target path will contain the directory hierarchy starting from *apps* with directory names separated by a period. The project name is followed by a hyphen and then the platform name. Finally, the actions to be performed after the build are specified, such as download and run. For example, to build, download, and run the application scan which exists in *apps\snip\scan*, create the following make target:

```

snip.scan-CY8CKIT 062 download apps download run

```

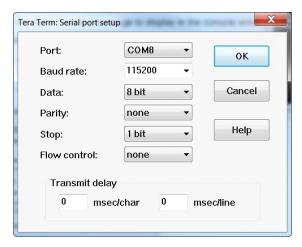

This project will periodically scan for Wi-Fi access points and will list them using the serial-to-USB connection on the kit.

Perform these steps to create the make target, build, program, and test application scan:

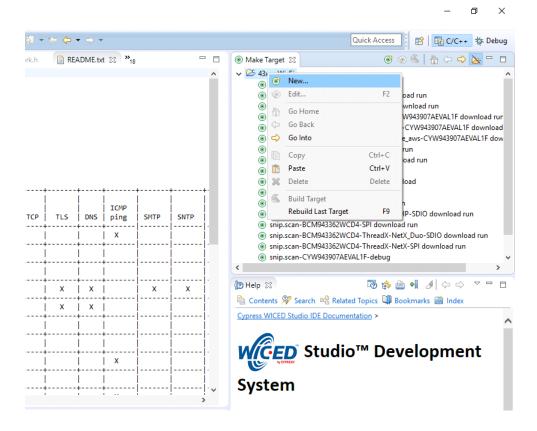

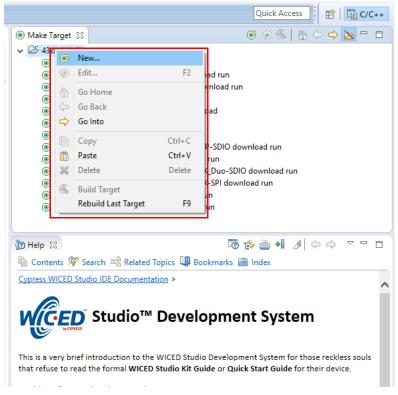

3. Right-click 43xxx Wi-Fi in the Make Target window as shown in Figure 3-2 and click New.

Figure 3-2. Creating New Make Target

4. Enter snip.scan-CY8CKIT\_062 download\_apps download run in the Target name field and click **OK**.

**Note:** The list of all commands that can be provided in the Make target is listed in *<WICED-SDK* installation directory>/ 43xxx\_Wi-Fi/Makefile.

snip.scan-CY8CKIT 062 download apps download run indicates the following:

- a. snip = Directory inside apps folder

- b. scan = Sub-directory and name of the application to be built. For example, to build the console application under test directory in apps, then use test.console instead of snip.scan.

- c. CY8CKIT 062 = Board/platform name

- d. download\_apps = Download application resources into QSPI Flash

- e. download = Indicates download to target

- f. run = Resets the target and starts execution

- 5. Double-click (alternately, right-click and select **Build Target**) the Clean Make Target to remove any output from the previous build. It is recommended to do Make clean when any new files are added or removed to the corresponding Target.

**Note:** Before executing the next step, ensure that you connect the CY8CKIT-062-WiFi-BT kit to the same PC through the Type-C USB cable connected to the J10 port. See 4.3.3 Kit Enumeration and Programming Modes of KitProg2 to ensure that the kit is successfully enumerated and **Port Selection** is set to CMSIS-DAP mode.

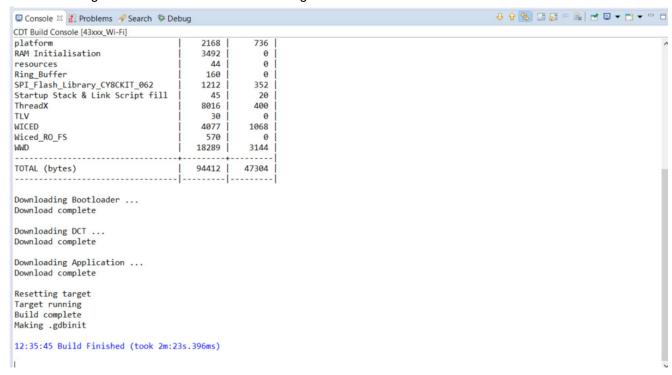

6. Double-click (alternatively right-click and select **Build Target**) the snip.scan-CY8CKIT\_062

download\_apps download run make target to build and download it to the CY8CKIT-062-WiFi-BT.

The project is built and programmed into the CY8CKIT-062-WiFi-BT, as shown in Figure 3-3.

Figure 3-3. Successful Build and Program

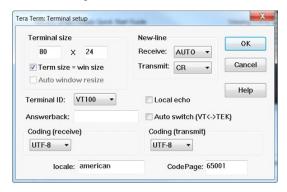

- 7. To view output messages with a terminal emulation program (such as Tera Term), follow these steps:

- a. Start the terminal emulation program.

- b. Go to Setup > Terminal, set the Terminal ID to VT100 and New-Line Receive to AUTO. Other settings should be left at the default settings.

c. Go to **Setup > Serial port**, initiate a connection with the Serial port number from the Device Manager on the PC.

Note: The exact Port number will vary with the corresponding PC port.

- d. Press the Reset button on the CY8CKIT-062-WiFi-BT to view the application start-up messages.

- 8. The output of the Terminal Emulation program should be similar to what is shown in Figure 3-4.

Figure 3-4. Console Output

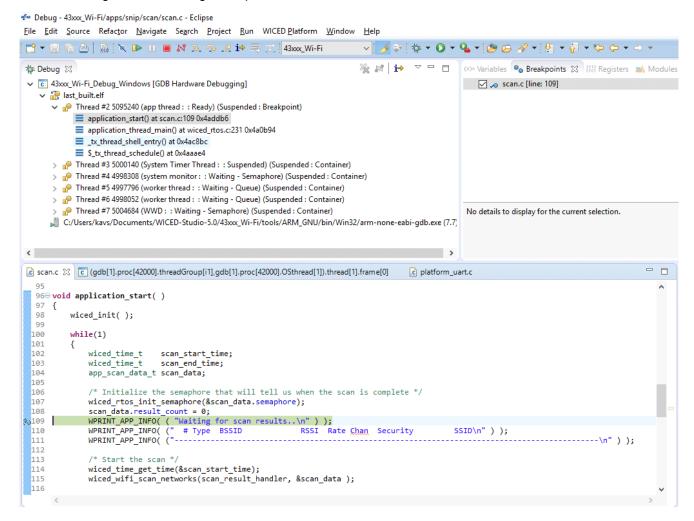

### 3.4.2 Debugging a Project using Breakpoints

After programming a project, it is possible to debug it in CY8CKIT-062-WiFi-BT using the built-in debugger.

Note that the scan example used in section 3.4.1 is also used here. The steps outlined in section 3.4.1 should be first followed with a slight change (adding -debug to the Make Target command and removing run). Instead of

snip.scan-CY8CKIT 062 download apps download run

The following make command should be used:

snip.scan-CY8CKIT 062-debug download apps download

If <code>-debug</code> is not added, then it will be built for release. The important difference between the debug and release configurations is optimization. Debug is built with no optimization and release is built with optimization. It is possible to debug without using <code>-debug</code> as well, but with many variables and lines optimized away, many breakpoints may not get hit.

Note that breakpoints must be placed after starting a debug session in WICED Studio 6.1 or later. If there are any breakpoints that were created prior to the start of debug session, their properties must be changed to be enabled for all threads.

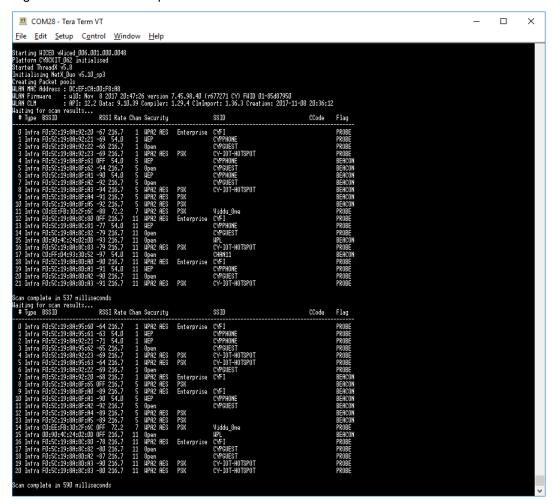

Perform these steps to debug the project:

- 1. Execute the make target described above to download the project to the device.

- 2. Click the arrow next to the **Debug** icon as shown in Figure 3-5 and select 43xxx-Wi-Fi\_Debug\_Windows. The Confirm Perspective Switch dialog appears; click **Yes**. The Debug session starts and halts in the *start\_GCC.s* file.

#### Notes:

- a. The Confirm Perspective Switch dialog is not displayed if you previously selected the **Remember my decision** check box in the Confirm Perspective Switch dialog.

- b. If any MakeFile/Build error occurs, then clean (using the Clean make target), re-build, and download to the CY8CKIT-062-WiFi-BT again.

- c. In the Debug Perspective, the Project explorer window goes away by default. To view the source files, switch back to the "C/C++" perspective.

- d. To switch between perspectives use the "C/C++" or "Debug" icon at the top right corner of screen.

Figure 3-5. Debugging Project

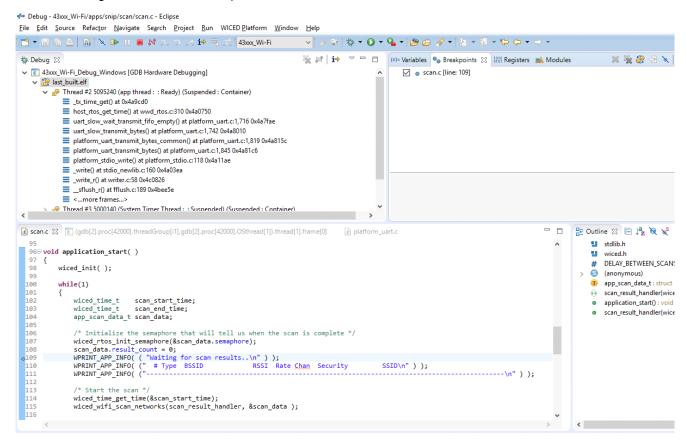

- 3. Open the scan.c file from the Project Explorer window. Click the line with WPRINT\_APP\_INFO(

("Waiting for scan results...\n")); and press the [Ctrl +Shift+B] keys on your keyboard. A blue hollow circle along with a check mark appears next to the line number, as shown in Figure 3-6.

- 4. From the main menu, click **Run** > **Resume**. Execution will stop at the breakpoint that you added. To continue after hitting the breakpoint, click **Resume** again.

- 5. To disable the breakpoint, press the **[Ctrl+Shift+B]** keys again on the same line, or deselect the corresponding check box in the Breakpoints window.

- **Note:** If the Breakpoint window does not appear, then choose **Window > Show View > Breakpoints**.

- To terminate the Debugging session, click Run > Terminate, or click on the red Square icon.

Once you terminate the session, click C/C++ in the upper right corner to return to the C/C++ perspective.

Figure 3-6. Placing Breakpoint in Code

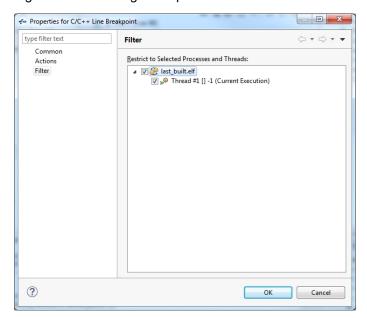

- 7. If Breakpoints are created prior to starting the current Debug session, they will not be associated with the current thread and will be indicated with a Blue circle without a check mark. To enable the Breakpoints in the current thread, associate the properties from the Breakpoints window with the current thread.

- **Note:** If you do not see any breakpoints in the Breakpoints window, click the **Show Breakpoints Supported by Selected Target** icon as shown in Figure 3-7. The breakpoints are displayed.

- 8. Right-click the desired breakpoint check box and click **Breakpoint Properties...**. Click the **last\_built.elf** check box, as shown in Figure 3-8. The check mark appears before the actual breakpoint indicating its association with the current execution.

Figure 3-7. Show Breakpoints Icon

Figure 3-8. Enabling Breakpoint for Current Execution

## 3.5 Kit Code Example

### 3.5.1 Building and Programming a Project in the WICED Studio IDE

Before starting with the kit code example, make sure you install the kit software and WICED 6.1 to your PC. The steps to install the kit installer is explained in Install Kit Software on page 18. The installation of WICED 6.1 is explained Install WICED on page 24. To build and program the WICED based project of the CY8CKIT-062-WiFi-BT kit, perform the following steps:

- To open the WICED IDE on Windows PC, go to Start > All Programs > Cypress > WICED-Studio.

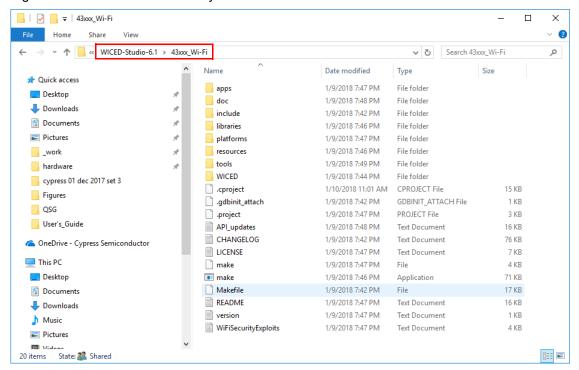

- 2. Locate the WICED WiFi-SDK directory in your PC. The default location is *C:\Users\<user name>\Documents\WICED-Studio-6.1\43xxx\_WiFi*, as shown in Figure 3-9. However, it may be in a different location depending on the path you choose when installing WICED Studio.

Figure 3-9. WICED SDK Directory

- 3. Also, locate the CY8CKIT-062-WiFi-BT Kit Code Example at the location < Install\_Directory>\CY8CKIT-062-WiFi-BT PSoC 6 WiFi-BT Pioneer Kit\<version>\Firmware\PSoC 6 MCU\CE222494\_PSoC6\_WICED\_WiFi\_Demo. This has two directories called apps and resources. Open the apps\demo folder and copy the CE222494\_PSoC6\_WICED\_WiFi folder into the WICED-Studio-6.1\43xxx\_Wi-Fi\apps\demo folder.

- 4. Open the resources\apps folder and copy the CE222494\_PSoC6\_WICED\_WiFi folder into WICED-Studio-6.1\43xxx Wi-Fi\resources\apps.

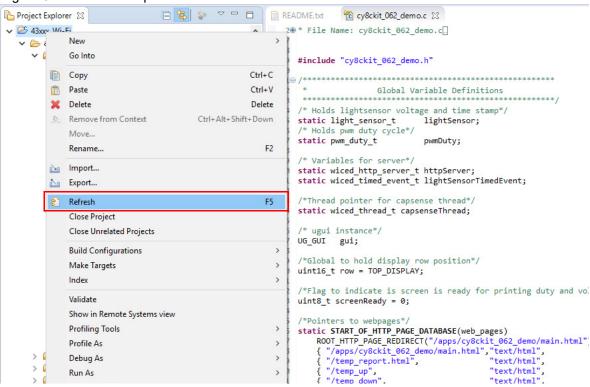

- If WICED Studio 6.1 (or later) is opened with 43xxx\_Wi-Fi as the WICED Filter, then the new folders appear as shown in Figure 3-10.

- If the projects are not visible in WICED Studio 6.1 (or later), then right-click the 43xxx\_Wi-Fi folder in Project Explorer and click **Refresh**, as shown in Figure 3-10.

Figure 3-10. Setup Package in WICED Studio 6.1 (or later)

Figure 3-11. Refresh Top Folder

5. In the Make Target window, right-click and select **New**, and give it the following Target Name: demo.CE222494\_PSoC6\_WICED\_WiFi-CY8CKIT\_062 download\_apps download run (see Figure 3-12).

Figure 3-12. Creating New Make Target

The Make Target window will show the following added target:

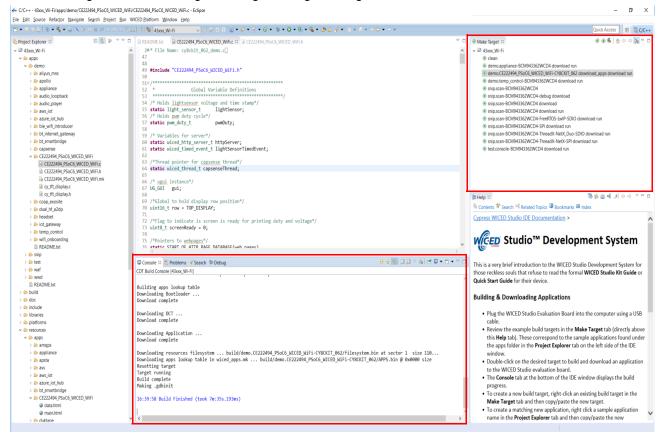

demo.CE222494\_PSoC6\_WICED\_WiFi-CY8CKIT\_062 download\_apps download run (see Figure 3-13).

**Note:** Before executing the next step, ensure that you connect the CY8CKIT-062-WiFi-BT kit to the same PC through the Type-C USB cable connected to the J10 port. See 4.3.3 Kit Enumeration and Programming Modes of KitProg2 to ensure that the kit is successfully enumerated and **Port Selection** is set to CMSIS-DAP mode.

6. Double-click the newly created make target to build the code, program the kit, and run the example. Note that this may take a few minutes.

The Console window will display a message "Build Finished" as shown in Figure 3-13.

Figure 3-13. Building and Programming the Target

To know more about this code example, refer to CE222494 WiFi BT WICED WiFi Demo.

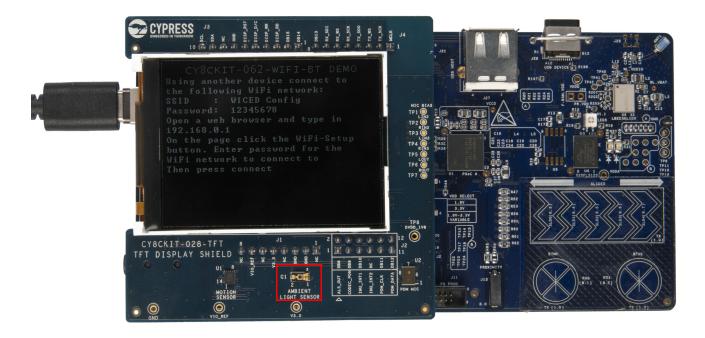

This kit is shipped with this code example preprogrammed to it. While power is on, and when you peel the sticker on the TFT display, you can see the instructions on the display as shown in Figure 3-14.

Figure 3-14. TFT Screen Instruction Display

Table 3-1 shows the code example, developed in WICED, which can be used with this kit. See the WICED 6.1 code example documents for additional details.

Table 3-1. Code Example in WICED

| Project                          | Description                                                                                                                                                                                                                                                                |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CE222494_WiFi_BT_WICED_WiFi_Demo | This code example demonstrates how to use PSoC 6 MCU and WICED to enable WiFi communication. It demonstrates how the PSoC 6 MCU with the 4343W module can be used as a configuration access point (AP) to allow a user to enter the credentials of their personal network. |  |

# 4. Kit Hardware

## 4.1 CY8CKIT-062-WiFi-BT Details

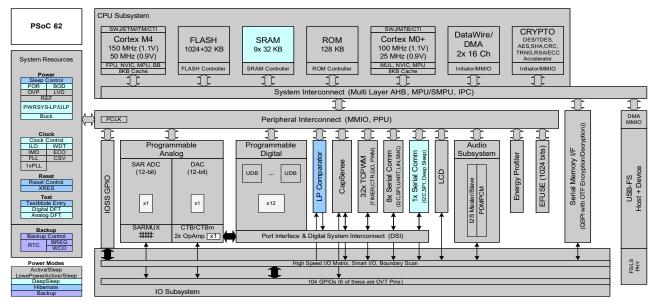

The PSoC 6 WiFi-BT Pioneer Kit is built around the PSoC 6 MCU; Figure 4-1 shows the block diagram of the device. For details of the PSoC 6 MCU features, see the device datasheet.

Figure 4-1. PSoC 6 MCU Block Diagram

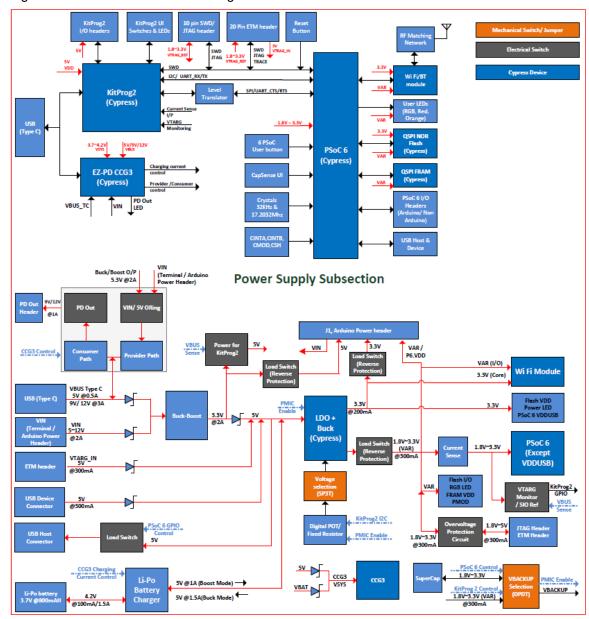

Figure 4-2 shows the block diagram of the Pioneer board.

Figure 4-2. Pioneer Board Block Diagram

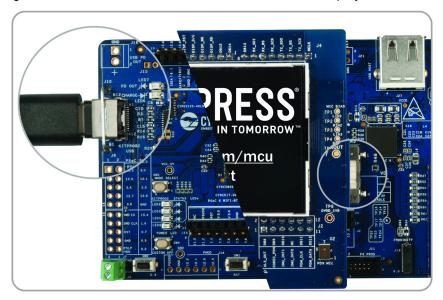

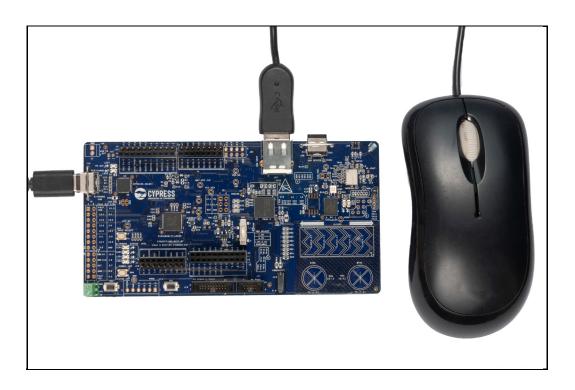

The CY8CKIT-062-WiFi-BT Pioneer Kit comes with the PSoC 6 WiFi-BT Pioneer board, which has the CY8CKIT-028-TFT display shield connected, as Figure 4-3 shows.

Figure 4-3. PSoC 6 WiFi-BT Pioneer Board and TFT Display Shield

Figure 4-4 shows the markup of the Pioneer board.

Figure 4-4. PSoC 6 WiFi-BT Pioneer Board - Top View

The PSoC 6 WiFi-BT Pioneer board has the following peripherals:

- 1. USB PD out indicator (LED7): This LED turns ON when the USB Type-C power delivery output is available for use.

- 2. Battery charging indicator (LED6): This LED turns ON when the onboard battery charger is charging a lithium-ion polymer battery connected to J15. Note that the battery connector and

- battery are not included in the kit and should be purchased separately if you want to test the battery charging functionality.

- 3. KitProg2 USB connector (J10): The USB cable provided along with the PSoC 6 WiFi-BT Pioneer Kit connects between this USB connector and the PC to use the KitProg2 onboard programmer and debugger and to provide power to the Pioneer board. J10 is also used for the USB Type-C power delivery system. See "EZ-PD CCG3 Type-C Power Delivery" on page 56 for more details.

- 4. Cypress EZ-PD CCG3 Type-C Port Controller with PD (CYPD3125-40LQXIT, U3): The Pioneer board includes an EZ-PD CCG3 USB Type-C port controller with power delivery system. This device is pre-programmed and can deliver power from a Type-C port to an onboard header J16, while simultaneously charging a lithium-ion polymer battery connected to J15. In addition, the power delivery system can deliver power to a Type-C power sink or consumer, such as a mobile phone, with the power derived from the VIN supply. See "EZ-PD CCG3 Type-C Power Delivery" on page 56 for more details.

- 5. KitProg2 programming button (SW3): This button can be used to switch between the KitProg2 operation modes (proprietary SWD programming/CMSIS-DAP mode). This button can also be used to provide input to the PSoC 5LP in custom application mode. For more details, see the KitProg2 User Guide.

- 6. KitProg2 I/O header (J6): This header brings out several GPIOs of the onboard KitProg2 PSoC 5LP device. This includes the USB-I2C, USB-UART, and USB-SPI bridge lines. The additional PSoC 5LP pins are direct connections to the internal programmable analog logic of the PSoC 5LP. You can also use these pins for custom applications. For more details on KitProg2, see the KitProg2 User Guide.

- 7. **KitProg2 programming/custom application header (J7):** This header brings out more GPIOs of the PSoC 5LP, which can be used for custom applications. It also contains a five-pin SWD programming header for the PSoC 5LP.

- 8. External power supply VIN connector (J9): This connector connects an external DC power supply input to the onboard regulators and the USB Type-C power delivery system. The voltage input from the external supply should be between 5 V and 12 V. Moreover, when used as an input to the USB Type-C power delivery system, the external power supply should have enough current capacity to support the load connected via the Type-C port. See "EZ-PD CCG3 Type-C Power Delivery" on page 56 for more details.

- **9. PSoC 6 MCU** user button (SW2): This button can be used to provide an input to PSoC 6 MCU. Note that by default the button connects the PSoC 6 MCU pin to ground when pressed, so you need to configure the PSoC 6 MCU pin as a digital input with resistive pull-up for detecting the button press. This button also provides a wake-up source from low-power modes of the device.

- **10.KitProg2 application selection button (SW4):** This button can be used to switch between KitProg2 programming mode and custom application mode. For more details, see the KitProg2 User Guide.

- **11. Digilent Pmod-compatible I/O header (J14):** This header can be used to connect Digilent Pmod 1 x 6 pin modules.

- **12. Power LED (LED4):** This is the amber LED that indicates the status of power supplied to PSoC 6 MCU.

- **13. Kitprog2 status LEDs (LED1, LED2, and LED3):** Red, amber, and green LEDs (LED1, LED2, and LED3 respectively) indicate the status of KitProg2. For more details on the KitProg2 status, see the KitProg2 User Guide.

- **14. PSoC 6 MCU reset button (SW1):** This button is used to reset PSoC 6 MCU. It connects the PSoC 6 MCU reset (XRES) pin to ground.

- **15. PSoC 6 MCU I/O headers (J18, J19, and J20):** These headers provide connectivity to PSoC 6 MCU GPIOs that are not connected to the Arduino-compatible headers. Most of these pins are

- multiplexed with onbroad peripherals and are not connected to PSoC 6 MCU by default. For detailed information on how to rework the kit to access these pins, see Table 4-2 on page 45.

- **16. Arduino-compatible power header (J1):** This header powers the Arduino shields. It also has a provision to power the kit though the VIN input.

- **17. PSoC 6 MCU debug and trace header (J12):** This header can be connected to an Embedded Trace Macrocell (ETM)-compatible programmer/debugger.

- **18.** Arduino Uno R3-compatible I/O headers (J2, J3, and J4): These I/O headers bring out pins from PSoC 6 MCU to interface with the Arduino shields. Some of these pins are multiplexed with onboard peripherals and are not connected to PSoC 6 MCU by default. For a detailed information on how to rework the kit to access these pins, see Table 4-2 on page 45

- 19. PSoC 6 MCU program and debug header (J11): This 10-pin header allows you to program and debug the PSoC 6 MCU using an external programmer such as MiniProg3. In addition, an external PSoC 4, PSoC 5LP, or PSoC 6 device can be connected to this header and programmed using KitProg2.

- **20.** CapSense proximity header (J13): A wire can be connected to this header to evaluate the proximity sensing feature of CapSense.

- 21. CapSense slider (SLIDER) and buttons (BTN0 and BTN1): The CapSense touch-sensing slider and two buttons, all of which are capable of both self-capacitance (CSD) and mutual-capacitance (CSX) operation, allow you to evaluate Cypress' fourth-generation CapSense technology. The slider and buttons have a 1-mm acrylic overlay for smooth touch sensing.

- **22.** System power V<sub>DD</sub> selection switch (SW5): This switch is used to select the PSoC 6 MCU V<sub>DD</sub> supply voltage between constant 1.8 V, constant 3.3 V, and variable 1.8 to 3.3 V. In the variable 1.8 to 3.3 V mode, the PSoC Programmer software can control the voltage via KitProg2.

- 23. Cypress 512-Mbit serial NOR flash memory (S25FL512S, U4): The S25FL512S NOR flash of 512Mb capacity is connected to the serial memory interface (SMIF) of the PSoC 6 MCU. The NOR device can be used for both data and code memory with execute-in-place (XIP) support and encryption.

- **24.PSoC 6 MCU user LEDs (LED8 and LED9):** These two user LEDs can operate at the entire operating voltage range of PSoC 6 MCU. The LEDs are active LOW, so the pins must be driven to ground to turn ON the LEDs.

- **25.RGB LED (LED5):** This onboard RGB LED can be controlled by the PSoC 6 MCU. The LEDs are active LOW, so the pins must be driven to ground to turn ON the LEDs.

- **26.WiFi and Bluetooth module (LBEE5KL1DX-883, U6):** This kit features the onboard WiFi and Bluetooth combination module to demonstrate the IoT features. The LBEE5KL1DX is a Type 1DX module available with 2.4-GHz WLAN and Bluetooth functionality. Based on Cypress CYW4343W, this module provides high-efficiency RF front-end circuits.

- **27.Cypress 4-Mbit serial Ferroelectric RAM (FM25V10, U5):** Footprint to connect a FM25V10 or any other pin-compatible F-RAM.

- **28. WiFi-BT antenna (ANT1):** This is the onboard antenna connected to the WiFi and Bluetooth module.

- 29.VBACKUP and PMIC control selection switch (SW7, on the bottom side of the board): This switches the VBACKUP supply connection to PSoC 6 MCU between V<sub>DDD</sub>/KitProg2 and the Super Cap/PSoC 6. When V<sub>DDD</sub>/KitProg2 is selected, the regulator ON/OFF is controlled by KitProg2. When the super-capacitor is selected, the regulator ON/OFF is controlled by PSoC 6 MCU.

- **30.PSoC 6 USB Type-C connector (J28):** The USB cable provided with the PSoC 6 WiFi-BT Pioneer Kit can also be connected between this USB connector and the PC to use the PSoC 6 MCU USB device applications.

- **31.Cypress PSoC 6 MCU (CY8C6247BZI-D54, U1):** This kit is designed to highlight the features of the PSoC 6 MCU. For details on PSoC 6 MCU pin mapping, see Table 4-2 on page 45.

- **32.PSoC 6 USB Type-A connector (J27):** USB devices can be connected to this USB Type-A connector and communicate with PSoC 6 MCU USB host applications.

- **33.Arduino-compatible ICSP header (J5):** This header provides an SPI interface for Arduino ICSP-compatible shields.

- **34.PSoC 6 MCU** current measurement jumper (J8, on the bottom side of the board): An ammeter can be connected to this jumper to measure the current consumed by the PSoC 6 MCU.

- **35.KitProg2 (PSoC 5LP) programmer and debugger (CY8C5868LTI-LP039, U2):** The PSoC 5LP device (CY8C5868LTI-LP039) serving as KitProg2, is a multi-functional system, which includes a programmer, debugger, USB-I2C bridge, USB-UART bridge, and a USB-SPI bridge. KitProg2 also supports custom applications. For more details, see the KitProg2 User Guide.

- **36.Battery connector (J15, on the bottom side of the board):** This connector can be used to connect a lithium-ion polymer battery. Note that a battery is not included in the kit package and should be purchased separately if you want to demonstrate battery charging.

- **37.USB PD output (J16):** This header provides a voltage output when the USB Type-C power delivery system receives power from an external host connected to **J10**. See "EZ-PD CCG3 Type-C Power Delivery" **on page 56** for more details.

See "Hardware Functional Description" on page 58 for details on various hardware blocks.

Table 4-1 shows the functionalities of the on-board selection switches.

Table 4-1. Selection Switches on the Pioneer Board

| Switch | Location on the<br>Board | Purpose                                                                                                                                                                                                                                                                          | Default<br>Position        |

|--------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| SW5    | Front                    | Selects the $V_{DD}$ supply of the PSoC 6 MCU between 1.8 V, 3.3 V, and the variable 1.8 V to 3.3 V, which is controlled by KitProg2.                                                                                                                                            | 3.3 V                      |

| SW7    | Back                     | Selects the VBACKUP supply connection of the PSoC 6 MCU between V <sub>DDD</sub> and the super-capacitor. When V <sub>DDD</sub> is selected, the regulator can be turned ON/OFF by KitProg2. When the super-capacitor is selected, the PSoC 6 MCU can turn the regulator ON/OFF. | V <sub>DDD</sub> /KitProg2 |

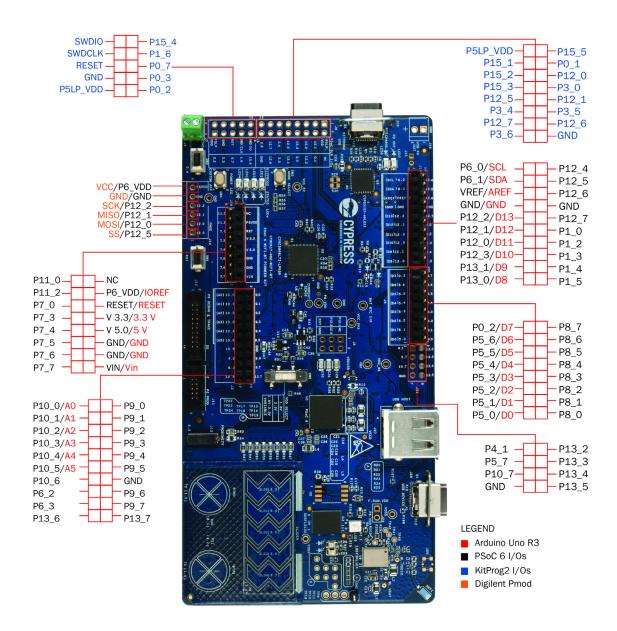

Figure 4-5 shows the pinout of the Pioneer board.

Figure 4-5. Pioneer Board Pinout

Table 4-2. Pioneer Board Pinout

| PSoC 6<br>Pin | Primary<br>Onboard Function                     | Secondary<br>Onboard Function             | Connection Details                                                                                                   |

|---------------|-------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| XRES          | Reset                                           | -                                         |                                                                                                                      |

| P0.0          | WCO IN                                          | _                                         |                                                                                                                      |

| P0.1          | WCO OUT                                         | -                                         |                                                                                                                      |

| P0.2          | Arduino header J4.8, D7                         | _                                         |                                                                                                                      |

| P0.3          | RGB red LED                                     | _                                         |                                                                                                                      |

| P0.4          | User button with Hibernate<br>wakeup capability | _                                         |                                                                                                                      |

| P0.5          | PMIC control                                    | _                                         |                                                                                                                      |

| P1.0          | CapSense Tx                                     | GPIO on non-<br>Arduino header<br>(J19.5) | Populate R174 to connect to the header or remove R62 to disconnect from CapSense.                                    |

| P1.1          | RGB green LED                                   | _                                         |                                                                                                                      |

| P1.2          | GPIO on non-Arduino<br>header (J19.4)           | -                                         |                                                                                                                      |

| P1.3          | GPIO on non-Arduino<br>header (J19.3)           | _                                         |                                                                                                                      |

| P1.4          | GPIO on non-Arduino<br>header (J19.2)           | -                                         |                                                                                                                      |

| P1.5          | Orange user LED                                 | GPIO on non-<br>Arduino header<br>(J19.1) | Connected to primary and secondary functions by default. Remove R27 to disconnect from LED.                          |

| P2.0          | SDIO DATA0                                      | J25.7<br>(WL_JTAG_TMS)                    | Remove R122 (or R110) and mount R115 to disconnect from PSoC 6 and connect the WiFi/BT module to the JTAG connector. |

| P2.1          | SDIO DATA1                                      | J25.3<br>(WL_JTAG_TDI)                    | Remove R32 (or R111) and mount R116 to disconnect from PSoC 6 and connect the WiFi/BT module to the JTAG connector.  |

| P2.2          | SDIO DATA2                                      | J25.5<br>(WL_JTAG_TDO)                    | Remove R128 (or R112) and mount R117 to disconnect from PSoC 6 and connect the WiFi/BT module to the JTAG connector. |

| P2.3          | SDIO DATA3                                      | J25.1<br>(WL_JTAG_TRSTN)                  | Remove R109 (or R132) and mount R114 to disconnect from PSoC 6 and connect the WiFi/BT module to the JTAG connector. |

| P2.4          | SDIO CMD                                        |                                           |                                                                                                                      |

| P2.5          | SDIO CLK                                        | J25.9<br>(WL_JTAG_TCK)                    | Remove R108 (or R28) and mount R113 to disconnect from PSoC 6 and connect the WiFi/BT module to the JTAG connector.  |

| P3.0          | BT UART TXD                                     |                                           | BT UART TXD pin of the WiFi/BT module                                                                                |

| P3.1          | BT UART RXD                                     |                                           | BT UART RXD pin of the WiFi/BT module                                                                                |

| P3.2          | BT UART CTS                                     |                                           | BT UART CTS pin of the WiFi/BT module                                                                                |

| P3.3          | BT UART RTS                                     |                                           | BT UART RTS pin of the WiFi/BT module                                                                                |

Table 4-2. Pioneer Board Pinout (continued)

| PSoC 6<br>Pin | Primary<br>Onboard Function                       | Secondary<br>Onboard Function             | Connection Details                                                                                                 |

|---------------|---------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| P3.4          | BT REG ON                                         |                                           | BT REG ON pin of the WiFi/BT module                                                                                |

| P3.5          | BT HOST WAKE                                      |                                           | BT HOST WAKE pin of the WiFi/BT module                                                                             |

| P4.0          | BT DEV WAKE                                       |                                           | BT DEV WAKE pin of the WiFi/BT module                                                                              |

| P4.1          | Header J21.1                                      |                                           |                                                                                                                    |

| P5.0          | Arduino J4.1, D0<br>UART RX<br>KitProg2 UART TX   | -                                         | Remove R159 to disconnect from KitProg2 UART TX.                                                                   |

| P5.1          | Arduino J4.2, D1<br>UART TX<br>KitProg2 UART RX   | -                                         | Remove R156 to disconnect from KitProg2 UART RX.                                                                   |

| P5.2          | Arduino J4.3, D2<br>UART RTS<br>KitProg2 UART CTS | -                                         | Remove R93 to disconnect from KitProg2 UART CTS. This will also disconnect RTS and SPI lines from KitProg2.        |

| P5.3          | Arduino J4.4, D3<br>UART CTS<br>KitProg2 UART RTS | -                                         | Remove R88 to disconnect from KitProg2 UART CTS. This will also disconnect RTS and SPI lines from KitProg2.        |

| P5.4          | Arduino J4.5, D4                                  | -                                         |                                                                                                                    |

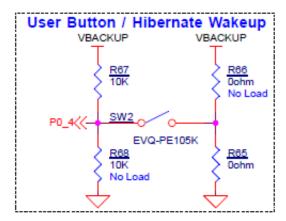

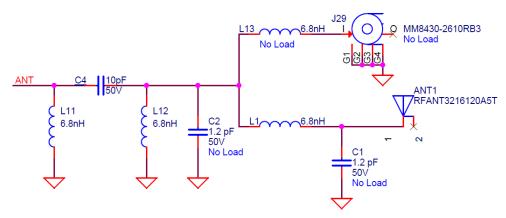

| P5.5          | Arduino J4.6, D5                                  | _                                         |                                                                                                                    |