The following document contains information on Cypress products. The document has the series name, product name, and ordering part numbering with the prefix "MB". However, Cypress will offer these products to new and existing customers with the series name, product name, and ordering part number with the prefix "CY".

## How to Check the Ordering Part Number

- 1. Go to <u>www.cypress.com/pcn</u>.

- 2. Enter the keyword (for example, ordering part number) in the **SEARCH PCNS** field and click **Apply**.

- 3. Click the corresponding title from the search results.

- 4. Download the Affected Parts List file, which has details of all changes

## For More Information

Please contact your local sales office for additional information about Cypress products and solutions.

## About Cypress

Cypress is the leader in advanced embedded system solutions for the world's most innovative automotive, industrial, smart home appliances, consumer electronics and medical products. Cypress' microcontrollers, analog ICs, wireless and USB-based connectivity solutions and reliable, high-performance memories help engineers design differentiated products and get them to market first. Cypress is committed to providing customers with the best support and development resources on the planet enabling them to disrupt markets by creating new product categories in record time. To learn more, go to www.cypress.com.

# 8-bit Microcontroller F<sup>2</sup>MC-8L Family MB89202R Series

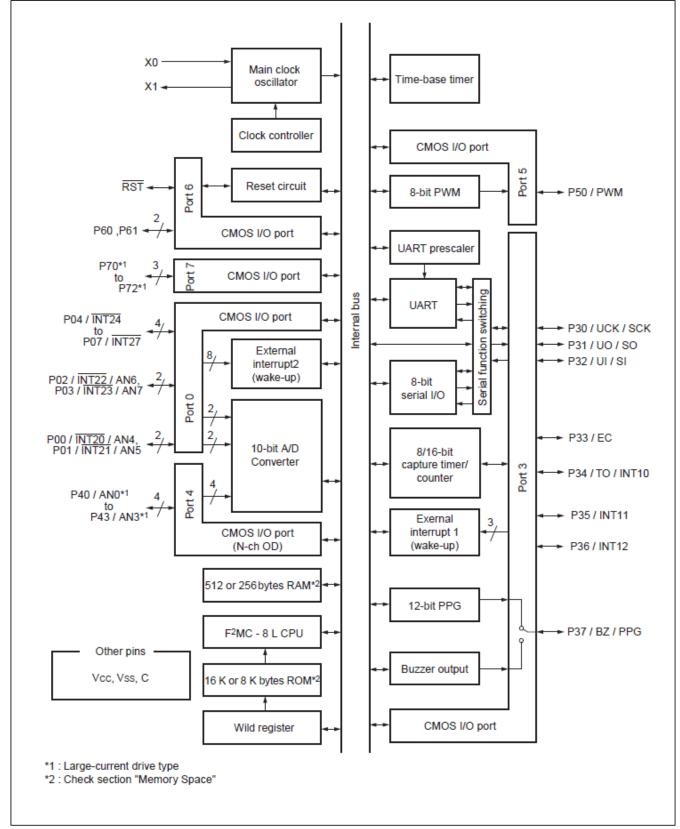

The MB89202R series is a line of single-chip microcontrollers. In addition to a compact instruction set, the microcontrollers contain a variety of peripheral functions such, timers, a serial interface, an A/D converter and an external interrupt.

## Features

- ■F<sup>2</sup>MC-8L family CPU core

- ■Maximum memory space : 64 Kbytes

- ■Minimum execution time : 0.32 µs/12.5 MHz

- ■Interrupt processing time : 2.88 µs/12.5 MHz

- ■I/O ports : Max 26 channels

- ■21-bit time-base timer

- ■8-bit PWM timer

- ■8/16-bit capture timer/counter

- ■10-bit A/D converter : 8 channels

- ∎UART

- ■8-bit serial I/O

- External interrupt 1 : Up to 3 channels

- External interrupt 2 : Up to 8 channels

- ■Wild Register : 2 bytes

- Flash (at least 10,000 program / erase cycles) with read protection

- Low-power consumption modes ( sleep mode, and stop mode)

- ■SH-DIP-32, SSOP-34 package

- ■CMOS Technology

## Contents

| Features                                                | 1    |

|---------------------------------------------------------|------|

| Contents                                                | 2    |

| Product Lineup                                          | 3    |

| Package and Corresponding Products                      | 4    |

| Differences Among Products                              | 4    |

| Pin Assignments                                         |      |

| Pin Description                                         | 7    |

| I/O Circuit Type                                        | 9    |

| Handling Devices                                        | . 11 |

| Programming and Erase Flash Memory                      | . 13 |

| Programming to the EPROM with Evaluation Product Device | . 14 |

| Block Diagram                                           | . 15 |

| CPU Core                                                | . 16 |

| I/O Мар                                                 | . 20 |

| Electrical Characteristics                              |      |

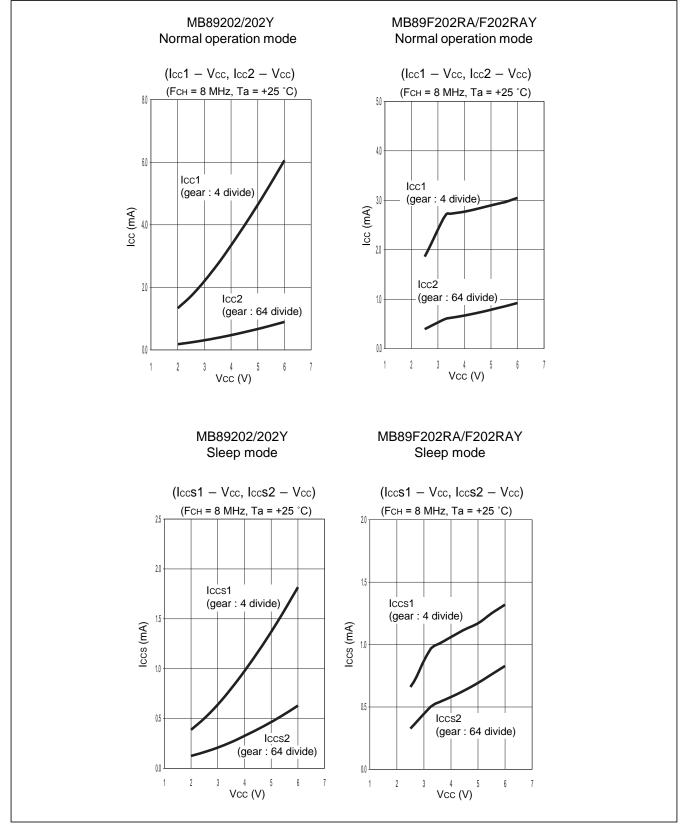

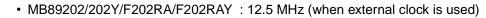

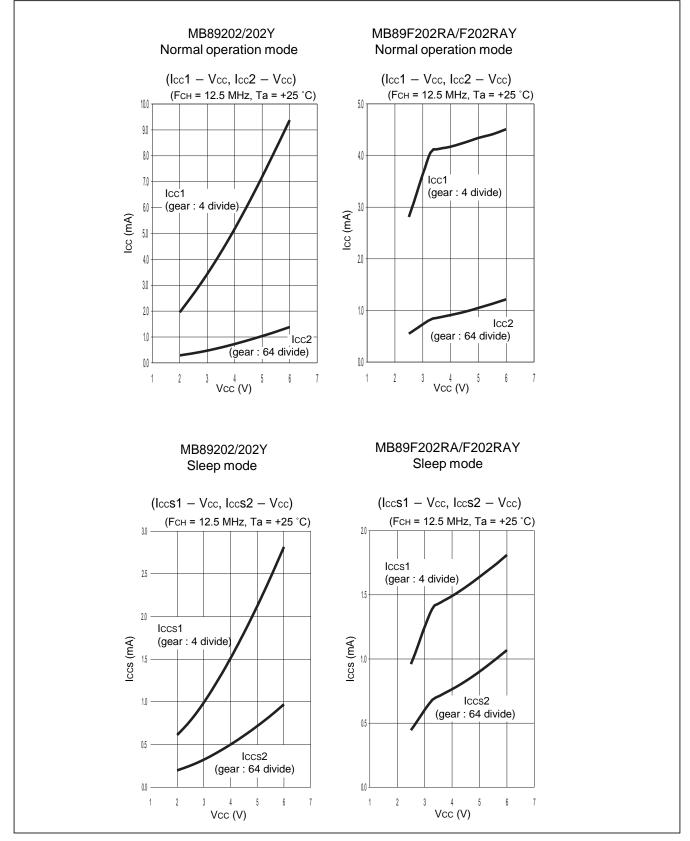

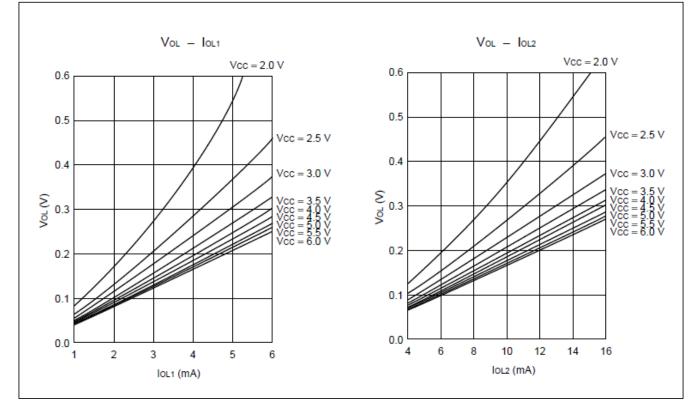

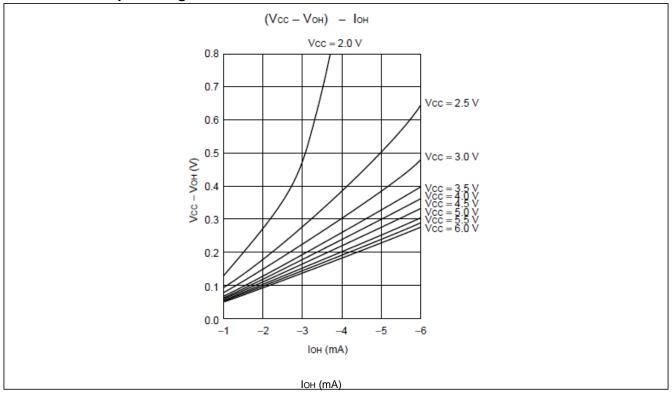

| Example Characteristics                                 | . 37 |

| Mask Options                                            | . 42 |

| Ordering Information                                    |      |

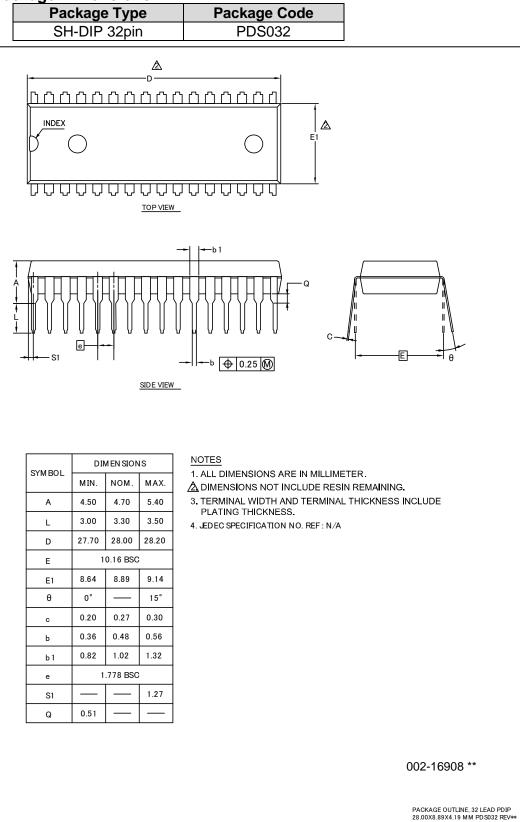

| Package Dimensions                                      | . 43 |

| Major Changes                                           | . 44 |

| Document History                                        | . 45 |

| Sales, Solutions, and Legal Information                 | . 46 |

## **Product Lineup**

| Part number<br>Parameter                   | MB89202<br>MB89202Y                                                                                                                                                                                                                                                                                                                                                            | MB89F202RA<br>MB89F202RAY                                 | MB89V201                                                   |  |  |  |  |  |  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|--|--|--|--|--|--|

| Classification                             | Mask ROM product                                                                                                                                                                                                                                                                                                                                                               | Flash memory product<br>(read protection)                 | Evaluation product (for development)                       |  |  |  |  |  |  |

| ROM size                                   | 16 K × 8 bits<br>(internal mask ROM)                                                                                                                                                                                                                                                                                                                                           | 16 K $\times$ 8 bits (internal flash)                     | 32 K $\times$ 8 bits (external EPROM)                      |  |  |  |  |  |  |

| RAM size                                   |                                                                                                                                                                                                                                                                                                                                                                                | $512 \times 8$ bits                                       |                                                            |  |  |  |  |  |  |

| CPU functions                              | Number of instructions :<br>Instruction bit length :<br>Instruction length :<br>Data bit length :                                                                                                                                                                                                                                                                              | 136<br>8 bits<br>1 to 3 bytes<br>1, 8, 16 bits            |                                                            |  |  |  |  |  |  |

|                                            |                                                                                                                                                                                                                                                                                                                                                                                | Interrupt processing time : 2.88 µs to 46.1 µs (12.5 MHz) |                                                            |  |  |  |  |  |  |

| Ports                                      | General-purpose I/O ports (CMOS) : 26 (also serve as peripherals )<br>(4 ports are also an N-ch open-drain type.)                                                                                                                                                                                                                                                              |                                                           |                                                            |  |  |  |  |  |  |

| 21-bit<br>time-base timer                  | 21-bit Interrupt cycle : 0.66 ms, 2.64 ms, 21 ms, or 335.5 ms with 12.5 MHz main clock                                                                                                                                                                                                                                                                                         |                                                           |                                                            |  |  |  |  |  |  |

| Watchdog timer                             | Reset generation cycle: 335.5 ms minimum with 12.5 MHz main clock                                                                                                                                                                                                                                                                                                              |                                                           |                                                            |  |  |  |  |  |  |

| 8-bit PWM timer                            | <ul> <li>8-bit interval timer operation (square output capable, operating clock cycle :<br/>0.32 μs , 2.56 μs, 5.1 μs, 20.5 μs)</li> <li>8-bit resolution PWM operation (conversion cycle : 81.9 μs to 21.47 s : in the selection of internal shift clock of 8/16-bit capture timer)</li> <li>Count clock selectable between 8-bit and 16-bit timer/counter outputs</li> </ul> |                                                           |                                                            |  |  |  |  |  |  |

| 8/16-bit<br>capture, timer/counter         | External captured input selectable<br>8-bit capture timer/counter × 1 channel + 8-bit timer or<br>16-bit capture timer/counter × 1 channel<br>Capable of event count operation and square wave output with 8-bit timer 0 or 16-bit<br>counter                                                                                                                                  |                                                           |                                                            |  |  |  |  |  |  |

| UART                                       | Transfer data length : 6/7/8                                                                                                                                                                                                                                                                                                                                                   | bits                                                      |                                                            |  |  |  |  |  |  |

| 8-bit Serial I/O                           | 8 bits LSB first/MSB first se<br>One clock selectable from f<br>(one external shift clock, th                                                                                                                                                                                                                                                                                  |                                                           | 3 μs, 6.4 μs, 25.6 μs)                                     |  |  |  |  |  |  |

| 12-bit PPG timer                           | Output frequency : Pulse w                                                                                                                                                                                                                                                                                                                                                     | idth and cycle selectable                                 |                                                            |  |  |  |  |  |  |

| External interrupt 1<br>(wake-up function) | Rising/falling/both edge sel                                                                                                                                                                                                                                                                                                                                                   |                                                           | equest output enabled)<br>on is also permitted in the stop |  |  |  |  |  |  |

| External interrupt 2<br>(wake-up function) | 8 channels (low-level interru<br>Used for wake-up from stop<br>mode.)                                                                                                                                                                                                                                                                                                          |                                                           | on is also permitted in the stop                           |  |  |  |  |  |  |

(Continued)

(Continued)

| Part number<br>Parameter                                          | MB89202<br>MB89202Y                                                                                                        | MB89F202RA<br>MB89F202RAY                                                                                                                                                                                     | MB89V201                                                                                                                                                                                 |  |  |  |  |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 10-bit A/D converter                                              | 10-bit precision × 8 channels<br>A/D conversion function (Co<br>Continuous activation by 8/1                               | onversion time : 12.16 μs/12                                                                                                                                                                                  |                                                                                                                                                                                          |  |  |  |  |

| Wild Register                                                     |                                                                                                                            | 8-bit × 2                                                                                                                                                                                                     |                                                                                                                                                                                          |  |  |  |  |

| Standby mode                                                      | Sleep mode, and Stop mode                                                                                                  |                                                                                                                                                                                                               |                                                                                                                                                                                          |  |  |  |  |

| Overhead time from<br>reset to the first<br>instruction execution | Power-on reset:<br>Oscillation stabilization<br>wait <sup>*1</sup><br>External reset: a few μs<br>Software reset: a few μs | Power-on reset:<br>Voltage regulator and<br>oscillation stabilization<br>wait<br>(31.5 ms/12.5 MHz)<br>External reset:<br>Oscillation stabilization<br>wait<br>(21.0 ms/12.5 MHz)<br>Software reset: a few μs | Power-on reset:<br>Oscillation stabilization<br>wait<br>(21.0 ms / 12.5 MHz)<br>External reset:<br>Oscillation<br>stabilization wait<br>(21.0 ms / 12.5 MHz)<br>Software reset: a few μs |  |  |  |  |

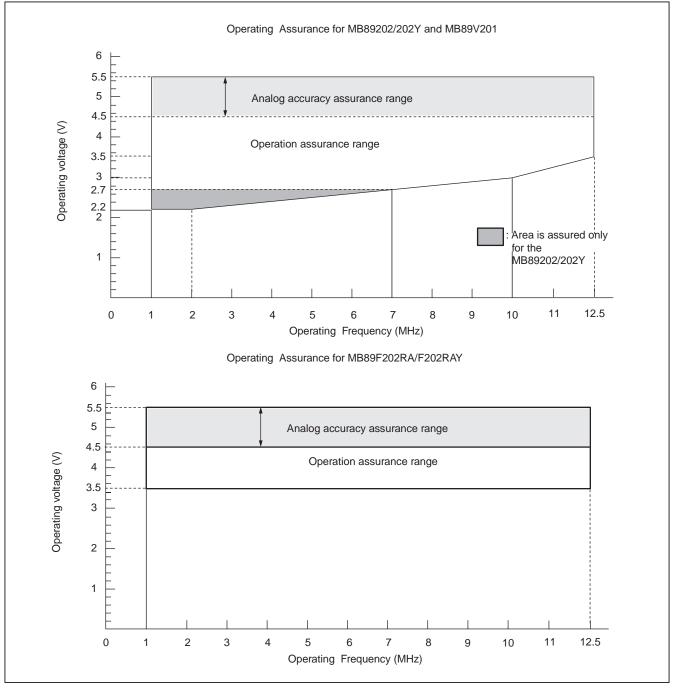

| Power supply voltage*2                                            | 2.2 V to 5.5 V                                                                                                             | 3.5 V to 5.5 V                                                                                                                                                                                                | 2.7 V to 5.5 V                                                                                                                                                                           |  |  |  |  |

\*1 : Check section "Mask Options".

\*2 : The minimum operating voltage varies with the operating frequency, the function. (The operating voltage of the A/D converter is assured separately. Check section "Electrical Characteristics")

## Package and Corresponding Products

| Package       | MB89202 | MB89202Y | MB89F202RA | MB89F202RAY | MB89V201 |

|---------------|---------|----------|------------|-------------|----------|

| PDS032        | 0       | ×        | 0          | ×           | ×        |

| FPT-34P-M03 * | ×       | 0        | ×          | 0           | ×        |

| LQD064        | х       | х        | ×          | ×           | 0        |

$\bigcirc$  : Available  $\times$  : Not available

\*: This package is manufacturing discontinuance.

## **Differences Among Products**

## Memory Size

Before evaluating using the evaluation product, verify its differences from the product that will actually be used.

## Mask Options

Functions that can be selected as options and how to designate these options vary by the product. Before using options check section "Mask Options".

## **Pin Assignments**

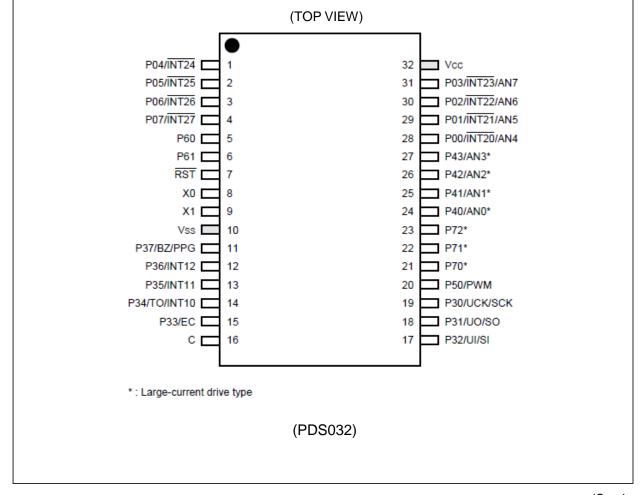

## • MB89202, MB89F202RA

(Continued)

## (Continued)

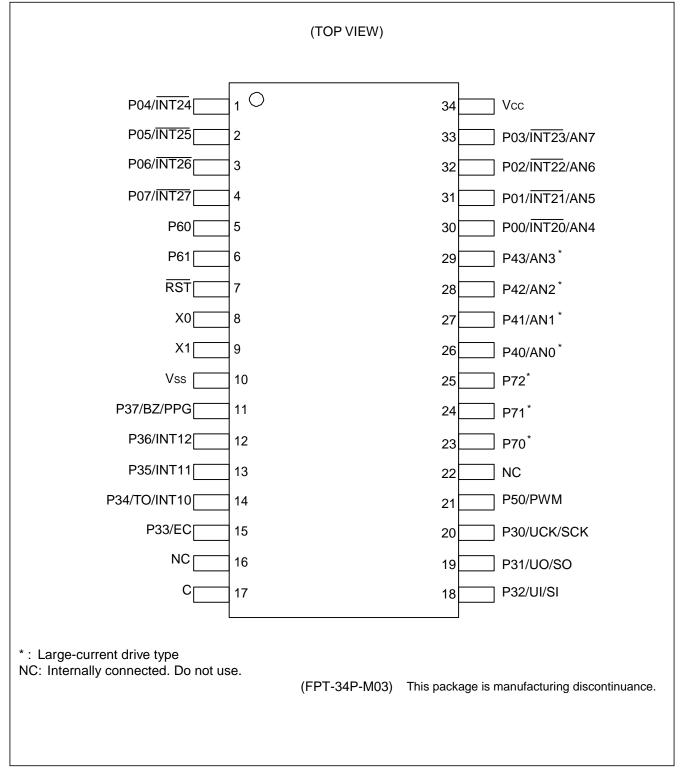

## • MB89202Y, MB89F202RAY

## **Pin Description**

| Pin        | No.      |                                                  | I/O               |                                                                                                                                                                                                                                                                                            |

|------------|----------|--------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SH-DIP32*1 | SSOP34*2 | Pin name                                         | circuit<br>type∗₃ | Function                                                                                                                                                                                                                                                                                   |

| 8          | 8        | X0                                               | A                 | Pins for connecting the crystal for the main clock. To use an                                                                                                                                                                                                                              |

| 9          | 9        | X1                                               | ~                 | external clock, input the signal to X0 and leave X1 open.                                                                                                                                                                                                                                  |

| 5, 6       | 5, 6     | P60, P61                                         | H/E               | General-purpose CMOS input ports for MB89F202RA/F202RAY.<br>General-purpose CMOS I/O ports for MB89202/202Y/MB89V201.                                                                                                                                                                      |

| 7          | 7        | RST                                              | С                 | Reset I/O pin.<br>This pin serves as an N-channel open-drain reset output and a reset<br>input as well. The reset is a hysteresis input.<br>It outputs the "L" signal in response to an internal reset request. Also,<br>it initializes the internal circuit upon input of the "L" signal. |

| 1 to 4     | 1 to 4   | P04/I <u>NT24 t</u> o<br>P07/INT27               | D                 | General-purpose CMOS I/O ports.<br>These pins also serve as an input (wake-up input) of external interrupt<br>2. The input of external interrupt 2 is a hysteresis input.                                                                                                                  |

| 28, 29     | 30, 31   | P00/INT20/<br>A <u>N4 ,</u><br>P01/INT21/<br>AN5 | G                 | General-purpose CMOS I/O ports.<br>These pins also serve as an input (wake-up input) of external interrupt<br>2 or as a 10-bit A/D converter analog input. The input of external<br>interrupt 2 is a hysteresis input.                                                                     |

| 30, 31     | 32, 33   | P02/INT22/<br>A <u>N6,</u><br>P03/INT23/<br>AN7  | G                 | General-purpose CMOS I/O ports.<br>These pins also serve as an input (wake-up input) of external interrupt<br>2 or as a 10-bit A/D converter analog input. The input of external<br>interrupt 2 is a hysteresis input.                                                                     |

| 19         | 20       | P30/UCK/<br>SCK                                  | В                 | General-purpose CMOS I/O port.<br>This pin also serves as the clock I/O pin for the UART or 8-bit serial<br>I/O. The resource is a hysteresis input.                                                                                                                                       |

| 18         | 19       | P31/UO/SO                                        | Е                 | General-purpose CMOS I/O port.<br>This pin also serves as the data output pin for the UART or 8-bit serial<br>I/O.                                                                                                                                                                         |

| 17         | 18       | P32/UI/SI                                        | В                 | General-purpose CMOS I/O port.<br>This pin also serves as the data input pin for the UART or 8-bit serial<br>I/O. The resource is a hysteresis input.                                                                                                                                      |

| 15         | 15       | P33/EC                                           | В                 | General-purpose CMOS I/O port.<br>This pin also serves as the external clock input pin for the 8/16-bit<br>capture timer/counter. The resource is a hysteresis input.                                                                                                                      |

| 14         | 14       | P34/TO/<br>INT10                                 | В                 | General-purpose CMOS I/O port.<br>This pin also serves as the output pin for the 8/16-bit capture timer/<br>counter or as the input (wake-up input) for external interrupt 1. The<br>resource is a hysteresis input.                                                                       |

| 13, 12     | 13, 12   | P35/INT11,<br>P36/INT12                          | В                 | General-purpose CMOS I/O ports.<br>These pins also serve as the input (wake-up input) for external<br>interrupt 1. The resource is a hysteresis input.                                                                                                                                     |

(Continued)

(Continued)

| Pin        | No.      |                          | I/O               |                                                                                                                                                                                                                                         |

|------------|----------|--------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SH-DIP32*1 | SSOP34*2 | Pin name                 | circuit<br>type∗₃ | Function                                                                                                                                                                                                                                |

| 11         | 11       | P37/BZ/<br>PPG           | Е                 | General-purpose CMOS I/O port.<br>This pin also serves as the buzzer output pin or the 12-bit PPG<br>output.                                                                                                                            |

| 20         | 21       | P50/PWM                  | E                 | General-purpose CMOS I/O port.<br>This pin also serves as the 8-bit PWM timer output pin.                                                                                                                                               |

| 24 to 27   | 26 to 29 | P40/AN0<br>to<br>P43/AN3 | F                 | General-purpose CMOS I/O ports.<br>These pins can also be used as N-channel open-drain ports.<br>These pins also serve as 10-bit A/D converter analog input pins.                                                                       |

| 21 to 23   | 23 to 25 | P70 to P72               | E                 | General-purpose CMOS I/O ports.                                                                                                                                                                                                         |

| 32         | 34       | Vcc                      | _                 | Power supply pin                                                                                                                                                                                                                        |

| 10         | 10       | Vss                      | _                 | Power (GND) pin                                                                                                                                                                                                                         |

| 16         | 17       | С                        |                   | MB89F202RA/F202RAY:<br>Capacitance pin for regulating the power supply.<br>Connect an external ceramic capacitor of about 0.1μF.<br>MB89202/202Y:<br>This pin is not internally connected. It is unnecessary to connect<br>a capacitor. |

| _          | 16, 22   | NC                       | —                 | Internally connected pins<br>Be sure to leave it open.                                                                                                                                                                                  |

\*1: DIP-32P-M06

\*2: FPT-34P-M03

\*3: Refer to "I/O Circuit Type" for details on the I/O circuit types.

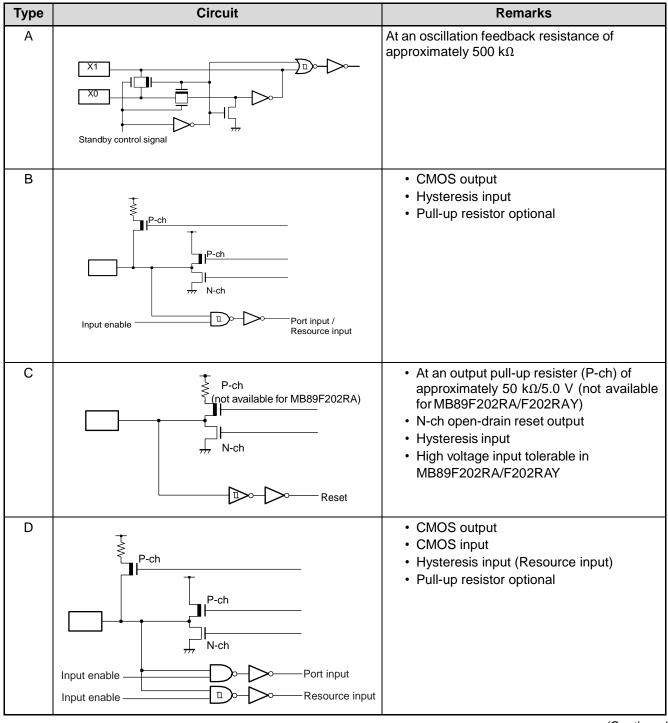

## I/O Circuit Type

(Continued)

## (Continued) Туре Circuit Remarks · CMOS output Е CMOS input P-ch · Pull-up resistor optional • P70-P72 are large-current drive type P-ch N-ch Port input Input enable F · CMOS output CMOS input P-ch Open-drain control · Analog input • N-ch open-drain output available • P40-P43 are large-current drive type N-ch Analog input Input enable Port input A/D enable G · CMOS output Š CMOS input • Hysteresis input (Resource input) P-ch · Analog input P-ch Input enable Port input Input enable Resource input Analog input A/D enable Н **CMOS** input Port input Input enable

## Handling Devices

## • Preventing Latch-up

Latch-up may occur on CMOS ICs if voltage higher than Vcc or lower than Vss is applied to input and output pins other than medium- and high-voltage pins or if higher than the voltage which shows on "1. Absolute Maximum Ratings" in section "Electrical Characteristics" is applied between Vcc and Vss.

When latch-up occurs, power supply current increases rapidly and might thermally damage elements. When using, take great care not to exceed the absolute maximum ratings.

#### • Treatment of Unused Input Pins

Leaving unused input terminals open may lead to permanent damage due to malfunction and latch-up; pull up or pull down the terminals through the resistors of 2 k $\Omega$  or more.

Make the unused I/O terminal in a state of output and leave it open or if it is in an input state, handle it with the same procedure as the input terminals.

#### • Treatment of NC Pins

Be sure to leave (internally connected) NC pins open.

#### Power Supply Voltage Fluctuations

Although V<sub>CC</sub> power supply voltage is assured to operate within the rated range, a rapid fluctuation of the voltage could cause malfunctions, even if it occurs within the rated range. Stabilizing voltage supplied to the IC is therefore important. As stabilization guidelines, it is recommended to control power so that V<sub>CC</sub> ripple fluctuations (P-P value) will be less than 10% of the standard V<sub>CC</sub> value at the commercial frequency (50 Hz/60 Hz) and the transient fluctuation rate will be less than 0.1 V/ms at the time of a momentary fluctuation such as when power is switched.

#### • Precautions when Using an External Clock

When an external clock is used, oscillation stabilization time is required even for power-on reset (optional) and wake-up from stop mode.

#### About the Wild Register Function

No wild register can be debugged on the MB89V201. For the operation check, test the MB89F202RA/F202RAY installed on a target system.

#### Program Execution in RAM

When the MB89V201 is used, no program can be executed in RAM.

#### • Note to Noise in the External Reset Pin (RST)

If the reset pulse applied to the external reset pin ( $\overline{RST}$ ) does not meet the specifications, it may cause malfunctions. Use caution so that the reset pulse less than the specifications will not be fed to the external reset pin ( $\overline{RST}$ ).

## • External pull-up for the External Reset Pin (RST)

Internal pull-up control for  $\overline{RST}$  pin is not available for MB89F202RA/F202RAY. To ensure proper external reset control in MB89F202RA/F202RAY, an external pull-up (recommend 100 k $\Omega$ ) for  $\overline{RST}$  pin must be required. Please also check section "Programming and Erase Flash Memory".

#### Notes on selecting mask option

Please select "With reset output" by the mask option when power-on reset is generated at the power supply ON, and the device is used without inputting external reset.

## Programming and Erase Flash Memory

## 1. Flash Memory

The flash memory incorporates a flash memory interface circuit that allows read access and program access from the CPU to be performed in the same way as mask ROM. Programming and erasing flash memory is also performed via the flash memory interface circuit by executing instructions in the CPU. This enables the flash memory to be updated in place under the control of the CPU, providing an efficient method of updating program and data.

## 2. Flash Memory Features

- 16 K byte × 8-bit configuration or 8 K byte × 8-bit configuration\*

- Automatic programming algorithm (Embedded Algorithm)

- Data polling and toggle bit for detection of program/erase completion

- Detection of program/erase completion via CPU interrupt

- Compatible with JEDEC-standard commands

- No. of program / erase cycles: Minimum 10,000

- \* : Check section "Memory Space".

## 3. Procedure for Programming and Erasing Flash Memory

Programming and reading flash memory cannot be performed at the same time. Accordingly, to program or erase flash memory, the program must first be copied from flash memory to RAM so that programming can be performed without program access from flash memory. Also for flash memory program or erase, a high voltage (instead of an external pull-up) must be applied to external reset RST pin. Check section " 6. Flash Memory Program/Erase Characteristics" in "Electrical Characteristics".

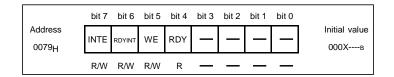

## 4. Flash Memory Control Status Register (FMCS)

## 5. Memory Space

The series has 1 flash memory size configuration. The memory space for the CPU access and for the flash programmer access of the configuration is listed below. Check section " 6. Flash Memory Program/Erase Characteristics" in "Electrical Characteristics".

| Part Number               | Memory size | CPU address                            | Programmer address |

|---------------------------|-------------|----------------------------------------|--------------------|

| MB89F202RA<br>MB89F202RAY | 16 K bytes  | FFFF <sub>H</sub> to C000 <sub>H</sub> | 3FFFн to 0000н     |

## 6. Flash Content Protection

Flash content can be read using parallel / serial programmer if the flash content protection mechanism is not activated.

One predefined area of the flash (FFFC<sub>H</sub>) is assigned to be used for preventing the read access of flash content. If the protection code " $01_{\text{H}}$ " is written in this address (FFFC<sub>H</sub>), the flash content cannot be read by any parallel/ serial programmer.

Note: The program written into the flash cannot be verified once the flash protection code is written ("01<sub>H</sub>" in FFFC<sub>H</sub>). It is advised to write the flash protection code at last.

## Programming to the EPROM with Evaluation Product Device

## 1. EPROM for Use

MBM27C256A (DIP-28)

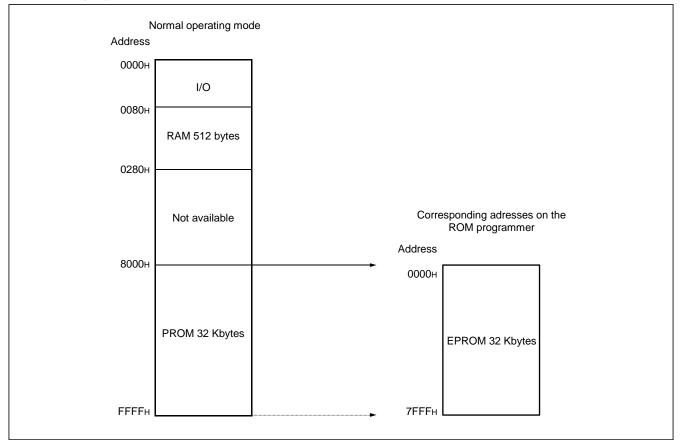

## 2. Memory Space

## 3. Programming to the EPROM

- (1) Set the EPROM programmer to the MBM27C256A.

- (2) Load program data into the EPROM programmer at 0000H to 7FFFH.

- (3) Program to 0000H to 7FFFH with the EPROM programmer.

## **Block Diagram**

## **CPU Core**

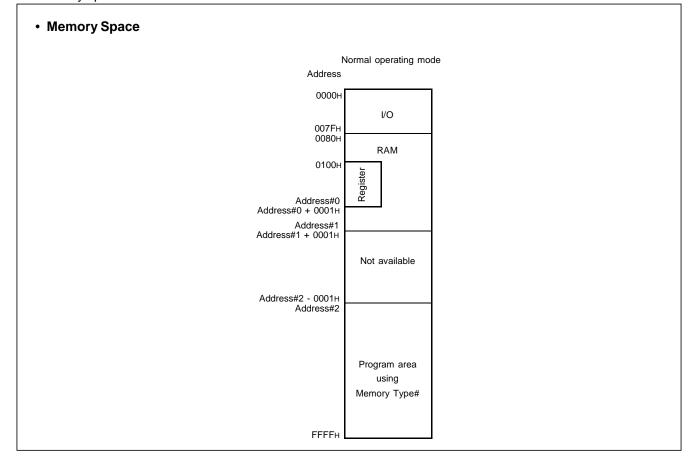

## 1. Memory Space

The microcontrollers of the MB89202R series offer a memory space of 64 Kbytes for storing all of I/O, data, and program areas. The I/O area is located at the lowest address. The data area is provided immediately above the I/O area. The data area can be divided into register, stack, and direct areas according to the application. The program area is located at exactly the opposite end, that is, near the highest address. Provide the tables of interrupt reset vectors and vector call instructions toward the highest address within the program area. The memory space of the MB89202R series is structured as illustrated below.

| Part Number                                    | RAM size  | Address#0 | Address#1 |

|------------------------------------------------|-----------|-----------|-----------|

| MB89V201<br>MB89F202RA/F202RAY<br>MB89202/202Y | 512 bytes | 01FF⊦     | 027Fн     |

| Part Number        | Memory Type#                    | Address#2 |

|--------------------|---------------------------------|-----------|

| MB89V201           | 32 Kbytes External EPROM        | 8000н     |

| MB89F202RA/F202RAY | 16 Kbytes Internal Flash Memory | С000н     |

| MB89202/202Y       | 16 Kbytes ROM                   | С000н     |

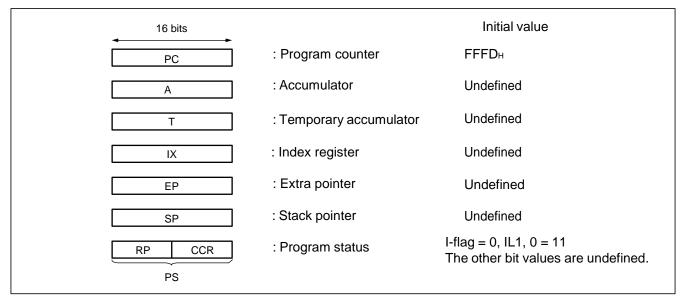

## 2. Registers

The MB89202R series has two types of registers; dedicated registers in the CPU and general-purpose registers in the memory. The following dedicated registers are provided :

| Program counter (PC) :      | A 16-bit register for indicating instruction storage positions                                                                                                       |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Accumulator (A) :           | A 16-bit temporary register for storing arithmetic operations, etc. When the instruction is an 8-bit data processing instruction, the lower byte is used.            |

| Temporary accumulator (T) : | A 16-bit register which performs arithmetic operations with the accumulator<br>When the instruction is an 8-bit data processing instruction, the lower byte is used. |

| Index register (IX) :       | A 16-bit register for index modification                                                                                                                             |

| Extra pointer (EP) :        | A 16-bit pointer for indicating a memory address                                                                                                                     |

| Stack pointer (SP) :        | A 16-bit register for indicating a stack area                                                                                                                        |

| Program status (PS) :       | A 16-bit register for storing a register pointer, a condition code                                                                                                   |

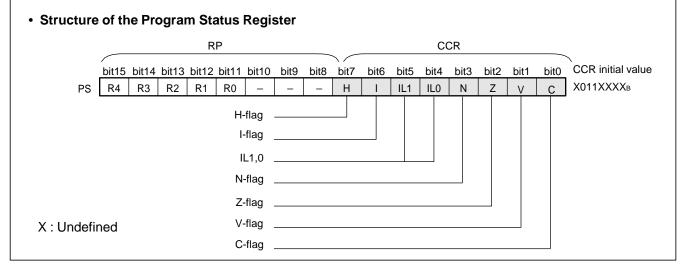

The PS can further be divided into higher 8 bits for use as a register bank pointer (RP) and the lower 8 bits for use as a condition code register (CCR) . (See the diagram below.)

The RP indicates the address of the register bank currently in use. The relationship between the pointer contents and the actual address is based on the conversion rule illustrated below.

|                     |     |       |       |     |     |     |     |       |    | R  | Ρ  |    | L  | ower | OP co | odes |

|---------------------|-----|-------|-------|-----|-----|-----|-----|-------|----|----|----|----|----|------|-------|------|

|                     | "0" | "0"   | "0"   | "0" | "0" | "0" | "0" | "1" [ | R4 | R3 | R2 | R1 | R0 | b2   | b1    | b0   |

|                     | ¥   | ¥     | ¥     | ¥   | ¥   | ¥   | ¥   | + -   | ¥  | +  | ¥  | ŧ  | +  | ¥    | ¥     | ŧ    |

| Generated addresses | A1  | 5 A14 | 1 A13 | A12 | A11 | A10 | A9  | A8    | A7 | A6 | A5 | A4 | A3 | A2   | A1    | Α    |

The CCR consists of bits indicating the results of arithmetic operations and the contents of transfer data and bits for control of CPU operations at the time of an interrupt.

- H- flag: Set to "1" when a carry or a borrow from bit 3 to bit 4 occurs as a result of an arithmetic operation. Cleared to "0" otherwise. This flag is for decimal adjustment instructions.

- I-flag : Interrupt is enabled when this flag is set to "1". Interrupt is disabled when the flag is cleared to "0". Cleared to "0" at the reset.

- IL1, 0: Indicates the level of the interrupt currently allowed. Processes an interrupt only if its request level is higher than the value indicated by this bit.

| IL1 | IL0 | Interrupt level | High-low           |

|-----|-----|-----------------|--------------------|

| 0   | 0   | 1               | High               |

| 0   | 1   | l I             | t                  |

| 1   | 0   | 2               |                    |

| 1   | 1   | 3               | Low = no interrupt |

- N-flag: Set to "1" if the MSB becomes to "1" as the result of an arithmetic operation. Cleared to "0" when the bit is cleared to "0".

- Z-flag: Set to "1" when an arithmetic operation results in 0. Cleared to "0" otherwise.

- V-flag: Set to "1" if the complement on 2 overflows as a result of an arithmetic operation. Cleared to "0" if the overflow does not occur.

- C-flag: Set to "1" when a carry or a borrow from bit 7 occurs as a result of an arithmetic operation. Cleared to "0" otherwise. Set to the shift-out value in the case of a shift instruction.

The following general-purpose registers are provided :

General-purpose registers : An 8-bit register for storing data

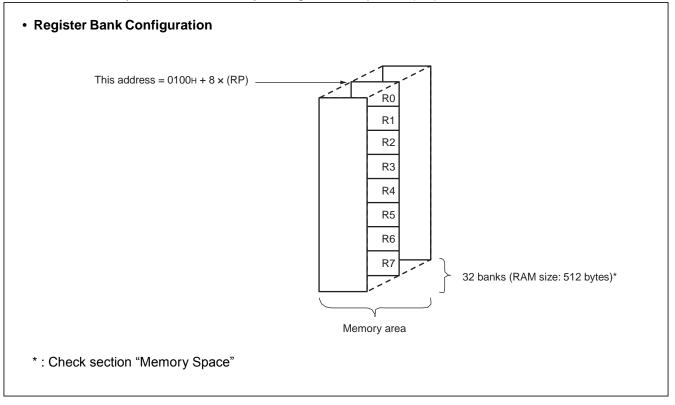

The general-purpose registers are 8 bits and located in the register banks of the memory. One bank contains eight registers and up to a total of 32 banks (in 512 RAM size) can be used in the MB89202R series. The bank currently in use is indicated by the register bank pointer (RP).

## I/O Map

| Address        | Register name | Register description                    | Read/write | Initial value |

|----------------|---------------|-----------------------------------------|------------|---------------|

| 0000н          | PDR0          | Port 0 data register                    | R/W        | ХХХХХХХ в     |

| 0001н          | DDR0          | Port 0 data direction register          | W          | 00000000      |

| 0002н to 0006н |               | Reserved                                |            |               |

| 0007н          | SYCC          | System clock control register           | R/W        | 1 1 1 1 0 0 в |

| 0008н          | STBC          | Standby control register                | R/W        | 00010в        |

| 0009н          | WDTC          | Watchdog timer control register         | R/W        | 0 ХХХХ в      |

| 000Ан          | TBTC          | Time-base timer control register        | R/W        | 00000 в       |

| 000Вн          |               | Reserved                                |            |               |

| 000Сн          | PDR3          | Port 3 data register                    | R/W        | ХХХХХХХ В     |

| 000Dн          | DDR3          | Port 3 data direction register          | W          | 00000000      |

| 000Ен          | RSFR          | Reset flag register                     | R          | ХХХХв         |

| 000Fн          | PDR4          | Port 4 data register                    | R/W        | ХХХХ в        |

| 0010н          | DDR4          | Port 4 data direction register          | R/W        | в             |

| 0011н          | OUT4          | Port 4 output format register           | R/W        | в             |

| 0012н          | PDR5          | Port 5 data register                    | R/W        | Хв            |

| 0013н          | DDR5          | Port 5 data direction register          | R/W        |               |

| 0014н          | RCR21         | 12-bit PPG control register 1           | R/W        | 0000000 в     |

| 0015н          | RCR22         | 12-bit PPG control register 2           | R/W        | 000000 в      |

| 0016н          | RCR23         | 12-bit PPG control register 3           | R/W        | 0-00000 в     |

| <b>0017</b> н  | RCR24         | 12-bit PPG control register 4           | R/W        | 000000        |

| <b>0018</b> н  | BZCR          | Buzzer register                         | R/W        |               |

| 0019н          | TCCR          | Capture control register                | R/W        | 0000000       |

| 001Ан          | TCR1          | Timer 1 control register                | R/W        | 000-000 в     |

| 001Bн          | TCR0          | Timer 0 control register                | R/W        | 00000000      |

| 001Сн          | TDR1          | Timer 1 data register                   | R/W        | ХХХХХХХ в     |

| 001Dн          | TDR0          | Timer 0 data register                   | R/W        | ХХХХХХХ в     |

| 001Eн          | ТСРН          | Capture data register H                 | R          | ХХХХХХХ в     |

| 001Fн          | TCPL          | Capture data register L                 | R          | ХХХХХХХ В     |

| 0020н          | TCR2          | Timer output control register           | R/W        |               |

| 0021н          |               | Reserved                                | 1          |               |

| 0022н          | CNTR          | PWM control register                    | R/W        | 0-00000       |

| 0023н          | COMR          | PWM compare register                    | W          | ХХХХХХХ в     |

| 0024н          | EIC1          | External interrupt 1 Control register 1 | R/W        | ООООООО в     |

(Continued)

| Address        | Register name | Register description                    | Read/write | Initial value |  |  |  |

|----------------|---------------|-----------------------------------------|------------|---------------|--|--|--|

| 0025н          | EIC2          | External interrupt 1 Control register 2 | R/W        | вооов         |  |  |  |

| 0026н          |               |                                         |            |               |  |  |  |

| 0027н          |               | Reserved                                |            |               |  |  |  |

| 0028н          | SMC           | Serial mode control register            | R/W        | 00000-00в     |  |  |  |

| 0029н          | SRC           | Serial rate control register            | R/W        | 011000в       |  |  |  |

| 002Ан          | SSD           | Serial status and data register         | R/W        | 00100-1Хв     |  |  |  |

| 002Bн          | SIDR          | Serial input data register              | R          | ХХХХХХХ В     |  |  |  |

| UUZDH          | SODR          | Serial output data register             | W          | ХХХХХХХ В     |  |  |  |

| 002Сн          | UPC           | Clock division selection register       | R/W        | 0010в         |  |  |  |

| 002Dн to 002Fн |               | Reserved                                |            |               |  |  |  |

| 0030н          | ADC1          | A/D control register 1                  | R/W        | - 0000000 в   |  |  |  |

| 0031н          | ADC2          | A/D control register 2                  | R/W        | - 0000001 в   |  |  |  |

| 0032н          | ADDH          | A/D data register H                     | R          | ХХв           |  |  |  |

| 0033н          | ADDL          | A/D data register L                     | R          | ХХХХХХХ В     |  |  |  |

| 0034н          | ADEN          | A/D enable register                     | R/W        | 0000000       |  |  |  |

| 0035н          |               | Reserved                                |            |               |  |  |  |

| 0036н          | EIE2          | External interrupt 2 control register1  | R/W        | 00000000      |  |  |  |

| 0037н          | EIF2          | External interrupt 2 control register2  | R/W        | Ов            |  |  |  |

| 0038н          |               | Reserved                                |            |               |  |  |  |

| 0039н          | SMR           | Serial mode register                    | R/W        | 00000000      |  |  |  |

| 003Ан          | SDR           | Serial data register                    | R/W        | ХХХХХХХ В     |  |  |  |

| 003Вн          | SSEL          | Serial function switching register      | R/W        | Ов            |  |  |  |

| 003Cн to 003Fн |               | Reserved                                |            |               |  |  |  |

| 0040н          | WRARH0        | Upper-address setting register 0        | R/W        | ХХХХХХХ В     |  |  |  |

| 0041н          | WRARL0        | Lower-address setting register 0        | R/W        | ХХХХХХХ В     |  |  |  |

| 0042н          | WRDR0         | Data setting register 0                 | R/W        | ХХХХХХХ В     |  |  |  |

| 0043н          | WRARH1        | Upper-address setting register 1        | R/W        | ХХХХХХХ В     |  |  |  |

| 0044н          | WRARL1        | Lower-address setting register 1        | R/W        | ХХХХХХХ В     |  |  |  |

| 0045н          | WRDR1         | Data setting register 1                 | R/W        | ХХХХХХХ В     |  |  |  |

| 0046н          | WREN          | Address comparison EN register          | R/W        | ХХХХХХОО в    |  |  |  |

| 0047н          | WROR          | Wild-register data test register        | R/W        |               |  |  |  |

| 0048н to 005Fн |               | Reserved                                | ·          |               |  |  |  |

(Continued)

| (Continued)    |               |                                      |               |               |  |  |

|----------------|---------------|--------------------------------------|---------------|---------------|--|--|

| Address        | Register name | Register description                 | Read/write    | Initial value |  |  |

| 0060н          | PDR6          | Port 6 data register                 | R/W           | ХХв           |  |  |

| 0061н          | DDR6          | Port 6 data direction register*      | R/W           |               |  |  |

| 0062н          | PUL6          | Port 6 pull-up setting register*     | R/W           |               |  |  |

| 0063н          | PDR7          | Port 7 data register                 | R/W           | ХХХ в         |  |  |

| 0064н          | DDR7          | Port 7 data direction register       | R/W           |               |  |  |

| 0065н          | PUL7          | Port 7 pull-up setting register      | R/W           |               |  |  |

| 0066н to 006Fн |               | Reserved                             |               |               |  |  |

| 0070н          | PUL0          | Port 0 pull-up setting register      | R/W           | 00000000      |  |  |

| 0071н          | PUL3          | Port 3 pull-up setting register      | R/W           | 00000000      |  |  |

| 0072н          | PUL5          | Port 5 pull-up setting register      | R/W           |               |  |  |

| 0073н to 0078н |               | Reserved                             | •             |               |  |  |

| 0079н          | FMCS          | Flash memory control status register | R/W           | 000Хв         |  |  |

| 007Ан          |               | Reserved                             | ·             | ·             |  |  |

| 007Вн          | ILR1          | Interrupt level setting register1    | W             | 1111111 в     |  |  |

| 007Сн          | ILR2          | Interrupt level setting register2 W  |               | 1111111 в     |  |  |

| 007Dн          | ILR3          | Interrupt level setting register3    | W             | 1111111 в     |  |  |

| 007Eн          | ILR4          | Interrupt level setting register4    | W             | 1111111 в     |  |  |

| 007 <b>F</b> н | ITR           | Interrupt test register              | Not available |               |  |  |

- : Unused, X  $\,$  : Undefined

\* : No used in MB89F202RA/F202RAY

Note: Do not use prohibited areas.

## **Electrical Characteristics**

## 1. Absolute Maximum Ratings

| Parameter                              | Symbol          | Ra        | ting      | Unit | Remarks                                                                                           |

|----------------------------------------|-----------------|-----------|-----------|------|---------------------------------------------------------------------------------------------------|

| Farameter                              | Symbol          | Min       | Max       | Unit | itemaiks                                                                                          |

| Power supply voltage*                  | Vcc             | Vss - 0.3 | Vss + 6.0 | V    |                                                                                                   |

| Input voltage*                         | VI1             | Vss - 0.3 | Vcc + 0.3 | V    | Pins excluding RST, P60                                                                           |

| input voltage                          | V <sub>12</sub> | Vss - 0.3 | 12.25     | V    | For pins $\overline{RST}$ , P60                                                                   |

| Output voltage*                        | Vo              | Vss - 0.3 | Vcc + 6.0 | V    |                                                                                                   |

| "L" level maximum output current       | OL              | _         | 15        | mA   |                                                                                                   |

| "L" level average output current       | IOLAV1          | _         | 4         | mA   | Average value (operating<br>current × operating rate)<br>Pins excluding P40 to P43,<br>P70 to P72 |

|                                        | Iolav2          | _         | 12        | mA   | Average value (operating<br>current × operating rate)<br>Pins P40 to P43, P70 to P72              |

| "L" level total maximum output current | ΣΙΟL            |           | 100       | mA   |                                                                                                   |

| "H" level maximum output current       | Іон             |           | -10       | mA   | Pins excluding P60, P61                                                                           |

| "H" level average output current       | Юнач            | _         | -4        | mA   | Average value (operating current $\times$ operating rate)                                         |

| "H" level total maximum output current | ΣІон            | _         | -50       | mA   |                                                                                                   |

| Power consumption                      | Pd              | —         | 200       | mW   |                                                                                                   |

| Operating temperature                  | Та              | -40       | +85       | °C   |                                                                                                   |

| Storage temperature                    | Tstg            | -55       | +150      | °C   |                                                                                                   |

\* : This parameter is based on  $V_{SS} = 0.0 V$ .

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

## 2. Recommended Operating Conditions

(Vss = 0.0 V)

| Parameter                                 | arameter Symbol Value Unit |                          | Unit      | Remarks |                                                                                                                                                |

|-------------------------------------------|----------------------------|--------------------------|-----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Farameter                                 | Symbol                     | Min                      | Max       | Unit    | Remarks                                                                                                                                        |

|                                           |                            | 2.2                      | 5.5       | V       | MB89202/202Y                                                                                                                                   |

| Power supply voltage                      | Vcc                        | 3.5                      | 5.5       | V       | MB89F202RA/F202RAY                                                                                                                             |

| Fower supply voltage                      | VCC                        | 2.7                      | 5.5       | V       | MB89V201                                                                                                                                       |

|                                           |                            | 1.5                      | 5.5       | V       | Retains the RAM state in stop mode                                                                                                             |

|                                           | Vін                        | 0.7 Vcc                  | Vcc + 0.3 | V       | P00 to P07, P31, P37, P40 to P43, P50, P61,P70 to P72                                                                                          |

| "H" lovel input veltage                   | Vihs                       | 0.8 Vcc                  | Vcc + 0.3 | V       | EC, INT20 to INT27, UCK/SCK,<br>INT10 to INT12, P30, P32 to P36, UI/SI                                                                         |

| "H" level input voltage                   | Vінн                       | 0.7 Vcc                  | 12.25     | V       | P60. Under the normal operation, V <sub>IHH</sub> should not exceed Vcc + 0.3 V. Setting of V <sub>IHH</sub> > Vcc + 0.3 V is a reserved mode. |

|                                           | VIHHS                      | 0.8 Vcc                  | 12.25     | V       | RST*                                                                                                                                           |

| "L" level input voltage                   | VIL                        | Vss - 0.3                | 0.3 Vcc   | V       | P00 to P07, P31, P37, P40 to P43, P50,<br>P60, P61, P70 to P72                                                                                 |

|                                           | Vils                       | VILS VSS - 0.3 0.2 Vcc V |           | V       | RST, EC, INT20 to INT27, UCK/SCK,<br>INT10 to INT12, P30, P32 to P36, UI/SI                                                                    |

| Open-drain output pin application voltage | VD                         | Vss <b>-</b> 0.3         | Vcc + 0.3 | V       | P40 to P43, RST                                                                                                                                |

| Operating temperature                     | Та                         | -40                      | +85       | °C      | Room temperature is recommended<br>for programming the flash memory on<br>MB89F202RA/F202RAY                                                   |

\* : RST acts as high voltage supply for the flash memory during program and erase on MB89F202RA/F202RAY. It can tolerate high voltage input. Please check section "6. Flash Memory Program/Erase Characteristics".

# WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

## 3. DC Characteristics

| $(V_{cc} = 5.0 \text{ V} \pm 10\%)$ | , Vss = 0.0 V, Fсн = 12. | 5 MHz (External clock) | , Ta = $-40 ^{\circ}\text{C}$ to $+85 ^{\circ}\text{C}$ ) |

|-------------------------------------|--------------------------|------------------------|-----------------------------------------------------------|

| ( · · · · · – · · ·                 | ,                        |                        | ,                                                         |

|                                                    | Sym-  |                                                                                               | Value                |           |             |           |    |                                                                                                                                              |

|----------------------------------------------------|-------|-----------------------------------------------------------------------------------------------|----------------------|-----------|-------------|-----------|----|----------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                          | bol   | Pin name                                                                                      | Condition            | Min       | Min Typ Max |           |    | Remarks                                                                                                                                      |

|                                                    | Vih   | P00 to P07, P31, P37,<br>P40 to P43, P50, P61,<br>P70 to P72                                  |                      | 0.7 Vcc   | _           | Vcc + 0.3 | V  |                                                                                                                                              |

|                                                    | Vihs  | P30, P32 to P36,<br>UCK/SCK,UI/SI, EC,<br>INT20 to INT27,<br>INT10 to INT12                   | _                    | 0.8 Vcc   |             | Vcc + 0.3 | V  |                                                                                                                                              |

| "H" level input<br>voltage                         | Vінн  | P60                                                                                           |                      | 0.7 Vcc   |             | 12.25     | V  | Under the<br>normal<br>operation, VIHH<br>should not<br>exceed Vcc +<br>0.3 V. Setting<br>of VIHH > Vcc +<br>0.3 V is a<br>reserved<br>mode. |

|                                                    | VIHHS | RST                                                                                           | —                    | 0.8 Vcc   |             | 12.25     | V  |                                                                                                                                              |

|                                                    | VIL   | P00 to P07,<br>P31, P37, P40 to P43,<br>P50, P60, P61,<br>P70 to P72                          | _                    | Vss – 0.3 | _           | 0.3 Vcc   | V  |                                                                                                                                              |

| "L" level input<br>voltage                         | Vils  | P30, P32 to P36, RST,<br>UCK/SCK, UI/SI, EC,<br>INT20 to INT27,<br>INT10 to INT12             | _                    | Vss – 0.3 | _           | 0.2 Vcc   | V  |                                                                                                                                              |

| Open-drain<br>output pin<br>application<br>voltage | VD    | P40 to P43, RST                                                                               | _                    | Vss – 0.3 |             | Vcc + 0.3 | V  |                                                                                                                                              |

| "H" level<br>output voltage                        | Vон   | P00 to P07, P30 to P37,<br>P40 to P43, P50,<br>P70 to P72                                     | Iон = -4.0 mA        | 4.0       | _           | _         | V  |                                                                                                                                              |

| "L" level                                          | Vol1  | P00 to P07, P30 to P37,<br>P50, RST                                                           | lo∟ = 4.0 mA         | _         |             | 0.4       | V  |                                                                                                                                              |

| output voltage                                     | Vol2  | P40 to P43, P70 to P72                                                                        | lo∟ = 12.0 mA        | —         | _           | 0.4       | V  |                                                                                                                                              |

| Input leakage<br>current                           | lu    | P00 to P07, P30 to P37,<br>P40 to P43, P50 ,<br>P60, P61, RST,<br>P70 to P72                  | 0.45 V < Vi <<br>Vcc |           |             | ±5        | μΑ | Without<br>pull-up<br>resistor                                                                                                               |

| Pull-up<br>resistance                              | Rpull | P00 to P07, P30 to P37,<br>P50, RST, P70 to P72<br>P00 to P07, P30 to P37,<br>P50, P70 to P72 | $V_{1} = 0.0 V$      | 25        | 50          | 100       | kΩ | MB89202/<br>202Y<br>MB89F202RA/<br>F202RAY<br>(Continued)                                                                                    |

(Continued)

| Parameter            | Sym- |      | Pin name                                | Condition        |     | Value | 1   | Unit | Remarks                    |

|----------------------|------|------|-----------------------------------------|------------------|-----|-------|-----|------|----------------------------|

| Farameter            | bol  |      | Finname                                 | Condition        | Min | Тур   | Max | Unit | Remarks                    |

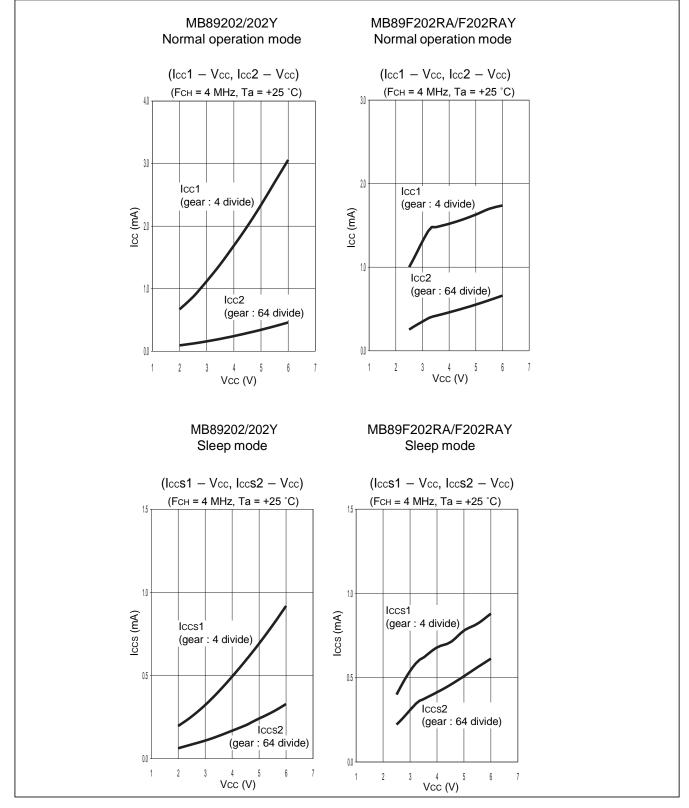

|                      |      |      | W/h or                                  | When A/D         | _   | 8     | 12  | mA   | MB89202/<br>202Y           |

|                      | Icc  |      | Normal operation mode                   | converter stops  | _   | 6     | 9   | mA   | MB89F202<br>RA/<br>F202RAY |

|                      | ICC  |      | (External clock,<br>highest gear speed) | When A/D         | _   | 10    | 15  | mA   | MB89202/<br>202Y           |

| Power supply         |      | Vcc  |                                         | converter starts | _   | 8     | 12  | mA   | MB89F202<br>RA/<br>F202RAY |

| current              |      | VCC  | Sleep mode                              | (External clock, | _   | 4     | 6   | mA   | MB89202/<br>202Y           |

|                      | Iccs |      | (External clock,<br>highest gear speed) |                  | _   | 3     | 5   | mA   | MB89F202<br>RA/<br>F202RAY |

|                      |      |      | Stop mode                               | When A/D         | _   | —     | 1   | μA   | MB89202/<br>202Y           |

|                      | Іссн |      | Ta = +25 °C<br>(External clock)         | converter stops  | _   | _     | 10  | μΑ   | MB89F202<br>RA/<br>F202RAY |

| Input<br>capacitance | CIN  | Othe | er than C, Vcc, Vss                     | —                | _   | 10    | _   | pF   |                            |

\* : RST acts as high voltage supply for the flash memory during program and erase on MB89F202RA/F202RAY. It can tolerate high voltage input. Please check section "6. Flash Memory Program/Erase Characteristics".

## 4. AC Characteristics

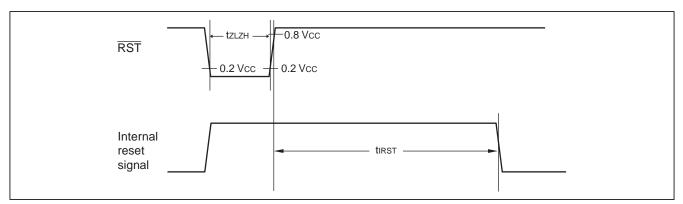

## (1) Reset Timing

(VSS = 0.0 V, Ta = -40 °C to +85 °C)

| Boromotor                      | Symbol Condition |   | Valu      | Unit |      |

|--------------------------------|------------------|---|-----------|------|------|

| Parameter                      |                  |   | Min       | Мах  | Unit |

| RST "L" pulse width            | <b>t</b> zlzh    | _ | 45        |      | ns   |

| Internal reset pulse extension | <b>t</b> IRST    | — | 48 thcyl* | _    | ns   |

\* : they 1 oscillating clock cycle time

Note: If the reset pulse applied to the external reset pin (RST) does not meet the specifications, it may cause malfunctions. Use caution so that the reset pulse less than the specifications will not be fed to the external reset pin (RST).

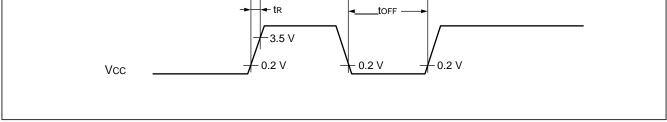

## (2) Power-on Reset

P F

|                           |        |            |       |        | (V   | ss = 0.0 V, Ta = −40 °C to +85 °C |

|---------------------------|--------|------------|-------|--------|------|-----------------------------------|

| Deremeter                 | Symbol | Condition  | Value |        | Unit | Remarks                           |

| Parameter                 | Symbol | Condition  | Min   | Max    | Unit | Reliidiks                         |

| Power supply rising time  | tR     |            |       | 50     | ms   |                                   |

| Power supply cut-off time | toff   | _          | 1     | _      | ms   | Due to repeated operations        |

|                           |        |            |       |        |      |                                   |

|                           |        | → + + + tR |       | tore — |      |                                   |

Note: : The supply voltage must be set to the minimum value required for operation within the prescribed default oscillation settling time.

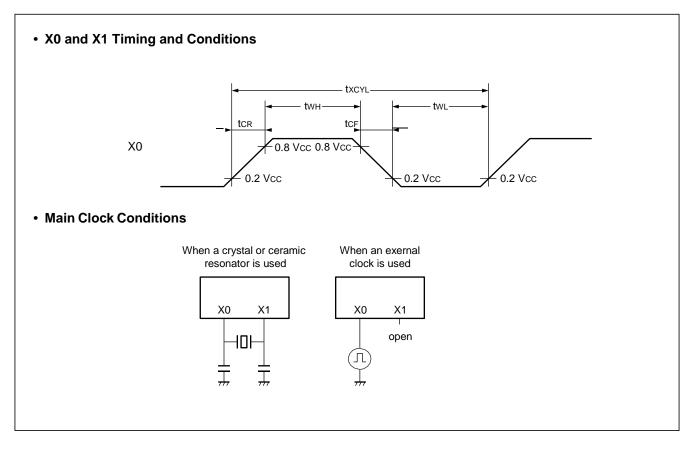

## (3) Clock Timing

|                                 |                  |           | (Vss = 0 | ).0 V, Ta = −40°C | to +85°C) |  |

|---------------------------------|------------------|-----------|----------|-------------------|-----------|--|

| Parameter                       | Symbol           | Condition | Va       | Unit              |           |  |

| Farameter                       | Symbol Condition |           | Min      | Мах               | Unit      |  |

| Clock frequency                 | Fсн              |           | 1        | 12.5              | MHz       |  |

| Clock cycle time                | <b>t</b> xcyL    |           | 80       | 1000              | ns        |  |

| Input clock pulse width         | twн<br>tw∟       |           | 20       | _                 | ns        |  |

| Input clock rising/falling time | tcr<br>tcr       |           | _        | 10                | ns        |  |

## (4) Instruction Cycle

| Parameter                                     | Symbol        | Value (typical)              | Unit | Remarks                                                                                          |

|-----------------------------------------------|---------------|------------------------------|------|--------------------------------------------------------------------------------------------------|

| Instruction cycle<br>(minimum execution time) | <b>t</b> INST | 4/Fсн, 8/Fсн, 16/Fсн, 64/Fсн |      | $t_{\text{INST}}=0.32~\mu s$ when operating at $F_{\text{CH}}=12.5~\text{MHz}~(4/F_{\text{CH}})$ |

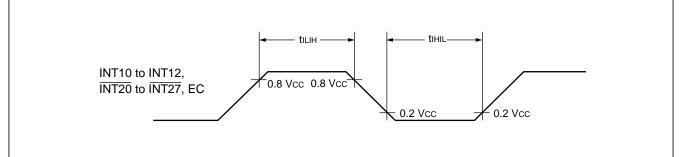

## (5) Peripheral Input Timing

$(V_{CC} = 5.0 \text{ V} \pm 10\%, \text{ Vss} = 0.0 \text{ V}, \text{ Ta} = -40 \text{ }^{\circ}\text{C} \text{ to } +85 \text{ }^{\circ}\text{C})$

| Parameter                        | Symbol | Pin name                | Va               | Unit |      |

|----------------------------------|--------|-------------------------|------------------|------|------|

|                                  |        |                         | Min              | Max  | Onic |

| Peripheral input "H" pulse width |        | I <u>NT10</u> to INT12, | 2 tinst*         | _    | μS   |

| Peripheral input "L" pulse width | tını∟  | INT20 to INT27, EC      | 2 <b>t</b> INST* |      | μS   |

\* : For information on tINST see " (4) Instruction Cycle".

$(V_{CC} = 5.0 \text{ V} \pm 10\%, \text{ Vss} = 0.0 \text{ V}, \text{ Ta} = -40 \text{ }^{\circ}\text{C} \text{ to } +85 \text{ }^{\circ}\text{C})$

| Parameter                        | Symbol | Pin name                                                                                 | Value |     |     | Unit |

|----------------------------------|--------|------------------------------------------------------------------------------------------|-------|-----|-----|------|

| Farameter                        |        | Finnanie                                                                                 | Min   | Тур | Max | Unit |

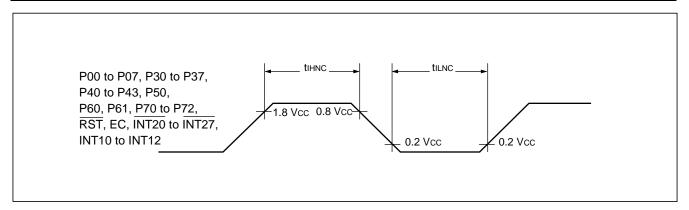

| Peripheral input "H" noise limit | tihnc  | P00 to P07, P30 to P37,                                                                  |       | 45  |     | ns   |

| Peripheral input "L" noise limit | tilnc  | P40 to P43,<br>P50,P60,P61,<br>P70 to P72, RST, EC,<br>INT20 to INT27,<br>INT10 to INT12 | _     | 45  | _   | ns   |

## (6) UART, Serial I/O Timing

|                                                   |        | (Vcc = 5    | .0 V <u>+</u> 10%, Vss       | = 0.0 V, Ta =           | = -40 °C to - | +85 °C) |

|---------------------------------------------------|--------|-------------|------------------------------|-------------------------|---------------|---------|

| Parameter                                         | Symbol | Pin name    | Condition                    | Value                   |               | Unit    |

| Falanetei                                         | Symbol | Finnanie    |                              | Min                     | Max           | Unit    |

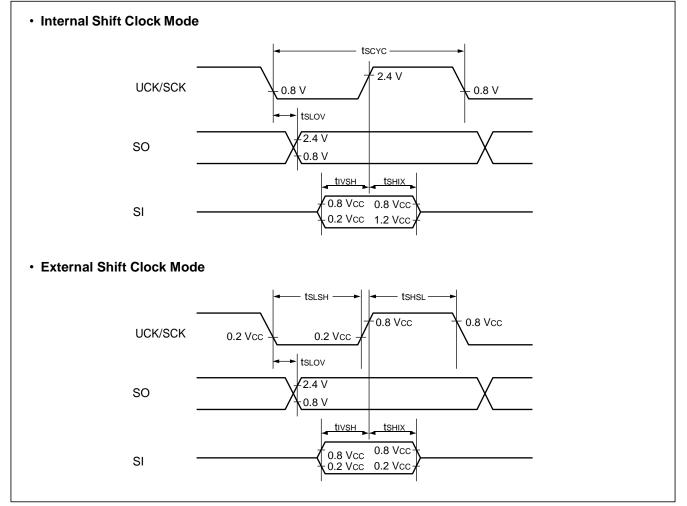

| Serial clock cycle time                           | tscyc  | UCK/SCK     | Internal shift<br>clock mode | 2 <b>t</b> INST*        | _             | μs      |

| UCK/SCK↓→SOtime                                   | tslov  | UCK/SCK, SO |                              | -200                    | + 200         | ns      |

| Valid SI $\rightarrow$ UCK/SCK $\uparrow$         | tıvsн  | UCK/SCK, SI |                              | 1/2 t <sub>INST</sub> * | _             | μs      |

| UCK/SCK $\uparrow \rightarrow$ Valid SI hold time | tsнix  | UCK/SCK, SI |                              | 1/2 tinst*              |               | μs      |

| Serial clock "H" pulse width                      | tsнs∟  | UCK/SCK     |                              | tinst*                  |               | μs      |

| Serial clock "L" pulse width                      | ts∟sн  | UCK/SCK     | External shift<br>clock mode | tinst*                  | _             | μs      |

| UCK/SCK↓→SOtime                                   | tslov  | UCK/SCK, SO |                              | 0                       | 200           | ns      |

| Valid SI $\rightarrow$ UCK/SCK                    | tıvsн  | UCK/SCK, SI |                              | 1/2 tinst*              |               | μs      |

| UCK/SCK $\uparrow \rightarrow$ Valid SI hold time | tsнix  | UCK/SCK, SI |                              | 1/2 tinst*              |               | μs      |

\* : For information on tinst, see "(4) Instruction Cycle".

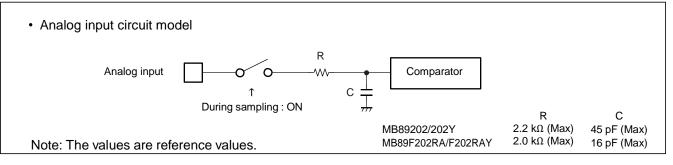

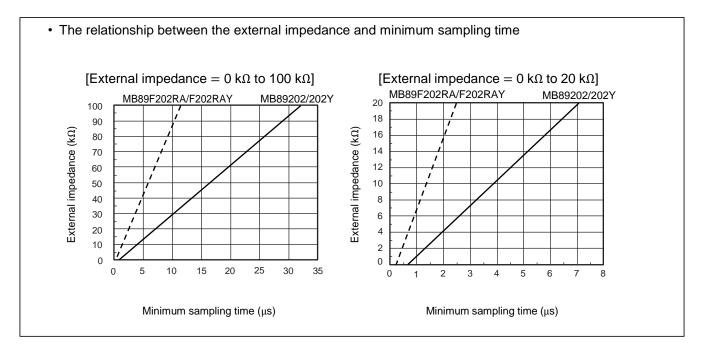

## 5. A/D Converter

#### (1) A/D Converter Electrical Characteristics

$(V_{ss} = 0.0 \text{ V}, \text{Ta} = -40 \text{ }^{\circ}\text{C} \text{ to } +85 \text{ }^{\circ}\text{C})$

| Parameter                                          | Symbol | Value         |               |               |      |

|----------------------------------------------------|--------|---------------|---------------|---------------|------|

| Farameter                                          | Symbol | Min           | Тур           | Мах           | Unit |

| Resolution                                         |        |               |               | 10            | bit  |

| Total error                                        |        | -5.0          |               | +5.0          | LSB  |

| Linearity error                                    |        | -3.0          | _             | +3.0          | LSB  |

| Differential linearity error                       |        | -2.5          | _             | +2.5          | LSB  |

| Zero transition voltage                            | Vот    | Vss – 3.5 LSB | Vss + 0.5 LSB | Vss + 4.5 LSB | V    |

| Full-scale transition voltage                      | Vfst   | Vcc - 6.5 LSB | Vcc – 1.5 LSB | Vcc + 2.0 LSB | V    |

| A/D mode conversion time                           | _      | _             | _             | 38 tinst*     | μs   |

| Analog port input current                          | lain   | _             | _             | 10            | μA   |

| Analog input voltage range                         | _      | 0             | _             | Vcc           | V    |

| Power supply voltage for<br>A/D accuracy assurance | Vcc    | 4.5           | _             | 5.5           | V    |

\* : For information on t<sub>inst</sub>, see " (4) Instruction Cycle" in "4. AC Characteristics."

## (2) A/D Converter Glossary

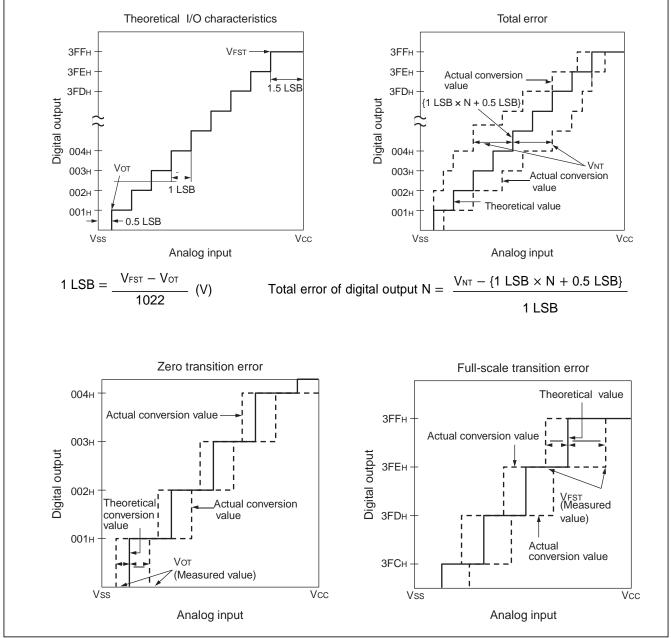

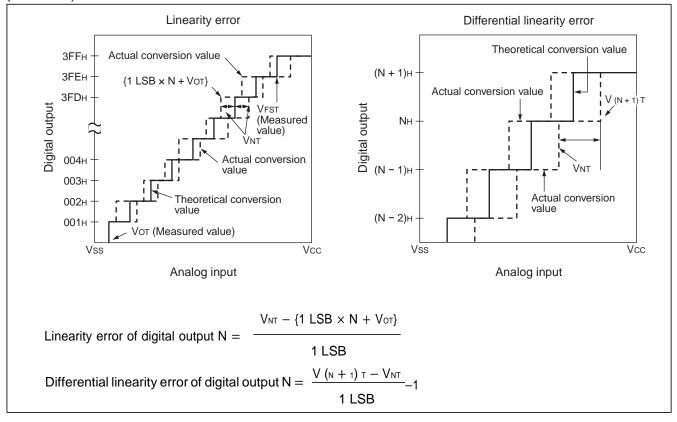

Resolution Analog changes that are identifiable with the A/D converter

When the number of bits is 10, analog voltage can be divided into  $2^{10} = 1024$ .