## S6BT112A01/S6BT112A02

# ASSP CXPI Transceiver IC for Automotive Network

The S6BT112A01 and S66BT112A02 are integrated transceiver ICs for automotive communication network with Clock Extension Peripheral Interface (CXPI). It has a flexible bit rate ranging from 2.4 Kbps to 20 Kbps and is JASO CXPI compliant. This CXPI transceiver IC connects the CXPI data link controller and the CXPI Bus line, and enables direct connection to the vehicle battery with a high surge protection. Additionally, these devices have an optional Spread Spectrum Clock Generator (SSCG) function.

During Sleep mode, S6BT112A01 and S6BT112A02 reduce power consumption. The Cypress CXPI transceiver IC supports master node and slave node as selected SELMS pins.

## Features

- Compliant with the JASO CXPI (JASO D 015-3-15) standard

- Compliant with the SAE CXPI ( J3076\_201510) standard

- ■Supports 2.4 Kbps to 20 Kbps bitrate

- ■Waveshaping for low Electromagnetic Interference (EMI)

- ■Operating voltage range: 5.3 V to 18 V

- Direct battery operation with protection against load dump, jump start, and transients

- ■BUS short to V<sub>BAT</sub> overcurrent protection.

- Loss of ground protection; BUS pin leakage is lower than ±1 mA.

- Easy selection of master node or slave node.

- ■Overtemperature protection

- ■Low-voltage detection.

- ■Supports Sleep and Wakeup modes

- ■Sleep mode current: 6 µA (typical at Slave)

- ■Halogen-free 8-pin SOIC package

- ESD protection HBM (1.5 kΩ, 100 pF) ±8 kV (BUS pin, BAT pin)

- ■Voltage tolerance ±40 V (BUS pin)

- S6BT112A01: With SSCG. S6BT112A02: Without SSCG.

198 Champion Court

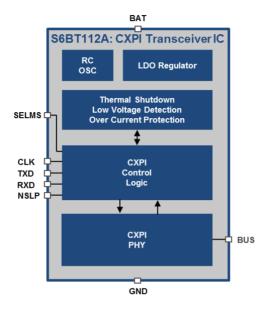

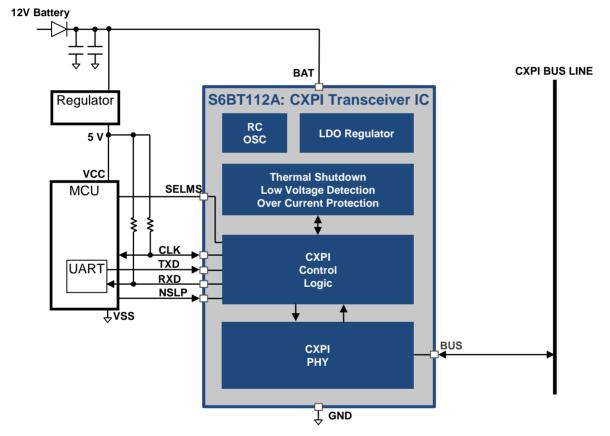

## S6BT112A Block Diagram

## **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| S6BT112A Block Diagram                  | 2  |

| 1. Applications                         | 4  |

| 2. Pin Assignment                       | 5  |

| 3. Pin Descriptions                     | 6  |

| 4. Block Diagram                        | 7  |

| 5. Function Description                 | 8  |

| 5.1 Operation Modes                     | 8  |

| 5.2 Master Node                         | 9  |

| 5.2.1 Normal Mode                       | q  |

| 5.2.2 Sleep Mode                        |    |

| 5.2.3 Standby Mode                      |    |

| 5.2.4 Power-on Sequence                 |    |

| 5.3 Slave Node                          |    |

| 5.3.1 Normal Mode                       | 12 |

| 5.3.2 Sleep Mode                        | 13 |

| 5.3.3 Standby Mode                      | 15 |

| 5.3.4 Power-on Sequence                 | 15 |

| 5.4 Common Functions                    | 16 |

| 5.4.1 Overtemperature Protection        | 16 |

| 5.4.2 WP_ThermalShutdown                | 16 |

| 5.4.3 Low-voltage Reset                 | 17 |

| 5.4.4 Overcurrent Protection            |    |

| 5.4.5 Secondary Clock Master            | 18 |

| 5.4.6 Arbitration                       | 20 |

| 5.4.7 TXD Toggle                        | 21 |

| 6. Absolute Maximum Ratings             | 23 |

| 7. Recommended Operating Conditions     | 24 |

| 8. Electrical Characteristics           | 25 |

| 9. Ordering Information                 | 36 |

| 10. Package Dimensions                  | 36 |

| Document History                        | 37 |

| Sales, Solutions, and Legal Information | 38 |

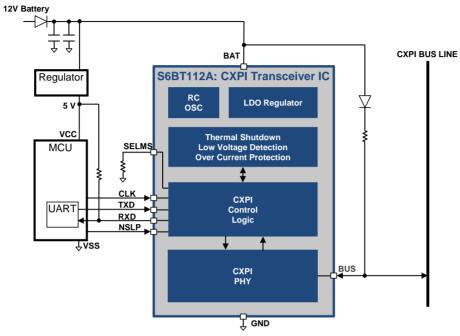

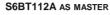

## 1. Applications

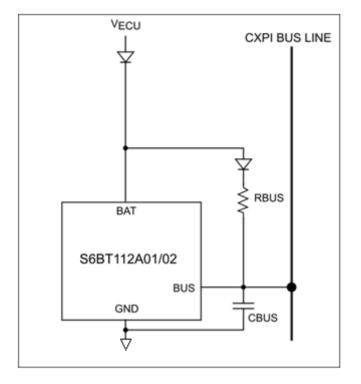

The following figures illustrate the typical applications of S6BT112A01 or S6BT112A02.

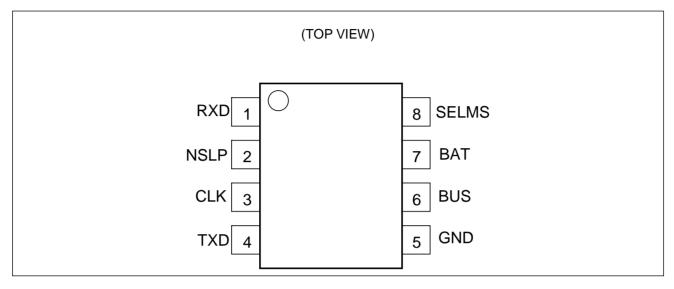

## 2. Pin Assignment

### Figure 2-1 Pin Assignment

## 3. Pin Descriptions

### **Table 3-1 Pin Descriptions**

| Pin<br>Number | Symbol | Direction | Description                                                           |  |

|---------------|--------|-----------|-----------------------------------------------------------------------|--|

| 1             | RXD    | Output    | Receive data output (open-drain).                                     |  |

|               |        |           | Requires external pull-up resistor. (refer to Table 7-1)              |  |

|               |        |           | Sleep control input.                                                  |  |

| 2             | NSLP   | Input     | Low: Sleep mode or Standby mode                                       |  |

| 2             | NOLF   | mput      | High: Normal mode.                                                    |  |

|               |        |           | Refer to section 5.2.2 or section 5.3.2                               |  |

|               |        |           | When the SELMS pin is Low, the CLK pin is the Baud rate clock input.  |  |

|               |        |           | Input clock signal with baud rate frequency.                          |  |

|               |        | I/O       | (When the input clock frequency is 20 kHz, the bit rate is 20 Kbps)   |  |

| 3             | CLK    |           | When the SELMS pin is High, the CLK pin is Baud rate clock output.    |  |

| 3             |        |           | Outputs clock signal with baud rate frequency.                        |  |

|               |        |           | (When the output clock frequency is 20 kHz , the bit rate is 20 Kbps) |  |

|               |        |           | Open drain output.                                                    |  |

|               |        |           | Requires external pull-up resistor. (refer to Table 7-1)              |  |

| 4             | TXD    | Input     | Transmit data input                                                   |  |

| 5             | GND    | -         | Ground                                                                |  |

| 6             | BUS    | I/O       | CXPI BUS line Input/Output                                            |  |

| 7             | BAT    | -         | Battery (voltage source) supply.                                      |  |

|               |        |           | Master / slave node select input.                                     |  |

| 8             | SELMS  | Input     | Low: Master                                                           |  |

|               |        |           | High: Slave                                                           |  |

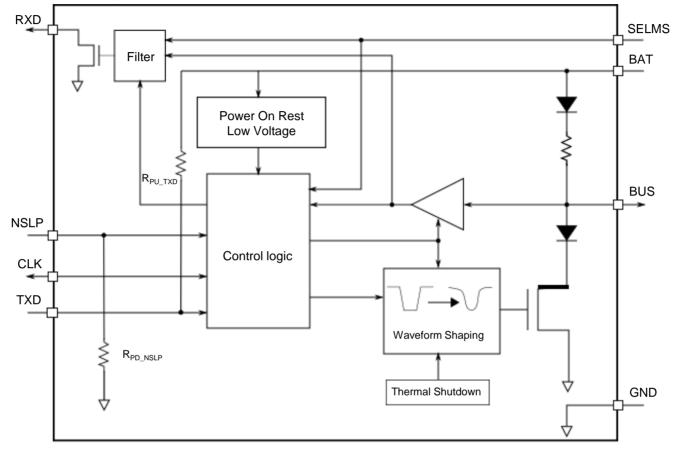

## 4. Block Diagram

## Figure 4-1 Block Diagram

## 5. Function Description

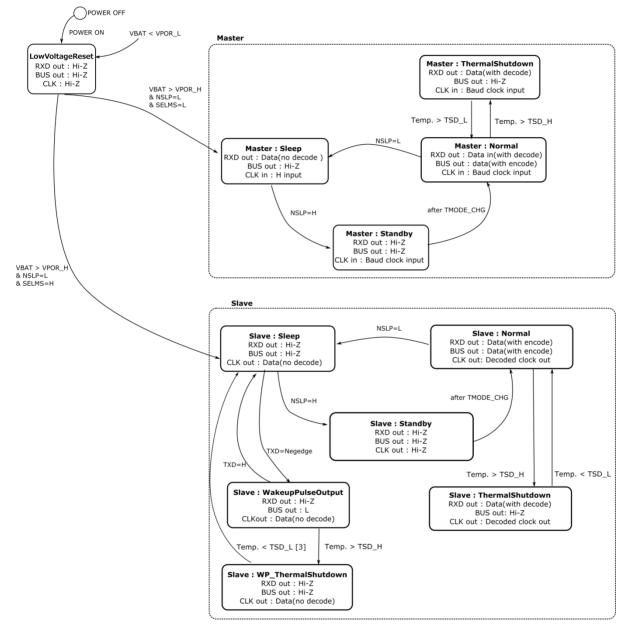

### 5.1 Operation Modes

#### Figure 5-1 State Transition Diagram

#### Notes

- [1] : "Hi-z" means high-impedance.

- [2] : Switching of the master / slave during operation is prohibited. Refer to section 5.4.5.

- [3] : The operation mode, after the transceiver powers on, has to start from sleep mode.

- [4] : If TXD is Low when releasing the thermal shutdown, TXD has to toggle "High" before valid. TXD is a Low signal input. For details, refer to section 5.4.7.

### 5.2 Master Node

There is only one node in a system, which functions as a schedule manager and a primary clock master.

The transceiver works in Master mode when low-level is applied on SELMS.

- The baud rate clock is applied on the CLK pin in the Master state.

- The transceiver is usually used as the "Master" or "Slave", except for the "Secondary Clock master function".

- The SELMS input should not be changed in normal mode.

- The SELMS input should not be changed during wakeup pulse transmission in Sleep mode.

- The CLK pin inputs for the baud rate clock in Master state.

#### Table 5-1 SELMS Pin State for Master

| Pin   | Input Signal | Master/Slave |

|-------|--------------|--------------|

| SELMS | Low          | Master       |

#### Figure 5-2 CLK Input -> BUS signal (Master)

| NSLP H  | - |

|---------|---|

| TXD H   | - |

| CLK(in) | - |

| BUS     | - |

#### 5.2.1 Normal Mode

The Normal mode denotes the state to which communication is possible. The master node transmits the clock to the CXPI BUS, which means that the clock is master. During the Normal mode, the transmitted signal is encoded and the received signal is decoded. When the transmitting node transmits data to the CXPI BUS, it transmits to the TXD pin after converting the data to UART format by 1 byte. The data is transmitted to the CXPI BUS as LSB first.

When the receiving node receives data from the CXPI BUS, it receives from the RXD pin in the UART format by 1 byte. The UART format is listed in Table 5-2. Refer to the JASO CXPI (JASO D 015-3:2015) standard for details of the operation.

### Table 5-2 UART Format

#### 5.2.2 Sleep Mode

The Sleep mode denotes a power-saving state during which each node stops transmitting and receiving data. All nodes transition to Sleep mode immediately after power-on. The nodes also transition to Sleep mode after the Sleep processing is executed from the Normal mode and transition from Standby mode or Normal mode due to CXPI BUS error.

When each node receives the Wakeup factor during the Sleep mode, it transitions to the Standby mode. The Wakeup factor (for example, detecting that the ignition has been turned on) of each node is different from each application (for example, detecting that the ignition has been turned on) and the external factor that receives the Wakeup pulse from the CXPI BUS. During the Sleep mode, the reception signal is received without decoding. The MCU can detect a wakeup pulse width monitor using the RXD signal.

The sleep mode is initiated by a falling edge on the NSLP pin while TXD is already set High. The CXPI BUS transmit path is immediately disabled when the NSLP pin goes Low. All wake-up events must be maintained for a specific period (refer to the  $T_{MODE\_CHG}$  parameter in Table 8-7).

#### Table 5-3 Transition from Normal to Sleep mode

| Pin   | Pin State      | Description                                |

|-------|----------------|--------------------------------------------|

| TXD   | High           | No data transmitting                       |

| CLK   | High           | No clock receiving                         |

| NSLP  | High to Low    | -                                          |

| RXD   | High impedance | High level with external pull-up resistor. |

| BUS   | High impedance | High level with external pull-up resistor. |

| SELMS | Low            | -                                          |

Note: The "Pin State" indicates before the falling edge in the NSLP pin

#### Table 5-4 Transition from Sleep to Normal mode

| Pin   | Pin State      | Description                                |

|-------|----------------|--------------------------------------------|

| TXD   | High           | No data transmitting                       |

| CLK   | High           | No clock receiving                         |

| NSLP  | Low to High    | -                                          |

| RXD   | High impedance | High level with external pull-up resistor. |

| BUS   | High impedance | High level with external pull-up resistor. |

| SELMS | Low            | -                                          |

**Note:** The "Pin State" indicates the state before the rising edge in the NSLP pin

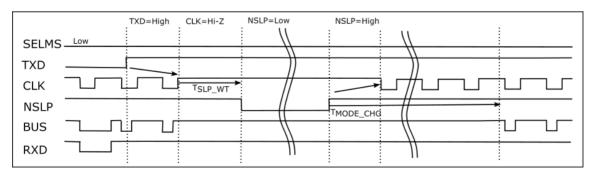

#### Figure 5-3 Transition Sequence Between Sleep and Normal Mode

#### Note:

[1] "Hi-Z" means high-impedance.

### Table 5-5 Bitrate of 20 Kbps (50 µs/Bit)

| UART Receive Data | Number of Bits of L Level | Wakeup Pulse Width |

|-------------------|---------------------------|--------------------|

| FCH               | 3-bit                     | 150 µs             |

| F8H               | 4-bit                     | 200 µs             |

| F0H               | 5-bit                     | 250 µs             |

| E0H               | 6-bit                     | 300 µs             |

| СОН               | 7-bit                     | 350 µs             |

| 80H               | 8-bit                     | 400 µs             |

| 00H               | 9-bit                     | 450 µs             |

#### 5.2.3 Standby Mode

The Standby mode denotes the prepared state to the Normal mode after releasing the Sleep mode. During the CLK state (in slave node), the RXD pin and the BUS pin are in a high-impedance state. After  $T_{MODE\_CHG}$ , the state changes to the Normal mode.

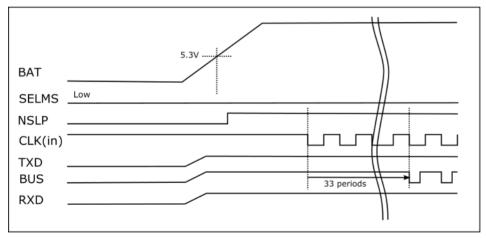

#### 5.2.4 Power-on Sequence

The power-on sequence occurs at power-up while setting up Sleep mode. When  $V_{BAT}$  is above 5.3 V, the NSLP pin should be in a High state. After transition to the normal mode, activate the BUS pin after a clock input of 33 periods.

#### Figure 5-4 Power-on Sequence of Master Node

### 5.3 Slave Node

All the nodes, except the master node, are connected with the system. The transceiver works as Slave when High level is applied on SELMS. The CLK pin outputs the baud rate clock during the Slave state.

The transceiver is usually used as the "Master" or "Slave", except for the "Secondary Clock master function".

#### Table 5-6 SELMS Pin State for Slave

| Pin   | Input Signal | Master/Slave |  |  |

|-------|--------------|--------------|--|--|

| SELMS | High         | Slave        |  |  |

The SELMS input should not be changed during the Normal mode or during wakeup pulse transmission in the Sleep mode. The CLK pin outputs the baud rate clock in Slave node.

#### Figure 5-5 CLK Pin Clock Output (Slave)

| SELMS       | High    |

|-------------|---------|

| NSLP<br>BUS | High —— |

|             |         |

|             |         |

#### 5.3.1 Normal Mode

The Normal mode can perform data transmit and receive. During the Normal mode, the signal that is transmitted is encoded and the signal that is received is decoded. When the transmitting node transmits data to the CXPI BUS, it transmits to the TXD pin after converting the data to UART format by 1 byte. The data is transmitted to the CXPI BUS by LSB first. When the receiving node receives data from the CXPI BUS, it revises from the RXD pin in the UART format by 1 byte. The UART format is shown in Table 5-7. Refer to the JASO CXPI (JASO D 015-3:2015) standard for details of the operation.

#### Table 5-7 UART Format

| Start bit | bit 0 (LSB) | bit 1 | bit 2 | bit 3 | bit 4 | bit 5 | bit 6 | bit 7(MSB) | Stop bit |

|-----------|-------------|-------|-------|-------|-------|-------|-------|------------|----------|

|-----------|-------------|-------|-------|-------|-------|-------|-------|------------|----------|

#### 5.3.2 Sleep Mode

The Sleep mode denotes a state of power saving during which each node stops transmit and receive of data. All nodes transition to the Sleep mode immediately after power-on. They also transition to the Sleep mode after the sleep processing is executed from the Normal mode and transition from the Standby mode or the Normal mode due to CXPI BUS error.

During the Sleep mode, when each node receives the Wakeup factor, it transitions to the Standby mode. The Wakeup factor is different from each application and is composed of the internal factor (for example, detecting that the ignition has been turned on) and the external factor that receives the Wakeup pulse from the CXPI BUS.

During the Sleep mode, the reception signal is received without decoding. The sleep mode is initiated by a falling edge on the NSLP pin while the TXD pin is already set High. The CXPI BUS transmit path is immediately disabled when the NSLP pin goes Low.

All wake-up events must be maintained for a specific period (refer to T<sub>MODE\_CHG</sub> in Table 8-7).

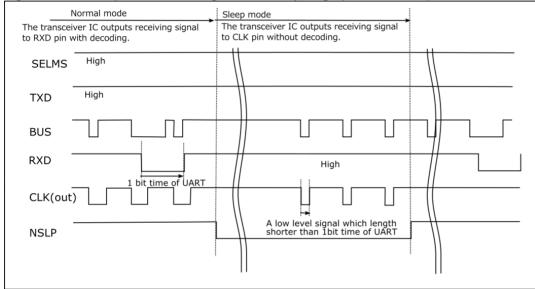

#### Figure 5-6 Transition Sequence Between Sleep and Normal Mode

|                | NSLP=Low | NSLP=High |

|----------------|----------|-----------|

| SELMS High     |          |           |

| TXD High       |          |           |

| ськ тот страни | × //     |           |

| NSLP           | <u> </u> |           |

| BUS            |          |           |

| RXD            | 1)       | <u> </u>  |

#### Table 5-8 Transition from Normal to Sleep mode

| Pin   | Pin State      | Description                                |

|-------|----------------|--------------------------------------------|

| TXD   | High           | No data transmitting                       |

| CLK   | High impedance | High level with external pull-up resistor. |

| NSLP  | High to Low    | -                                          |

| RXD   | High impedance | High level with external pull-up resistor. |

| BUS   | High impedance | High level with external pull-up resistor. |

| SELMS | High           | -                                          |

Note: The "Pin State" indicates the state before the falling edge of the NSLP pin.

Table 5-9 Transition from Sleep to Normal mode

| Pin   | Pin State      | Description                                |

|-------|----------------|--------------------------------------------|

| TXD   | High           | No data transmitting                       |

| CLK   | High impedance | High level with external pull-up resistor. |

| NSLP  | Low to High    | -                                          |

| RXD   | High impedance | High level with external pull-up resistor. |

| BUS   | High impedance | High level with external pull-up resistor. |

| SELMS | High           | -                                          |

Note: The "Pin State" indicates the state before the rising edge of the NSLP pin.

#### Receiver function in Sleep mode

During the Sleep mode, the received signal will be output from the CLK pin without decoding a received signal. The RXD pin outputs at High level. When the Master node transmits the encoded PWM clock signal to the CXPI BUS during a wake-up sequence, Slave MCUs receive shorter low-level width signals than the UART communication period and possibly get errors. This is because the Slave node is received without decoding. To avoid these errors, S6BT112A01 or S6BT112A02 CXPI transceiver IC outputs receive signals on the CLK pin in the Sleep mode.

MCU can detect a wake-up pulse width to monitor the CLK signal. (Figure 5-7)

### Figure 5-7 CLK Output of Receive Signal, RXD stays High (for Slave node)

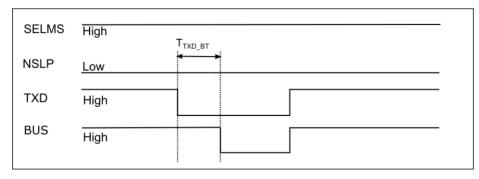

#### ■Wakeup function

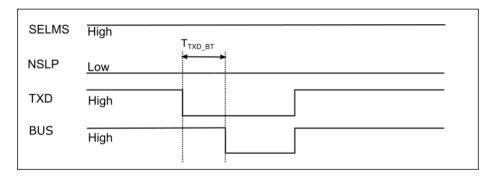

The WakeupPulseOutput state transmits out the wakeup pulse in the Slave node. When the slave device returns from the Sleep mode, it must transmit a wake-up pulse. As the NSLP pin is in a Low state, the TXD pin transmits a Low state. The TXD signal is transmitted to the BUS pin without encode. The TXD pin outputs the signal width, which is a value obtained by subtracting the T<sub>TXD\_BT</sub>:

Signal width = TXD signal ("L") – TTXD\_BT("L")

#### Figure 5-8 Wake-Up Pulse Transmission

#### 5.3.3 Standby Mode

This is the standby state during the Normal mode after releasing the Sleep mode. During this state, CLK (in slave node), the RXD pin, and the BUS pin enter the high-impedance state. After " $T_{MODE\_CHG}$ ," this state changes to the Normal mode.

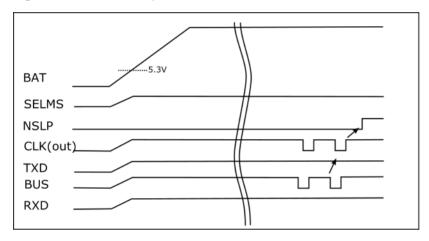

#### 5.3.4 Power-on Sequence

This sequence occurs at power-up, while setting up the Sleep mode. When  $V_{BAT}$  is above 5.3 V, the NSLP pin should be in a High state.

### Figure 5-9 Power-on Sequence of Slave Node

#### 5.4 Common Functions

#### 5.4.1 Overtemperature Protection

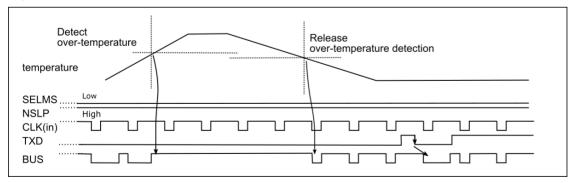

The overtemperature protection (OTP) monitors the die temperature. If the junction temperature exceeds the shutdown junction temperature,  $T_{SD_{-}H}$ , the thermal protection circuit disables the output driver.

The driver is enabled again when the junction temperature falls below T<sub>SD\_L</sub> and theTXD pin is toggled. (see Table 5-10)

#### 5.4.2 WP\_ThermalShutdown

The WP\_ThermalShutdown state detects the "shutdown temperature" during the WakeupPulseOutput mode. The overtemperature protection is inactive during the Sleep mode.

| Table 5-10 Input Signal Change after Recover | ry from thermal shutdown |

|----------------------------------------------|--------------------------|

|----------------------------------------------|--------------------------|

| Master/Slave | Pin | Toggle of Input Signal |

|--------------|-----|------------------------|

| Master       | TXD | Required               |

| Slave        | TXD | Required               |

#### Table 5-11 State Under Thermal Shutdown

| Master/Slave | Pin        | Description                                                       |

|--------------|------------|-------------------------------------------------------------------|

|              | TXD        | Normal function                                                   |

|              | NSLP       | High: Normal mode / Low: Sleep mode (Thermal protection inactive) |

| Master       | CLK(input) | Normal function                                                   |

|              | RXD        | Normal function                                                   |

|              | BUS        | High impedance                                                    |

|              | TXD        | Normal function                                                   |

|              | NSLP       | High: Normal mode / Low: Sleep mode (Thermal protection inactive) |

| Slave        | CLK        | Normal function                                                   |

|              | RXD        | Normal function                                                   |

|              | BUS        | High impedance                                                    |

#### Figure 5-10 Sequence of Thermal Shutdown

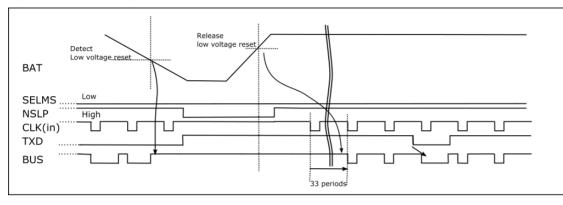

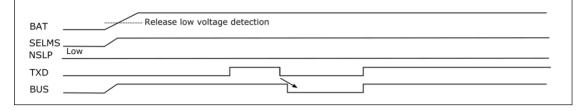

#### 5.4.3 Low-voltage Reset

The low-voltage reset state detects the low voltage of the BAT pin. This device has an integrated power-on reset and low-voltage detection at the supply BAT.

If the supply voltage, V<sub>BAT</sub>, is dropping below the power-on reset level (that is, V<sub>BAT</sub><V<sub>POR\_L</sub>), then change the LowPowerReset mode. In the LowPowerReset mode, the output stage is disabled and communication to the CXPI BUS is not possible.

If the power supply reaches a higher level than the low-voltage reset level, V<sub>BAT</sub>> V<sub>POR\_H</sub>, then change the Standby mode (the NSLP pin is High) or Sleep mode (the NSLP pin is Low).

After releasing LowPowerRest mode, enable the Power-up sequence.

#### Table 5-12 Input Signal Change after Recovery from Low Voltage Reset

| Master/Slave | Pin | Toggle of Input Signal |

|--------------|-----|------------------------|

| Master       | TXD | Required               |

| Slave        | TXD | Required               |

Table 5-13 State Under Low voltage Reset

| Master/Slave | Pin   | Description           |  |

|--------------|-------|-----------------------|--|

|              | SELMS | Reset                 |  |

|              | TXD   | Reset                 |  |

| Master       | NSLP  | Reset                 |  |

| Master       | CLK   | Reset(High impedance) |  |

|              | RXD   | High impedance        |  |

|              | BUS   | High impedance        |  |

|              | SELMS | Reset                 |  |

| Slave        | TXD   | Reset                 |  |

|              | NSLP  | Reset                 |  |

|              | CLK   | Reset(High impedance) |  |

|              | RXD   | High impedance        |  |

|              | BUS   | High impedance        |  |

#### Figure 5-11 Low-Voltage Detection

After releasing the low-voltage reset mode, the logical value high is output to the BUS pin after a clock input of 33 periods. The TXD data is valid from the falling edge on the TXD pin.

#### 5.4.4 Overcurrent Protection

The current in the transmitter output stage is limited to protect the transmitter against short-circuit to BAT or GND pins.

| Master/Slave | Pin  | Description                        |

|--------------|------|------------------------------------|

|              | TXD  | Normal function                    |

|              | NSLP | Normal function                    |

| Master       | CLK  | Normal function                    |

|              | RXD  | Normal function                    |

|              | BUS  | Output current limited by IBUS_LIM |

|              | TXD  | Normal function                    |

|              | NSLP | Normal function                    |

| Slave        | CLK  | Normal function                    |

|              | RXD  | Normal function                    |

|              | BUS  | Output current limited by IBUS_LIM |

#### Table 5-14 Overcurrent Protection

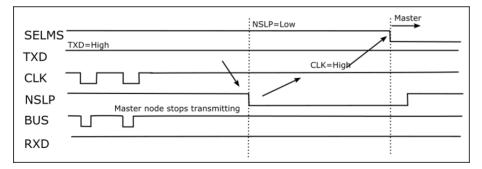

#### 5.4.5 Secondary Clock Master

The node that detects the wakeup event transmits the wakeup pulse on to the CXPI BUS. If the primary clock master cannot transmit the clock to the CXPI BUS due to failure, the wakeup pulse is retransmitted. If the clock is not transmitted to the CXPI BUS, each node detects the CXPI BUS error.

The secondary clock master may transmit the clock to the CXPI BUS instead of the primary clock master if it detects that the clock does not exist, and confirms that the clock does not exist on the CXPI BUS for the period during which it transitions from the Sleep mode

#### Operation sequence from master to slave

The TXD input pin is set High and the CLK pin is high-impedance. A Low setting on the NSLP pin initiates a transition to the Sleep mode. After the RXD pin is confirmed to High state, the SELMS pin goes to High state. Table 5-15 shows the pin states just before the SELMS pin input signal change.

### Table 5-15 Pin State Table (from Master to Slave)

| Pin   | Pin State      | Description                                |

|-------|----------------|--------------------------------------------|

| TXD   | High           | No data transmitting                       |

| CLK   | High impedance | High level with external pull-up resistor. |

| NSLP  | Low            | Sleep mode                                 |

| SELMS | Low to High    | -                                          |

| RXD   | High           | No data receiving                          |

| BUS   | High           | No wakeup signal receiving preferred       |

Figure 5-12 Application example Secondary Clock Master

#### S6BT112A AS SLAVE (SECONDARY CLOCK MASTER )

#### Figure 5-13 Transition Sequence from Master to Slave

| SELMS | TXD=High | CLK=Hi-Z            | NSLP=Low     | Slave   |

|-------|----------|---------------------|--------------|---------|

| тхр   |          |                     | /            |         |

| СГК   |          | T <sub>SLP_WT</sub> |              |         |

| NSLP  |          |                     | L/           |         |

| BUS   | Ļ        |                     | $\mathbf{X}$ |         |

| RXD   |          |                     | RXD=High     | <u></u> |

#### Operation sequence from slave to master

The TXD pin inputs high and the slave node transitions to the Sleep mode after the CLK pin was confirmed to High, and the SELMS pin goes to Low.

| Table 5-16 Pin State Table (from Slave to Master) |

|---------------------------------------------------|

|---------------------------------------------------|

| Pin   | Pin State      | Description                          |

|-------|----------------|--------------------------------------|

| TXD   | High           | No data transmitting                 |

| CLK   | High impedance | No wakeup signal receiving           |

| NSLP  | Low            | Sleep mode                           |

| SELMS | High to Low    | -                                    |

| RXD   | High           | -                                    |

| BUS   | High           | No wakeup signal receiving preferred |

Note: The pin states just before the SELMS input signal change.

Figure 5-14 Transition Sequence from Slave to Master

#### 5.4.6 Arbitration

Transceivers arbitrate bit-by-bit. Arbitration in bytes is done in the MCU.

In the Normal mode, each node always compares the received bit from the CXPI BUS with the transmitted bit to the CXPI BUS. When the value of the bit is corresponding, the node may continuously transmit to the CXPI BUS. When the value of the bit is not corresponding, the loss of arbitration is detected, and the transmission of the bit after that shall discontinue. If the transmitting node detects the arbitration loss, it behaves as the receiving node. The data of each bit transmitted on the CXPI BUS performs arbitration from the start by the bit. Moreover, arbitration is targeted at the entire field of the frame. When two or more nodes begin transmitting at the same time, by arbitration only the node that transmits the highest priority frame can complete the transmission.

The MCU compares between the transmitted data (TXD) and received data (RXD). If the data difference is detected, MCU has to stop data transmission until finding IFS.

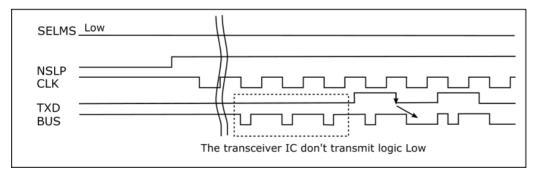

### 5.4.7 TXD Toggle

If the TXD pin is short to ground or open, the BUS pin output is not fixed Low (logic value). Therefore, it does not interfere with the communication of the other device.

An initial TXD dominant check prevents the bus line being driven to a permanent dominant state (blocking all network communications) if the TXD pin is forced permanently Low by a hardware and/or software application failure. The TXD input level is checked after a transition to the Normal mode.

If the TXD pin is Low, the transmit path remains disabled and is only enabled when the TXD pin goes High.

A TXD toggle is required in the following cases.

- Data transmission after recovery from low-voltage reset.

- Data transmission after recovery from thermal shutdown.

- □ First TXD data transmission in the Normal mode.

- □ First wake-up pulse transmission in sleep mode.

#### Short-circuit from the TXD pin to ground.(failure detect)

In the event of a short-circuit to ground or an open-wire on the TXD pin, the BUS pin output remains High (logical value '1') by this toggle function. In this case, by comparing the sent data to the TXD pin and received data from the RXD pin of the transceiver IC, the MCU can detect the permanent Low on the TXD pin by the data difference. In this case too, the receiver is active.

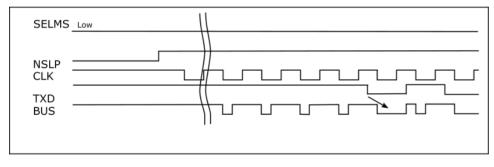

#### Figure 5-15 Normal Transmission Sequence of Master

#### Figure 5-16 TXD Toggle of Master after Transition to Normal mode

#### Figure 5-17 Slave TXD Toggle after Recovery from Low voltage State

## 6. Absolute Maximum Ratings

Semiconductor devices may be permanently damaged by application of stress (including, without limitation, voltage, current or temperature) in excess of absolute maximum ratings. Do not exceed any of these ratings.

| Deveryor             | Cumhal           | Conditions | Rat  | ting | Unit |

|----------------------|------------------|------------|------|------|------|

| Parameters           | Symbol           | Conditions | Min  | Max  | Unit |

| Power supply voltage | Vbat             | BAT pin    | -0.3 | 40   | V    |

|                      | VNSLP            | NSLP pin   | -0.3 | 6.9  | V    |

|                      | VSELMS           | SELMS pin  | -0.3 | 18   | V    |

| Input voltage        | Vclk             | CLK pin    | -0.3 | 6.9  | V    |

|                      | V <sub>TXD</sub> | TXD pin    | -0.3 | 6.9  | V    |

|                      | Vrxd             | RXD pin    | -0.3 | 6.9  | V    |

| Output voltage       | Vclk             | CLK pin    | -0.3 | 6.9  | V    |

| BUS pin voltage      | VBUS             | BUS pin    | -40  | 40   | V    |

| BUS pin ESD          | N                | DUO air    | -8   | 8    | kV   |

| (1.5 kΩ, 100 pF)     | Vesdbus          | BUS pin    | 0    | 0    |      |

| BAT pin ESD          | Vesdbat          | BAT pin    | -8   | 8    | kV   |

| (1.5 kΩ, 100 pF)     | VESUBAI          |            |      |      |      |

|                      |                  | NSLP pin   |      |      |      |

| ESD                  |                  | SELMS pin  |      |      |      |

|                      | Vesd             | CLK pin    | -2   | 2    | kV   |

| (1.5 kΩ, 100 pF)     |                  | TXD pin    |      |      |      |

|                      |                  | RXD pin    |      |      |      |

| Storage temperature  | T <sub>STG</sub> | -          | -55  | 150  | °C   |

| Maximum              | Тјмах            | -          | -40  | 150  | °C   |

| junction temperature | I JMAX           | -          | _    |      | -    |

## 7. Recommended Operating Conditions

### Table 7-1 Recommended condition

| Parameters                    | Symbol Conditions |                                  |     |      | Unit |      |

|-------------------------------|-------------------|----------------------------------|-----|------|------|------|

| Falameters                    | Symbol            | Conditions                       | Min | Тур  | Max  | Unit |

| Power supply voltage          | VBAT              | BAT pin [1]                      | 5.3 | -    | 18   | V    |

| Operating ambient temperature | T <sub>A</sub>    | -                                | -40 | +25  | +125 | °C   |

| BUS pin pull-up resistance    | Rmaster           | BUS pin (Master node : SELMS=0V) | 900 | 1000 | 1100 | Ω    |

| RXD pin pull-up resistance    | R <sub>RXD</sub>  | RXD pin                          | 2.4 | 10   | -    | kΩ   |

| CLK pin pull-up resistance    | R <sub>CLK</sub>  | CLK pin (SELMS=5V)               | 2.4 | 10   | -    | kΩ   |

#### Note

[1]: (18 V < V<sub>BAT</sub>  $\leq$  27 V) less than 2 minutes.

#### WARNING:

- 1. The recommended operating conditions are requiredir to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated under these conditions.

- 2. Any use of semiconductor devices will be under their recommended operating condition.

- 3. Operation under any conditions other than these conditions may adversely affect reliability of device and could result in device failure.

- 4. No warranty is made with respect to any use, operating conditions or combinations not represented on this data sheet. If you are considering application under any conditions other than listed herein, please contact sales representatives beforehand.

## 8. Electrical Characteristics

## **Table 8-1 DC Characteristics**

$V_{BAT}$  = 5.3 V~27 V<sup>[1]</sup>,  $T_A$  = -40~125 °C; All voltages are referenced to Pin 8 (GND); Positive currents flow into the IC; unless otherwise specified.

| Parameters                   | Symbol   | Pin<br>Name | Conditions                                                                              | Min | Тур | Max | Unit |

|------------------------------|----------|-------------|-----------------------------------------------------------------------------------------|-----|-----|-----|------|

|                              |          |             | Normal mode<br>TXD=5 V<br>CLK=20 kHz, Duty 50%                                          | -   | 1.4 | 2.9 | mA   |

|                              |          |             | Normal mode<br>TXD=0 V<br>CLK=20 kHz, Duty 50%                                          | -   | 2.0 | 4.0 | mA   |

|                              |          |             | Sleep mode<br>$V_{BAT} = 12 V$<br>TXD=5 V<br>SELMS=5 V<br>BUS= $V_{BAT}$<br>$T_A=25 °C$ | -   | 6   | -   | μΑ   |

| Power supply current         | Ibat     | BAT         | Sleep mode<br>$V_{BAT} = 12 V$<br>TXD=5 V<br>SELMS=0 V<br>BUS= $V_{BAT}$<br>$T_A=25 °C$ | -   | 16  | -   | μΑ   |

|                              |          |             | Sleep mode<br>V <sub>BAT</sub> =12 V<br>TXD=5 V<br>SELMS=5 V<br>BUS= V <sub>BAT</sub>   | -   | -   | 50  | μΑ   |

|                              |          |             | Sleep mode<br>V <sub>BAT</sub> =12 V<br>TXD=5 V<br>SELMS=0 V<br>BUS= V <sub>BAT</sub>   | -   | -   | 60  | μΑ   |

| BUS pin pull-up resistance   | RBUSpu   | BUS         | -                                                                                       | 20  | 30  | 47  | kΩ   |

| BUS short circuit<br>current | IBUS_LIM | BUS         | V <sub>BUS</sub> =18 V                                                                  | 40  | -   | 200 | mA   |

| Parameters                                        | Symbol                  | Pin<br>Name | Conditions                                                                   | Min                       | Тур | Max                       | Unit |

|---------------------------------------------------|-------------------------|-------------|------------------------------------------------------------------------------|---------------------------|-----|---------------------------|------|

| BUS input leak current<br>(HIGH)                  | BUS_PAS_rec             | BUS         | BUS=18 V<br>V <sub>BAT</sub> =5.3 V<br>TXD=5 V<br>T <sub>A</sub> =25 °C      | -                         | -   | 20                        | μΑ   |

| BUS input leak current<br>(LOW)                   | IBUS_PAS_dom            | BUS         | BUS=0 V<br>V <sub>BAT</sub> =12 V<br>TXD=5 V                                 | -1                        | -   | -                         | mA   |

| loss of ground BUS<br>leak current                | Ibus_no_gnd             | BUS         | V <sub>BAT</sub> =GND=18 V<br>BUS=0 V                                        | -1                        | -   | 1                         | mA   |

| loss of battery BUS<br>leak current               | I <sub>BUS_NO_BAT</sub> | BUS         | V <sub>BAT</sub> =0 V<br>BUS=18 V<br>T <sub>A</sub> =25 °C                   | -                         | -   | 30                        | μΑ   |

| BUS drop voltage                                  | VBUSDR                  | BUS         | V <sub>BAT</sub> =13.5 V<br>IBUSsource=-100 μA                               | 2.4                       | -   | 5.7                       | V    |

| BUS low level output                              | $V_{O\_dom}$            | BUS         | TXD=0 V<br>V <sub>BAT</sub> =7 V<br>BUS pull-up resistance=<br>$500 \Omega$  | -                         | -   | 1.4                       | V    |

| voltage                                           | Vo_dom                  | BUS         | TXD=0 V<br>V <sub>BAT</sub> =18 V<br>BUS pull-up resistance=<br>$500 \Omega$ | -                         | -   | 2                         | V    |

| Receiver low level threshold voltage              | VBUSdom                 | BUS         | Vват =12V, Та=25 °С                                                          | -                         | -   | 0.423<br>Vbat             | V    |

| Receiver high level threshold voltage             | V <sub>BUSrec</sub>     | BUS         | VBAT =12V, TA=25 °C                                                          | 0.556<br>V <sub>BAT</sub> | -   | -                         | V    |

| Receiver hysteresis voltage                       | V <sub>HYS</sub>        | BUS         | V <sub>BAT</sub> =12V, T <sub>A</sub> =25°C                                  | -                         | -   | 0.133<br>V <sub>BAT</sub> | V    |

| Low level power-on reset threshold voltage        | V <sub>POR_L</sub>      | BAT         | -                                                                            | 3.1                       | 3.8 | 4.7                       | V    |

| High level power-on<br>reset threshold<br>voltage | Vpor_h                  | BAT         | -                                                                            | 3.3                       | 4.1 | 4.9                       | V    |

| power-on reset<br>hysteresis voltage              | VPOR_HYS                | BAT         | -                                                                            | 0.2                       | 0.3 | 0.5                       | V    |

| Temperature shutdown threshold                    | T <sub>SD_H</sub>       | -           | [2]                                                                          | 156                       | 165 | 174                       | °C   |

| Temperature shutdown release threshold            | T <sub>SD_L</sub>       | -           | [2]                                                                          | 151                       | 159 | 168                       | °C   |

#### Notes

[1]: (18 V <  $V_{BAT} \le 27$  V) less than 2 minutes.

[2]: Guaranteed by design

## Table 8-2 DC Characteristics CLK Pin

(If SELMS = 5 V, this pin operates as Open Drain Output Pin. If SELMS = 0 V, this pin operates as an input pin)

$V_{BAT}$  = 5.3 V $\sim$ 27 V<sup>[1]</sup>, T<sub>A</sub> = -40 $\sim$ 125 °C; all voltages are referenced to Pin 8 (GND). **P**ositive current flow into the IC; unless otherwise specified.

| Parameters                        | Symbol   | Pin<br>Name | Conditions                | Min  | Тур | Max | Unit |

|-----------------------------------|----------|-------------|---------------------------|------|-----|-----|------|

| High level input voltage          | Vih_clk  | CLK         | SELMS = 0 V               | 2    | -   | 6   | V    |

| Low level input voltage           | Vil_clk  | CLK         | SELMS = 0 V               | -0.3 | -   | 0.8 | V    |

| Hysteresis range of input voltage | Vhys_clk | CLK         | SELMS = 0 V               | 0.03 | -   | 0.5 | V    |

| Low level output voltage          | Vol clk  | CLK         | I <sub>CLK</sub> = 2.2 mA | -    | -   | 0.6 | V    |

| Low level output voltage          |          |             | SELMS = 5 V               |      |     |     |      |

| Low level current                 | Iol_clk  | CLK         | SELMS = 5 V               | 1.3  | 3   | -   | mA   |

| High level leak current           | Iilh_clk | CLK         | SELMS = 5 V               | -3   | -   | 3   | μA   |

| Low level leak current            | lill_clk | CLK         | SELMS = 5 V               | -3   | -   | 3   | μA   |

#### Note

[1]: (18 V <  $V_{BAT} \le 27$  V) less than 2 minutes.

### Table 8-3 DC Characteristics NSLP Pin

$V_{BAT} = 5.3 \text{ V} \sim 27 \text{ V}^{[1]}$ ,  $T_A = -40 \sim 125 \text{ °C}$ ; all voltages are referenced to Pin 8 (GND). Positive current flow into the IC; unless otherwise specified.

| Parameters                        | Symbol                | Pin<br>Name | Conditions | Min  | Тур | Max | Unit |

|-----------------------------------|-----------------------|-------------|------------|------|-----|-----|------|

| High level input voltage          | $V_{\text{IH\_NSLP}}$ | NSLP        | -          | 2    | -   | 6   | V    |

| Low level input voltage           | VIL_NSLP              | NSLP        | -          | -0.3 | -   | 0.8 | V    |

| Hysteresis range of input voltage | V <sub>HYS_NSLP</sub> | NSLP        | -          | 0.03 | -   | 0.5 | V    |

| Internal pull-down resistance     | Rpd_nslp              | NSLP        | NSLP = 5 V | 100  | 250 | 650 | kΩ   |

| Low level leak current            | IILL_NSLP             | NSLP        | NSLP = 0 V | -3   | -   | 3   | μA   |

### Note

[1]: (18 V < V<sub>BAT</sub>  $\leq$  27 V) less than 2 minutes

## Table 8-4 TXD Pin

$V_{BAT}$  = 5.3 V~27 V<sup>[1]</sup>,  $T_A$  = -40~125 °C; all voltages are referenced to Pin 8 (GND). Positive current flow into the IC; unless otherwise specified.

| Parameters                        | Symbol              | Pin<br>Name | Conditions | Min  | Тур | Max | Unit |

|-----------------------------------|---------------------|-------------|------------|------|-----|-----|------|

| High level input voltage          | V <sub>IH_TXD</sub> | TXD         | -          | 2    | -   | 6   | V    |

| Low level input voltage           | VIL_TXD             | TXD         | -          | -0.3 | -   | 0.8 | V    |

| Hysteresis range of input voltage | Vhys_txd            | TXD         | -          | 0.03 | -   | 0.5 | V    |

| Internal pull-up resistance       | Rpu_txd             | TXD         | TXD = 0 V  | 50   | 125 | 325 | kΩ   |

| High level leak current           | Iilh_txd            | TXD         | TXD = 5 V  | -3   | -   | 3   | μA   |

#### Note

[1]: (18V <  $V_{BAT} \le 27V$ ) less than 2 minutes

## Table 8-5 SELMS Pin

$V_{BAT} = 5.3 \text{ V} \sim 27 \text{ V}^{[1]}$ ,  $T_A = -40 \sim 125 \text{ °C}$ ; all voltages are referenced to Pin 8 (GND). Positive current flow into the IC; unless otherwise specified.

| Parameters                        | Symbol     | Pin<br>Name | Conditions  | Min  | Тур | Max  | Unit |

|-----------------------------------|------------|-------------|-------------|------|-----|------|------|

| High level input voltage          | VIH_SELMS  | SELMS       | -           | 2    | -   | 6    | V    |

| Low level input voltage           | VIL_SELMS  | SELMS       | -           | -0.3 | -   | 0.8  | V    |

| Hysteresis range of input voltage | VHYS_SELMS | SELMS       | -           | 0.03 | -   | 0.5  | V    |

| Internal pull-up resistance       | Rpu_selms  | SELMS       | SELMS = 0 V | 200  | 500 | 1300 | kΩ   |

| High level leak current           | IILH_SELMS | SELMS       | SELMS = 5 V | -3   | -   | 3    | μA   |

#### Note

[1]: (18 V <  $V_{BAT} \le 27$  V) less than 2 minutes.

## Table 8-6 RXD Pin (Open Drain Output)

$V_{BAT} = 5.3 \text{ V} \sim 27 \text{ V}^{[1]}$ ,  $T_A = -40 \sim 125 \text{ °C}$ ; all voltages are referenced to Pin 8 (GND). Positive current flow into the IC; unless otherwise specified.

| Parameters               | Symbol   | Pin Name | Conditions                 | Min | Тур | Max | Unit |

|--------------------------|----------|----------|----------------------------|-----|-----|-----|------|

| Low level output voltage | Vol_rxd  | RXD      | $I_{RXD} = 2.2 \text{ mA}$ | -   | -   | 0.6 | V    |

| Low level current        | IOL_RXD  | RXD      | RXD = 0.4 V                | 1.3 | 3   | -   | mA   |

| High level leak current  | Iolh_rxd | RXD      | RXD = 5 V                  | -3  | -   | 3   | μA   |

| Low level leak current   | Ioll_rxd | RXD      | RXD = 0 V                  | -3  | -   | 3   | μA   |

#### Note

[1]: (18 V < V<sub>BAT</sub> $\leq$  27 V) less than 2 minutes.

### **Table 8-7 AC Characteristics**

$V_{BAT}$  = 5.3 V~27 V<sup>[1]</sup>, T<sub>A</sub> = -40~125 °C BUS Load 1 k $\Omega$  /1 nF; unless otherwise specified.

| Parameters                                                       | Symbol              | Pin<br>Name | Conditions                                                                                                                         | Min | Тур | Max | Unit                |

|------------------------------------------------------------------|---------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------------|

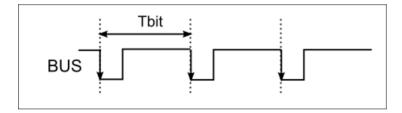

| Bitrate                                                          | T <sub>BUAD</sub>   | BUS         | $V_{TH}(bus)^{[3]} = 0.5 V_{BAT}$                                                                                                  | 2.4 | -   | 20  | kbps                |

| Mode transition time<br>(Sleep to Normal or<br>Normal to Sleep.) | Tmode_chg           | NSLP        | V <sub>TH</sub> (5v) <sup>[4]</sup> = 50%                                                                                          | -   | -   | 1   | ms                  |

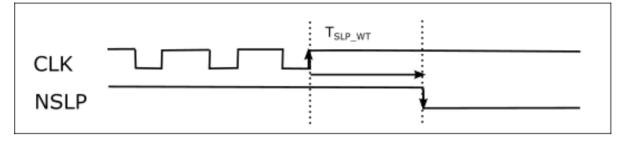

| NSLP wait time                                                   | T <sub>SLP_WT</sub> | CLK<br>NSLP | V <sub>TH</sub> (5 V) <sup>[4]</sup> = 50%                                                                                         | 100 | -   | -   | μs                  |

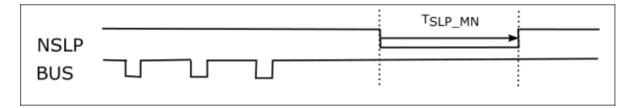

| Minimum sleep time                                               | T <sub>SLP_MN</sub> | NSLP        | -                                                                                                                                  | 1   | -   | -   | ms                  |

| Driver boot time under sleep mode. <sup>[2]</sup>                | T <sub>txd_bt</sub> | TXD         | NLSP = 0 V<br>SELMS = 5 V<br>V <sub>TH</sub> (5v) <sup>[4]</sup> =50%<br>V <sub>TH</sub> (bus) <sup>[3]</sup> =0.3V <sub>BAT</sub> | -   | -   | 195 | μs                  |

| CLK transmission delay<br>time                                   | T <sub>CLK_PD</sub> | CLK         | NLSP = 5 V<br>SELMS = 0 V<br>CLK=input clock<br>TXD=5 V<br>$V_{TH}(5v)^{[4]}=50\%$<br>$V_{TH}(bus)^{[3]}=0.3V_{BAT}$               | -   | -   | 0.9 | Tbit <sup>[5]</sup> |

| Parameters                                           | Symbol                        | Pin<br>Name | Conditions                                                                                                | Min                                   | Тур | Max             | Unit |

|------------------------------------------------------|-------------------------------|-------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------|-----|-----------------|------|

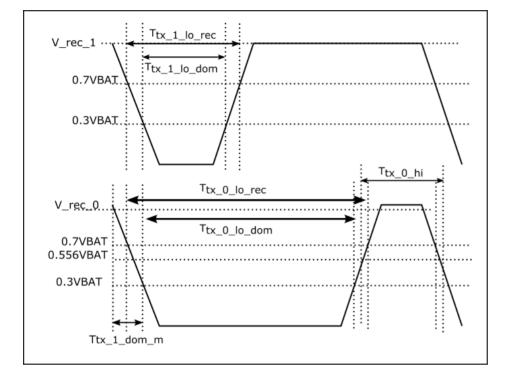

| Time of Low level of<br>logic value '1'              | T <sub>tx_1_lo_rec</sub>      | BUS         | NLSP = 5 V<br>SELMS = 0 V<br>CLK=input clock<br>TXD=5 V<br>VTH(bus) <sup>[3]</sup> = 0.7V <sub>BAT</sub>  | -                                     | -   | 0.39Tbit<br>+6т | -    |

| Time of Low level of<br>logic value '1'              | Ttx_1_lo_dom                  | BUS         | NLSP = 5 V<br>SELMS = 0 V<br>CLK=input clock<br>TXD=5 V<br>VTH(bus) <sup>[3]</sup> = 0.3 V <sub>BAT</sub> | 0.11                                  | -   | -               | Tbit |

| Time of Low level of<br>logic value '0'              | T <sub>tx_0_lo_rec</sub>      | BUS         | NLSP = 5 V<br>TXD = 0 V<br>V <sub>TH</sub> (bus) <sup>[3]</sup> = 0.7 V <sub>BAT</sub>                    | T <sub>tx_1_lo_rec</sub><br>+0.06Tbit | -   | -               | -    |

| Time of Low level of<br>logic value '0'              | Ttx_0_lo_dom                  | BUS         | NLSP = 5 V<br>TXD=0 V<br>V <sub>TH</sub> (bus) <sup>[3]</sup> = 0.3 V <sub>BAT</sub>                      | T <sub>tx_1_lo_dom</sub><br>+0.06Tbit | -   | -               | -    |

| High level time at receiving node.                   | T <sub>tx_0_hi</sub>          | BUS         | NLSP = 5 V<br>TXD = 0 V<br>$V_{TH}(bus)^{[3]} = 0.556$<br>$V_{BAT}$                                       | 0.06                                  | -   | -               | Tbit |

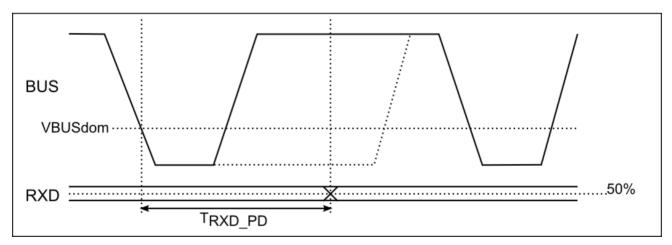

| Receiver delay time                                  | T <sub>RXD_PD</sub>           | RXD         | NSLP = 5 V<br>V <sub>TH</sub> (bus) <sup>[3]</sup> =<br>VBUSdom                                           | -                                     | -   | 2.4             | Tbit |

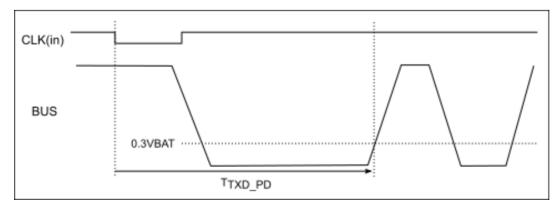

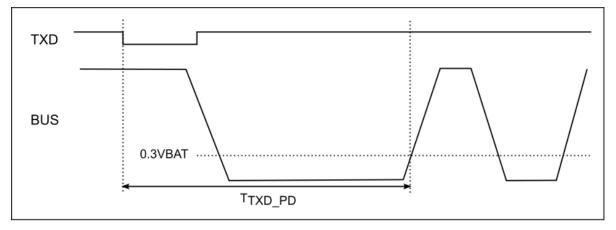

| Delay time of<br>transmission if logic<br>value '0'. | T <sub>TXD_PD</sub>           | TXD         | NSLP = 5 V<br>V <sub>TH</sub> (bus) <sup>[3]</sup> =0.3 V <sub>BAT</sub>                                  | -                                     | -   | 3.3             | Tbit |

| Input clock duty                                     | Ticlk_dy                      | CLK         | SELMS = 0 V<br>VTH(5 V) <sup>[4]</sup> = 50%                                                              | 30                                    | -   | 70              | %    |

| Output clock duty <sup>[6]</sup>                     | T <sub>oclk_dy</sub>          | CLK         | SELMS = 5 V<br>Vтн(5 V) <sup>[4]</sup> = 50%                                                              | 14                                    | -   | 50              | %    |

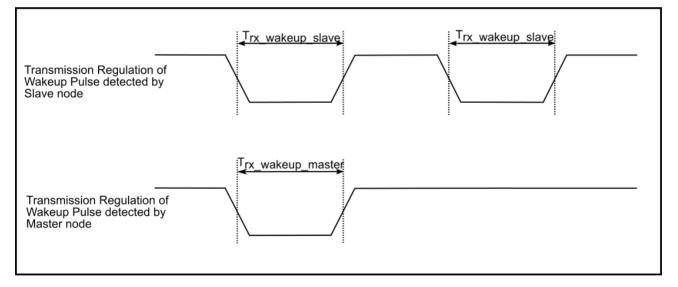

| Wakeup pulse filter<br>constant(Master)              | T <sub>rx_wakeup_master</sub> | BUS         | NSLP = 0 V<br>SELMS = 0 V<br>V <sub>TH</sub> (bus) <sup>[3]</sup> =42.3%                                  | 30                                    | -   | 150             | μs   |

\_\_\_\_\_

| Parameters                             | Symbol           | Pin<br>Name | Conditions                                                                                    | Min  | Тур | Мах  | Unit    |

|----------------------------------------|------------------|-------------|-----------------------------------------------------------------------------------------------|------|-----|------|---------|

| Wakeup pulse filter<br>constant(Slave) | Trx_wakeup_slave | BUS         | NSLP = 0 V<br>SELMS = 5 V<br>V <sub>TH</sub> (bus) <sup>[3]</sup> = 42.3%                     | 0.5  | -   | 5    | μs      |

| Time of bus slope from minimum         | Ttx_1_dom_m      | BUS         | NSLP = 5 V<br>SELMS = 0 V<br>$V_{BAT} = 7V$<br>VTH(bus) <sup>[3]</sup> = 0.3 V <sub>BAT</sub> | -    | -   | 0.16 | Tbit    |

| Recessive level of logical value '0'.  | V_rec_0          | BUS         | NSLP = 5 V                                                                                    | 0.93 | -   | -    | V_rec_1 |

#### Notes

[1]: (18 V < V<sub>BAT</sub>  $\leq$  27 V) less than 2 minutes RXD pin load: 20 pF

[2]: CXPI BUS load (Figure 8-11) : 10 nF/500 Ω

[3]: V<sub>TH</sub>(bus) : threshold of BUS pin

[4]:  $V_{TH}(5v)$  : threshold of NSLP,CLK,TXD,SELMS,RXD pins.

[5]: Tbit stands for 1bit time.(Figure 8-1)

[6]: logic '0/1' threshold clock

## Figure 8-1 Definition of Tbit

## Figure 8-2 Mode Transition Time

| NSLP |                |

|------|----------------|

| BUS  | High level     |

| RXD  | <br>High level |

|      |                |

## Figure 8-3 NSLP Wait Time

## Figure 8-4 Minimum Sleep Time

## Figure 8-5 Driver boot Time Under Sleep Mode

## Figure 8-6 CLK Transmission Delay Time

Figure 8-7 Logic low and high CXPI BUS Waveform

Figure 8-8 Receiver Delay Time

Figure 8-9 Logic low Transmission Delay Time

## Figure 8-10 Wakeup Pulse Waveform

## Figure 8-11 CXPI BUS Load Connection

## 9. Ordering Information

| Part Number       | Package                                   |

|-------------------|-------------------------------------------|

| S6BT112A01SSBB002 | 8-pin 150-mil SOIC Tape and Reel (SOA008) |

| S6BT112A02SSBB002 | 8-pin 150-mil SOIC Tape and Reel (SOA008) |

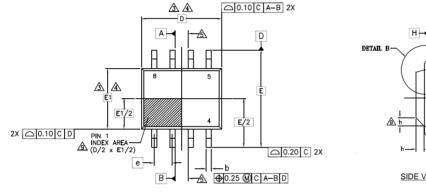

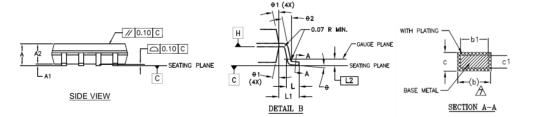

## **10. Package Dimensions**

| Package Type | Package Code |

|--------------|--------------|

| SOP 8        | SOA 008      |

TOP VIEW

SIDE VIEW

| PACKAGE         | SOA 008(MM) |      | SOA 008(INCHES) |       |

|-----------------|-------------|------|-----------------|-------|

| JEDEC           | MS-012(F)AA |      | MS-012(F)AA     |       |

| SYMBOL          | MIN MAX     |      | MIN             | MAX   |

| A               | -           | 1.75 | -               | 0.069 |

| A1              | 0.10        | 0.25 | 0.004           | 0.010 |

| A2              | 1.32        | -    | 0.052           | -     |

| b               | 0.31        | 0.51 | 0.012           | 0.020 |

| b1              | 0.28        | 0.48 | 0.011           | 0.019 |

| с               | 0.17        | 0.25 | 0.007           | 0.010 |

| c1              | 0.17        | 0.23 | 0.007           | 0.009 |

| D               | 4.90 BSC    |      | 0.193 BSC       |       |

| E               | 6.00 BSC    |      | 0.236 BSC       |       |

| E1              | 3.90 BSC    |      | 0.153 BSC       |       |

| e               | 1.27 BSC    |      | 0.050 BSC       |       |

| L               | 0.40        | 0.89 | 0.016           | 0.035 |

| L1              | 1.04 REF    |      | 0.041 REF       |       |

| L2              | 0.25 BSC    |      | 0.010 BSC       |       |

| N               | 8           |      | 8               |       |

| h               | 0.25        | 0.50 | 0.10            | 0.196 |

| 0-              | 0°          | 8°   | 0°              | 8°    |

| <del>0</del> -1 | 5°          | 15°  | 5°              | 15°   |

| 0-2             | 0° REF      |      | 0° REF          |       |

- 1. ALL DIMENSIONS ARE IN MILLIMETERS (INCHES ARE FOR REFERENCE ONLY).

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M 1994.

- INTERLEAD FLASH OR PROTEUSION SHALL NOT EXCEED 0.25 mm PER SIDE D AND E1 DIMENSIONS ARE DETERMINED AT DATUM H. THE FACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM. DIMENSIONS D AND E1 ARE DETERMINED AT THE OUTMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, THE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY. DATUMS A AND B TO BE DETERMINED AT DATUM H.

- "N" IS THE MAXIMUM NUMBER OF TERMINAL POSITIONS FOR THE SPECIFIED PACKAGE LENGTH.

- 6. ∕A ∕® TN' IS THE MAXIMUM NUMBER OF TERMINAL POSITIONS FOR THE SPECIFIED PACKAGE LENGTH.

ATHE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 TO 0.25 mm FROM THE LEAD TIP.

DIMENSION 'b' DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWER LEAMBAR PROTRUSION SHALL BE 0.10 mm TOTAL

IN EXCESS OF THE 'b' DIMENSION AT MAXIMUM MATERIAL CONDITION. THE DAMBAR CANNOT BE LOCATED ON THE

LOWER RADIUS OF THE LEAD FOOT.

MIST BE LOCATED WITHIN THE INDEX AREA INDICATED.

LEAD COPLANARITY SHALL BE WITHIN 0.10 mm AS MEASURED FROM THE SEATING PLANE.

F16-038.3 \*I

## **Document History**

## Document Title: S6BT112A01/S6BT112A02 ASSP CXPI Transceiver IC for Automotive Network

## Document Number: 002-10203

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 5046456 | AKFU               | 12/11/2015         | Initial release<br>New Spec.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| *A       | 5208207 | AKFU               | 04/06/2016         | Revised the sentence style of the cover page<br>Changed all section 5 for easy to understand.<br>Changed figure of application.<br>Changed Figure 4-1 and Figure 5-1.<br>Removed "Driver recovery time when over-temperature detection is released."                                                                                                                                                                                                     |

| *В       | 5528948 | AKFU               | 11/24/2016         | Changed figure of application.<br>Changed Figure 4-1 Block Diagram<br>Changed Figure 5-12 Application example Secondary clock master<br>Added the conditions of V <sub>BUSdom</sub> /V <sub>BUSrec</sub> / V <sub>HYS</sub> /T <sub>tx_1_dom_m</sub> .<br>Removed the prameter of Receiver center level voltage (V <sub>BUS_CNT</sub> ).<br>Changed Figure 8-11 CXPI BUS Load Connection<br>Changed Ordering Information.<br>Changed Package Dimensions. |

| *C       | 5547736 | AKFU               | 12/09/2016         | Updated Introduction.<br>Updated Note [3] (Page 8).<br>Updated 5.2 Master Node.<br>Updated 5.2.2 Sleep Mode.                                                                                                                                                                                                                                                                                                                                             |

| *D       | 5757034 | AKFU               | 06/20/2017         | Changed figure of 1. Applications<br>Changed Figure 5-12 Application example Secondary Clock Master                                                                                                                                                                                                                                                                                                                                                      |

## Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless/RF                                           | cypress.com/wireless   |

#### **PSoC®** Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

**Technical Support**

cypress.com/support

All other trademarks or registered trademarks referenced herein are the property of their respective owners

© Cypress Semiconductor Corporation, 2015-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware product. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Interface - Specialised category:

Click to view products by Cypress manufacturer:

Other Similar products are found below :

CY7C910-51LMB MEC1632-AUE RKSAS4 HMC677G32 LPC47N207-JV FTP-637DSL633R SM712GX04LF04-BA MCW1001A-I/SS HOA6241-001 SC74HC4066ADTR2G NCN5120MNTWG NCN5150DR2G NCN8025MTTBG C100N50Z4A DG407AK/883B SRT2-ATT01 TDA8035HN/C1/S1J LTC1694CS5#TRMPBF DS90UB947TRGCRQ1 SP510ECF-L NCS2300MUTAG ADG1404YCPZ-REEL HMC677LP5E HMC677LP5ETR LTC1756EGN#PBF LTC1955EUH#PBF LT3669EUFD-2#PBF LTC6820HMS#3ZZTRPBF MXL1543BCAI MAX3170CAI+ XL1192D KTU1109EFAA-TR CH368L CH7307C-DEF LTC1694-1IS5#TRMPBF LTC1694CS5#TRPBF LTC1694IS5#TRM LTS 25-NP 73S8024RN-20IMF 73S8024RN-IL/F DS2413P+ DS2413P+T&R DS28E17Q+ DS8113-RNG+ MAX13036ATI+ MAX13174ECAG+ MAX216CWN+ MAX3172CAI+ AS8222-HSSM MAX6618AUB+