# **OLED DISPLAY MODULE**

**Application Notes**

| PRODUCT<br>NUMBER | DD-9664FC-2A with EVK board |

|-------------------|-----------------------------|

|-------------------|-----------------------------|

## TABLE OF CONTENTS

| 1 | EVK SCHEMATIC                        | 4 |

|---|--------------------------------------|---|

| 2 | SYMBOL DEFINITION                    | 5 |

|   | TIMING CHARACTERISTICS               |   |

| 4 | CONNECTION BETWEEN OLED AND EVK      | 9 |

| 5 | MODULE POWER UP SEQUENCE             |   |

|   | 5.1 POWER DOWN AND POWER UP SEQUENCE |   |

| 6 | HOW TO USE THE DD-9664FC-2A          |   |

| 7 | HOW TO USE THE DD-9664FC-2A          |   |

|   | 7.1 RECOMMENDED INITIAL CODE         |   |

| Product No  | DD-9664FC-2A | REV. A | ] | Dago | 2/15 |

|-------------|--------------|--------|---|------|------|

| Floduct No. |              |        |   | Page | 2/13 |

#### **REVISION RECORD**

| Rev. | Date                         | Page | Chapt. | Comment     | ECR no. |

|------|------------------------------|------|--------|-------------|---------|

| А    | 14 <sup>th</sup> Sep<br>2007 |      |        | First Issue |         |

|      |                              |      |        |             |         |

|      |                              |      |        |             |         |

|      |                              |      |        |             |         |

|      |                              |      |        |             |         |

|      |                              |      |        |             |         |

|      |                              |      |        |             |         |

|      |                              |      |        |             |         |

| Product No  | DD-9664FC-2A | REV. A | Daga | 2/15 |

|-------------|--------------|--------|------|------|

| Product No. |              |        | Page | 5/15 |

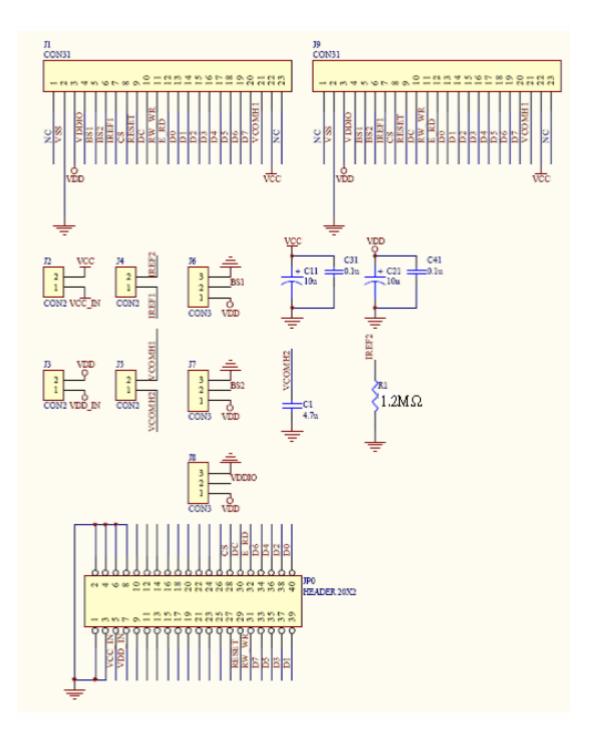

## 1 EVK Schematic

| Product No  | DD-9664FC-2A | REV. A | Daga | 4/15 |

|-------------|--------------|--------|------|------|

| Product No. |              |        | Page | 4/13 |

## 2 Symbol Definition

**D0-D7**: These pins are 8-bit bi-directional data bus to be connected to the MCU's data bus.

**BS1, BS2 :** These input pins are used to configure MCU interface selection by appropriate logic setting, which is described in the following table. User can fix these pins by jumper (J6, J7) or can setup by programme.

|     | 6800-parallel interface (8 bit) | 8080-parallel interface (8 bit) | Serial interface |

|-----|---------------------------------|---------------------------------|------------------|

| BS1 | 0                               | 1                               | 0                |

| BS2 | 1                               | 1                               | 0                |

Table 1 – MCU Interface Selection Setting

**E/RD#**: This pin is MCU interface input. When interfacing to a 6800-series microprocessor, this pin is used as the Enable (E) signal. Read/write operation is initiated when this pin is pulled high and the chip is selected.

When connecting to an 8080-microprocessor, this pin receives the Read (RD) signal. Data read operation is initiated when this pin is pulled low and the chip is selected. When serial interface is selected, this pin E(RD) must be connected to VSS.

$\mathbf{R}/\mathbf{W}$ <sup>#</sup>: This pin is MCU interface input. When interfacing to a 6800-series microprocessor, this pin is used as Read/Write ( $\mathbf{R}/\mathbf{W}$ ) selection input. Read mode will be carried out when this pin is pulled high and write mode when low.

When 8080 interface mode is selected, this pin is the Write (WR) input. Data write operation is initiated when this pin is pulled low and the chip is selected. When serial interface is selected, this pin R/W must be connected to VSS.

**D/C#**: This pin is Data/Command control pin. When the pin is pulled high, the data at D0-D8 is treated as display data. When the pin is pulled low, the data at D0-D8 is transferred to the command register. For detail relationship to MCU interface signals, please refer to the timing characteristics diagrams at following pages and datasheet.

**RESET#** : This pin is reset signal input. When the pin is low, initialization of the chip is executed.

**CS#**: This pin is the chip select input. The chip is enabled for MCU communication only when CS is pulled low.

**VCC** : This is the most positive voltage supply pin of the chip.

**VDD** : Power supply pin for logic operation of the driver.

**VCC\_IN**: This is the external most positive voltage supply. This pin should be shorted with VCC by Jumper 2 (J2)

**VDD\_IN:** This is the external positive voltage supply. This pin should be shorted with VDD by Jumper 3 (J3)

**VDDIO:** Power supply for interface logic level. It should be match with the MCU interface voltage level. VDDIO must always be equal or lower than VDD (J8)

| riduct No. rage 37 | Droduct No  | DD-9664FC-2A | REV. A | ] | Dago | 5 / 15 |

|--------------------|-------------|--------------|--------|---|------|--------|

|                    | Product No. |              |        |   | Page | 3/13   |

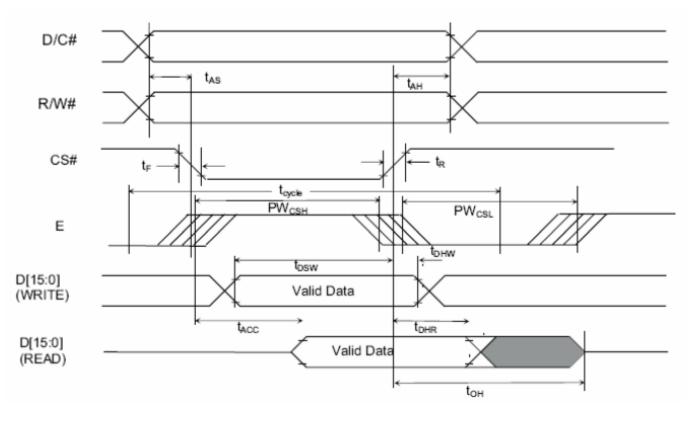

## 3 Timing characteristics

VDD = 2.4 to 3.5V, TA= -40to 85°C

#### $(VDD - VSS = 2.4V \text{ to } 3.5V, VDDIO = 2.4V \text{ to } VDD, TA = -40 \text{ to } +85^{\circ}C)$

| Symbol             | Parameter                              | Min | Тур | Max | Unit |

|--------------------|----------------------------------------|-----|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time (write cycle)         | 130 | -   | -   | ns   |

| PW <sub>CSL</sub>  | Control Pulse Low Width (write cycle)  | 60  | -   | -   | ns   |

| PWcsh              | Control Pulse High Width (write cycle) | 60  | -   | -   | ns   |

| t <sub>cycle</sub> | Clock Cycle Time (read cycle)          | 200 | -   | -   | ns   |

| PWcsL              | Control Pulse Low Width (read cycle)   | 100 | -   | -   | ns   |

| PWcsh              | Control Pulse High Width (read cycle)  | 100 | -   | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time                     | 0   | -   | -   | ns   |

| tан                | Address Hold Time                      | 10  | -   | -   | ns   |

| tosw               | Data Setup Time                        | 40  | -   | -   | ns   |

| tонw               | Data Hold Time                         | 10  | -   | -   | ns   |

| tacc               | Data Access Time                       | -   | -   | 140 | ns   |

| t <sub>OH</sub>    | Output Hold time                       | -   | -   | 70  | ns   |

| le.                | RiseTime                               | -   | -   | 15  | ns   |

| te .               | Fall Time                              | -   | -   | 15  | ns   |

#### Table 2 6800-Series MPU Parallel Interface Timing Characteristics

Figure 1 6800-series MPU parallel interface characteristics

| Product No. | DD-9664FC-2A | REV. A | ] | Dago | 6 / 15 |

|-------------|--------------|--------|---|------|--------|

| Product No. |              |        |   | Page | 6/15   |

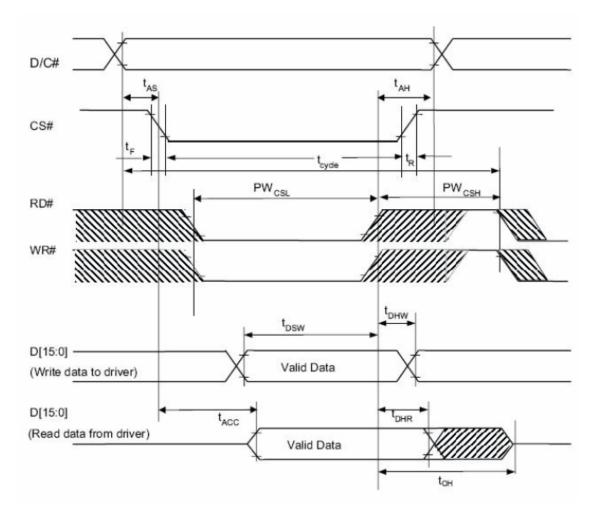

#### (VDD - VSS = 2.4V to 3.5V, VDDIO = 2.4V to VDD, TA = -40 to 85°C)

| Symbol             | Parameter                            | Min | Тур | Max | Unit |

|--------------------|--------------------------------------|-----|-----|-----|------|

| t <sub>oyole</sub> | Clock Cycle Time                     | 130 | -   | -   | ns   |

| tas                | Address Setup Time                   | 0   | -   | -   | ns   |

| tan                | Address Hold Time                    | 10  | -   | -   | ns   |

| tosw               | Write Data Setup Time                | 40  | -   | -   | ns   |

| t <sub>OHW</sub>   | Write Data Hold Time                 | 10  | -   | -   | ns   |

| tone.              | Read Data Hold Time                  | 20  | -   | -   | ns   |

| t <sub>он</sub>    | Output Disable Time                  | -   | -   | 70  | ns   |

| t <sub>ACC</sub>   | Access Time                          | -   | -   | 140 | ns   |

| PW <sub>cs.</sub>  | Chip Select Low Pulse Width (read)   | 100 | -   | -   | ns   |

|                    | Chip Select Low Pulse Width (write)  | 60  |     |     |      |

| PW <sub>CSH</sub>  | Chip Select High Pulse Width (read)  | 60  | -   | -   | ns   |

|                    | Chip Select High Pulse Width (write) | 60  |     |     |      |

| t <sub>R</sub>     | RiseTime                             | -   | -   | 15  | ns   |

| t <sub>e</sub>     | Fall Time                            | -   | -   | 15  | ns   |

#### Table 5 obou-series MITU raranel Interface Thining Unaracteristics

Figure 2 8080-series MPU parallel interface characteristics

Note : When 8 bit used:  $D_0 \sim D_7$  instead.

| Product No. | DD-9664FC-2A | REV. A | Dego | 7 / 15 |

|-------------|--------------|--------|------|--------|

| Product No. |              |        | Page | //15   |

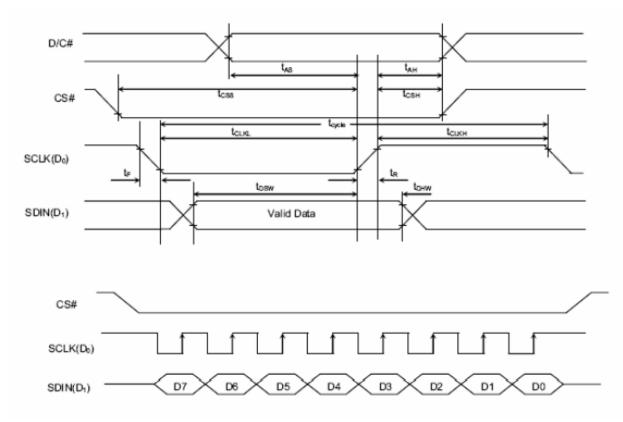

#### $(VDD - VSS = 2.4V \text{ to } 3.5V, VDDIO = 2.4V \text{ to } VDD, TA = -40 \text{ to } 85^{\circ}C)$

| Symbol             | Parameter              | Min | Тур | Max | Unit |

|--------------------|------------------------|-----|-----|-----|------|

| t <sub>cyde</sub>  | Clock Cycle Time       | 150 | -   | -   | ns   |

| 1AS                | Address Setup Time     | 40  | -   | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time      | 40  | -   | -   | ns   |

| t <sub>CSS</sub>   | Chip Select Setup Time | 75  | -   | -   | ns   |

| t <sub>CSH</sub>   | Chip Select Hold Time  | 60  | -   | -   | ns   |

| tosw               | Write Data Setup Time  | 40  | -   | -   | ns   |

| t <sub>orw</sub>   | Write Data Hold Time   | 40  | -   | -   | ns   |

| ta.v.              | Clock Low Time         | 75  | -   | -   | ns   |

| t <sub>cux</sub> H | Clock High Time        | 75  | -   | -   | ns   |

| t <sub>R</sub>     | Rise Time              | -   | -   | 15  | ns   |

| t≓                 | Fall Time              | -   | -   | 15  | ns   |

**Table 4 Serial Interface Timing Characteristics**

**Figure 3 Serial interface characteristics**

| Product No. | DD-9664FC-2A | REV. A | ] | Dago | Q / 15 |

|-------------|--------------|--------|---|------|--------|

| Product No. |              |        |   | Page | 0/13   |

### 4 Connection Between OLED and EVK

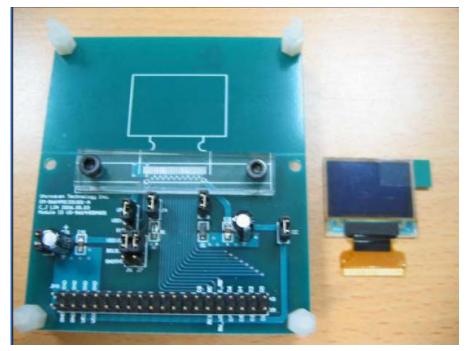

Figure 4 EVK PCB and DD-9664FC-2A Module

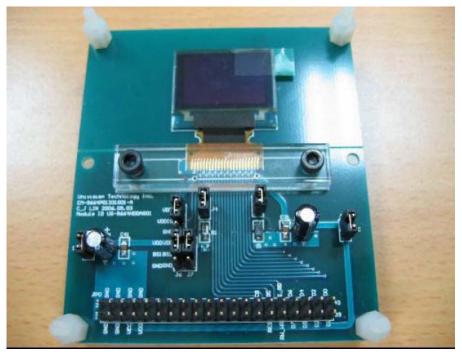

Figure 5 the DD-9664FC-2A and EVK assembled (Top view)

| Product No. | DD-9664FC-2A | REV. A | ] | Daga | 0 / 15 |

|-------------|--------------|--------|---|------|--------|

|             |              |        |   | Page | 9/15   |

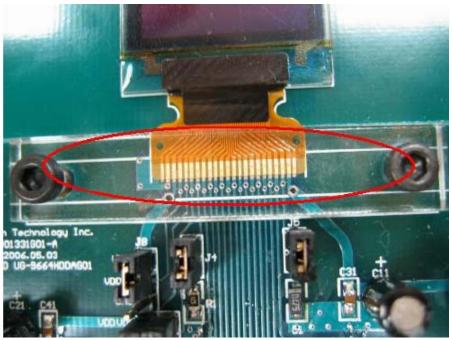

Figure 6 control MCU (not supplied ) connected with EVK

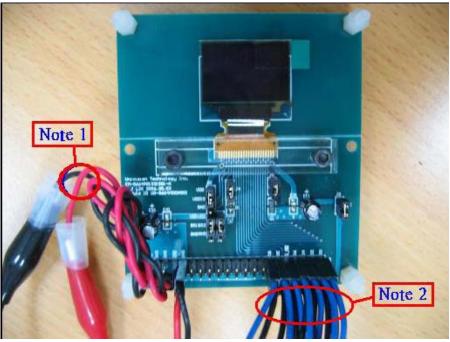

DD-9664FC-2A is a COG type module, please refer to Fig 5, Fig 6. The user can use leading wire to connect EVK with customers system. The example shows as Fig 7.

Figure 7 control MCU connected with EVK

Note 1: It is the external most positive voltage supply. In this sample is connected to power supply.

Note 2: The leading wire has 13 pins totally in this case. (D0-D7, E/RD#, R/W#, E/RD~,RES#,CS#)

| Dreduct No. | DD-9664FC-2A | REV. A | Page | 10 / 15 |

|-------------|--------------|--------|------|---------|

| Product No. |              |        | Fage | 10/13   |

## 5 Module Power Up Sequence

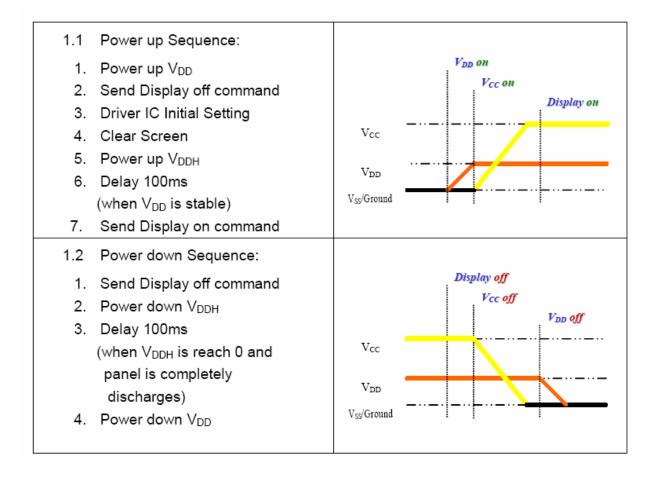

#### 5.1 Power down and Power up sequence

To protect OLED panel and extend the panel life time, the driver IC power up/down routine should include a delay period between high voltage and low voltage power sources during turn on/off. Such that panel has enough time to charge up or discharge before/after operation.

| Product No  | DD-9664FC-2A | REV. A | Page | 11/15 |

|-------------|--------------|--------|------|-------|

| Product No. |              |        | rage | 11/13 |

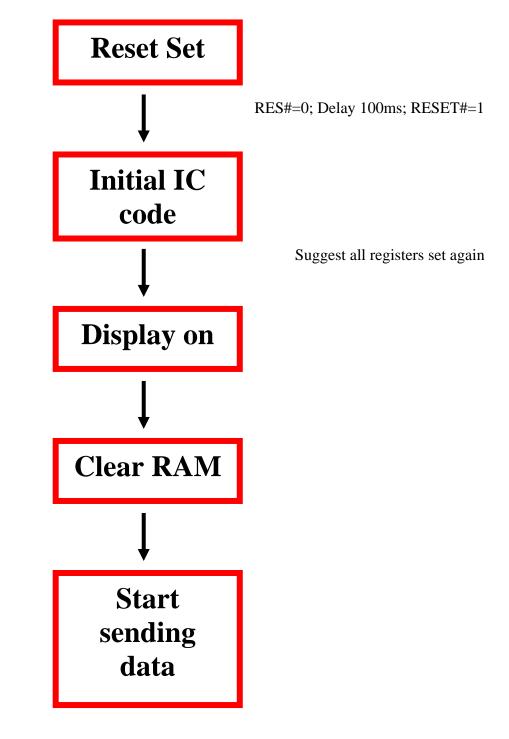

### 6 How to use the DD-9664FC-2A

|             | Daga | 12/15 |

|-------------|------|-------|

| Product No. | Page | 12/15 |

## 7 How to use the DD-9664FC-2A

#### 7.1 Recommended Initial code

| Void Initial_ic(void)                          |                                                           |

|------------------------------------------------|-----------------------------------------------------------|

| {<br>IOCLR=0xffffffff; //dat                   | ta=0                                                      |

| IOSET=bBS1 bBS2 bRE                            | CS bCS bE_RD;                                             |

| IOCLR=bD_C bR_W;                               |                                                           |

| Reset_SSD1331Z();                              |                                                           |

| Write_Register (0xae);                         | //Display off                                             |

| Write_Register(0x81);                          | //set contrast for colorA                                 |

| Write_Register(0x91);<br>Write_Register(0x82); | //145<br>//set contrast for colorB                        |

| ,                                              |                                                           |

| Write_Register(0x50);                          | //80                                                      |

| Write_Register(0x83);                          | //set contrast for colorC                                 |

| Write_Register(0x7d);                          | //125                                                     |

| Write_Register(0x87);                          | //master current control                                  |

| Write_Register(0x06);                          | //6                                                       |

| Write_Register(0x8a);                          | //Set Second Pre-change Speed For ColorA                  |

| Write_Register(0x64);<br>Write_Register(0x8b); | <pre>//100 //Set Second Pre-change Speed For ColorB</pre> |

| Write_Register(0x78);                          | //120                                                     |

| Write_Register(0x8c);                          | //Set Second Pre-change Speed For ColorC                  |

| Write_Register(0x64);                          | //100                                                     |

| Write_Register(0xa0);                          | //set re=map & data format                                |

| Write_Register(0x74);                          |                                                           |

| Write_Register(0xa1);                          | //set display start line                                  |

| Write_Register(0x00);                          |                                                           |

| Write_Register(0xa2);                          | //set display offset                                      |

| Write_Register(0x00);                          |                                                           |

|                                                |                                                           |

| Droduct No. | DD-9664FC-2A | REV. A | ] | Dago | 12/15 |

|-------------|--------------|--------|---|------|-------|

| Product No. |              |        |   | Page | 13/13 |

| Write_Register(0                                                                               | )xa4);      | //set display mode   | :                 |             |

|------------------------------------------------------------------------------------------------|-------------|----------------------|-------------------|-------------|

| Write_Register(0                                                                               | )xa8);      | //set multiplex rati | io                |             |

| Write_Register(0                                                                               | )x3f);      |                      |                   |             |

| Write_Register(0<br>Write_Register(0                                                           |             | //set master config  | guration          |             |

| Write_Register(0                                                                               | )xb0);      | //set power save     |                   |             |

| Write_Register(0                                                                               | )x00);      |                      |                   |             |

| Write_Register(0                                                                               | )xb1);      | //phase 1 and 2 pe   | riod adjustmen    | ıt          |

| Write_Register(0<br>Write_Register(0<br>Write_Register(0                                       | )xb3);      | //display clock div  | vider / oscillato | r frequency |

| Write_Register(0                                                                               | )xbb);      | //Set Pre-Change     | Level             |             |

| Write_Register(0                                                                               | )x3a);      | //58                 |                   |             |

| Write_Register(0                                                                               | )xbe);      | //set vcomh          |                   |             |

| Write_Register(0                                                                               | )x3e);      | //62                 |                   |             |

| Write_Register(0                                                                               | )xaf);      | //set display on }   |                   |             |

| void Reset_SSD                                                                                 | 1331Z(voi   | d)                   |                   |             |

| IOCLR=bRES;<br>Delay_1ms(10);<br>IOSET=bRES;                                                   |             |                      |                   |             |

| void Write_Regis<br>{                                                                          | ster (unsig | ned char out_comn    | nand)             |             |

| IOCLR=bD_C;<br>IOCLR=bCS;<br>IOCLR=bR_W;<br>IOCLR=0x00000<br>IOSET= out_con<br>IOSET=bCS;<br>} |             | OSET=bR_W;           |                   |             |

| Product No.                                                                                    | DI          | D-9664FC-2A          | REV. A            | ]           |

| Page | 14 / 15 |

|------|---------|

|      | 1.7 10  |

$Copyright @2006 \ DENSITRON \ TECHNOLOGIES \ plc. \ All \ rights \ reserved. - Proprietary \ Data$

#### void Write\_Data (unsigned char out\_data)

IOSET=bD\_C; IOCLR=bCS;

IOCLR=bR\_W; IOCLR=0x000000ff; IOSET=out\_data; IOSETbR\_W; IOSET=bCS; }

void Delay\_1ms(int Cycle)

{

unsigned int i,k; for (i=0 ;i<Cycle;i++) for(k=0;k<0x2fff;k++);

}

| Product No. | DD-9664FC-2A | REV. A | Dego | 15/15 |

|-------------|--------------|--------|------|-------|

| Product No. |              |        | Page | 13/13 |

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for densitron manufacturer:

Other Similar products are found below :

DMT024QVNUNT0-2C DMT028QVNTNT0S-1A DMT028QVHXCMI-1A DMT024QVNUCMI-2A LMR4048BG2C16HNG/5V