## **Description**

DM6359S combines a highly integrated current mode PWM controller with a high voltage power MOS. it is optimized for high performance, low standby power, and cost effective off line flyback converter application in sub 20W range.

VDD low startup current and low operating current contribute to a reliable power on startup and low standby design with DM6359S.

DM6359S offers complete protection coverage with automatic self recovery feature including Cycle-by-Cycle current limiting(OCP),over load protection(OLP),VDD under voltage lockout (UVLO), over temperature protection (OTP), and over voltage protection (OVP). Excellent EMI performance is achieved with internal frequency jitter technique and soft switching control at the totem pole gate drive output.

The tone energy at below 22KHz is minimized in the design and audio noise is eliminated.

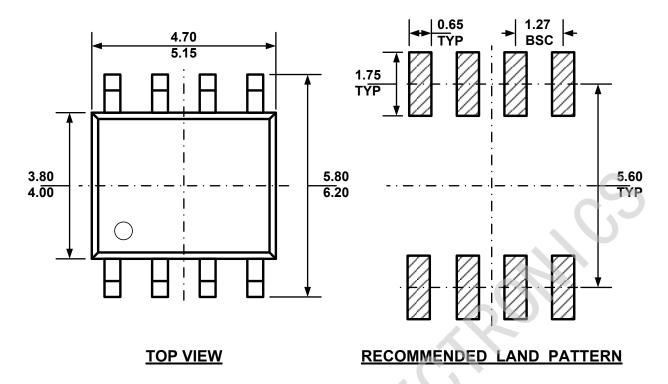

DM6359S is offered in SOP-8 package.

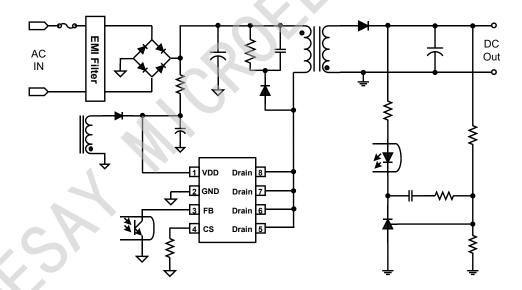

## **Typical Application**

#### **Features**

- ◆ Extra Low Standby(<75mW)

- ◆ Power-on Soft Start Reducing MOS Stress

- ◆ Built-in 630V power MOS

- ◆ Fixed 65KHz Switching Frequency

- ◆ Low VDD startup and operating current

- Frequency jitter to Minimize EMI

- Leading edge blanking on current sense

- ◆ Audio Noise Free Operation

- ◆ VDD Under Voltage Lockout with Hysteresis

- ◆ Cycle-by-Cycle Over Current Protection

- Over Load Protection (OLP)

- ◆ Over Temperature Protection (OTP)

- ◆ VDD Over Voltage Protection (OVP)

## **Applications**

Offline AC/DC flyback converter for

- ♦ AC/DC Adapter

- Set-Top Box Power Supplies

- Auxiliary Power Supply

- Open-frame SMPS

# **Pin Configuration**

YY: Year Code WW: Week Code(01-52)

# **Ordering Information**

| Part number | Package |         | TOP MARK | Shipping    |  |

|-------------|---------|---------|----------|-------------|--|

| DM6359S     | SOP-8   | Pb-free | DM6359   | Tape & Reel |  |

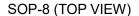

# **Block Diagram**

## **Pin Descriptions**

| Name  | Pin     | Description                              |  |

|-------|---------|------------------------------------------|--|

| VDD   | 1       | Power Supply                             |  |

| GND   | 2       | Ground                                   |  |

| FB    | 3       | Feedback input pin                       |  |

| CS    | 4       | Current sense input and Power MOS Source |  |

| Drain | 5/6/7/8 | Power MOS Drain                          |  |

## **Absolute Maximum Ratings**

| Symbol             | Parameter                                         | Min.  | Max.  | Unit         |

|--------------------|---------------------------------------------------|-------|-------|--------------|

| $V_{Drain}$        | Drain Voltage(off state)                          |       | BVdss | V            |

| I <sub>Drain</sub> | Continuous Drain Current                          |       | 4     | Α            |

| $V_{DD}$           | DC Supply Voltage                                 |       | 38    | V            |

| $I_{DD}$           | VDD DC Clamp Current                              |       | 10    | mA           |

| $V_{FB}$           | FB Input Voltage                                  | -0.3V | 5     | V            |

| Vcs                | CS Input Voltage                                  | -0.3V | 5     | V            |

| $R_{JA}$           | SOP-8 Thermal Resistance (Junction-to-Air)        |       | 120   | °C/W         |

| $T_J$              | Operating Junction Temperature                    | -20   | 150   | $^{\circ}$ C |

| T <sub>STG</sub>   | Storage Temperature Range                         | -55   | 160   | $^{\circ}$ C |

| $T_L$              | Lead Temperature (Wave Soldering or IR,10Seconds) |       | 260   | $^{\circ}$ C |

| ESD                | Human Body Model,JEDEC:JESD22-A114                |       | 2.5   | KV           |

| ESD                | Machine Model, JEDEC:JESD22- A115                 |       | 250   | V            |

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum-rated conditions for extended period may affect device's reliability.

# **Recommended Operating Conditions**

| Symbol            | Parameter                     | Min. | Max. | Unit       |

|-------------------|-------------------------------|------|------|------------|

| $V_{DD}$          | DC Supply Voltage             | 10   | 34   | V          |

| T <sub>A</sub>    | Operating Ambient Temperature | -20  | 85   | $^{\circ}$ |

| $C_{VDD}$         | VDD Capacitor                 | 4.7  | 10   | uF         |

| P <sub>OMAX</sub> | Output Power@90~264V Input    |      | 18   | W          |

|                   | Output Power@230V Input       |      | 20   | W          |

Maximum practical continuous power in an open frame design with sufficient drain pattern as a heat sink, at  $45^{\circ}$ C ambient. Higher output power is possible with extra added heat sink or air circulation to reduce thermal resistance.

# **Electrical Characteristics**(T<sub>A</sub> = 25°C, V<sub>DD</sub>=18V, unless otherwise noted)

| Symbol                   | Parameter                                               | Conditions                 | Min. | Тур. | Max. | Unit        |  |

|--------------------------|---------------------------------------------------------|----------------------------|------|------|------|-------------|--|

| Supply Volt              | Supply Voltage (VDD)                                    |                            |      |      |      |             |  |

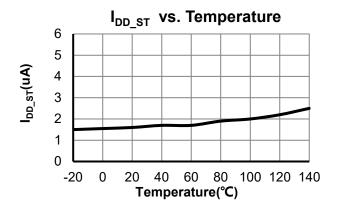

| I <sub>DD_ST</sub>       | Startup Current                                         | VDD=V <sub>DD_ON</sub> -1V |      | 2    | 5    | uA          |  |

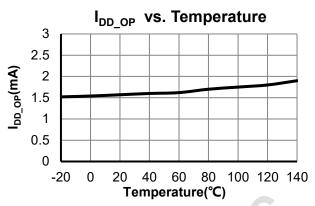

| I <sub>DD_OP</sub>       | Operation Current                                       | VFB=3V                     |      | 2.5  | 3.0  | mA          |  |

| I <sub>DD_Burst</sub>    | Burst Current                                           | VCS=0V,VFB=0.5V            |      | 0.6  | 0.7  | mA          |  |

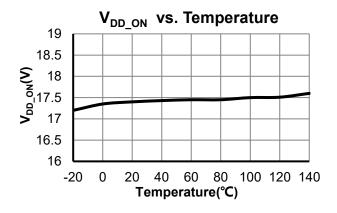

| $V_{DD\_ON}$             | Threshold Voltage to Startup                            | VDD Rising                 | 16.3 | 17.3 | 18.3 | V           |  |

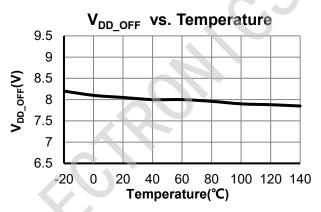

| $V_{DD\_OFF}$            | Threshold Voltage to Stop<br>Switching in Normal Mode   | VDD Falling                | 7.0  | 8.0  | 9.0  | ٧           |  |

| $V_{Pull-up}$            | Pull-up PMOS active                                     |                            |      | 10   |      | ٧           |  |

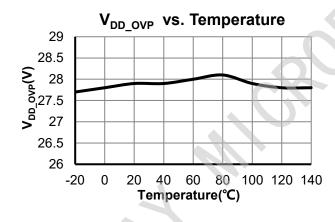

| $V_{\text{DD\_OVP}}$     | Over voltage protection voltage                         |                            | 34.0 | 35.0 | 36.0 | <b>V</b>    |  |

| $V_{DD\_Clamp}$          | VDD Clamp voltage                                       | I <sub>DD</sub> =10mA      |      | 38.0 |      | V           |  |

| Feedback li              | nput Section(FB Pin)                                    |                            |      |      |      |             |  |

| V <sub>FB_Open</sub>     | FB Open Loop Voltage                                    |                            |      | 4.8  |      | V           |  |

| $A_V$                    | PWM input gain ΔVFB/ ΔVCS                               |                            |      | 1.71 |      | V/V         |  |

| D <sub>MAX</sub>         | Max duty cycle                                          | VFB=3V,VCS=0.3V            | 77   | 80   | 83   | %           |  |

| V <sub>Ref_Green</sub>   | The threshold enter green mode                          |                            |      | 2.1  |      | V           |  |

| V <sub>Ref_Burst_H</sub> | The threshold exit Burst mode                           |                            |      | 1.35 |      | V           |  |

| V <sub>Ref_Burst_L</sub> | The threshold enter Burst mode                          | (,)                        |      | 1.25 |      | <b>&gt;</b> |  |

| I <sub>FB_Short</sub>    | FB pin short circuit current                            | Short FB pin to GND        |      | 0.3  |      | mΑ          |  |

| V <sub>TH_PL</sub>       | Power Limiting FB Threshold Voltage                     |                            |      | 3.6  |      | V           |  |

| T <sub>D_PL</sub>        | Power limiting Debounce Time                            |                            |      | 60   |      | mS          |  |

| Z <sub>FB_IN</sub>       | Input Impedance                                         |                            |      | 20   |      | ΚΩ          |  |

| Current Ser              | nse Input(CS Pin)                                       |                            |      |      |      |             |  |

| T <sub>SS</sub>          | Soft start time                                         |                            |      | 5    |      | ms          |  |

| T <sub>LEB</sub>         | Leading edge blanking time                              |                            |      | 300  |      | ns          |  |

| T <sub>D_OC</sub>        | Over Current Detection and Control Delay                |                            |      | 90   |      | ns          |  |

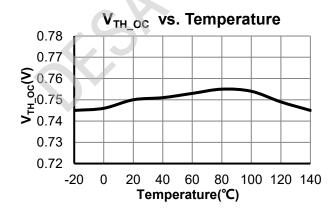

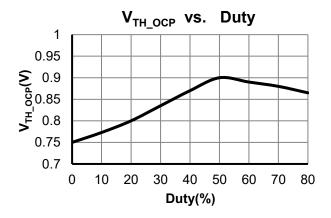

| V <sub>тн_ос</sub>       | Current Limiting Threshold Voltage with zero duty cycle |                            |      | 0.75 |      | ٧           |  |

| V <sub>OCP_Clamp</sub>   | CS voltage clamper                                      |                            |      | 0.9  |      | V           |  |

| Oscillator               |                                                         |                            |      |      |      |             |  |

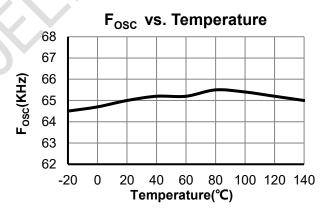

| Fosc                     | Normal Oscillation Frequency                            | VFB=3V,VCS=0V              | 60   | 65   | 70   | KHz         |  |

| F <sub>JR</sub>          | Frequency jitter range                                  |                            |      | +/-4 |      | %           |  |

| F <sub>Jitter</sub>      | jitter frequency                                        |                            |      | 25   |      | Hz          |  |

| F <sub>DT</sub>          | Frequency Variation vs. Temperature Deviation           |                            |      | 5    |      | %           |  |

| F <sub>DV</sub>          | Frequency Variation vs. V <sub>DD</sub> Deviation       |                            |      | 1    |      | %           |  |

| Symbol              | Parameter                   | Conditions                | Min. | Тур. | Max. | Unit          |  |

|---------------------|-----------------------------|---------------------------|------|------|------|---------------|--|

| F <sub>Burst</sub>  | Burst Mode Switch Frequency |                           |      | 22   |      | KHz           |  |

| Power MOS           |                             |                           |      |      |      |               |  |

| BVdss               | Drain-CS Breakdown voltage  | I <sub>Drain</sub> =250uA | 630  |      |      | V             |  |

| R <sub>DS(ON)</sub> | Drain-CS ON resistance      | I <sub>D</sub> =2A        |      | 2.0  | 2.4  | Ω             |  |

| In-chip OTP         |                             |                           |      |      |      |               |  |

| T <sub>OTP_EN</sub> | OTP enter                   |                           |      | 150  |      | ${\mathbb C}$ |  |

| T <sub>OTP_EX</sub> | OTP exit                    |                           |      | 120  |      | $^{\circ}$    |  |

# **Typical Performance Characteristics**(T<sub>A</sub> = 25°C, V<sub>DD</sub>=18V, unless otherwise noted)

## **Functional Description**

The DM6359S is a low power off-line SMPS Switcher optimized for off-line flyback converter applications in sub 20W power range. The Burst Mode control greatly reduces the standby power consumption and helps the design easily to meet the international power conservation requirements.

## **Startup Current and Startup Control**

Startup current of DM6359S is designed to be very low so that VDD could be charged up above  $V_{DD\_ON}$  and device starts up quickly. A large value startup resistor can therefore be used to minimize the power loss yet achieve a reliable startup in application.

## **Operating Current**

The Operating current of DM6359S is low at 2.5mA (typical). Good efficiency is achieved with DM6359S low operation current together with the Burst Mode control features.

### **Soft Start**

DM6359S features an internal 5ms (typical) soft start to soften the electrical stress occurring in the power supply during startup. It is activated during the power on sequence. As soon as VDD reaches  $V_{DD\_ON}$ , the CS peak voltage is gradually increased from 0.05V to the maximum level. Every restart up is followed by a soft start.

#### Frequency jitter for EMI improvement

The frequency jitter is implemented in DM6359S. The oscillation frequency is modulated so that the tone energy is spread out. The spread spectrum minimizes the conduction band EMI and therefore eases the system design.

## **Oscillator Operation**

The switching frequency of DM6359S is internally fixed at 65KHz. No external frequency setting components are required for PCB design simplification.

### **Multi-mode Operation for High Efficiency**

DM6359S is a multi-mode controller. The controller changes the mode of operation according to the

FB pin voltage. At the normal operating condition, the IC operates in traditional fix frequency (65KHz) PWM mode. As the output load current is decreased, the IC enter into green mode smoothly from the PWM mode. In this mode, the switching frequency will start to linearly decrease from 65KHz to 22KHz. So the switching loss is minimized and the high conversion efficiency can be achieved. At light load or no load condition, most of the power dissipation in a switching mode power supply is from switching loss of the MOS, the core loss of the transformer and the loss of the snubber circuit. The magnitude of power loss is in proportion to the switching frequency. Lower switching frequency leads to the reduction on the power loss and thus conserves the energy. The switching frequency is internally adjusted at no load or light load condition. The switch frequency reduces at light/no load condition to improve the conversion efficiency.

At light load or no load condition, the FB input drops below  $V_{Ref\_Burst\_L}$  and device enters Burst Mode control. The Gate drive output switches when FB input rises back to  $V_{Ref\_Burst\_H}$ . Otherwise the gate drive remains at off state to minimize the switching loss and reduces the standby power consumption to the greatest extend.

#### **Current Sensing and Leading Edge Blanking**

Cycle-by-Cycle current limiting is offered in DM6359S current mode PWM control. The switch current is detected by a sense resistor into the CS pin. An internal leading edge blanking circuit chops off the sensed voltage spike at initial internal power MOSFET on state due to snubber diode reverse recovery and surge gate current of power MOSFET. The current limiting comparator is disabled and cannot turn off the internal power MOSFET during the blanking period. The PWM duty cycle is determined by the current sense input voltage and the FB input voltage.

#### **Internal Synchronized Slope Compensation**

Built-in slope compensation circuit adds voltage ramp into the current sense input voltage for PWM generation. This greatly improves the close loop stability at CCM and prevents the sub-harmonic oscillation and thus reduces the output ripple voltage.

#### **Driver**

The internal power MOSFET in DM6359S is driven by a dedicated gate driver for power switch control. Too weak the gate driver strength results in higher conduction and switch loss of MOSFET while too strong gate driver strength results the compromise of EMI.

A good tradeoff is achieved through the built-in totem pole gate design with right output strength and dead time control. The low idle loss and good

EMI system design is easier to achieve with this dedicated control scheme.

#### **Protection Controls**

Good power supply system reliability is achieved with auto-recovery protection features including Cycle-by-Cycle current limiting (OCP), Under Voltage Lockout on VDD (UVLO), Over Temperature Protection (OTP), VDD Over Voltage Protection (OVP). The OCP is line voltage compensated to achieve constant output power limit over the universal input voltage range. At overload condition when FB input voltage exceeds power limit threshold value for more than  $T_{D\_PL}$ , control circuit reacts to shut down the converter. It restarts when VDD voltage drops below UVLO limit.

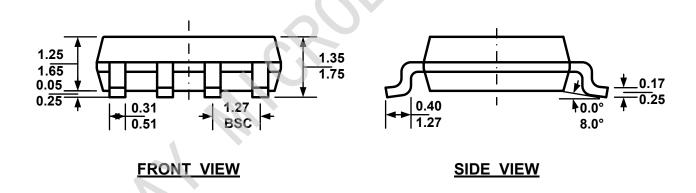

# **Package Information**

### SOP-8

#### Note:

- 1. All dimensions are in millimeters

- 2. Package length does not include mold flash protrusion or gate burr

- 3. Package WIDTH does not include mold flash protrusion

- 4. Drawing is not to scale

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by DESAY manufacturer:

Other Similar products are found below:

LV5065VB-TLM-H LV5066V-TLM-H LV5725JAZ-AH 633888R MP2908AGF AZ7500EP-E1 NCP1012AP133G NCP1217P133G

NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP1587GDR2G NCP6153MNTWG

NCP81005MNTWG NCP81101BMNTXG NCP81205MNTXG HV9123NG-G-M934 IR35207MTRPBF ISL6367HIRZ CAT874-80ULGT3

SJ6522AG SJE6600 TLE63893GV50XUMA1 IR35215MTRPBF SG3845DM NCP1216P133G NCP1236DD65R2G NCP1247BD100R2G

NCP1250BP65G NCP4202MNR2G NCP4204MNTXG NCP6132AMNR2G NCP81141MNTXG NCP81142MNTXG NCP81172MNTXG

NCP81203MNTXG NCP81206MNTXG NX2155HCUPTR UC3845ADM UBA2051C IR35201MTRPBF MAX8778ETJ+

MAX17500AAUB+T MAX17411GTM+T MAX16933ATIR/V+ NCP1010AP130G NCP1063AD100R2G NCP1216AP133G

NCP1217AP100G