# **General description**

iW6401 is a highly versatile digital processor IC for off-line LED drivers in smart lighting applications. With its high degree of configurability it can serve as a platform for a wide range of digital dimming LED applications.

Multiple dimming interfaces connect the iW6401 to home or building automation systems: I<sup>2</sup>C-bus, DLT receiver (IEC 62756 compliant), light switch on/off events using a configurable state machine. Lamp dimming curves are programmable.

iW6401 can serve as a power front-end for wireless communication modules, intelligent sensors or generic microcontrollers. An integrated LDO provides a stable supply voltage for external peripherals.

All operating parameters and functions are configurable using unique multi-write OTP programming. Digital control loops provide precise control of both input power and light output. A high power factor can be achieved while maintaining stable and flicker-free light across an ultra-wide dimming range.

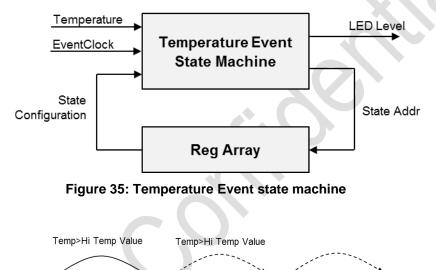

iW6401 can actively manage lamp temperature using on-chip or off-chip sensors and a configurable state machine. Accurate temperature settings permit thermal optimization of the lamp design to reduce the cost of cooling parts. Other system supervision functions such as short circuit and open load can be easily configured via register settings.

iW6401 can be configured for AC supply voltages ranging from 90 V to 264 V. It is available in a small leadless DFN12 package.

Although the iW6401 offers ultimate flexibility with full programmability most applications will use predetermined data for programming for fastest time to market. Reference designs can be used to verify ready-made memory profiles.

# **Key features**

- High performance wide range dimming engine

- Quasi-resonant (soft) switching

- Patented PrimAccurate<sup>™</sup> LED current control

- IEC62756 data receiver & bypass load

- I2C dimming and control interface

- Programmable dimming curves .

- OTP configuration memory

- Software controlled standby/wakeup .

- Toggle-switch event driven state machine

- Regulated power for external master

- Programmable soft start

- End-of-Line diagnostics and calibration

- Small leadless 4x4 mm DFN12 package

- Active PFC control with High Power Factor

- Open/short protection with auto-restart

- State machine based temperature de-rating

- Internal/External temperature sensor

- Input overvoltage protection

# Applications

- Dimmable retrofit LED bulbs

- **Dimmable linear LED tubes**

- Standalone AC supply driven LED drivers

- Wireless dimmable LED bulbs and drivers

- IEC62756 compatible LED bulbs and drivers

- Lamps with integrated smart sensors

**Company confidential**

# **Digital Programmable LED Driver IC**

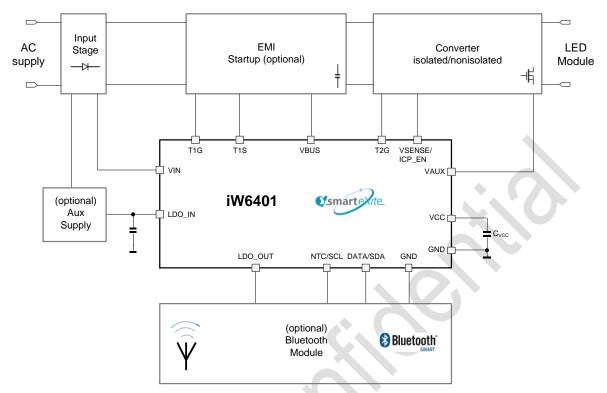

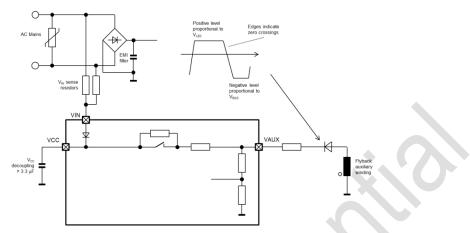

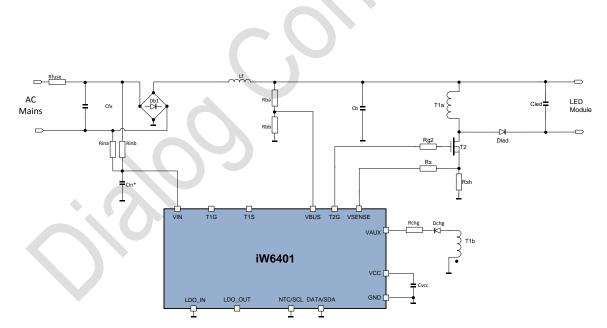

# System and Application diagram

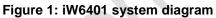

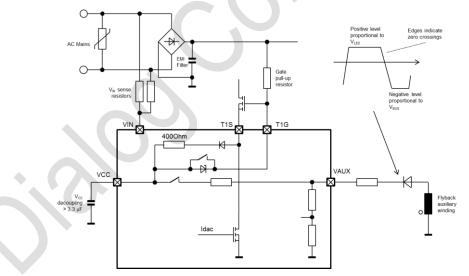

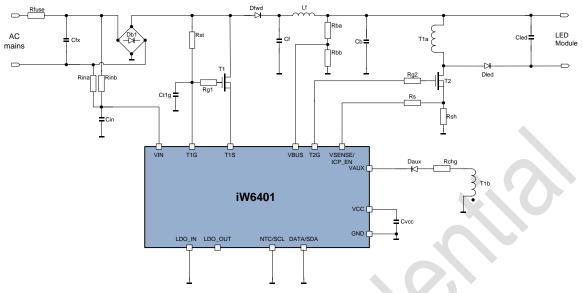

Figure 2: iW6401 typical application

# Digital Programmable LED Driver IC

**Company confidential**

# **Table of Content**

| Ge  | neral description                     | 1 |

|-----|---------------------------------------|---|

| Ke  | y features                            | 1 |

| Ар  | plications                            | 1 |

| Sy  | stem and Application diagram          | 2 |

| Tal | ble of Content                        | 3 |

| Fig | ures                                  | 4 |

| Ta  | bles                                  | 5 |

| 1   | Terms and definitions                 | 6 |

| 2   | References                            | 6 |

| 3   | Block diagram                         | 7 |

| 4   | Chip Configuration and Programming1   | 3 |

| 5   | Absolute maximum ratings              |   |

| 6   | Recommended operating conditions      |   |

| 7   | Electrical characteristics            |   |

| 8   | Thermal characteristics               |   |

| 9   | Functional description                | 7 |

| 10  | Protection mechanisms                 | 2 |

| 11  | Chip programming and data interfaces5 | 7 |

| 12  | Typical Application Diagrams          | 2 |

| 13  | Package information                   | 4 |

| 14  | Ordering information                  | 5 |

| 15  | Revision history                      | 5 |

## **Company confidential**

# Figures

| Figure 1: iW6401 system diagram                                                   | 2  |

|-----------------------------------------------------------------------------------|----|

| Figure 2: iW6401 typical application                                              | 2  |

| Figure 3: iW6401 block diagram                                                    | 7  |

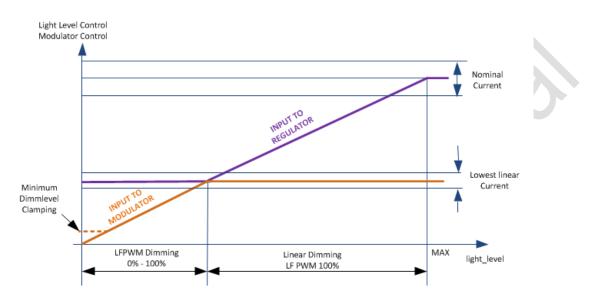

| Figure 4: Scaling of LED Current vs. Dim-Level                                    |    |

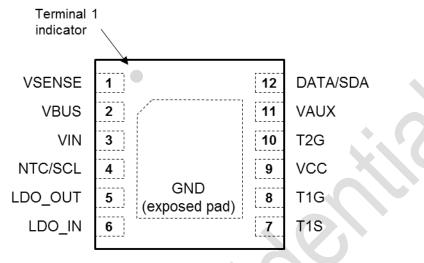

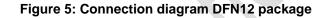

| Figure 5: Connection diagram DFN12 package                                        | 13 |

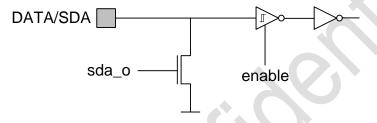

| Figure 6: Pin DATA/SDA internal circuit                                           |    |

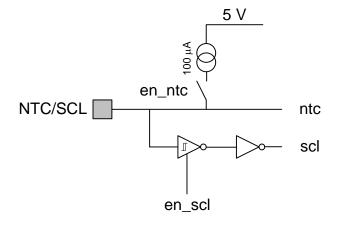

| Figure 7: Pin NTC/SCL internal circuit                                            | 16 |

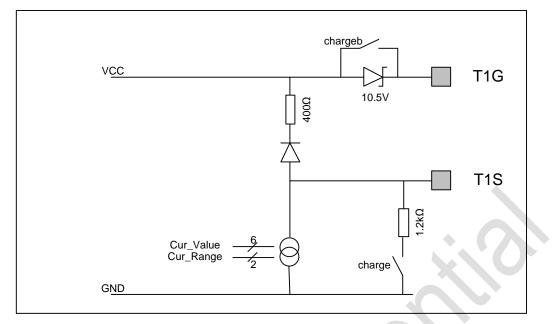

| Figure 8: Pins T1G and T1S internal circuit                                       | 18 |

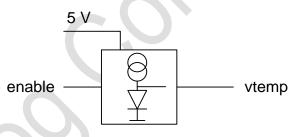

| Figure 9: Internal temperature sensor                                             | 18 |

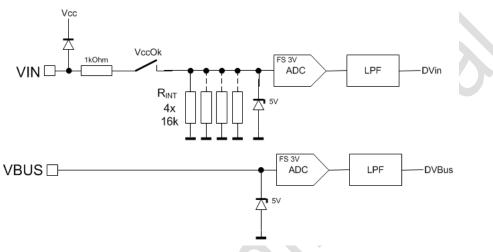

| Figure 10: Pins LDO_IN and LDO_out internal circuit                               | 19 |

| Figure 11: Typical LDO output current vs. V <sub>LDO IN</sub> and V <sub>CC</sub> | 19 |

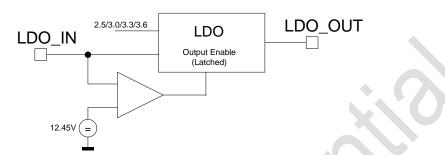

| Figure 12: Vin and Vbus Sensing Scheme                                            | 20 |

| Figure 13: Pin VSENSE                                                             | 21 |

| Figure 14: Internal circuit at Vaux                                               | 21 |

| Figure 15: Power modes state diagram                                              |    |

| Figure 16: Vin turn on conditions                                                 |    |

| Figure 17: Power supply with passive startup                                      |    |

| Figure 18: Power supply with active startup                                       | 32 |

| Figure 19: Vcc Control Scheme                                                     | 33 |

| Figure 20: Vcc Control Scheme                                                     |    |

| Figure 21: Simplified Vcc waveform in case of charging faster than 5 mV/µs        | 34 |

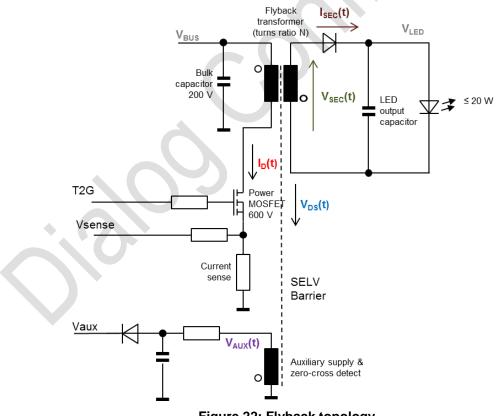

| Figure 22: Flyback topology                                                       |    |

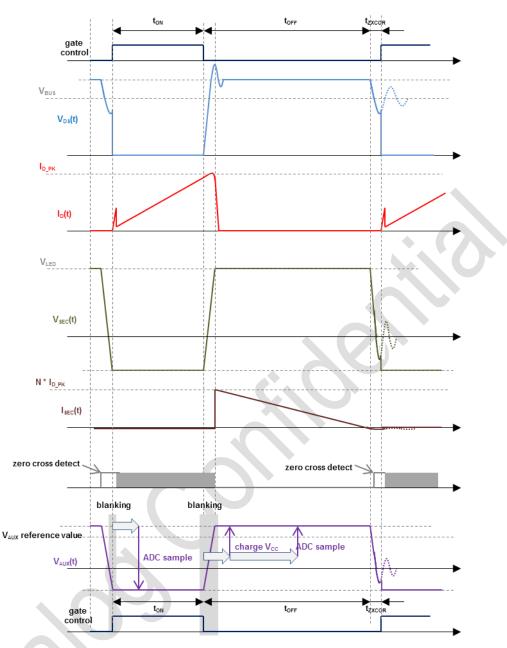

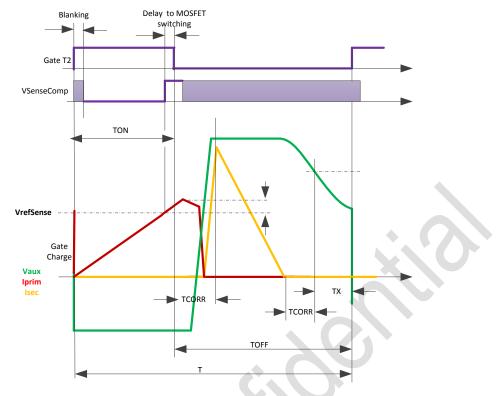

| Figure 23: Flyback stage waveforms (typical) in linear mode                       | 38 |

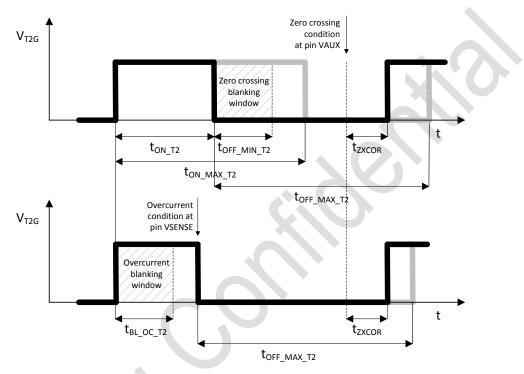

| Figure 24: PWM waveforms for QR DCM mode                                          | 39 |

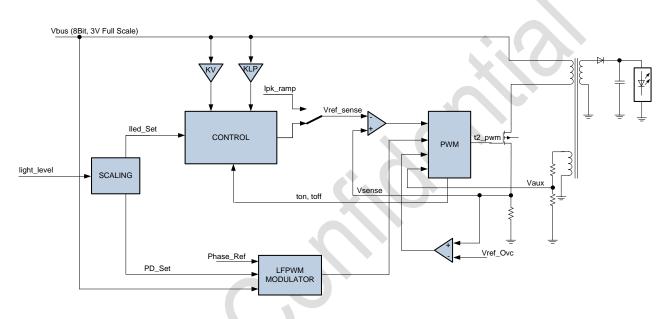

| Figure 25: Flyback control system                                                 |    |

| Figure 26: Flyback control timing diagram                                         |    |

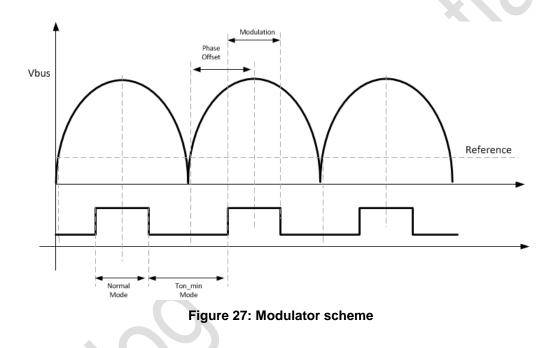

| Figure 27: Modulator scheme                                                       |    |

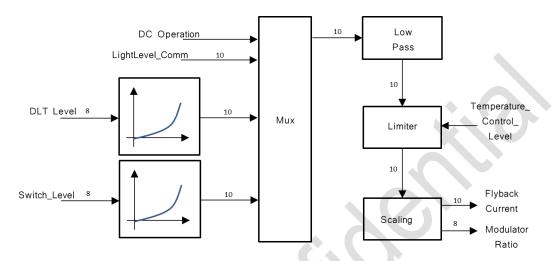

| Figure 28: Dimming management scheme                                              | 44 |

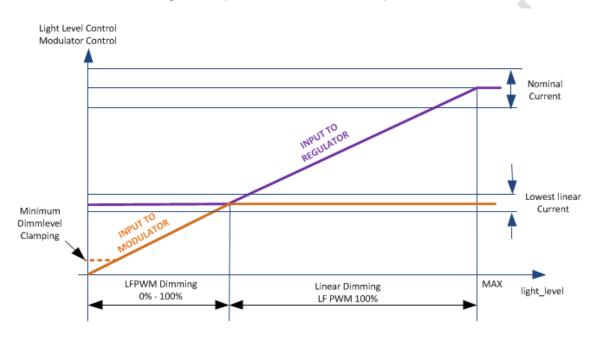

| Figure 29: Mapping light level to flyback current setpoint                        | 45 |

| Figure 30: Interpolating points in OTP to set the dimcurves                       |    |

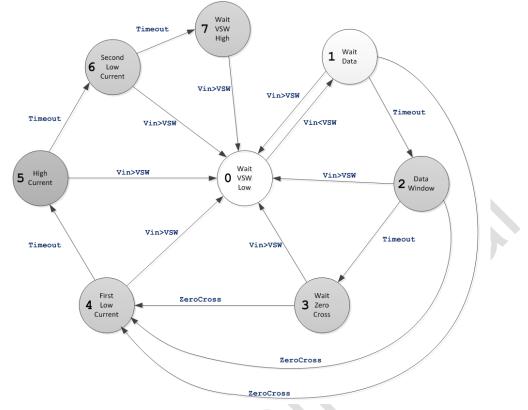

| Figure 31: Switch event detection scheme                                          | 46 |

| Figure 32: Switch event state machine                                             |    |

| Figure 33: DLT dimming                                                            |    |

| Figure 34: DLT state machine                                                      |    |

| Figure 35: Temperature Event state machine                                        |    |

| Figure 36: Example implementation                                                 |    |

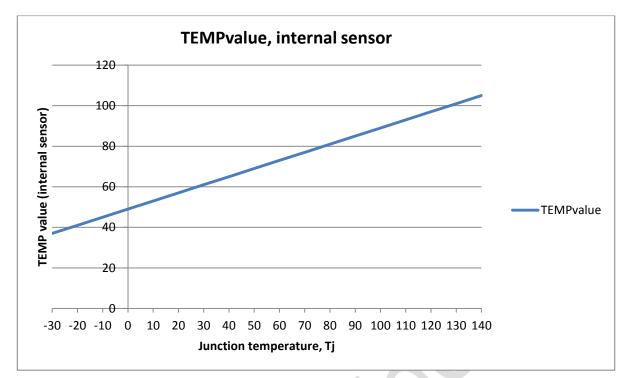

| Figure 37: Typical characteristic of the on-chip temperature sensor               |    |

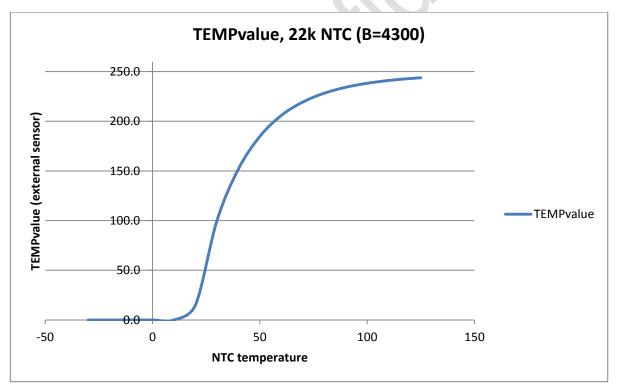

| Figure 38: Example characteristic of an external NTC temperature sensor           | 54 |

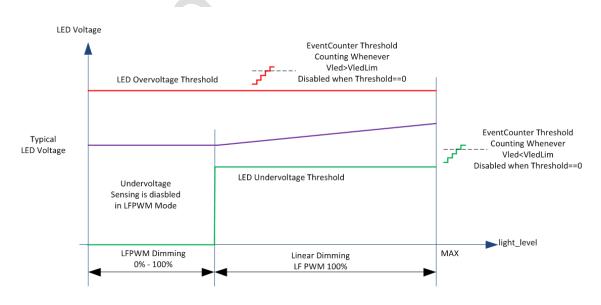

| Figure 39: Led monitoring thresholds                                              |    |

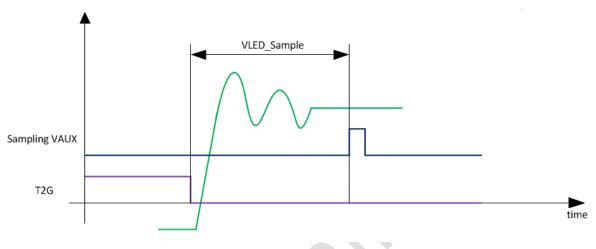

| Figure 40: Timing of VLED Sampling                                                |    |

| Figure 41: Programming Interfaces                                                 |    |

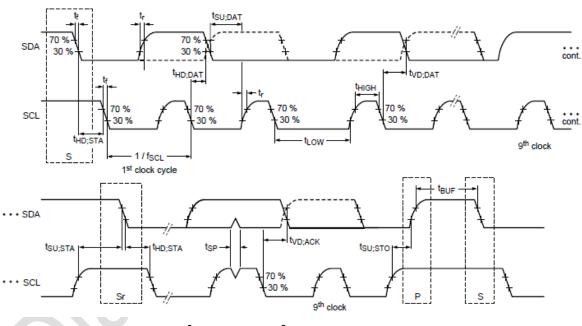

| Figure 42: I <sup>2</sup> C-bus timing I <sup>2</sup> C-bus timing (normal mode)  | 58 |

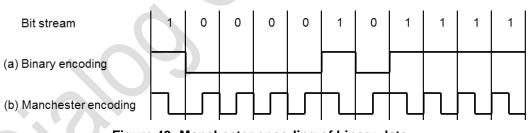

| Figure 43: Manchester encoding of binary data                                     |    |

| Figure 44: Application diagram for DLT dimming                                    |    |

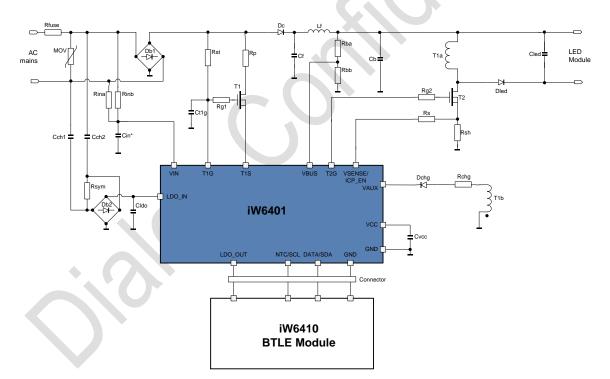

| Figure 45: Application diagram with Bluetooth module and startup circuit          |    |

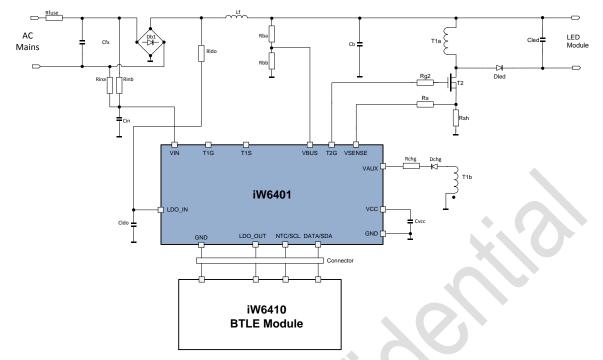

| Figure 46: Application diagram with Bluetooth module and passicve startup         |    |

| Figure 47: Application diagram with single flyback stage and passive startup      |    |

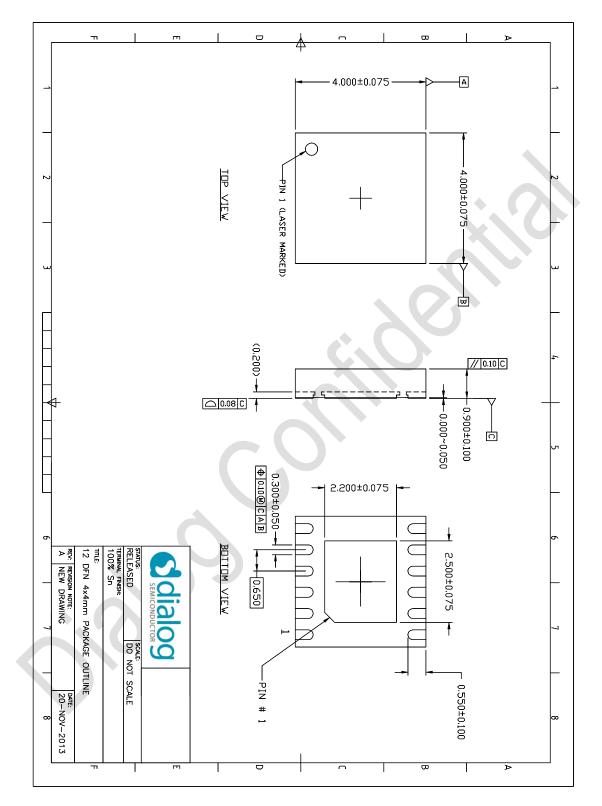

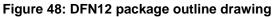

| Figure 48: DFN12 package outline drawing                                          | 6/ |

|                                                                                   | 04 |

## **Company confidential**

# Tables

| Table 1: Pin description                                           | 13 |

|--------------------------------------------------------------------|----|

| Table 2: Pin type definition                                       |    |

| Table 3: Selection of Resistors at Pin Vin                         |    |

| Table 4: Absolute maximum ratings                                  |    |

| Table 5: Recommended operating conditions                          |    |

| Table 6: Electrical characteristics                                |    |

| Table 7: Thermal characteristics                                   |    |

| Table 8: Switch event state configuration                          | 47 |

| Table 9: Temperature event state configuration                     |    |

| Table 10: Temperature event timeout                                |    |

| Table 11: registers used by the temperature control state machine. |    |

| Table 12: Ordering information                                     |    |

**Company confidential**

# **Digital Programmable LED Driver IC**

# 1 Terms and definitions

| DCM    | Discontinuous Conduction Mode                             |

|--------|-----------------------------------------------------------|

| DLT    | Digital Load Side Transmission (according to IEC 62756-1) |

| EoL    | End of Line (production line)                             |

| ICP    | In-Circuit Programming                                    |

| LDO    | Low Drop-Out (regulator)                                  |

| LED    | Light Emitting Diode                                      |

| MCU    | Microcontroller                                           |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor         |

| NTC    | Negative Temperature Coefficient (thermistor)             |

| OTP    | One Time Programmable (memory)                            |

| PFC    | Power Factor Correction                                   |

| PSRR   | Power Supply Rejection Ratio                              |

| PWM    | Pulse Width Modulation                                    |

| LFPWM  | Low Frequency Pulse Width Modulation                      |

| SELV   | Safety Extra Low Voltage                                  |

| SOA    | Safe Operating Area                                       |

| SSM    | System State Machine                                      |

| QR     | Quasi Resonant (switching mode)                           |

|        |                                                           |

# 2 References

- 1. The I<sup>2</sup>C-bus specification v2.1, Philips Semiconductors, 9398 393 40011, 2000.

- 2. I<sup>2</sup>C-bus specification and user manual v4.0, NXP Semiconductors, UM10204, 2012.

- 3. IEC 62756, Digital load side transmission lighting control (DLT) Part 1: Basic requirement.

- 4. Bluetooth Module Specification

- 5. Bluetooth Smart Communication Standard

Company confidential

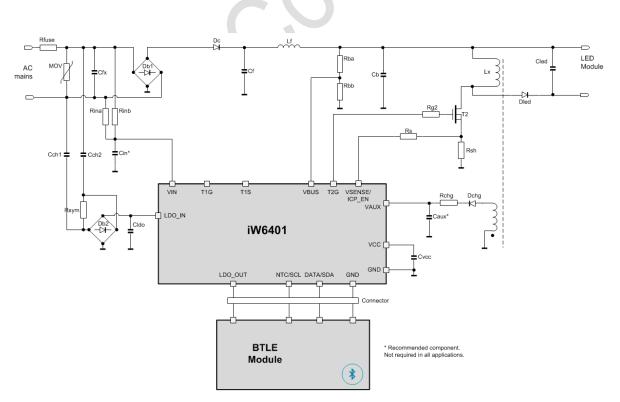

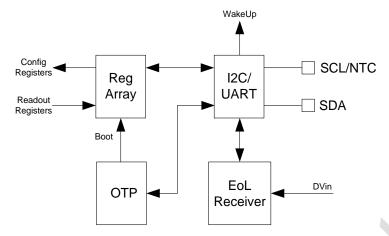

# 3 Block diagram

| Datasheet            | Version 3.0 | 22-May-2015                          |

|----------------------|-------------|--------------------------------------|

| CED0011 100 00 Day 1 | 7 -1 00     | © 2015 Dialag Samiaga dugtar Carbl I |

## 3.1 Functional Overview

The following chapter summarize all functions of the control chip. More detailled descriptions of each of the subfunctions are given in the corresponding chapters.

#### Startup and chip power supply

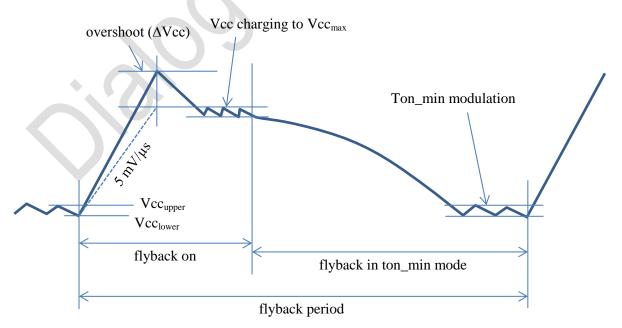

The chip is started up via two parallel methods: passive startup via the upper resistor of the VIN voltage divider and active startup through the external bypass load MOSFET. Active startup is used whenever the external MOSFET is fitted. For active startup the gate of the external bypass load MOSFET is pulled up by a high value resistor limited by an 11V zener allowing current through T1S pin into VCC. Once VCC reaches the turn-on threshold active startup is disabled by connecting the T1G pin to VCC and setting the internal current source to zero. The passive startup is disabled by connecting the through VAUX by controlling the charging switch between VAUX and VCC. The maximum VCC is monitored and if above the programmable limit the charging control switch is disabled. The charging switch alternatings with flyback cycles to allow V<sub>LED</sub> measurements, the alternating pattern can be configured. Whenever the flyback is in "ton\_min" mode charging is enabled every cycle. The amount of charging in each cycle is controlled by setting ton\_min, the external charging resistor at VAUX and the actual VAUX voltage.

The switches in the block diagram are set according to the VccOk signal. VccOk is asserted when the VCC reaches the turn-on level Vcc (~17V) and remains asserted until the VCC crosses the lower threshold Vcc (~10V). The capacitor at VCC is recommended to be a minimum of  $10\mu$ F.

#### **Flyback Operation**

The flyback converter stage is operated in two different modes: peak current regulation and ton\_min.

1.) Peak current regulation:

The primary peak current is regulated such that the average LED current meets the control setpoint. The control setpoint is created by the current scaling module which translates a relative light level into a current set value. When dimmed, the magnitude of the LED current is reduced until a tripping point is reached. From there on the current is kept constant but the flyback is LFPWM controlled to toggle between peak current mode and ton\_min mode.

2.) Ton\_min

In this mode the flyback is operated with a constant ton/toff switching signal at the gate of the flyback MOSFET. Both values are programmable. Depending on the programmed setpoint and the design of the auxiliary winding, the VCC supply is powered during ton\_min mode.

The detailled operation of both modes is outlined in their corresponding chapters.

During peak current regulation the flyback is protected against overcurrent via a dedicated comparator at VSENSE. The overcurrent detection acts in two different ways: exceeding the overcurrent limit at VSENSE immediately turns off the flyback MOSFET. If consecutive overcurrent events are observed the state machine can be configured to shutdown.

The input voltgae of the flyback converter is monitored against over- and under-voltage to maintain a safe operating condition. VBUS is monitored and the flyback converter is enabled / disbled under control of the system state machine.

#### Flyback Peak Current Regulation

The peak of the primary current is regulated by means of a dynamic reference voltage provided from a DAC. The digital setpoint of the DAC is generated by a PI-type control loop. The input of the control loop is the difference between the light level as requested by the current scaling unit (LightLevelSet) and the calculated value of the LED current. Please refer to the corresponding chapter on the details

| _ |    |    | ъ. |   |    |

|---|----|----|----|---|----|

| D | at | as | sh | е | et |

**Company confidential**

of the control loop calculation. The regulator output can further be modulated by two independent linear gain factors in order to achieve high PSRR to the bus voltage and/or active PFC mode. The control coefficients for the PI control loop are programmable and can have different values for both high and low dim levels.

### **Current Scaling Unit**

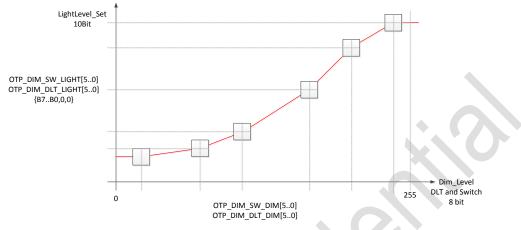

The current scaling unit implements the transfer characteristic as shown in the diagram below:

Figure 4: Scaling of LED Current vs. Dim-Level

The input relative light level is defined as a 10-bit value. The output of the scaling unit is a 10-bit setpoint value for the PI control loop. Below a programmable lowest current value, the scaling unit generates an 8-bit value for the LFPWM modulation. Between the maximum and lowest linear current the setpoint value is linearly scaled, below this limit the PWM is linearly scaled to give a resultant linear mapping from input to output. A dim-level clamping value can be set to keep the LED light above a minimum level.

#### Dim Control Unit:

Several sources can influence the light level which sets the LED output current:

- Data received via DLT

- Data received via I2C, serial

- Dimming setpoint from light-switch control

- Light modulation generated by the end of line programming

- Light Level as requested by the temperature derating unit

The dim control unit combines all data into one relative light level that feeds into the scaling unit. Inside the dim control block low pass filtering is applied to the relative light level to maintain smooth change of light. The filter frequency can be programmed. Data interpolation is applied to the DLT data input and the light-switch data input. This allows the user to calibrate the corresponding dimcurves for a smooth dimming experience.

| Datasheet | Version 3.0 | 22-May-2015 |

|-----------|-------------|-------------|

|           |             |             |

## **Digital Programmable LED Driver IC**

**Company confidential**

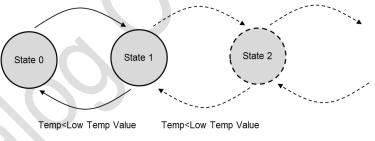

**Power Derating:** An internal or external temperature sensor can be selected to perform temperature control. The measured temperature dependant voltage is converted to a digital value and processed in the power derating unit. The module implements a programmable state machine to reduce output power when the system reaches programmable temperature thresholds. A programmable maximum temperature shut-down can be configured to protect the system from overheating.

$V_{IN}$  processing: During start up the external resistors connected to VIN is a charging path to VCC. During run mode a potential divider is formed between the external and the internal resistor. The internal resistor value is programmable.

In run mode the VIN signal is used to:

- 1.) Monitor the status of AC supply (light switch)

- 2.) Receive DLT data

- 3.) Control the bleed state machine

- 4.) Synchronize the Flyback LFPWM

VIN is digitised by an 8-bit ADC with a 3V full scale range.

#### **V**<sub>BUS</sub> processing:

VBUS is connected to an external potential divider and the voltage digitised by an 8-bit ADC with a 3V full scale range. The digitized values are low-pass filtered to reduce noise. VBUS is used to control the following functions:

- 1.) PSRR of PI control loop

- 2.) Active PFC control

- 3.) VBUS over- and under-voltage protection

**OTP and System Clock:** The iW6401 has two independent system clocks: 16kHz for controlling the system during low power (standby mode) operation and 40 MHz for the digital processing during normal (run mode) operation.

The OTP memory contains the configuration data, allowing the device to be setup in the application to give the best possible operation; this also allows variations in the external components to be compensated.

The OTP memory is accessible via both I2C/Serial and EoL programming. The iW6401 has default values for all user registers; wherever default values are applicable to the application no reprogramming is required.

*Important*: Changing OTP memory has an effect on the chip operation and invalid settings for a given application can lead to destructive system conditions.

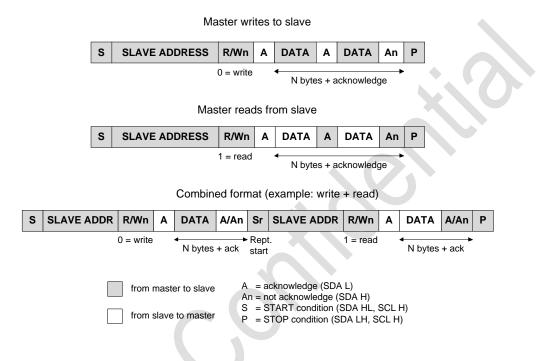

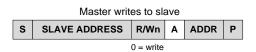

#### I2C/Serial Interface

This provides access to the register array via I2C or single-pin serial communication; SDA/SCL and DATA are used as communication pins respectively. For both communication protocols an external pull-up resistor is required – a value between  $1.5k\Omega$  and  $4.7k\Omega$  is recommended (depending on the communication speed).

The I2C interface operates at 100kHz (standard-mode), 400kHz (fast-mode), 1MHz (fast-mode plus). The iW6401 is configured as a slave device.

The Serial interface is configurable over a wide range of operating speeds.

<u>Changing register settings "on the fly" while the chip is active can lead to invalid configurations which</u> <u>can lead to destructive system conditions.</u>

#### Source Controlled MOSFET driver (SCMD)

This uses the bypass load MOSFET as a linear bleed current with an internal current source. The current profile is controlled via a programmable state machine. The source controlled driver is only active during the run mode of the chip. By default the state machine is programmed to serve as a bypass load according to the DLT specification IEC62756.

Whenever the chip is in standby mode, for example during start up, the external MOSFET is used for active start up.

The SCMD has 4 ranges each with 6-bits of current resolution; this results in an 8-bit value setting both range and current. The state machine can be configured for independent currents where state transitions are triggered based on VIN voltage and/or timeout.

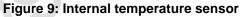

#### LDO

A linear voltage regulator provides power to an external controller (MCU/Bluetooth/etc.). The output voltage can be set to be 2.5 V, 3 V, 3.3 V or 3.6 V. The LDO can be programmed to keep the output voltage disabled until the LDO\_IN input has reached a threshold value of 12.5V; this allows the load to draw higher currents during initialization by using the stored charge in the decoupling capacitor.

#### Zero Cross and V<sub>LED</sub>/VCC control

The voltage on VAUX serves multiple functions:

- 1.) To establish QR operation of the flyback converter

- 2.) To charge VCC via a low impedance switch

- 3.) Monitoring the LED voltage during peak current regulation

Typically the voltage applied to this pin is generated by an auxiliary winding of the flyback converter transformer. The winding must be designed to have positive voltage levels during the period where the energy of the flyback converter is transferred into the LED. The target voltage level shall be proportional to the LED voltage and shall have a level of typically 25V. The transformer winding is connected to the chip via a current limiting resistor and a diode. Any potential ringing on the auxiliary winding must be clamped external to the chip to avoid any voltage overstress.

The different functions of the VAUX are controlled by a programmable alternating pattern of measure and charge cycles.

During measure cycle the VAUX input is internally loaded by a  $10k\Omega$  resistor in order to discharge any parasitic pin capacitance. An internal 11:1 potential divider is used to measure and sense the VAUX voltage. A comparator with a programmable reference triggers on the negative going edge to detect the zero-crossing of the flyback current; this establishes quasi resonant mode of the converter. The divided VAUX voltage digitised by an 8-bit ADC with a 3V full scale range, this sampled voltage is proportional to the LED voltage.

| Datasheet | Version 3.0 | 22-May-2015 |

|-----------|-------------|-------------|

|           |             |             |

**Company confidential**

During charge cycles the internal switch between VAUX and VCC is activated in order to charge the decoupling capacitor. Due to the fact that Vaux is now connected to VCC, detection of zero cross is no longer possible. The timing for the flyback switching and the  $V_{LED}$  voltage uses the values from the most recent measure cycle.

During 'ton\_min' mode only charge cycles are executed as all measurements are not required as there is no power transferred to the LED.

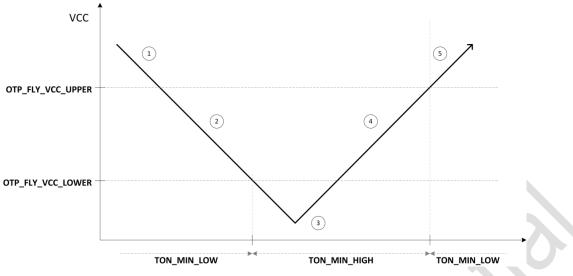

The VCC voltage is monitored and the system keeps this within its upper and lower limits.

Whenever VCC reaches its upper threshold the internal charging switch is disabled as no more charging is required.

Whenever Vcc reaches its lower threshold the 'ton\_min' is changed to a higher value in order to provide more charging current. An effective average 'ton\_min' is established by letting the system sweep between these two levels. This is a self-adaptive control to overcome any tolerance issues related to 'ton\_min' switching.

#### System State Machine

All iW6401 operating states are managed by the system state machine. Based on system events and timeouts, state transitions are triggered. The detailed state chart is given in the corresponding chapter.

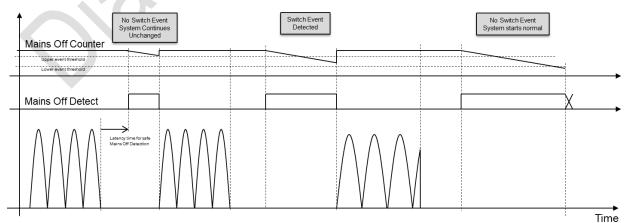

Based on the detection of light switch events (a short AC supply off/on switch event) a dimming request is transferred to the dim control unit.

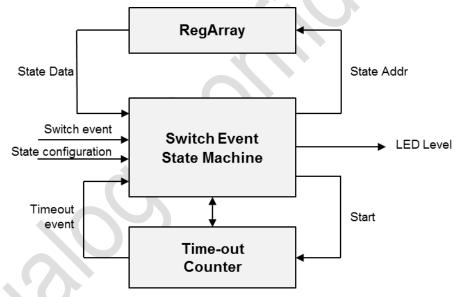

When a light switch is used to control the LED lamp, this block manages the timing of AC supply off/on period and uses a programmable state machine to dim the lamp according to the selected method. Eight states can be used to configure combinations of steps/levels or ramps of LED light level.

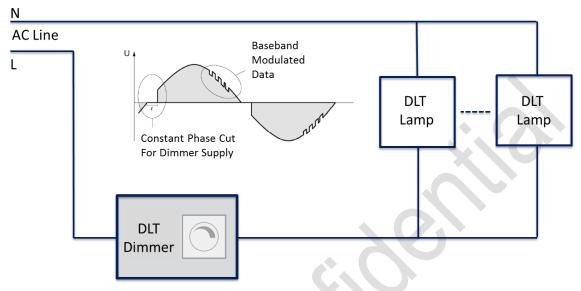

#### **DLT Receiver**

Receives modulated data via the AC supply input, this supports telegrams to control the LED current according to IEC 62756.

For good reception the VIN signal has to make full use of the 3V input range. Care must be taken in designing PCB layout to have low noise signals to reduce coupling from the flyback switching. The default register values can be used in most cases to get low reception error rates.

# **Digital Programmable LED Driver IC**

# 4 Chip Configuration and Programming

# 4.1 Pinout

Transparent top view

| Pin no. | Pin name | Type (Table 2) | Description                                                                                                                                                      |  |  |

|---------|----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | VSENSE   | AI             | Current sense input for flyback current.                                                                                                                         |  |  |

| 2       | VBUS     | AI             | Voltage sense input for flyback input voltage. Digitised by an 8-bit ADC with a 3V full scale range.                                                             |  |  |

| 3       | VIN      | HVI            | AC supply voltage sense input. During start up this pin is<br>used to charge VCC via a input resistor. Digitised by an 8-<br>bit ADC with a 3V full scale range. |  |  |

| 4       | NTC      | AI             | Input for external NTC temperature sensor. Connected to an internal current source of 100 $\mu$ A. Digitised by an 8-bit ADC with a 3V full scale range.         |  |  |

|         | SCL      | DI             | I <sup>2</sup> C-bus clock input. Requires external pull-up resistor.<br>When used as NTC input, I2C cannot be used.                                             |  |  |

| 5       | LDO_OUT  | AO             | Output of LDO regulator. Programmable output voltage of 2.5V, 3.0V, 3.3V or 3.6V                                                                                 |  |  |

| 6       | LDO_IN   | HVI            | Input for LDO regulator. Input voltage range from 5V to $V_{\text{CC\_LIM}}.$ Input threshold detect at 12.5V                                                    |  |  |

| 7       | T1S      | HVO            | Control signal for bypass load MOSFET. Connects to the source of the external MOSFET.                                                                            |  |  |

| 8       | T1G      | HVO            | Control signal for bypass load MOSFET. Connects to the gate of external MOSFET.                                                                                  |  |  |

| 9       | VCC      | PS             | Supply voltage (typ. 15 V). Requires external decoupling capacitor of $10\mu$ F to GND.                                                                          |  |  |

| 10      | T2G      | HVO            | Control signal for flyback MOSFET. Connects to the gate of external MOSFET.                                                                                      |  |  |

Table 1: Pin description

Datasheet

Version 3.0

#### **Company confidential**

# **Digital Programmable LED Driver IC**

| Pin no.        | Pin name | Type (Table 2) | Description                                                                                                                        |

|----------------|----------|----------------|------------------------------------------------------------------------------------------------------------------------------------|

| 11             | VAUX     | HVI            | Auxiliary voltage sense input. Connected to auxiliary winding of flyback transformer. Additionally used to charge VCC in run mode. |

| 12             | DATA     | DIO            | Serial data interface input/output. Requires external pull-<br>up resistor.                                                        |

|                | SDA      | DIO            | I <sup>2</sup> C-bus data input/output. Requires external pull-up resistor. When used as NTC input, I2C cannot be used.            |

| Exposed<br>pad | GND      | -              | Ground (0V). Common ground for all functions. Must be connected to PCB ground plane for thermal management.                        |

#### Table 2: Pin type definition

| Pin type | Description          | Pin type | Description         |

|----------|----------------------|----------|---------------------|

| DI       | Digital Input        | AI       | Analog Input        |

| DIO      | Digital Input/Output | PS       | Power Supply        |

| HVI      | High Voltage Input   | HVO      | High Voltage Output |

| AO       | Analog Output        |          |                     |

Note:

- The I2C and serial data interfaces have no internal pull-up resistors, When SDA/DATA or SCL pins are not used, connect them to GND or via a 100kΩ resistor to GND if communication interface is removable.

- 2. If the bypass load is not used, leave pins T1G and T1S open.

- 3. If the VBUS input is not used, connect the pin to GND.

- 4. If the LDO is not used, connect LDO\_IN to GND and leave LDO\_OUT open.

### 4.2 Internal circuits

#### 4.2.1 Pin VCC: supply voltage

The VCC pin is the supply voltage (typically 15V) of the iW6401. All other supply voltages are generated internally, the analog circuits operating at approximately 5V. No external components are needed, except for the VCC decoupling capacitor, typically 10  $\mu$ F.

When VCC exceeds  $V_{CC LOCK}$  (17V) the iW6401 switches to run mode.

When VCC drops below  $V_{CC\_UVLO}$  (10V) the iW6401 switches to standby mode.

### 4.2.2 Pin DATA/SDA

The DATA/SDA pin is used for both I2C and serial data input/output. It has a Schmitt trigger input with enable function. The input circuit is designed to operate with external devices at supply voltages ranging from 2.5V to 5V; with a typical threshold voltage of 1.2 V.

Figure 6: Pin DATA/SDA internal circuit

### 4.2.3 Pin NTC/SCL

The NTC/SCL pin has an internal current source of  $100\mu$ A and is typically connected to an external  $10k\Omega$  or  $22k\Omega$  NTC thermistor, which gives a voltage between 0V and 3V (corresponding with the ADC range) at the temperatures of interest. This allows the temperature of the LED substrate to be measured and the output power to be controlled to maintain the maximum operating temperature; typically this is set at 85°C for an optimal LED life time.

Internally, the NTC voltage is digitised by the ADC with a 3V full scale range, and the resulting digital value logically inverted to give a positive slope with temperature, for use with the temperature event state machine and look-up table. Since the 100  $\mu$ A current source is internally supplied at 5V, the digitised code at low temperatures will be 00h (after inversion).

The NTC/SCL pin is used for the I2C clock input. It has a Schmitt trigger input with enable function. The input circuit is designed to operate with external devices at supply voltages ranging from 2.5V to 5V; with a typical threshold voltage of 1.2 V.

When the 100µA current source is turned on, the Schmitt trigger input is disabled.

**Note:** In I<sup>2</sup>C interface mode either uses the internal temperature sensor or uses an external processor to sense the temperature and control the relevant registers to reduce the output power and/or turn off the LED drive.

#### **Company confidential**

#### Figure 7: Pin NTC/SCL internal circuit

#### 4.2.4 Pins T1G and T1S: source controlled MOSFET driver

The iW6401 contains a Source Controlled MOSFET Driver (SCMD) at pins T1G (gate) and T1S (source) to realise the bypass load function. This is a programmable current source with the additional circuitry to give the fast charge capability. The output current has four ranges: up to 125mA, 250mA, 375mA and 550mA. Within each current range a 6-bit control parameter (ISET) sets the current in linear steps. This function controls the AC supply load current during DLT dimming. The current range and setting are programmable via the corresponding registers of the DLT state machine.

In standby mode the switch across the zener is opened and pin T1G is pulled approximately 11V above VCC to turn on the external MOSFET, while pin T1S charges the VCC decoupling capacitor via an internal diode (and a  $400\Omega$  resistor to limit the current). In run mode the switch is closed and T1G is connected to VCC.

|       | Iscmd (mA) |         |         |         |

|-------|------------|---------|---------|---------|

| Value | Range=0    | Range=1 | Range=2 | Range=3 |

| 0     | 0.0        | 0.0     | 0.0     | 0.0     |

| 1     | 3.7        | 7.3     | 11.0    | 14.6    |

| 2     | 6.6        | 13.3    | 19.9    | 26.6    |

| 3     | 9.5        | 19.0    | 28.4    | 37.9    |

| 4     | 12.2       | 24.4    | 36.6    | 48.8    |

| 5     | 14.9       | 29.7    | 44.6    | 59.5    |

| 6     | 17.5       | 35.0    | 52.5    | 70.0    |

| 7     | 20.1       | 40.1    | 60.2    | 80.2    |

| 8     | 22.6       | 45.2    | 67.8    | 90.4    |

| 9     | 25.1       | 50.2    | 75.3    | 100.4   |

| 10    | 27.6       | 55.2    | 82.8    | 110.4   |

| 11    | 30.1       | 60.1    | 90.2    | 120.2   |

| 12    | 32.5       | 65.0    | 97.5    | 130.0   |

| 13    | 34.9       | 69.9    | 104.8   | 139.7   |

| 14    | 37.3       | 74.7    | 112.0   | 149.3   |

| 15    | 39.7       | 79.5    | 119.2   | 158.9   |

| 16    | 42.1       | 84.2    | 126.3   | 168.4   |

| 17    | 44.5       | 88.9    | 133.4   | 177.8   |

| 18    | 46.8       | 93.6    | 140.5   | 187.3   |

| 19    | 49.2       | 98.3    | 147.5   | 196.6   |

| 20    | 51.5       | 103.0   | 154.4   | 205.9   |

| 21    | 53.8       | 107.6   | 161.4   | 215.2   |

| 22    | 56.1       | 112.2   | 168.3   | 224.4   |

The following table lists the typical SCMD current values for Cur\_Value, for all four Cur\_Range=0,1,2,3.

#### Datasheet

Version 3.0

22-May-2015

## **Company confidential**

|       | Iscmd (mA) |         |         |         |

|-------|------------|---------|---------|---------|

| Value | Range=0    | Range=1 | Range=2 | Range=3 |

| 23    | 58.4       | 116.8   | 175.1   | 233.5   |

| 24    | 60.7       | 121.4   | 182.1   | 242.8   |

| 25    | 63.0       | 126.0   | 188.9   | 251.9   |

| 26    | 65.3       | 130.5   | 195.8   | 261.0   |

| 27    | 67.5       | 134.9   | 202.4   | 269.9   |

| 28    | 69.8       | 139.6   | 209.3   | 279.1   |

| 29    | 72.0       | 144.0   | 216.0   | 288.0   |

| 30    | 74.3       | 148.5   | 222.8   | 297.1   |

| 31    | 76.5       | 153.0   | 229.5   | 306.0   |

| 32    | 78.7       | 157.4   | 236.1   | 314.8   |

| 33    | 80.9       | 161.9   | 242.8   | 323.7   |

| 34    | 83.2       | 166.4   | 249.6   | 332.8   |

| 35    | 85.4       | 170.8   | 256.2   | 341.6   |

| 36    | 87.6       | 175.2   | 262.8   | 350.4   |

| 37    | 89.8       | 179.6   | 269.4   | 359.2   |

| 38    | 92.0       | 184.0   | 276.0   | 368.0   |

| 39    | 94.2       | 188.4   | 282.6   | 376.8   |

| 40    | 96.4       | 192.8   | 289.2   | 385.6   |

| 41    | 98.6       | 197.2   | 295.7   | 394.3   |

| 42    | 100.8      | 201.6   | 302.4   | 403.2   |

| 43    | 102.9      | 205.8   | 308.7   | 411.6   |

| 44    | 105.1      | 210.2   | 315.3   | 420.4   |

| 45    | 107.3      | 214.6   | 321.9   | 429.2   |

| 46    | 109.4      | 218.8   | 328.2   | 437.6   |

| 47    | 111.6      | 223.2   | 334.8   | 446.4   |

| 48    | 113.7      | 227.4   | 341.1   | 454.8   |

| 49    | 115.9      | 231.8   | 347.7   | 463.6   |

| 50    | 118.0      | 236.0   | 354.0   | 472.0   |

| 51    | 120.2      | 240.4   | 360.6   | 480.8   |

| 52    | 122.3      | 244.6   | 366.9   | 489.2   |

| 53    | 124.4      | 248.8   | 373.2   | 497.6   |

| 54    | 126.6      | 253.2   | 379.8   | 506.4   |

| 55    | 128.7      | 257.4   | 386.1   | 514.8   |

| 56    | 130.8      | 261.6   | 392.4   | 523.2   |

| 57    | 132.9      | 265.8   | 398.7   | 531.6   |

| 58    | 135.0      | 270.0   | 405.0   | 540.0   |

| 59    | 137.1      | 274.2   | 411.3   | 548.4   |

| 60    | 139.3      | 278.6   | 417.9   | 557.2   |

| 61    | 141.4      | 282.8   | 424.2   | 565.6   |

| 62    | 143.5      | 287.0   | 430.5   | 574.0   |

| 63    | 145.6      | 291.2   | 436.8   | 582.4   |

Datasheet

**Company confidential**

Figure 8: Pins T1G and T1S internal circuit

## 4.2.5 Pin T2G: flyback driver output

The T2G pin is a push-pull driver operating from the VCC supply voltage, driving the gate of the external flyback MOSFET. The driver has a typical source impedance of  $50\Omega$ .

### 4.2.6 Internal temperature sensor

The internal temperature sensor is available for power de-rating and safety shutdown. The high and low temperature thresholds are programmable using the corresponding registers in the temperature event state machine.

**Note:** In order to select an external NTC as the temperature sensor the register TEMP\_NTC has to be set accordingly. The external NTC sensor value or the internal temperature sensor value can be used by the temperature control state machine and is used for power de-rating. The internal temperature sensor is always used for the over-temperature shut down.

| Register | Description                                                                                       |

|----------|---------------------------------------------------------------------------------------------------|

| TEMP_NTC | Configure system for use of external temperature sensor.<br>I2C cannot be used for communication. |

|    | ata |     |     | 4  |

|----|-----|-----|-----|----|

| IJ | ara | ISI | lee | Т. |

|    |     |     |     |    |

# 4.2.7 Pins LDO\_IN, LDO\_OUT

The internal voltage regulator (LDO) supplies power to an external wireless module or microprocessor for remote control of the LED dimming. The regulator requires a minimum load capacitance of 10µF on pin LDO\_OUT.

The LDO has a programmable output voltage of 2.5V, 3.0V, 3.3V or 3.6V. Internally the driver stage is supplied from VCC and only the output stage from pin LDO\_IN. This allows the dissipated power in the output stage to be optimised depending on the load current requirement.

Figure 10: Pins LDO\_IN and LDO\_out internal circuit

The LDO output current can be up to 500mA for  $V_{LDO_IN} = 15$  V and  $V_{CC} = 15$  V. Figure 11 shows the rated output current capability as a function of  $V_{CC}$  for  $V_{LDO_IN}=5$ V. Below VCC=10V the current capability drops until the output is limited by the input supply voltage. Note that any external circuit that requires power to maintain operation when VCC<10V must limit its operating current (i.e. use a sleep mode).

The total dissipated power ( $P_{TOT}$ ) for the DFN12 package must be limited to keep the junction temperature below 125°C. Refer to application guidelines for PCB design recommendations.

|     | LDO setting |        |        |        |

|-----|-------------|--------|--------|--------|

| VCC | 2.5         | 3      | 3.3    | 3.6    |

| 17  | >500mA      | >500mA | >500mA | >500mA |

| 15  | >500mA      | >500mA | >500mA | >500mA |

| 12  | >500mA      | >500mA | >500mA | >500mA |

| 10  | >100mA      | >100mA | >100mA | >100mA |

| 9   | >100mA      | >100mA | >100mA | >100mA |

| 8   | >100mA      | >100mA | 87mA   | 43mA   |

| 7   | >100mA      | 33mA   | 5mA    | 3,34V  |

| 6   | 15mA        | 2.70V  | 2.70V  | 2.70V  |

Figure 11: Typical LDO output current vs. V<sub>LDO\_IN</sub> and V<sub>CC</sub>

### **Configuring the LDO**

The LDO is configured using the register LDO\_CONFIG.

The following options can be configured:

- Output voltage (2.5, 3.0, 3.3, 3.6V)

- Select LDO\_IN threshold detect before activating the output

- Enable LDO

| Register  | Description                                    |             |

|-----------|------------------------------------------------|-------------|

| LDO_CONF  | Configuration for LDO mode and output voltage. |             |

| Datasheet | Version 3.0                                    | 22-May-2015 |

# 4.3 Pin T2G: flyback driver output

The T2G pin is a push-pull driver operating from the VCC supply voltage, driving the gate of the external flyback MOSFET. The driver has a typical source impedance of about  $35\Omega$ .

# 4.4 Vin and Vbus Sense

The VIN input has 2 functions: to charge the VCC capacitor on start-up and standby mode, and provide AC supply voltage information in run mode.

Figure 12: Vin and Vbus Sensing Scheme

This block also contains the input circuitry for the VBUS pin.

The VBUS input digitizes the supply voltage to the fly-back converter; this is used as an input to the PI control loop in order to increase the PSRR to Ac supply voltage fluctuations. It requires an external potential divider as the voltage digitized by the ADC with a 3V full scale range.

The VIN input charges the VCC voltage when the RIN switch is open on start-up and standby mode. in run mode the switch is closed and the internal RIN forms a potential divider with the external resistor. The table shows the resistances that can be selected:

# Table 3: Selection of Resistors at Pin Vin

| Ctrl | RIN    |

|------|--------|

| 000  | 16kΩ   |

| 001  | 8kΩ    |

| 011  | 5.33kΩ |

| 111  | 4kΩ    |

| Register            | Description                                   |  |

|---------------------|-----------------------------------------------|--|

| VIN_RESISTOR_SELECT | Select one configuration for the Vin divider. |  |

| Datas | hoot |

|-------|------|

| Datas | neel |

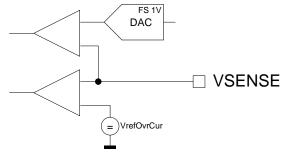

## 4.5 Pin VSENSE

The VSENSE/ICP\_EN pin is used to monitor the coil current in the flyback output stage via an external sense resistor. The pin has a peak coil current comparator programmable from 0 to 1V (set by the PI control loop) and an overcurrent detection comparator programmable from 0 to 3V.

Figure 13: Pin VSENSE

The overcurrent protection continuously monitors the peak current and immediately turns off the flyback MOSFET in overcurrent conditions. When the overcurrent condition remains for a longer time, the system state machine enters the stop mode.

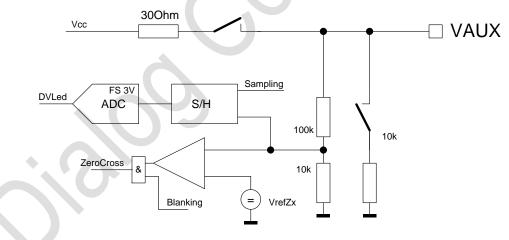

## 4.6 VAUX

The VAUX pin has three functions: to detect the coil zero-current condition to establish QR switching operation; to measure the LED voltage; to provide power to VCC.

Figure 14: Internal circuit at Vaux

The VAUX input has a HV switch to isolate the input from the VCC supply; this allows the VAUX to be independent of VCC without taking any current. When the switch is open, the VAUX input is loaded by a fixed  $10k\Omega$  resistor to ensure that the measured signal follows the voltage of the auxiliary winding.

During measure cycles the zero cross of the secondary current of the converter is detected by sensing the falling edge at VAUX. The measurement and zero-cross comparator are connected to an 11:1 potential divider, so giving a 32V input capability at the pin.

The reference value for the zero cross detection is set using the register VAUX\_VREF\_ZX.

| Datasheet | Version 3.0 | 22-May-2015 |

|-----------|-------------|-------------|

|           |             |             |

The divided voltage at Vaux is sampled and held using a fixed time delay after the negative edge of T2G. The time is set using the register VAUX\_TSTART\_SHVLED. Please be aware that the real LED voltage is measured indirectly and several terms have to be taken into account to scale this to the actual voltage:

- The voltage drop across 2 diodes

- The internal voltage divider

- The turns ration between Nsec and Naux

- The 8-bit ADC conversion with 3V full scale

In order to prevent from premature detection of zero cross a blanking time is set after the falling edge of T2G. During this time no zero cross event is detected.

The logic that controls the Vaux processing switches between charge and measure cycles. During measure cycles a normal zero-cross is performed and the  $V_{LED}$  is measured. During charge cycles the switch to VCC is closed and no sensing takes place. The default register settings does a sequence of 1 measure and 3 charge cycles.

| Register           | Description                                  |

|--------------------|----------------------------------------------|

| VAUX_VREF_ZX       | Set the reference voltage for the zero cross |

| VAUX_TSTART_SHVLED | Set the sampling time for the LED voltage    |

| VAUX_BLANK_OFF     | Set the blanking times for zero cross.       |

**Company confidential**

# **Digital Programmable LED Driver IC**

# 5 Absolute maximum ratings

#### Table 4: Absolute maximum ratings

| Symbol                        | Parameter                       | Conditions                                                              | Min                                             | Max                                         | Unit                       |

|-------------------------------|---------------------------------|-------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------|----------------------------|

| T <sub>STG</sub>              | storage temperature             |                                                                         | -65                                             | 150                                         | °C                         |

| TJ                            | junction temperature            |                                                                         | -40                                             | +125                                        | °C                         |

| V <sub>CC_LIM</sub>           | limiting supply voltage         | Pin: VCC                                                                | -0.3                                            | 25                                          | V                          |

| V <sub>HV_LIM</sub>           | limiting voltage (HV pins)      | Pins:<br>T1S<br>T1G (5mA max)<br>T2G<br>VIN (5mA max)<br>VAUX<br>LDO_IN | -0.3<br>VCC-0.3<br>-0.3<br>-0.3<br>-0.3<br>-0.3 | VCC+5<br>32<br>VCC+0.3<br>VCC+5<br>32<br>32 | V<br>V<br>V<br>V<br>V<br>V |

| $V_{\text{LV}\_\text{LIM}}$   | limiting voltage (LV pins)      | Pins: DATA/SDA, NTC/SCL,<br>VBUS, VSENSE                                | -0.3                                            | 5.5                                         | V                          |

| I <sub>CC_MAX</sub>           | maximum supply current          | V <sub>CC</sub> = 25 V                                                  | -                                               | 30                                          | mA                         |

| $V_{\text{ESD}_{\text{HBM}}}$ | electrostatic discharge voltage | Human Body Model;<br>JS-001-2012, Class 1B                              | -2000                                           | +2000                                       | V                          |

| $V_{ESD\_CDM}$                | electrostatic discharge voltage | Charged Device Model;<br>JESD22-C101C, Class II                         | -500                                            | +500                                        | V                          |

Stresses beyond those listed under "Absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, so functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 6 Recommended operating conditions

| Symbol              | Parameter                             | Conditions                                                                                                          | Min  | Тур | Max                | Unit |

|---------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|-----|--------------------|------|

| TJ                  | junction temperature                  |                                                                                                                     | -30  | -   | 125                | °C   |

| T <sub>JPROG</sub>  | junction temp for chip<br>programming | any OTP write access                                                                                                | -30  |     | 85                 | °C   |

| V <sub>cc</sub>     | supply voltage                        |                                                                                                                     | 12   | 15  | 17                 | V    |

| V <sub>LDO_IN</sub> | Regulator supply                      |                                                                                                                     |      | 15  |                    | V    |

| Vin_ramp            | input voltage during start<br>up      | supply ramp up                                                                                                      | -0.3 | -   | V <sub>CC</sub> +5 | V    |

| Vin_oper            | input voltage during operation        | Operating                                                                                                           | -0.3 | -   | 3.6                | V    |

| V <sub>AUX</sub>    | auxiliary winding voltage             |                                                                                                                     | -0.3 | -   | 28                 | V    |

| V <sub>SENSE</sub>  | current sensing voltage               |                                                                                                                     | -0.3 | -   | 1.1                | V    |

| V <sub>BUS</sub>    | Bus voltage sensing                   |                                                                                                                     | -0.3 | -   | 3.6                | V    |

| P <sub>DIS</sub>    | Expected power dissipation            | $V_{CC}=15V, V_{LDO_{IN}}=15V$<br>$V_{LDO_{OUT}}=3.0V, 2mA \ load$<br>No SCMD current<br>$V_{AUX}=28V, 50\% \ duty$ |      | 120 |                    | mW   |

### Table 5: Recommended operating conditions

#### Datasheet

Version 3.0

# 7 Electrical characteristics

#### **Table 6: Electrical characteristics**

Unless otherwise stated,  $T_J$ =-30°C to +125°C. Typical  $T_J$ =25°C.

| Symbol                       | Parameter                                | Conditions                                                                                                      | Min  | Тур               | Max  | Unit                      |

|------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|-------------------|------|---------------------------|

| Supply (pi                   | n VCC)                                   |                                                                                                                 |      |                   |      |                           |

| V <sub>CC_LOCK</sub>         | lock-in supply voltage                   | Initial power up                                                                                                | 16.5 | 17.2              | 18.0 | V                         |

|                              |                                          | Re-start after switch event                                                                                     | -1%  | 17.0              | +1%  | V                         |

| V <sub>CC_UVLO</sub>         | under-voltage lock-out<br>supply voltage |                                                                                                                 | -1%  | 10.0              | +1%  | V                         |

| $V_{CC\_CL}$                 | clamping supply voltage                  |                                                                                                                 | -    | 18.5              |      | V                         |

| R <sub>CC_CL</sub>           | Clamping resistance                      |                                                                                                                 |      | 5                 |      | kΩ                        |

| $V_{CC\_POR}$                | power-on reset                           |                                                                                                                 | -1%  | 5.0               | +1%  | V                         |

| Icc                          | supply current                           | Active state                                                                                                    | -    | 3.3               | 5    | mA                        |

| I <sub>CC_OFF</sub>          | off-state supply current                 | Vcc charge state                                                                                                |      | 35                | 70   | μΑ                        |

| $C_{\text{DEC}\_\text{VCC}}$ | decoupling capacitance                   | from pin VCC to GND;<br>$V_{CC} = 15 V$ ; Note 1                                                                | 3.3  | 10                | 100  | μF                        |

| AC supply                    | sensing (pin VIN)                        |                                                                                                                 |      |                   |      |                           |

| $V_{\text{ADC}_{VIN}}$       | ADC conversion range                     |                                                                                                                 | 0    | -                 | 3    | V                         |

| $V_{\text{IK}_{\text{VIN}}}$ | input clamp voltage                      | I <sub>IN</sub> = 1 mA                                                                                          | 5.5  | -                 | 5.9  | V                         |

| I <sub>IK_VIN</sub>          | input clamp current                      | V <sub>IN</sub> = 5 V                                                                                           | -    | -                 | 0.26 | mA                        |

| I <sub>CHG_VIN</sub>         | charge current (V <sub>CC</sub> )        | V <sub>IN</sub> < 32 V; V <sub>CC</sub> = 15 V                                                                  | -    | -                 | 5    | mA                        |

| RI_VIN_NOM                   | input resistance                         | V <sub>IN</sub> = 3 V; T <sub>J</sub> = 25 °C;<br>VIN_RESISTOR_SELECT=0                                         | 15.2 | 16                | 16.8 | kΩ                        |

| R <sub>I_VIN_TC</sub>        | TC of input resistance                   | R <sub>VIN</sub> =(TC2*(TJ-25) <sup>2</sup><br>+ TC1*(TJ-25))*RI_VIN_nom                                        |      | -2.5e-5<br>4.3e-7 |      | /°C<br>/(°C) <sup>2</sup> |

| SCMD con                     | trol (pins T1G and T1S)                  |                                                                                                                 |      | 1                 |      |                           |

| I <sub>Z_T1G</sub>           | zener current                            | V <sub>T1G</sub> < 32 V; V <sub>CC</sub> = 15 V                                                                 | -    | -                 | 5    | mA                        |

| V <sub>Z_T1G</sub>           | zener voltage                            | T <sub>J</sub> = 25 °C<br>I <sub>Z_T1G</sub> =5mA                                                               | 9.6  | 10.5              | 11.1 | V                         |

| V <sub>Z_T1G_TC</sub>        | TC of zener voltage                      |                                                                                                                 |      | -23               |      | mV/°C                     |

| I <sub>CHG_T1S</sub>         | charge current (V <sub>cc</sub> )        | $V_{T1S} = VCC+5 V; V_{CC} = 15 V$                                                                              | -    | -                 | 20   | mA                        |

| RDLT                         | DLT load during power up                 | V <sub>CC</sub> < V <sub>CC_LOCK</sub>                                                                          |      | 1.2               |      | kΩ                        |

| I <sub>S_T1S</sub>           | source current                           | CUR_RANGE = 00b;<br>IDAC = 100000b;<br>V <sub>CC</sub> = 15 V; V <sub>T1S</sub> =10V;<br>T <sub>J</sub> = 25 °C | 73   | 76.5              | 81   | mA                        |

| I <sub>S_R0</sub>            | source current<br>DLT_CUR_RANGE = 0      | IDAC=01d                                                                                                        |      | 2.93              |      | mA                        |

| I <sub>S_R1</sub>            | source current<br>DLT_CUR_RANGE = 1      | IDAC=01d                                                                                                        |      | 5.86              |      | mA                        |

| I <sub>S_R2</sub>            | source current<br>DLT_CUR_RANGE = 2      | IDAC=01d                                                                                                        |      | 8.79              |      | mA                        |

#### Datasheet

Version 3.0

# Digital Programmable LED Driver IC

## **Company confidential**

| Symbol                      | Parameter                                    | Conditions                                                                                      | Min  | Тур    | Max  | Unit  |

|-----------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------|------|--------|------|-------|

| I <sub>S_R3</sub>           | source current<br>DLT_CUR_RANGE = 3          | IDAC=01d                                                                                        |      | 11.72  |      | mA    |

| I <sub>S_MAX_T1S</sub>      | maximum source current                       | $V_{T1S} = 10 \text{ V};$ $T_{J\_MAX} \text{ must not be exceeded}$                             | 500  | 560    | -    | mA    |

| I <sub>S_TC</sub>           | TC of source current                         |                                                                                                 |      | -0.035 |      | %/°C  |

| Flyback se                  | ensing (pin VSENSE)                          |                                                                                                 |      |        |      |       |

| $V_{\text{OV}\_\text{SNS}}$ | Over-voltage threshold                       | Default value                                                                                   |      | 1.0    |      | V     |

| I <sub>I_VSENSE</sub>       | input leakage current (pin<br>VSENSE/ICP_EN) | V <sub>SENSE</sub> = 1 V                                                                        | -    | -      | 0.1  | μA    |

| Flyback co                  | ontrol (pin T2G)                             |                                                                                                 |      |        |      |       |

| R <sub>OH_T2G</sub>         | HIGH level output resistance                 |                                                                                                 | 22   | 35     | 58   | Ω     |

| $R_{OL\_T2G}$               | LOW level output resistance                  | $V_{T2G} = 0.3 \text{ V}; V_{CC} = 15 \text{ V}$                                                | 21   | 32     | 54   | Ω     |

| Bus voltag                  | je sensing (pin VBUS)                        | •                                                                                               |      |        |      |       |

| V <sub>ADC_BUS</sub>        | ADC conversion range                         |                                                                                                 | 0    | -      | 3    | V     |

| I <sub>IK_VBUS</sub>        | input clamp current                          | V <sub>BUS</sub> = 5 V                                                                          | 0.26 | -      | -    | mA    |

| I <sub>I_VBUS</sub>         | input leakage current (pin<br>VBUS)          | V <sub>BUS</sub> = 3 V                                                                          | 5    | -      | 0.1  | μΑ    |

| Auxiliary v                 | vinding sensing (pin VAUX)                   |                                                                                                 |      |        |      |       |

| VDR <sub>VAUX</sub>         | voltage divider ratio                        |                                                                                                 | 10.8 | 10.9   | 11.0 | ratio |

| V <sub>ADC_AUX</sub>        | ADC conversion range                         | After voltage divider                                                                           | 0    | -      | 3    | V     |

| R <sub>L_VAUX</sub>         | Internal load impedance                      | $V_{AUX} = 3 V \text{ to } 25 V;$<br>$V_{CC} = 10 V \text{ to } 17.5 V$                         | 8.5  | 9.2    | 10   | kΩ    |

| $R_{SW\_CHG}$               | charge switch resistance                     | V <sub>CC</sub> = 15 V;<br>I <sub>CHG</sub> = 10 mA                                             | 20   | 32     | 55   | Ω     |

| NTC curre                   | nt source (pin NTC/SCL)                      |                                                                                                 |      |        |      |       |

| I <sub>O_NTC</sub>          | NTC output current                           | $R_{NTC} = 20 \ k\Omega$                                                                        | 96   | 99     | 102  | mA    |

| $V_{ADC\_NTC}$              | ADC conversion range                         |                                                                                                 | 0    | -      | 3    | V     |

| I <sub>I_NTC</sub>          | input leakage current                        | NTC current source disabled                                                                     | -    | -      | 0.1  | μA    |

| Digital inp                 | ut/output pins                               |                                                                                                 |      |        |      |       |

| VIH                         | HIGH level input voltage                     | Pins: DATA/SDA, NTC/SCL                                                                         | 2.25 | -      | 3.96 | V     |

| V <sub>IL</sub>             | LOW level input voltage                      | Pins: DATA/SDA, NTC/SCL                                                                         | -    | -      | 0.3  | V     |

| V <sub>OL</sub>             | LOW level output voltage                     | Pin DATA/SDA; I <sub>OL</sub> = 2 mA                                                            | -    | 0.37   | 0.6  | V     |

| LDO regula                  | ator                                         |                                                                                                 |      |        |      |       |

| $V_{\text{IT\_LDO}}$        | input threshold voltage                      |                                                                                                 | -2%  | 12.5   | +2%  | V     |

| $V_{LDO_2V5}$               | LDO output voltage                           | MODE = 00b                                                                                      | 2.43 | 2.5    | 2.58 | V     |

| $V_{LDO_3V0}$               | LDO output voltage                           | MODE = 01b                                                                                      | 2.91 | 3.0    | 3.09 | V     |

| $V_{LDO_3V3}$               | LDO output voltage                           | MODE = 10b                                                                                      | 3.20 | 3.3    | 3.40 | V     |

| $V_{LDO_3V6}$               | LDO output voltage                           | MODE = 11b                                                                                      | 3.49 | 3.6    | 3.71 | V     |

| I <sub>LDO_10V</sub>        | LDO output current                           | $V_{LDO_{IN}} = 15 \text{ V}; V_{CC} = 10 \text{ V}$<br>T <sub>J_MAX</sub> must not be exceeded |      |        | 100  | mA    |

#### Datasheet

Version 3.0

22-May-2015

# **Digital Programmable LED Driver IC**

### **Company confidential**

| Symbol              | Parameter                  | Conditions                                           | Min | Тур    | Max | Unit |

|---------------------|----------------------------|------------------------------------------------------|-----|--------|-----|------|

| ILDO_15V            | LDO output current         | $V_{LDO_{IN}} = 15 \text{ V}; V_{CC} = 15 \text{ V}$ |     |        | 500 | mA   |

|                     |                            | $T_{J\_MAX}$ must not be exceeded                    |     |        |     |      |

| System              |                            |                                                      |     |        |     |      |

| f <sub>CLK_HS</sub> | high speed clock frequency | main system clock                                    |     | 40     |     | MHz  |

|                     | TC of system clock         |                                                      |     | +0.045 |     | %/°C |

| f <sub>CLK_LS</sub> | low speed clock frequency  | event counter clock                                  | -3% | 16     | +3% | kHz  |

|                     | TC of event clock          |                                                      |     | +0.078 |     | %/°C |

| ADCrange            | ADC conversion range       | Code 00h                                             |     | 0      |     | V    |

|                     |                            | Code FFh                                             | -1% | 3.0    | 1%  |      |

| ADC <sub>DNL</sub>  | ADC DNL                    | VIN, VBUS                                            | -2  |        | 2   | LSB  |

|                     |                            | NTC, VTEMP, VAUX                                     | -1  |        | 1   | LSB  |

**Note 1** Decoupling capacitor value is application dependent.

# 8 Thermal characteristics

#### Table 7: Thermal characteristics

| Symbol               | Parameter                                   | Conditions            | Тур | Unit |

|----------------------|---------------------------------------------|-----------------------|-----|------|

| R <sub>TH(J-A)</sub> | thermal resistance from junction to ambient | iW6401 mounted on PCB | 74  | °C/W |

**Note 1** A detailed description of the thermal performance and PCB layout requirements will be given in an application note. Contact Dialog for example PCB layout.

The exposed pad of the chip must be soldered on a grounded copper plane with a minimum area of 50mm<sup>2</sup>.

The total power dissipated inside the chip is given by:

- (i) The power dissipation of the signal processing system

- (ii) The power losses inside the LDO supply the external communcation module

- (iii) The power dissipated inside the source controlled mosfet driver.

Given by the thermal coupling to the environment and the power dissipated inside the chip temperature is set and may not exceed the maximum rated chip temperature at any time.

# 9 Functional description

## 9.1 Overview

The iW6401 uses a single stage flyback configuration to convert the AC supply voltage into a DC current for driving LEDs. A true dimming range from 100 % down to 1 % is realised by linearly reducing the flyback current and at low dimming levels by pulse width modulation.

The integrated Source Controlled MOSFET Driver can be used as a bypass load current sink or load current shunt for DLT dimming applications.

All analog input and output signals are digitally controlled. Multiple 8-bit ADC channels with a 3V full scale are used. State machines control the operation of the various functions. Two internal oscillators (16kHz and 40MHz) provide the clock signals for the digital core.

Precise control of the LED current uses patented numerical methods, including measurement of the flyback input voltage ( $V_{BUS}$ ) to improve the Power Supply Rejection Ratio (PSRR). This reduces visible LED noise (flicker) even at high AC supply voltage variations and substantially extends the dynamic range of the bus voltage allowing the use of small capacitors.

Dimming can be controlled via light switching, via a serial/I2C data interface or via an IEC 62756 Digital Load side Transmission (DLT) slave interface.

An integrated LDO regulator provides a programmable supply voltage between 2.5 V and 3.6 V for peripheral devices such as wireless communication modules, microcontrollers or intelligent sensors.

Configuration settings are controlled via registers which have default reset values, any register value can be changed by storing the new value in OTP (loaded during power up). Additionally any register can be changed by the serial/I2C interface. The OTP can be programmed via the serial/I2C interface. This allows pre-assembly calibration of the LED driver circuit. Post-assembly calibration of the LED lamp is supported via a AC supply modulation interface.

The iW6401 can be configured for different AC supply voltages between 90 V to 260 V by choosing appropriate external HW components.

# 9.2 Register read/write and OTP Programming

All functions inside the iW6401 are fully programmable. Programming can be done on 2 levels:

- Reading / Writing to the register array using I2C communication. Register can be read and written any time also during operation of the device. A range of registers is available to read internal values. Please refer to the register map for more details. Any content of the register array is overwritten the next time the device resets and all register values will be overwritten by OTP values.

- This mode is very convenient to optimize the system on the fly by changing values during normal operation. Once a correct system configuration is found the values can be programmed into OTP.

- (ii) The OTP is organized as a freeform memory where each entry has an address and data information. The address can be any register. During startup of the device at first all registers are set to their default values. Then during initialization the content of the OTP is read and all corresponding registers are updated inside the Register array.

For both cases an ICP programmer us used together with a control SW that allows access to each individual register. A detailed description of all registers can be found in the USER memory map.

To protect any programming a locking scheme can be used. Please refer to the corresponding application note about locking features.

|    | itas |     | -  |

|----|------|-----|----|

| Da | паз  | sne | ет |

|    |      |     |    |

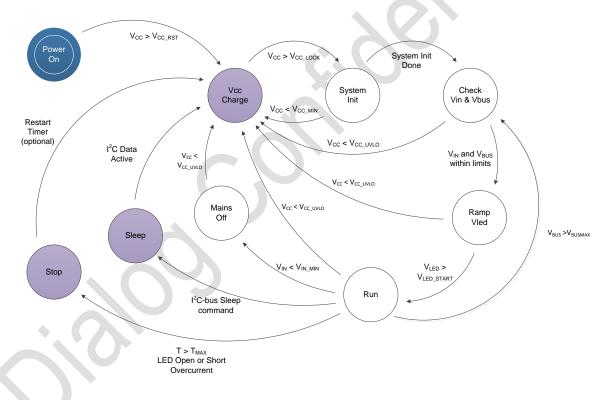

### 9.2.1 System State MachineSystem States

All operating modes of the chip are controlled via the main system state machine. The system state machine receives event signals from various external blocks and changes states accordingly. Each state uses one of three power modes:

- Reset Power mode: V<sub>CC</sub> below startup level, power-on reset active

- o States: PowerOn

- Low Power mode: V<sub>CC</sub> above startup level, event clock active, flyback stage not active

States: VccCharge, Stop, Sleep

- Normal Power mode: V<sub>CC</sub> within locking range, system and event clocks active, flyback stage active

- o States: SystemInit, RampVbus, RampVled, Run, MainsOff

The total power consumption in Normal Power mode depends on the activated features, operating frequencies and the applied power MOSFETs.

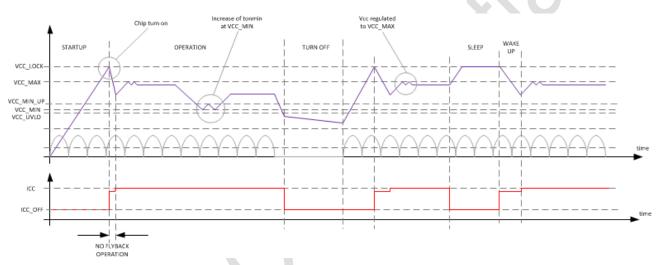

The state diagram in Figure 15 shows the power modes and how they are related via events and conditions.

#### Figure 15: Power modes state diagram

Legend:

- Dark Blue: Reset Power mode

- Cyan: Low Power mode

- White: Normal Power mode

| D | a | ta | s | h | е | et |

|---|---|----|---|---|---|----|

|   | a | La | 9 |   | C | Cι |

### 9.2.2 Configuring the state machine

When the chip is first powered on Vcc is charged up via either the external resistor at VIN or via the external active startup MOSFET or a combination of both. The state machine operates under control of several system flags:

| VinOk       | Vin(t)                                                                                                                                                                                    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | vin_tokmin vin_tnokmin<br>vin_min<br>Vin_min<br>VinOk                                                                                                                                     |

|             | Figure 16: Vin turn on conditions                                                                                                                                                         |

|             | VIN is converted to an 8-bit digital value with 3V full scale. A digital low-pass filter is applied to the samples for noise filtering.                                                   |

|             | VinOk is asserted when the VIN signal is above the 'vin_min' value for more than 'vin_tokmin' time and de-asserted when it is below the 'vin_min' value for more than 'vin_tnokmin' time. |

|             | Default values are 'vin_tokmin' = 1ms and 'vin_tnokmin'=4.8ms.                                                                                                                            |

|             | Note for correct start-up operation, 'vin_tokmin' should be greater than 100us                                                                                                            |