# ConnectCore®

for i.MX51

Hardware Reference Manual

## Revision history-90001128

| Revision | Date              | Description                                                                                                                                   |

|----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| М        | May, 2014         | Correct inaccuracy and sharpen clarity on the high temp start up issue.                                                                       |

| N        | November,<br>2014 | Miscellaneous editorial updates. Updated the voltages for the table in Coin cell input (VCC_COINCELL). Added a table of related publications. |

| Р        | June, 2017        | Updated branding and added statements for RED compliance.                                                                                     |

| R        | April, 2018       | Added coin cell input topic.                                                                                                                  |

| S        | January,<br>2019  | Added backdrive caution.                                                                                                                      |

# Trademarks and copyright

Digi, Digi International, and the Digi logo are trademarks or registered trademarks in the United States and other countries worldwide. All other trademarks mentioned in this document are the property of their respective owners.

© 2019 Digi International Inc. All rights reserved.

#### **Disclaimers**

Information in this document is subject to change without notice and does not represent a commitment on the part of Digi International. Digi provides this document "as is," without warranty of any kind, expressed or implied, including, but not limited to, the implied warranties of fitness or merchantability for a particular purpose. Digi may make improvements and/or changes in this manual or in the product(s) and/or the program(s) described in this manual at any time.

## Warranty

To view product warranty information, go to the following website:

www.digi.com/howtobuy/terms

## **Customer support**

**Gather support information:** Before contacting Digi technical support for help, gather the following information:

Product name and model

Product serial number (s)

Firmware version

Operating system/browser (if applicable)

Logs (from time of reported issue)

Trace (if possible)

Description of issue

Steps to reproduce

**Contact Digi technical support**: Digi offers multiple technical support plans and service packages. Contact us at +1 952.912.3444 or visit us at www.digi.com/support.

# **Feedback**

To provide feedback on this document, email your comments to

techcomm@digi.com

Include the document title and part number (ConnectCore for i.MX51 Hardware Reference Manual, 90001128 S) in the subject line of your email.

# Contents

# About the module

| Features and functionality         | 9  |

|------------------------------------|----|

| Module variant                     | 10 |

| Block diagram                      | 11 |

| CPU                                | 11 |

| Module                             | 11 |

| Module pinout                      | 13 |

| Pinout legend                      | 13 |

| Pinout definitions                 |    |

| J1 pinout                          |    |

| J2 pinout                          | 27 |

| Power                              |    |

| Module power supplies              | 41 |

| Supply inputs                      | 41 |

| Supply outputs                     |    |

| MC13892 power management           |    |

| Memory                             |    |

| DDR2 SDRAM memory                  |    |

| NAND flash memory                  |    |

| Chip selects                       |    |

| Chip select memory map             |    |

| Multiplexed GPIO                   | 46 |

| GPIO multiplexing table            |    |

| Interfaces                         |    |

| 1-Wire                             | 51 |

| Accelerometer                      |    |

| ADC and touch screen               | 51 |

| Synchronous Serial Interface (SSI) |    |

| External Memory Interface (EMI)    |    |

| Ethernet 1                         | 53 |

| Ethernet 2                         | 54 |

| I2C                                | 54 |

| Video subsystem                    |    |

| Video Processing Unit (VPU)        |    |

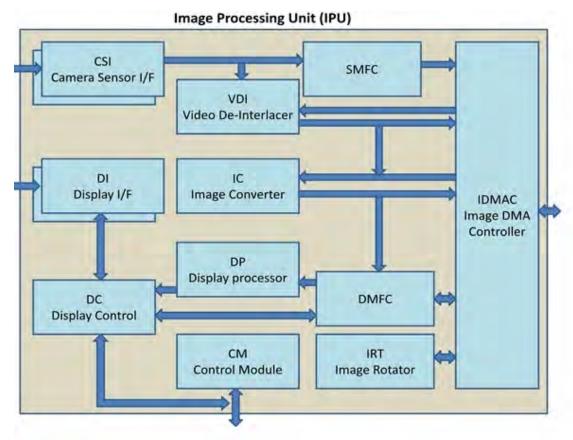

| Image Processing Unit (IPU)        |    |

| Keypad                             |    |

| Memory cards                       |    |

| PWM                                |    |

| RTC                                |    |

| SPDIF                              |    |

| SPI                                |    |

| Watchdog timer                         |    |

|----------------------------------------|----|

| UART                                   |    |

| USB Host and USB OTG                   |    |

| WLAN                                   | 61 |

|                                        |    |

| About the development board            |    |

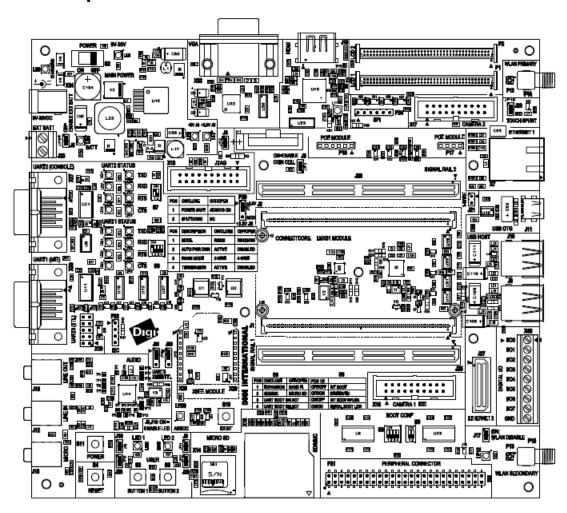

| About the development board            | 65 |

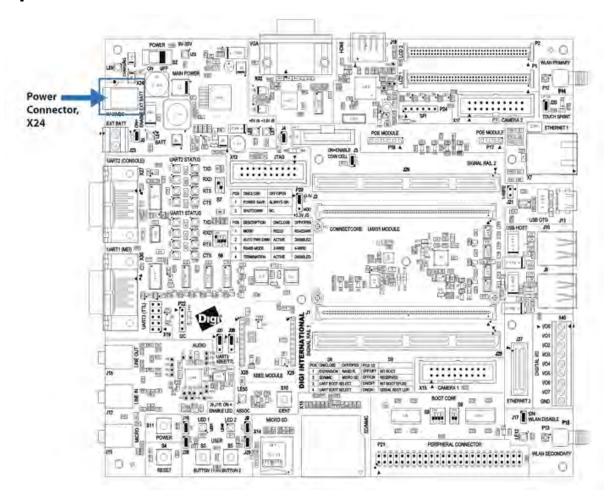

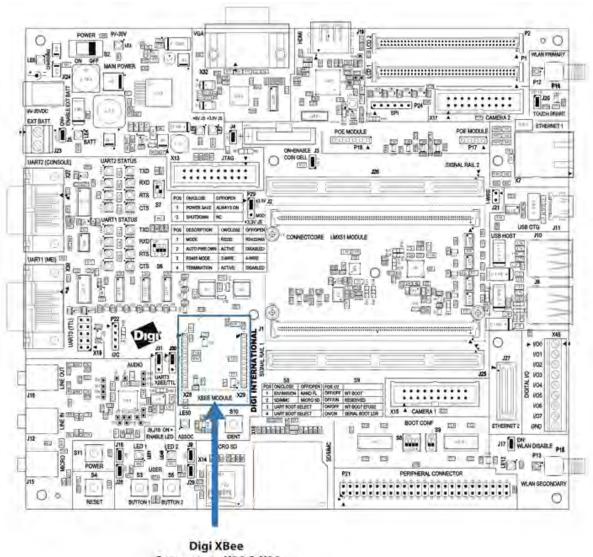

| The development board                  | 66 |

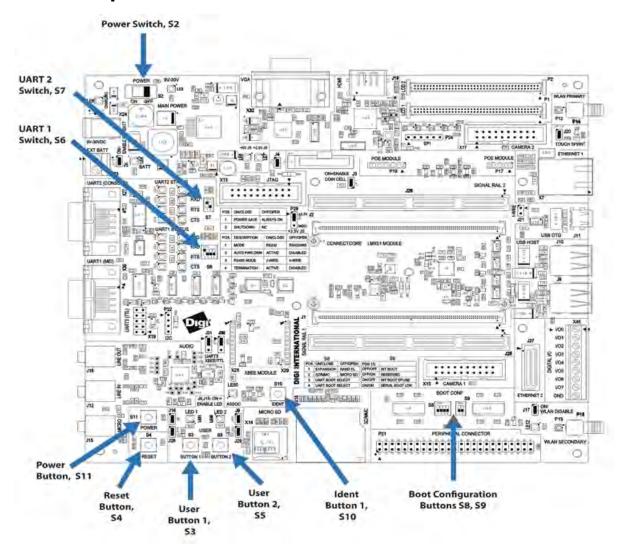

| Switches and push-buttons              |    |

| Power switch, S2                       |    |

| Reset button, S4                       | 67 |

| Power button, S11                      | 67 |

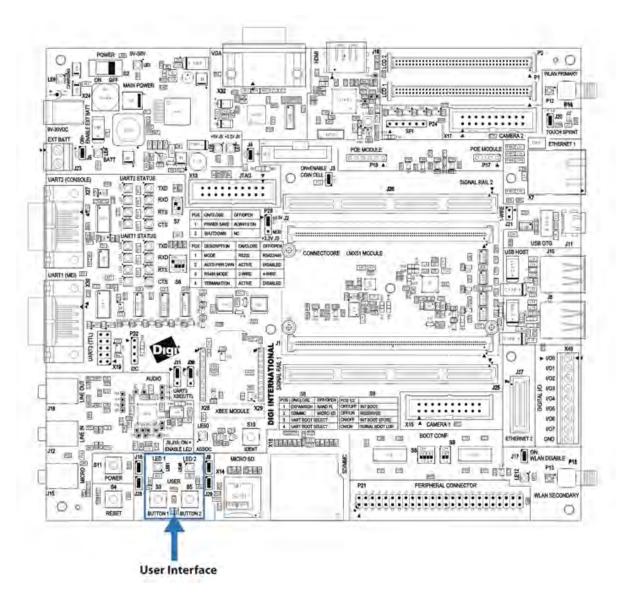

| User buttons, S3 and S5                |    |

| Ident button, S10                      |    |

| Legend for multi-position switches     |    |

| UART 1 switch, S6                      |    |

| UART 2 switch, S7                      | 69 |

| Boot configuration switches, S8 and S9 |    |

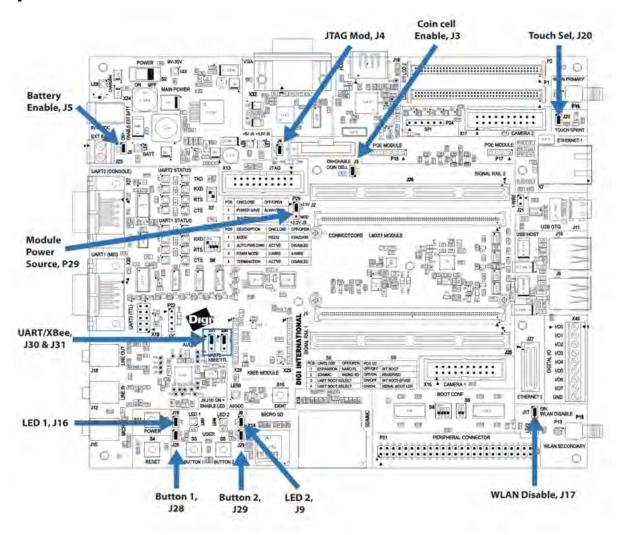

| Jumpers                                | 71 |

| Battery enable, J5                     | 71 |

| Module power source, P29               | 71 |

| LED 1, J16                             | 71 |

| LED 2, J9                              | 72 |

| Button 1, J28                          | 72 |

| Button 2, J29                          |    |

| UART3 / XBee selection, J30 and J31    |    |

| WLAN disable, J17                      | 72 |

| Touch selection, J20                   | 72 |

| Coincell enable, J3                    |    |

| JTAG mod., J4                          |    |

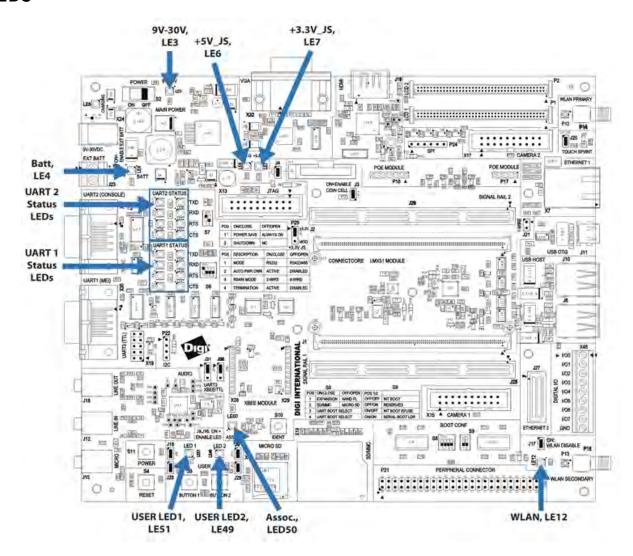

| LEDs                                   |    |

| WLAN, LE12                             |    |

| Power LEDs, LE3, LE4, LE6 and LE7      |    |

| User LEDs, LE49 and LE51               |    |

| Serial status LEDs                     |    |

| UART 1 status LEDs                     |    |

| UART 2 status LEDs                     |    |

| XBee Associate, LE50                   |    |

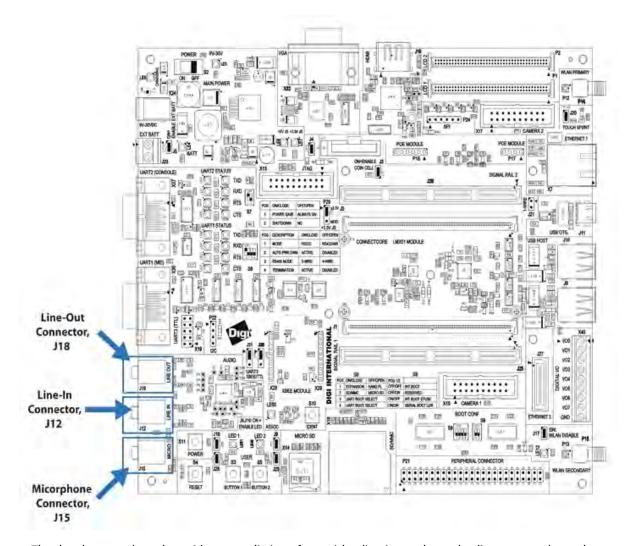

| Audio interface                        |    |

| Line-out connector pinout, J18         |    |

| Line-in connector pinout, J12          |    |

| Microphone connector pinout, J15       |    |

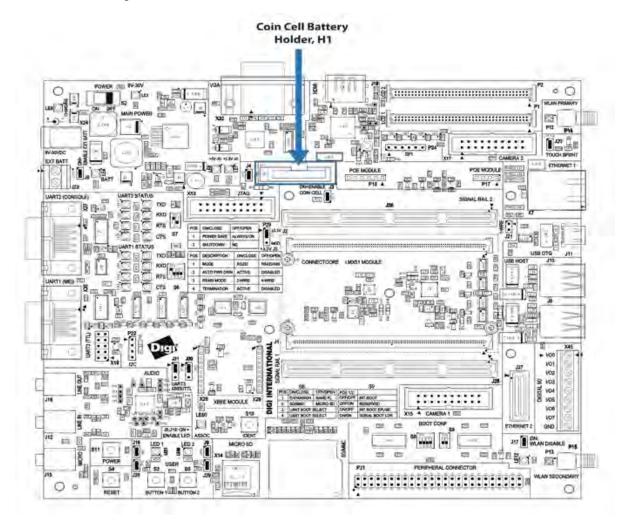

| Coin cell battery                      |    |

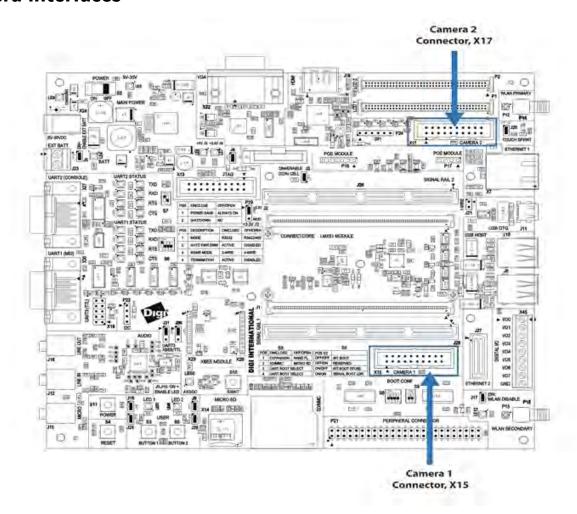

| Camera interfaces                      |    |

| X15 pinout                             |    |

| X17 pinout                             |    |

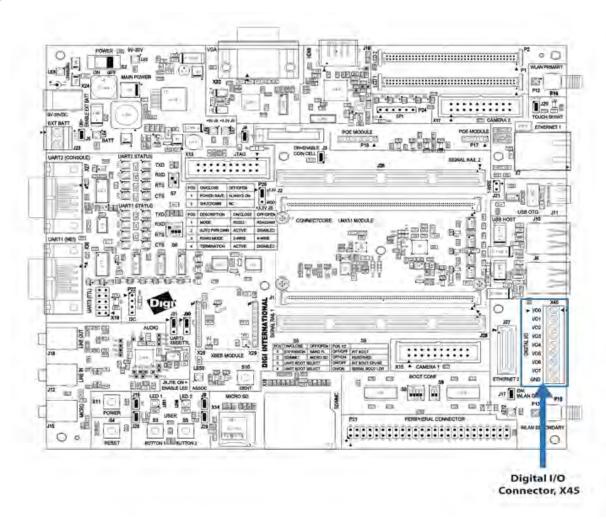

| Digital IO interface                   |    |

| Digital I/O connector, X45             |    |

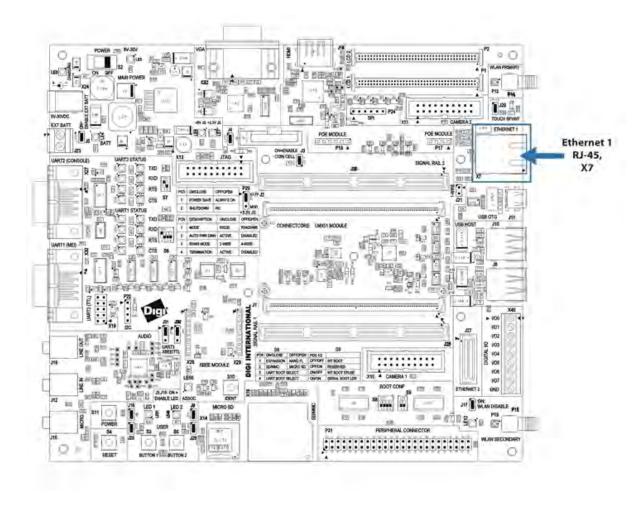

| Ethernet 1 interface                   | 81 |

| Ethernet 1, RJ-45 connector X7         |    |

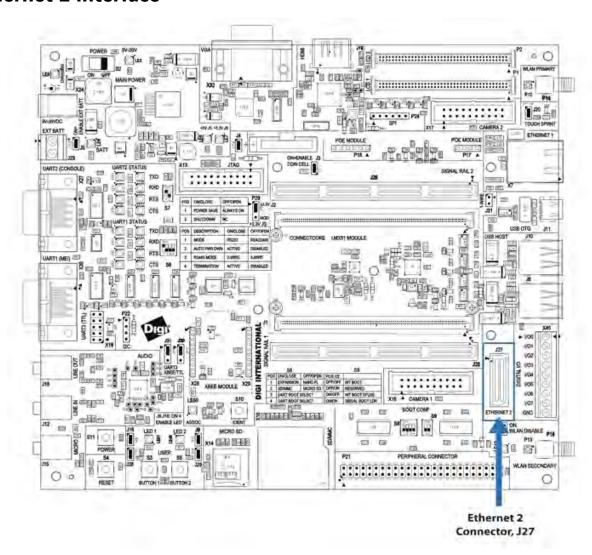

| Ethernet 2 interface                   |    |

| Ethernet 2, connector J17              |    |

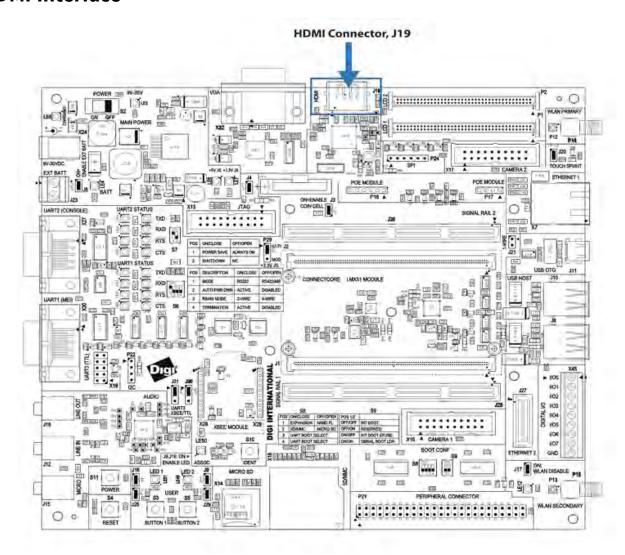

| HDMI interface                         |    |

| HDMI connector, J19                    | 85 |

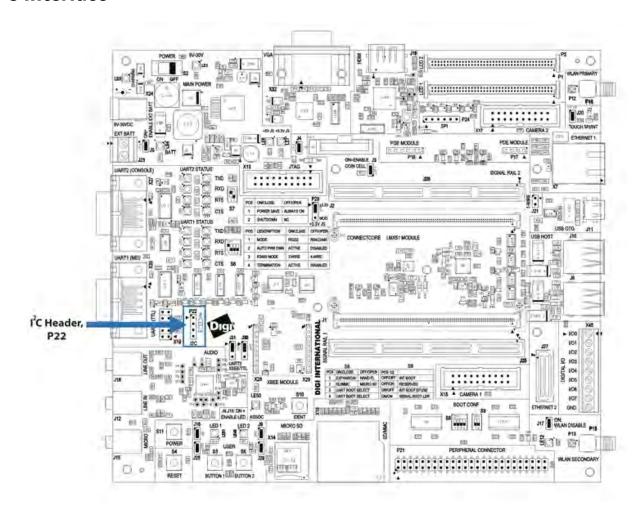

| I2C interface                                | 87  |

|----------------------------------------------|-----|

| I2C header, P22                              | 87  |

| JTAG interface                               | 89  |

| Standard JTAG ARM connector, X13             | 89  |

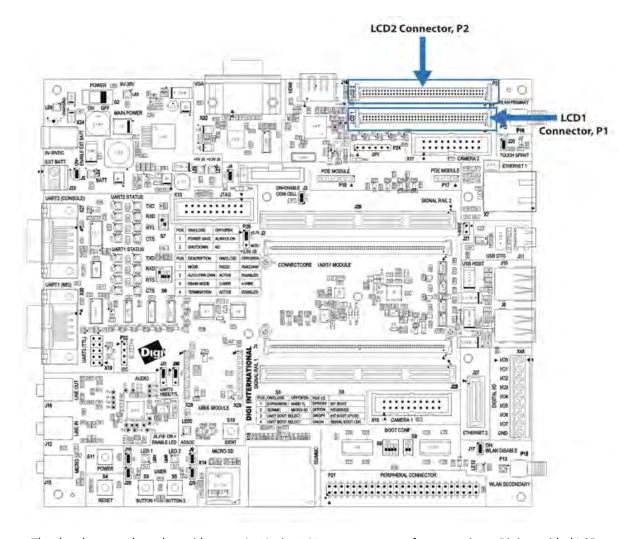

| LCD interfaces                               |     |

| LCD 1 connector, P1                          |     |

| P1 pinout                                    |     |

| LCD 2 connector, P2                          |     |

| P2 pinout                                    |     |

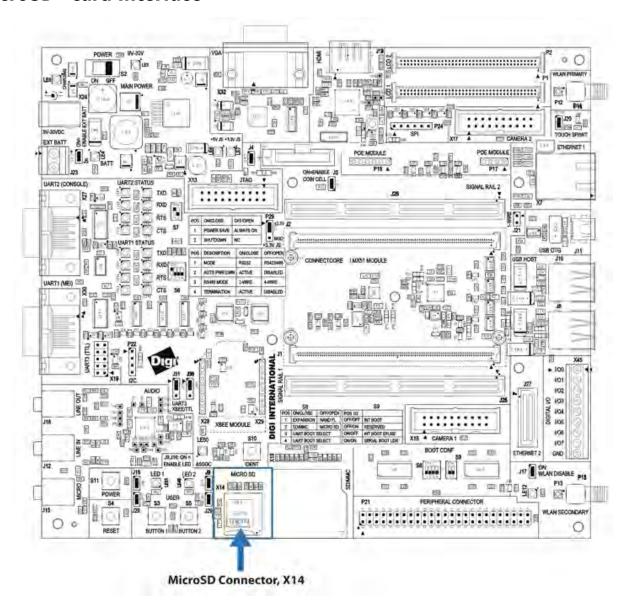

| MicroSD™ card interface                      |     |

| MicroSD connector, X14                       |     |

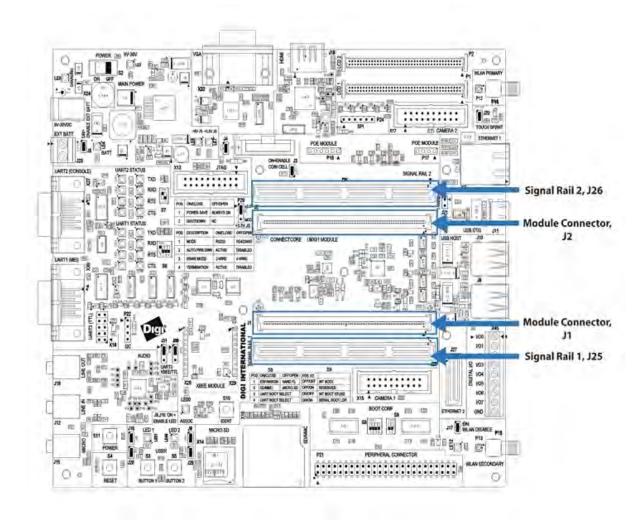

| Module connectors and signal rails           |     |

| Module connectors                            |     |

| Signal rails, J25 and J26                    |     |

| J25 pinout                                   |     |

| J26 pinout                                   |     |

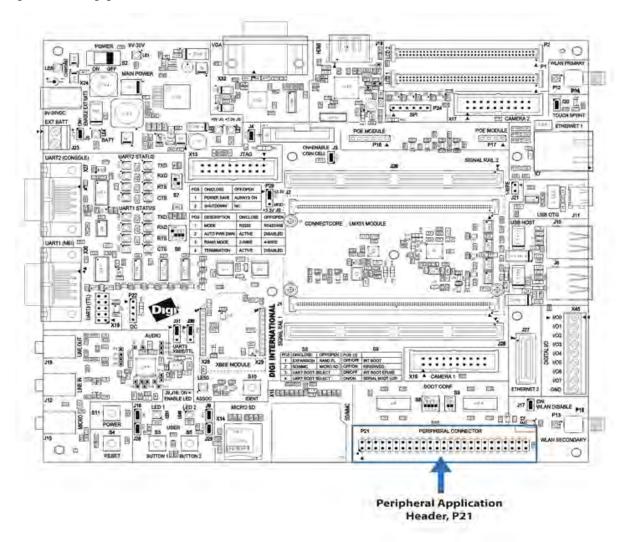

| Peripheral application header                |     |

| Peripheral application header, P21           |     |

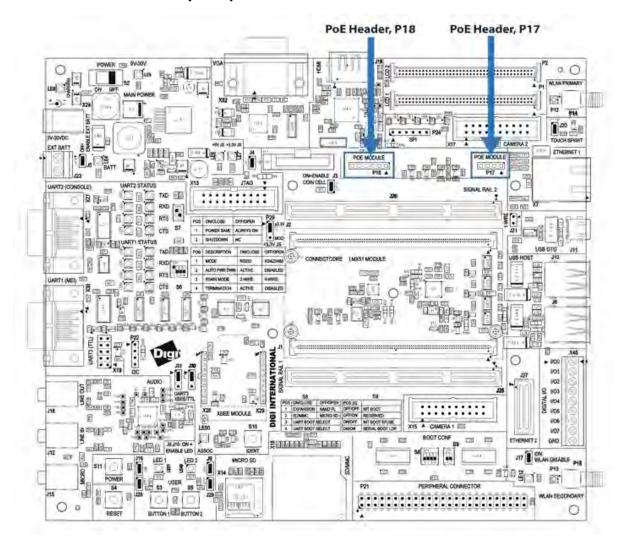

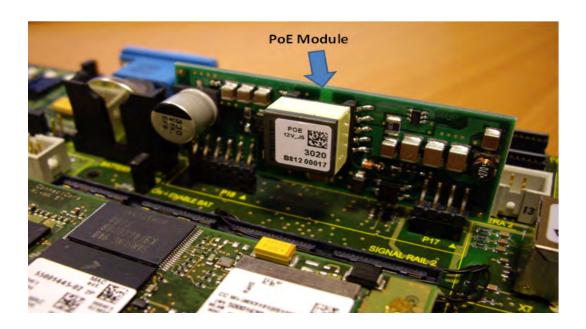

| Power-Over-Ethernet (PoE) - IEEE802.3af      |     |

| The PoE module                               |     |

| PoE connector (power in), P17                |     |

| PoE connector (power out), P18               |     |

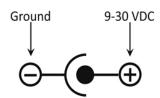

| Main power connector                         |     |

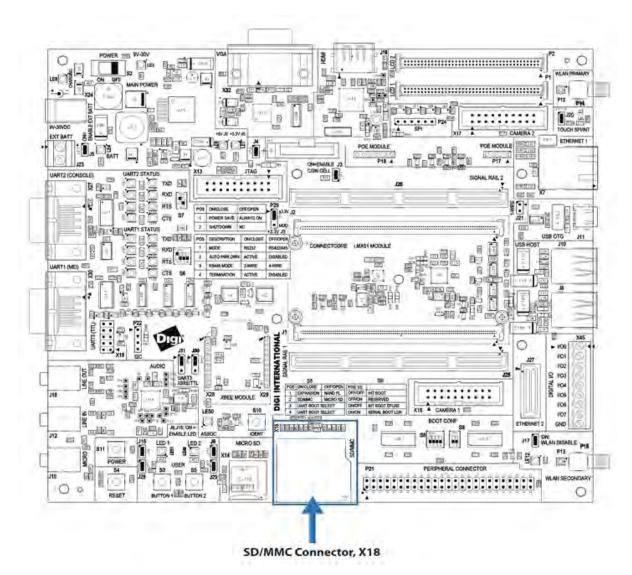

| SD-card interface                            |     |

| SD/MMC connector, X18                        |     |

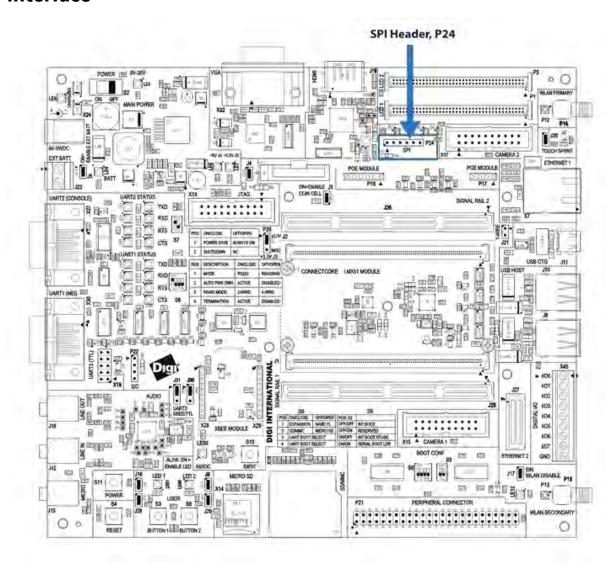

| SPI interface                                |     |

| SPI header, P24                              |     |

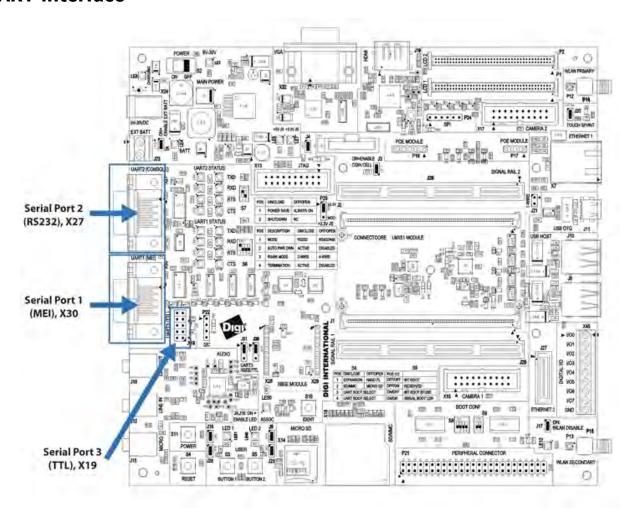

| UART interface                               |     |

| Serial port 2, RS232, X27                    |     |

| Serial port 1, MEI interface, X30            |     |

| Serial port 3, TTL interface, X19            |     |

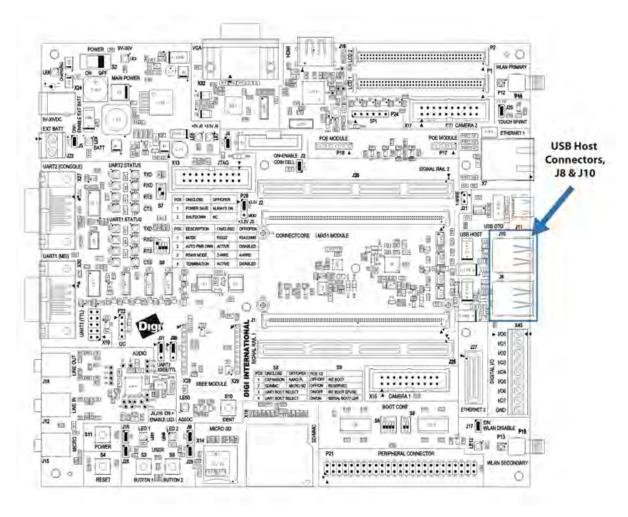

| USB host interface                           |     |

| USB host connectors, J8 and J10              |     |

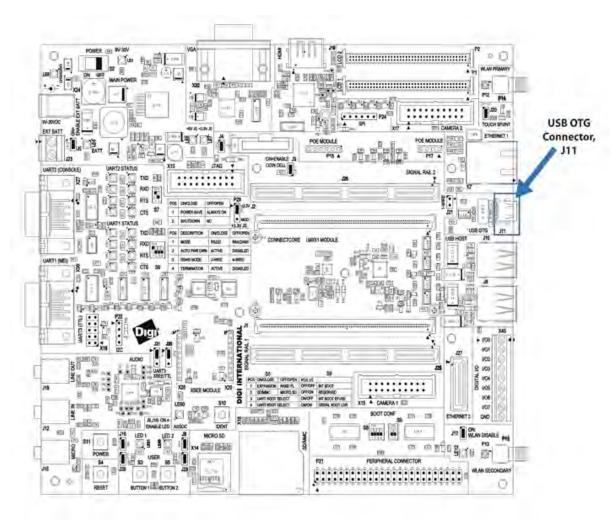

| USB OTG interface                            |     |

| USB OTG connector, J11                       |     |

| User interface                               |     |

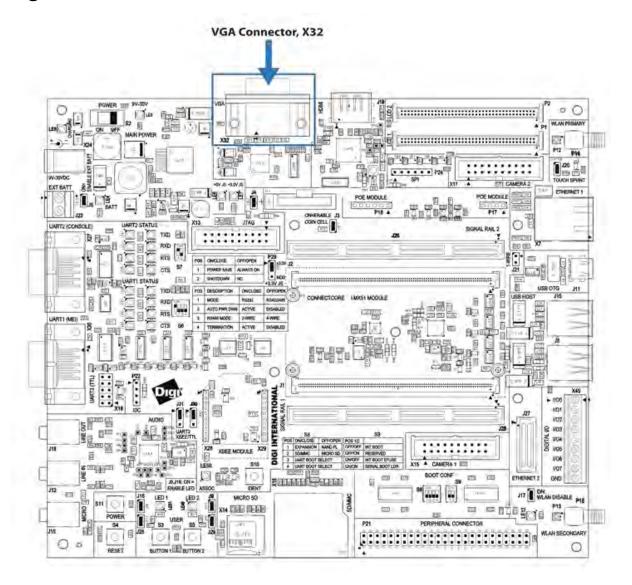

| Analog video interface                       |     |

| Analog video connector, X32                  |     |

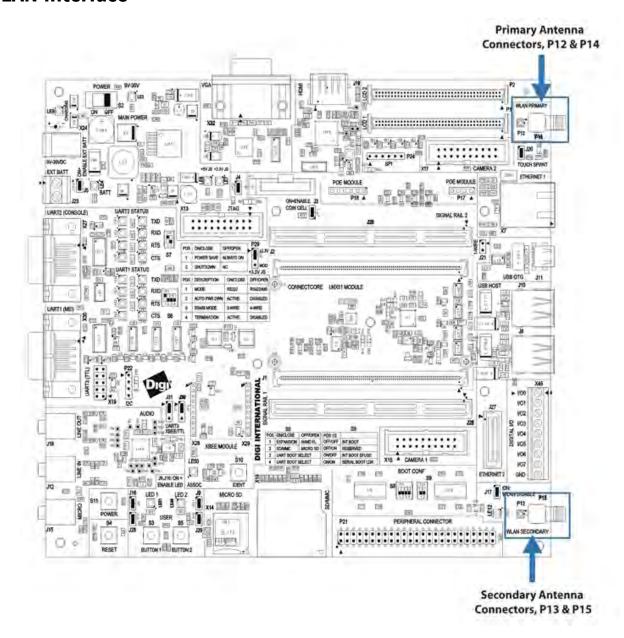

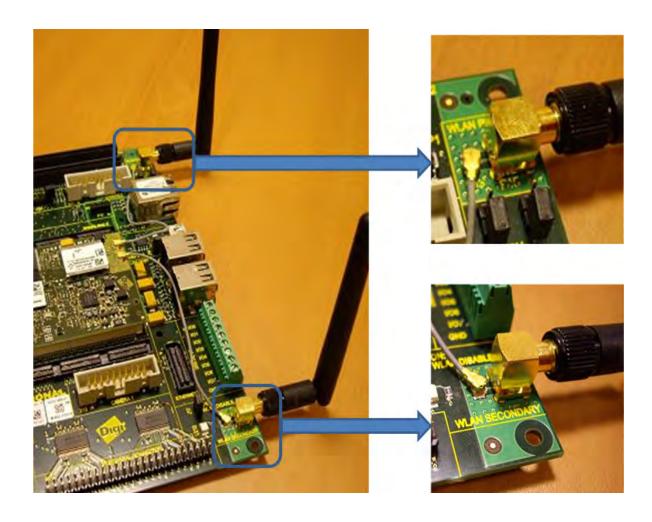

| WLAN interface                               |     |

| Antenna connectors (WLAN)                    |     |

| Digi XBee interface                          |     |

| Digi XBee module connectors, X28 and X29     |     |

| DISTABLE MOddle Connectors, A20 and A25      |     |

|                                              |     |

| Module specifications                        |     |

|                                              |     |

| Mechanical specifications                    |     |

| Fasteners and appropriate torque             | 126 |

| Environmental specifications                 |     |

| Network interface                            |     |

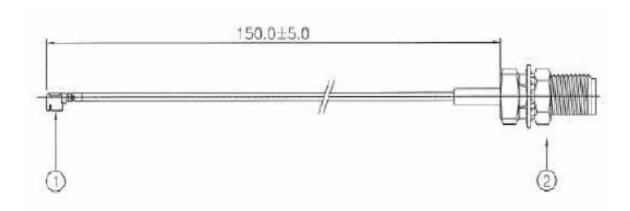

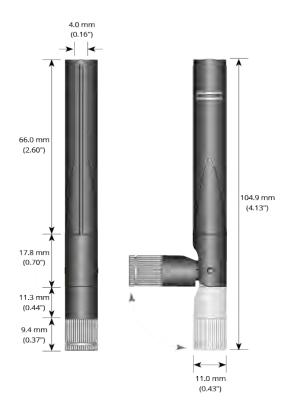

| Antenna specifications: 802.11 a/b/g antenna |     |

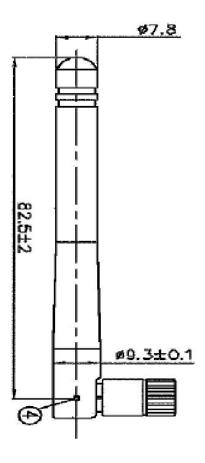

| Antenna specification: 802.11b/g antenna     |     |

| Ethernet 1                                   | 128 |

| Ethernet 2                                   | 129 |

| WLAN                                         |     |

| Electrical characteristics                   |     |

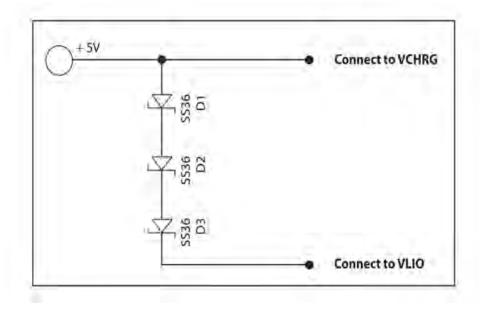

| Charger vs. battery                                           | 131 |

|---------------------------------------------------------------|-----|

| Supply voltages                                               | 132 |

| Supply current                                                | 132 |

| On-module power supplies                                      | 133 |

| I/O DC parameters                                             |     |

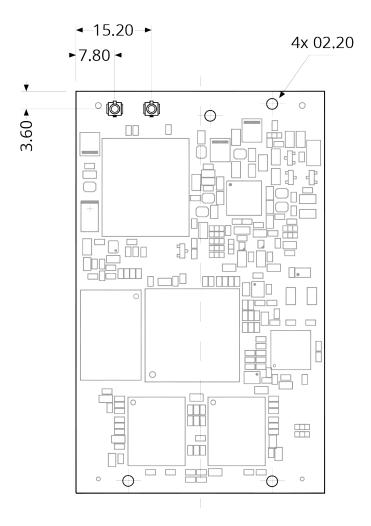

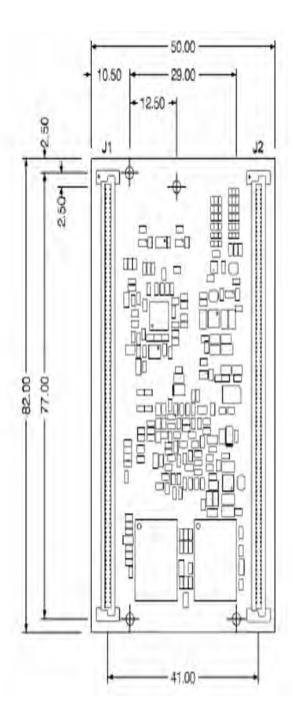

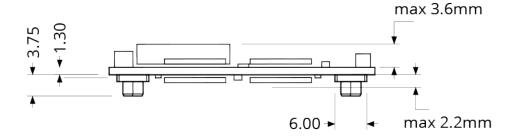

| Module dimensions                                             |     |

| Top view                                                      | 139 |

| Bottom view                                                   |     |

| Side view                                                     | 141 |

| Connectors                                                    | 141 |

| Regulatory information                                        |     |

| Federal Communication (FCC) regulatory information (USA only) | 142 |

| RF exposure                                                   | 142 |

| Modifications (FCC 15.21)                                     | 143 |

| Industry Canada                                               | 143 |

| Indoor/outdoor                                                | 143 |

| Japan certification                                           |     |

| Declaration of Conformity (DoC)                               |     |

| CE mark (Europe)                                              |     |

| International EMC standards                                   | 145 |

Maximum power and frequency specifications

## About the module

The network-enabled ConnectCore for i.MX51 is a highly integrated System-on-Module (SOM) solution based on the new Freescale® i.MX51X application processor with a high-performance ARM® Cortex-A8® core, powerful multimedia options, and a complete set of peripherals.

The module combines the fast integration, reliability and design flexibility of an off-the-shelf SOM with complete out-of-the-box software development support for platforms such as Microsoft® Windows® Embedded CE 6.0, Windows Embedded Compact 7Digi® Embedded Linux® and Timesys® LinuxLink®.

With industry-leading performance and key features like a dual-display interface and a hardware encryption engine, the module is the ideal choice for a broad range of target markets including medical, digital signage, security/access control, retail, industrial/building automation, transportation and more.

Complete and cost-efficient Digi JumpStart Kits™ for Microsoft Windows Embedded CE 6.0 and Linux allow immediate and professional embedded product development with dramatically reduced design risk and time-to-market.

| Features and functionality | 9  |

|----------------------------|----|

| Block diagram              |    |

| Module pinout              | 13 |

| Power                      |    |

| Memory                     |    |

| Chip selects               | 45 |

| Multiplexed GPIO           | 46 |

## **Features and functionality**

The ConnectCore for i.MX51 module is based on the i.MX51 processor from Freescale. This processor offers a high number of interfaces. Most of these interfaces are multiplexed and are not available simultaneously. The module has the following features:

- High-end, low-power 32-bit System-on-Module

- 600/800 MHZ ARM Cortex-A8 core

- 32 kB L1 instruction and 32 kB L1 data cache

- 256 kB L2 cache

- · NEON co-processor

- Vector Floating Point (VFP) unit

- SLC and MLC NAND flash support on module

- Up to 512 MB 32-bit/200 MHZ DDR2-400 memory

- Debug interfaces

- Joint Test Action Group (JTAG)

- Embedded Trace Macrocell™ (ETM) / Embedded Trace Buffer (ETB)

- Real Time Clock (RTC)

- Security co-processor

- Encryption: Advanced Encryption Standard (AES), Data Encryption Standard (DES), 3DES and RC4

- Hashing algorithms: Message Digest (MD)5, Secure Hash Algorithm (SHA)-1, SHA-224 and SHA-256

- Timer

- Watchdog

- Up to three universal asynchronous receiver/transmitter (UART) ports, up to 4 Mb/s each

- Up to three Serial Peripheral Interface (SPI), two of them up to 54 Mb/s each

- Two Inter-Integrated Circuit (I2C) (up to 400 kb/s)

- Three memory card interfaces (two for the wireless version of the module)

- SD/Secure Digital Input Output (SDIO) 1 and 4-bits (up to 200 Mb/s)

- MultiMediaCard (MMC) 1, 4 and 8-bits (up to 416 Mb/s)

- USB

- Up to 3x USB 2.0 High-Speed USB Host ports

- One USB 2.0 On-The-Go USB port with integrated Physical Layer (PHY) on the module

- 1-wire

- Keypad 6x4

- Two independent pulse-width modulation (PWM) interfaces

- 8, 16-bit External Memory interface

- General-purpose input/output (GPIO) with interrupt capabilities

- Up to 3x 10-bit analog-to-digital converter (ADC) channels

- Multimedia

- 2x Camera ports

- 2x Display ports

- 4-wire touch screen

- Sony/Philips Digital Interface Forma (SPDIF) output

- Three I2S / Audio Codec '97 (AC'97) / Synchronous Serial Interfaces (SSI), up to 1.4Mb/s each

- On-module three axis accelerometer (optional)

- On-module 10/100 Ethernet controller (optional)

- Second on-module 10/100Mb Ethernet interface (optional)

- 2.4 GHz and 5 GHz Institute of Electrical and Electronics Engineers (IEEE) 802.11a/b/g/n wireless local area network (LAN) interface (optional)

- Complete Microsoft Windows Embedded CE 6.0 and Linux platform support with full source code

#### **Module variant**

The ConnectCore for i.MX51 module is available with various population options such as network interfaces (Ethernet, wireless local area network [WLAN]), memory (flash, random-access memory [RAM]), processor (speed grade/operating temperature) and others.

About the module Block diagram

# **Block diagram**

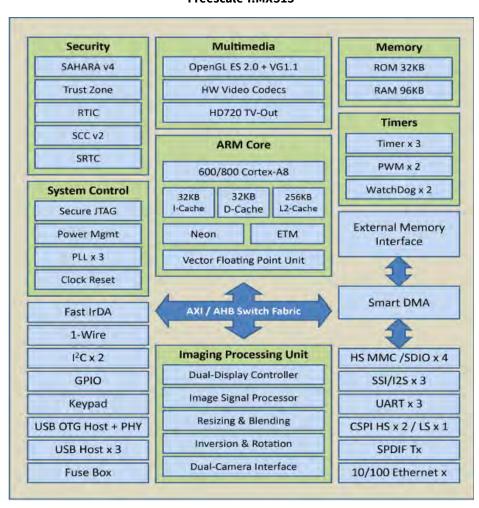

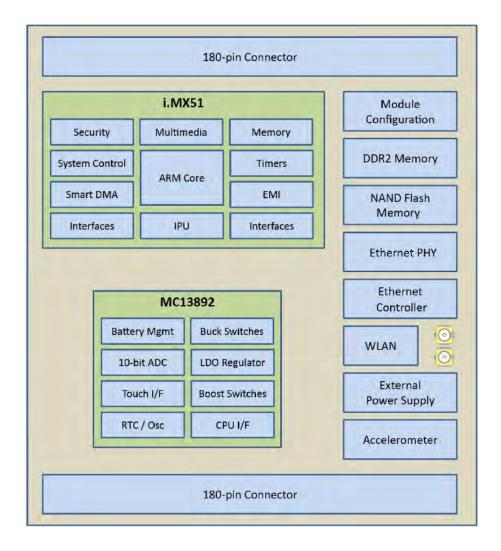

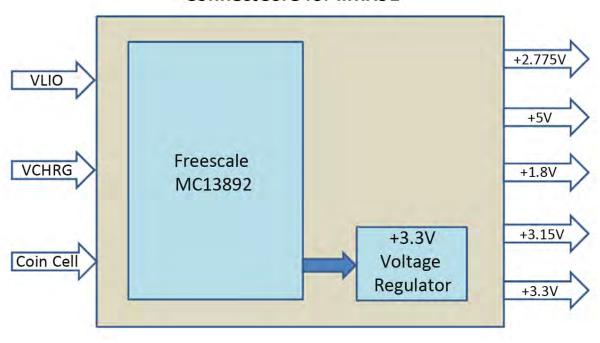

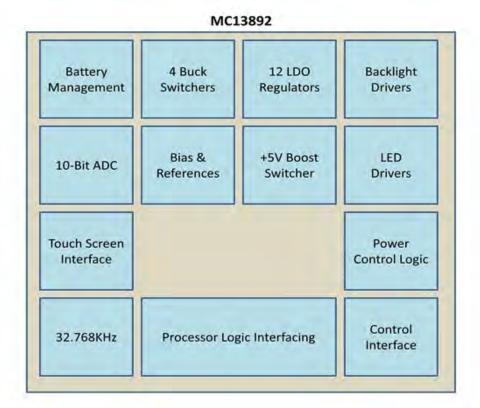

The next figures show the block diagram of the Freescale i.MX515 central processing unit (CPU) and the block diagram of the ConnectCore for i.MX51 module.

#### **CPU**

#### **Module**

ConnectCore I.MX51

About the module Block diagram

## **Module pinout**

The module has two 180-pin connectors, J1 and J2. The following tables describe each pin, its properties, and its use on the module and development board. The DC parameters for each I/O type are defined in the I/O DC parameters.

The "Use on module" column shows the connection of the signals on the module. The format of this column is "component: pad\_name," where "component" is the chip where the signals are connected, and "pad\_name" is the name of the pad where the signals are connected as they are defined in the component's datasheet.

#### **Pinout legend**

- I Input

- O Output

- 10 Input or output

- P Power

- # Low level active signal

#### **Pinout definitions**

GPIO - General Purpose IO UHVIO - Ultra High Voltage IO HSGPIO - High Speed GPIO LVIO - Low Voltage IO (meaning 1.8V)

The I/O Type descriptions can be read as follows:

- 18 1.8V logic level switching (for example, GPIO18)

- 27 2.775V logic level switching (for example, GPIO27)

- 31 3.15V logic level switching (for example, UHVIO31)

- 33 3.3V logic level switching (for example, UHVIO33)

The microprocessor used on this module, like all CMOS devices, can be driven into a latchup condition if any I/O pin is driven outside of its associated power rail. Care must be taken to:

- Never drive an I/O pin beyond its positive rail or below ground.

- Never drive an I/O pin from an external power source during the power-on or reset sequences.

- Never hot-swap the module or interrupt its ground connection to external circuitry.

Latch-up is a condition that can cause excessive current draw and result in excessive heating of the microprocessor or its power supplies. This excessive heating can permanently damage the microprocessor and/or its supporting components.

# J1 pinout

| Pin   | I/O Type     | Signal name         | Use on module           | Use on<br>development<br>board                | Comments |

|-------|--------------|---------------------|-------------------------|-----------------------------------------------|----------|

| J1:1  | GPIO27       | CSI1_D8/GPIO3_12    | i.MX51: CSI1_D8         | Not used                                      |          |

| J1:2  | GPIO27       | CSI1_D9/GPIO3_13    | i.MX51: CSI1_D9         | Camera 1 reset                                |          |

| J1:3  | HSGPIO2<br>7 | CSI1_D10            | i.MX51: CSI1_D10        | Camera 1 data                                 |          |

| J1:4  | HSGPIO2<br>7 | CSI1_D11            | i.MX51: CSI1_D11        | Camera 1 data                                 |          |

| J1:5  | HSGPIO2<br>7 | CSI1_D12            | i.MX51: CSI1_D12        | Camera 1 data                                 |          |

| J1:6  | HSGPIO2<br>7 | CSI1_D13            | i.MX51: CSI1_D13        | Camera 1 data                                 |          |

| J1:7  | HSGPIO2<br>7 | CSI1_D14            | i.MX51: CSI1_D14        | Camera 1 data                                 |          |

| J1:8  | HSGPIO2<br>7 | CSI1_D15            | i.MX51: CSI1_D15        | Camera 1 data                                 |          |

| J1:9  | HSGPIO2<br>7 | CSI1_D16            | i.MX51: CSI1_D16        | Camera 1 data                                 |          |

| J1:10 | HSGPIO2<br>7 | CSI1_D17            | i.MX51: CSI1_D17        | Camera 1 data                                 |          |

| J1:11 | HSGPIO2<br>7 | CSI1_D18            | i.MX51: CSI1_D18        | Camera 1 data                                 |          |

| J1:12 | HSGPIO2<br>7 | CSI1_D19            | i.MX51: CSI1_D19        | Camera 1 data                                 |          |

| J1:13 | GPIO27       | CSI1_VSYNC/GPIO3_14 | i.MX51: CSI1_<br>VSYNC  | Camera 1<br>vertical<br>synchronizatio<br>n   |          |

| J1:14 | GPI027       | CSI1_HSYNC/GPIO3_15 | i.MX51: CSI1_<br>HSYNC  | Camera 1<br>horizontal<br>synchronizatio<br>n |          |

| J1:15 | GPIO27       | CSI1_PIXCLK         | i.MX51: CSI1_<br>PIXCLK | Camera 1 pixel clock                          |          |

| J1:16 | GPIO27       | CSI1_MCLK           | i.MX51: CSI1_MCLK       | Camera 1 and<br>2 Master clock                |          |

| Pin   | I/O Type | Signal name    | Use on module               | Use on<br>development<br>board         | Comments                                                 |

|-------|----------|----------------|-----------------------------|----------------------------------------|----------------------------------------------------------|

| J1:17 | -        | GND            | -                           | -                                      |                                                          |

| J1:18 | -        | GND            | -                           | -                                      |                                                          |

| J1:19 | WLAN     | WLAN_TDO       | WLAN: TDO                   | Not used                               |                                                          |

| J1:20 | WLAN     | WLAN_TCK       | WLAN: TCK                   | Not used                               |                                                          |

| J1:21 | WLAN     | WLAN_TDI       | WLAN: TDI                   | Not used                               |                                                          |

| J1:22 | WLAN     | WLAN_TMS       | WLAN: TMS                   | Not used                               |                                                          |

| J1:23 | WLAN     | WLAN_LED       | WLAN: LED_ON                | WLAN light-<br>emitting diode<br>(LED) |                                                          |

| J1:24 | WLAN     | RS_BT_PRIORITY | WLAN: BT_<br>PRIORITY       | Not used                               |                                                          |

| J1:25 | WLAN     | RS_WLAN_ACTIVE | WLAN: WLAN_<br>ACTIVE       | Not used                               |                                                          |

| J1:26 | WLAN     | RS_BT_ACTIVE   | WLAN: BT_ACTIVE             | Not used                               |                                                          |

| J1:27 | LVIO     | BOOT_MODE0     | i.MX51: BOOT_<br>MODE0      | Boot Mode<br>selection                 | Boot<br>configuratio<br>n not<br>available in<br>EA Kit  |

| J1:28 | GPIO33   | WLAN_DISABLE#  | WLAN Power<br>Supply Switch | WLAN Disable<br>Jumper (J17)           | This signal<br>switch<br>ON/OFF the<br>supply of<br>WLAN |

| J1:29 | LVIO     | BOOT_MODE1     | i.MX51: BOOT_<br>MODE1      | Boot Mode<br>selection                 | Boot<br>configuratio<br>n not<br>available in<br>EA Kit  |

| J1:30 | -        | VLIO           | MC13892: BATT               | Battery supply                         |                                                          |

| J1:31 | -        | VLIO           | MC13892: BATT               | Battery supply                         |                                                          |

| J1:32 | -        | VCHRG          | MC13892:<br>CHRGRAW         | Charger supply                         |                                                          |

| J1:33 | -        | +2.775V        | -                           | -                                      |                                                          |

| Pin   | I/O Type         | Signal name    | Use on module                                    | Use on<br>development<br>board        | Comments                                                                                                                                      |

|-------|------------------|----------------|--------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| J1:34 | -                | VCHRG          | MC13892:<br>CHRGRAW                              | Charger supply                        |                                                                                                                                               |

| J1:35 | -                | +2.775V        | -                                                | -                                     |                                                                                                                                               |

| J1:36 | -                | +2.775V        | -                                                | -                                     |                                                                                                                                               |

| J1:37 | PMIC_<br>GPO     | MC13892_GPO1   | MC13892: GPO1                                    | Reserved                              |                                                                                                                                               |

| J1:38 | -                | +2.775V        | -                                                | -                                     |                                                                                                                                               |

| J1:39 | PMIC_<br>PWRON   | PMIC_PWRON1    | MC13892:<br>PWRON1                               | Connected to<br>Power Button<br>(S11) | Suspend /<br>Wake-up<br>button                                                                                                                |

| J1:40 | PMIC_<br>STDBY   | PMIC_STDBY_REQ | i.MX51: PMIC_<br>STBY_REQ<br>MC13892:<br>STANDBY | Reserved                              | Output from<br>i.MX51 to<br>put<br>MC13892 in<br>low power<br>mode                                                                            |

| J1:41 | PMIC_<br>INT     | PMIC_INT_REQ   | i.MX51: PMIC_INT_<br>REQ                         | Reserved                              | This high-priority interrupt input on i.MX51 is not used. The output interrupt from PMIC is connected to standard interrupt GPIO_5 on i.MX51. |

| J1:42 | PMIC_<br>PWGTDRV | PWRGTDRV1      | MC13892:<br>PWRGTDRV1                            | Not used                              |                                                                                                                                               |

| J1:43 | PMIC_<br>LED     | CHRGLED        | MC13892:<br>CHRGLED                              | Battery<br>Charging LED               |                                                                                                                                               |

| J1:44 | PMIC_<br>PWGTDRV | PWRGTDRV2      | MC13892:<br>PWRGTDRV2<br>+3.3V_REG:<br>ENABLE    | Not used                              | Used on<br>module to<br>enable /<br>disable the<br>+3.3V supply                                                                               |

| Pin   | I/O Type | Signal name                | Use on module               | Use on development board             | Comments                                                                                     |

|-------|----------|----------------------------|-----------------------------|--------------------------------------|----------------------------------------------------------------------------------------------|

| J1:45 | PMIC_SE  | CHRGSE1#                   | MC13892:<br>CHRGSE1#        | Charger<br>detection<br>circuit      | This circuit is needed to boot from charger                                                  |

| J1:46 | -        | VCC_COINCELL               | MC13892: LICELL             | Coincell<br>voltage                  |                                                                                              |

| J1:47 | -        | VLIO                       | MC13892: BATT               | Battery supply                       |                                                                                              |

| J1:48 | -        | VCHRG                      | MC13892:<br>CHRGRAW         | Charger supply                       |                                                                                              |

| J1:49 | -        | VLIO                       | MC13892: BATT               | Battery supply                       |                                                                                              |

| J1:50 | -        | VCHRG                      | MC13892:CHRGRA<br>W         | Charger supply                       |                                                                                              |

| J1:51 | -        | VLIO                       | MC13892: BATT               | Battery supply                       |                                                                                              |

| J1:52 | -        | VCHRG                      | MC13892:CHRGRA<br>W         | Charger supply                       |                                                                                              |

| J1:53 | ETH      | ETH1_TX+                   | ETH_PHY: TXP                | Ethernet 1 Tx+                       |                                                                                              |

| J1:54 | ETH      | ETH1_RX+                   | ETH_PHY: RXP                | Ethernet 1 Rx+                       |                                                                                              |

| J1:55 | ETH      | ETH1_TX-                   | ETH_PHY: TXN                | Ethernet 1 Tx-                       |                                                                                              |

| J1:56 | ETH      | ETH1_RX-                   | ETH_PHY: RXN                | Ethernet 1 Rx-                       |                                                                                              |

| J1:57 | -        | GND                        | -                           | -                                    |                                                                                              |

| J1:58 | GPIO33   | ETH1_LINK                  | ETH_PHY: LED1               | Ethernet 1<br>Link LED               |                                                                                              |

| J1:59 | GPI027   | DISPB2_SER_DIN/GPIO3_<br>5 | i.MX51: DISPB_2_<br>SER_DIN | GPIO1 signal<br>to LCD<br>connectors |                                                                                              |

| J1:60 | GPIO33   | ETH1_ACTIVITY              | ETH_PHY: LED2               | Ethernet 1<br>Activity LED           |                                                                                              |

| J1:61 | GPIO27   | DISPB2_SER_RS/GPIO3_8      | i.MX51: DISPB2_<br>SER_RS   | USB Host<br>Reset                    | In Early Availability Kit USB host and Digital IO interface cannot be used at the same time. |

| Pin   | I/O Type     | Signal name                          | Use on module                            | Use on<br>development<br>board  | Comments                                                         |

|-------|--------------|--------------------------------------|------------------------------------------|---------------------------------|------------------------------------------------------------------|

| J1:62 | GPIO27       | DISPB2_SER_DIO/GPIO3_<br>6           | i.MX51: DISPB2_<br>SER_DIO               | User button 1<br>& Digital IO 7 |                                                                  |

| J1:63 | GPIO27       | DISP2_DATA0/MII_<br>RXD3/USBH3_CLK   | i.MX51: DISP2_<br>DATA0<br>ETH_PHY: RXD3 | LCD2 Data                       | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:64 | GPIO27       | DISPB2_SER_CLK_<br>GPIO3_7           | i.MX51: DISPB2_<br>SER_CLK               | Camera 2<br>Reset               |                                                                  |

| J1:65 | HSGPIO2<br>7 | DISP2_DATA2                          | i.MX51: DISP2_<br>DATA2                  | LCD2 Data                       |                                                                  |

| J1:66 | GPIO27       | DISP2_DATA1/MII_RX_<br>ER/USBH3_DIR  | i.MX51: DISP2_<br>DATA1<br>ETH_PHY: RXD4 | LCD2 Data                       | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:67 | HSGPIO2<br>7 | DISP2_DATA4                          | i.MX51: DISP2_<br>DATA4                  | LCD2 Data                       |                                                                  |

| J1:68 | HSGPIO2<br>7 | DISP2_DATA3                          | i.MX51: DISP2_<br>DATA3                  | LCD2 Data                       |                                                                  |

| J1:69 | GPIO27       | DISP2_DATA6/MII_<br>TXD1/USBH3_STP   | i.MX51: DISP2_<br>DATA6<br>ETH_PHY: TXD1 | LCD2 Data                       | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:70 | HSGPIO2<br>7 | DISP2_DATA5                          | i.MX51: DISP2_<br>DATA5                  | LCD2 Data                       | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:71 | GPIO27       | DISP2_DATA8/MII_<br>TXD3/USBH3_DATA0 | i.MX51: DISP2_<br>DATA8<br>ETH_PHY: TDX3 | LCD2 Data                       | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| Pin   | I/O Type | Signal name                            | Use on module                              | Use on<br>development<br>board | Comments                                                         |

|-------|----------|----------------------------------------|--------------------------------------------|--------------------------------|------------------------------------------------------------------|

| J1:72 | GPIO27   | DISP2_DATA7/MII_<br>TXD2/UBH3_NXT      | i.MX51: DISP2_<br>DATA7<br>ETH_PHY: TDX2   | LCD2 Data                      | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:73 | GPIO27   | DISP2_DATA10/MII_<br>COL/USBH3_DATA2   | i.MX51: DISP2_<br>DATA10<br>ETH_PHY: COL   | LCD2 Data                      | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:74 | GPIO27   | DISP2_DATA9/MII_<br>TXEN/USBH3_DATA1   | i.MX51: DISP2_<br>DATA9<br>ETH_PHY: TXEN   | LCD2 Data                      | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:75 | GPIO27   | DISP2_DAT12/MII_RX_<br>DV/USBH3_DATA4  | i.MX51: DISP2_<br>DATA12<br>ETH_PHY: RXDV  | LCD2 Data                      | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:76 | GPIO27   | DISP2_DAT11/MII_RX_<br>CLK/USBH3_DATA3 | i.MX51: DISP2_<br>DATA11<br>ETH_PHY: RXCLK | LCD2 Data                      | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:77 | GPIO27   | DISP2_DATA14/MII_<br>RXD0/USBH3_DATA6  | i.MX51: DISP2_<br>DATA14<br>ETH_PHY: RXD0  | LCD2 Data                      | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:78 | GPIO27   | DISP2_DAT13/MII_TX_<br>CLK/USBH3_DATA5 | i.MX51: DISP2_<br>DATA13<br>ETH_PHY: TXCLK | LCD2 Data                      | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:79 | GPIO27   | DI2_PIN2/MII_MDC                       | i.MX51: DI2_PIN2<br>ETH_PHY: MDC           | LCD2 Data                      | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| Pin   | I/O Type | Signal name                          | Use on module                             | Use on<br>development<br>board | Comments                                                         |

|-------|----------|--------------------------------------|-------------------------------------------|--------------------------------|------------------------------------------------------------------|

| J1:80 | GPIO27   | DISP2_DAT15/MII_<br>TXD0/USBH3_DATA7 | i.MX51: DISP2_<br>DATA15<br>ETH_PHY: TXD0 | LCD2 Data                      | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:81 | GPIO27   | DI2_PIN4/MII_CRS                     | i.MX51: DI2_PIN4<br>ETH_PHY: CRS          | LCD2 Data                      | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:82 | -        | GND                                  | -                                         | -                              |                                                                  |

| J1:83 | RGB      | IOR                                  | i.MX51: IOR                               | Not used                       |                                                                  |

| J1:84 | GPIO27   | DI2_DISP_CLK/MII_RXD1                | i.MX51: DI2_DISP_<br>CLK<br>ETH_PHY: RXD1 | LCD2 Data                      | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:85 | RGB      | IOR_BACK                             | i.MX51: IOR_BACK                          | Not used                       |                                                                  |

| J1:86 | GPIO27   | DI2_PIN3/MII_MDIO                    | i.MX51: DI2_PIN3<br>ETH_PHY: MDIO         | LCD2 Data                      | Ethernet 1<br>and LCD2<br>cannot be<br>used at the<br>same time. |

| J1:87 | RGB      | IOB                                  | i.MX51: IOB                               | Not useD                       |                                                                  |

| J1:88 | IOG      | IOG                                  | i.MX51: IOG                               | Not used                       |                                                                  |

| J1:89 | RGB      | IOB_BACK                             | i.MX51: IOB_BACK                          | Not used                       |                                                                  |

| J1:90 | RGB      | IOG_BACK                             | i.MX51: IOG_BACK                          | Not used                       |                                                                  |

| J1:91 | GPIO18   | JTAG_TCK                             | i.MX51: JTAG_TCK                          | JTAG<br>Connector              |                                                                  |

| J1:92 | GPIO18   | JTAG_TRST#                           | i.MX51: JTAG_<br>TRST#                    | JTAG<br>Connector              |                                                                  |

| J1:93 | GPIO18   | JTAG_TMS                             | i.MX51: JTAG_TMS                          | JTAG<br>Connector              |                                                                  |

| J1:94 | GPIO18   | JTAG_MOD#                            | i.MX51: JTAG_<br>MOD#                     | JTAG Mod<br>Selection          |                                                                  |

| Pin        | I/O Type | Signal name       | Use on module                                                                           | Use on<br>development<br>board | Comments                                                                              |

|------------|----------|-------------------|-----------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------|

| J1:95      | GPIO18   | JTAG_TDI          | i.MX51: JTAG_TDI JTAG<br>Connector                                                      |                                |                                                                                       |

| J1:96      | GPIO18   | JTAG_DE#          | i.MX51: JTAG_DE_B                                                                       | JTAG<br>Connector              |                                                                                       |

| J1:97      | GPIO18   | JTAG_TDO          | i.MX51: JTAG_TDO                                                                        | JTAG<br>Connector              |                                                                                       |

| J1:98      | LVIO     | RESET_IN#         | i.MX51: RESET_IN_<br>B<br>MC13892: RESETB                                               | Not used                       | Warm reset input to i.MX51.                                                           |

| J1:99      | LVIO     | POR#              | i.MX51: POR_B MC13892: RESETBMCU  LCD 1 & 2 Reset, JTAG Connector and Reset Button (S4) |                                | Cold reset input to i.MX51. Used to reset the module and peripherals on the Dev. Kit. |

| J1:10<br>0 | -        | +1.8V             |                                                                                         | -                              |                                                                                       |

| J1:10<br>1 | -        | GND               |                                                                                         | -                              |                                                                                       |

| J1:10<br>2 | -        | GND               |                                                                                         | -                              |                                                                                       |

| J1:10<br>3 | ETH      | ETH2_TX+/ETH2_DA+ | ETH_CTRL: TPO+                                                                          | Ethernet 2 Tx+                 |                                                                                       |

| J1:10<br>4 | ETH      | ETH2_RX+/ETH2_DB+ | ETH_CTRL: TPI+                                                                          | Ethernet 2 Rx+                 |                                                                                       |

| J1:10<br>5 | ETH      | ETH2_TX-/ETH2_DA- | ETH_CTRL: TPO-                                                                          | Ethernet 2 Tx-                 |                                                                                       |

| J1:10<br>6 | ETH      | ETH2_RX-/ETH2_DB- | ETH_CTRL: TPI-                                                                          | Ethernet 2 Rx-                 |                                                                                       |

| J1:10<br>7 | -        | -                 | -                                                                                       | -                              | -                                                                                     |

| J1:10<br>8 | -        | -                 | -                                                                                       | -                              | -                                                                                     |

| J1:10<br>9 | -        | -                 | -                                                                                       | -                              | -                                                                                     |

| Pin        | I/O Type | Signal name                                                       | Use on module                    | Use on<br>development<br>board              | Comments |

|------------|----------|-------------------------------------------------------------------|----------------------------------|---------------------------------------------|----------|

| J1:11<br>0 | -        | -                                                                 | -                                | -                                           | -        |

| J1:11<br>1 | GPIO33   | ETH2_ACTIVITY#                                                    | ETH_CTRL:<br>GPIO1/LED2#         | Ethernet 2<br>Activity LED                  |          |

| J1:11<br>2 | GPIO33   | ETH2_LINK#                                                        | ETH_CTRL:<br>GPIO0/LED1#         | Ethernet 2<br>Link LED                      |          |

| J1:11<br>3 | GPIO18   | EIM_CS0/GPIO2_25                                                  | i.MX51: EIM_CS0                  | Peripheral<br>Application<br>Chip Select    |          |

| J1:11<br>4 | GPIO18   | EIM_CS1/GPIO2_26                                                  | i.MX51: EIM_CS1                  | Not used                                    |          |

| J1:11<br>5 | GPIO18   | EIM_CS2/GPIO2_27/FEC_<br>RDATA2/SISG5/CSI1_<br>D4/AUD5_TXD        | i.MX51: EIM_CS2                  | Not used                                    |          |

| J1:11<br>6 | GPIO18   | EIM_CS3/GPIO2_28/FEC_<br>RDATA3/SSI_EXT2_<br>CLK/CSI1_D5/AUD5_RXD | i.MX51: EIM_CS3                  | Not used                                    |          |

| J1:11<br>7 | GPIO18   | EIM_CS4/GPIO2_29/FEC_<br>RX_ER/SSI_EXT1_<br>CLK/CSI1_D6/AUD5_TXC  | i.MX51: EIM_CS4                  | Not used                                    |          |

| J1:11<br>8 | GPIO18   | EIM_CS5/GPIO2_30/FEC_<br>CRS/DI1_EXT_CLK/CSI1_<br>D7/AUD5_TXFS    | i.MX51: EIM_CS4<br>EHT_CTRL: CS# | Reserved                                    |          |

| J1:11<br>9 | GPIO18   | EIM_DTACK/GPIO2_31                                                | i.MX51: EIM_DTACK                | Not used                                    |          |

| J1:12<br>0 | GPIO18   | EIM_LBA/GPIO3_1                                                   | i.MX51: EIM_LBA                  | Not used                                    |          |

| J1:12<br>1 | GPIO18   | EIM_DA0/TRACE16                                                   | i.MX51: EIM_DA0<br>ETH_CTRL: A1  | Peripheral<br>Application<br>Data / Address |          |

| J1:12<br>2 | GPIO18   | EIM_DA1/TRACE17                                                   | i.MX51: EIM_DA1<br>ETH_CTRL: A2  | Peripheral<br>Application<br>Data / Address |          |

| J1:12<br>3 | GPIO18   | EIM_DA2/TRACE18                                                   | i.MX51: EIM_DA2<br>ETH_CTRL: A3  | Peripheral<br>Application<br>Data / Address |          |

| Pin        | I/O Type | Signal name      | Use on module                             | Use on<br>development<br>board              | Comments |

|------------|----------|------------------|-------------------------------------------|---------------------------------------------|----------|

| J1:12<br>4 | GPIO18   | EIM_DA3/TRACE19  | i.MX51: EIM_DA3<br>ETH_CTRL: A4           | Peripheral<br>Application<br>Data / Address |          |

| J1:12<br>5 | -        | GND              | -                                         | -                                           |          |

| J1:12<br>6 | GPIO18   | EIM_DA5/TRACE21  | i.MX51: EIM_DA5<br>ETH_CTRL: A6           | Peripheral<br>Application<br>Data / Address |          |

| J1:12<br>7 | GPIO18   | EIM_DA4/TRACE20  | i.MX51: EIM_DA4<br>ETH_CTRL: A5           | Peripheral<br>Application<br>Data / Address |          |

| J1:12<br>8 | GPIO18   | EIM_DA7/TRACE23  | i.MX51: EIM_DA7<br>ETH_CTRL: FIFO_<br>SEL | Peripheral<br>Application<br>Data / Address |          |

| J1:12<br>9 | GPIO18   | EIM_DA6/TRACE22  | i.MX51: EIM_DA6<br>ETH_CTRL: A7           | Peripheral<br>Application<br>Data / Address |          |

| J1:13<br>0 | -        | GND              | -                                         | -                                           |          |

| J1:13<br>1 | GPIO18   | EIM_DA8/TRACE24  | i.MX51: EIM_DA8                           | Peripheral<br>Application<br>Data / Address |          |

| J1:13<br>2 | GPIO18   | EIM_DA9/TRACE25  | i.MX51: EIM_DA9                           | Peripheral<br>Application<br>Data / Address |          |

| J1:13<br>3 | GPIO18   | EIM_DA10/TRACE26 | i.MX51: EIM_DA10                          | Not used                                    |          |

| J1:13<br>4 | GPIO18   | EIM_DA11/TRACE27 | i.MX51: EIM_DA11                          | Not used                                    |          |

| J1:13<br>5 | -        | GND              | -                                         | -                                           |          |

| J1:13<br>6 | GPIO18   | EIM_DA13/TRACE29 | i.MX51: EIM_DA13                          | Not used                                    |          |

| J1:13<br>7 | GPIO18   | EIM_DA12/TRACE28 | i.MX51: EIM_DA12                          | Not used                                    |          |

| J1:13<br>8 | GPIO18   | EIM_DA15/TRACE31 | i.MX51: EIM_DA15                          | Not used                                    |          |

| Pin        | I/O Type | Signal name                                                                            | Use on module                   | Use on<br>development<br>board    | Comments |

|------------|----------|----------------------------------------------------------------------------------------|---------------------------------|-----------------------------------|----------|

| J1:13<br>9 | GPIO18   | EIM_DA14/TRACE30                                                                       | i.MX51: EIM_DA14                | Not used                          |          |

| J1:14<br>0 | -        | GND                                                                                    | -                               | -                                 |          |

| J1:14<br>1 | GPIO18   | EIM_D16/GPIO2_<br>0/USBH2_DATA0/UART2_<br>CTS#/I2C1_SDA/AUD4_<br>RXFS/TRACE0/AUD5_TXD  | i.MX51: EIM_D16<br>ETH_CTRL: D0 | Peripheral<br>Application<br>Data |          |

| J1:14<br>2 | GPIO18   | EIM_D17/GPIO2_<br>1/USBH2_DATA1/UART2_<br>RXD/UART3_<br>CTS#/SISG4/TRACE1/AUD<br>5_RXD | i.MX51: EIM_D17<br>ETH_CTRL: D1 | Peripheral<br>Application<br>Data |          |

| J1:14<br>3 | GPIO18   | EIM_D18/GPIO2_<br>2/USBH2_DATA2/UART2_<br>TXD/UART3_<br>RTS#/SISG5/TRACE2/AUD<br>5_TXC | i.MX51: EIM_D18<br>ETH_CTRL: D2 | Peripheral<br>Application<br>Data |          |

| J1:14<br>4 | GPIO18   | EIM_D19/GPIO2_<br>3/USBH2_DATA3/UART2_<br>RTS#/I2C1_SCL/AUD4_<br>RXC/TRACE3/AUD5_TXFS  | i.MX51: EIM_D19<br>ETH_CTRL: D3 | Peripheral<br>Application<br>Data |          |

| J1:14<br>5 | -        | +3.15V                                                                                 | -                               | -                                 |          |

| J1:14<br>6 | GPIO18   | EIM_D21/GPIO2_<br>5/USBH2_DATA5/AUD4_<br>RXD/TRACE5                                    | i.MX51: EIM_D21<br>ETH_CTRL: D5 | Peripheral<br>Application<br>Data |          |

| J1:14<br>7 | GPIO18   | EIM_D20/GPIO2_<br>4/USBH2_DATA4/AUD4_<br>TXD/TRACE4                                    | i.MX51: EIM_D20<br>ETH_CTRL: D4 | Peripheral<br>Application<br>Data |          |

| J1:14<br>8 | GPIO18   | EIM_D23/GPIO2_<br>7/USBH2_DATA7/SPDIF_<br>OUT1/AUD4_TXFS/TRACE7                        | i.MX51: EIM_D23<br>ETH_CTRL: D7 | Peripheral<br>Application<br>Data |          |

| J1:14<br>9 | GPIO18   | EIM_D22/GPIO2_<br>6/USBH2_DATA6/AUD4_<br>TXC/TRACE6                                    | i.MX51: EIM_D22<br>ETH_CTRL: D8 | Peripheral<br>Application<br>Data |          |

| J1:15<br>0 | -        | GND                                                                                    | -                               | -                                 |          |

| Pin        | I/O Type | Signal name                                                      | Use on module                    | Use on<br>development<br>board    | Comments |

|------------|----------|------------------------------------------------------------------|----------------------------------|-----------------------------------|----------|

| J1:15<br>1 | GPIO18   | EIM_D24/GPIO2_<br>8/UART3_CTS#/I2C2_<br>SDA/AUD6_RXFS/TRACE8     | i.MX51: EIM_D24<br>ETH_CTRL: D8  | Peripheral<br>Application<br>Data |          |

| J1:15<br>2 | GPIO18   | EIM_D25/KEY_<br>COL6/UART3_<br>RXD/UART2_<br>CTS#/CMPOUT1/TRACE9 | i.MX51: EIM_D25<br>ETH_CTRL: D9  | Peripheral<br>Application<br>Data |          |

| J1:15<br>3 | GPIO18   | EIM_D26/KEY_<br>COL7/UART3_TXD/UART2_<br>RTS#/CMPOUT2/TRACE10    | i.MX51: EIM_D26<br>ETH_CTRL: D10 | Peripheral<br>Application<br>Data |          |

| J1:15<br>4 | GPIO18   | EIM_D27/GPIO2_<br>9/UART3_RTS#/I2C2_<br>SCL/AUD6_RXC/TRACE11     | i.MX51: EIM_D27<br>ETH_CTRL: D11 | Peripheral<br>Application<br>Data |          |

| J1:15<br>5 | -        | GND                                                              | -                                | -                                 |          |

| J1:15<br>6 | GPIO18   | EIM_D29/KEY_<br>ROW5/SISG1/AUD6_<br>RXD/TRACE13                  | i.MX51: EIM_D29<br>ETH_CTRL: D13 | Peripheral<br>Application<br>Data |          |

| J1:15<br>7 | GPIO18   | EIM_D28/KEY_<br>ROW4/SISG0/AUD6_<br>TXD/TRACE12                  | i.MX51: EIM_D28<br>ETH_CTRL: D12 | Peripheral<br>Application<br>Data |          |

| J1:15<br>8 | GPIO18   | EIM_D31/KEY_<br>ROW7/SISG03/AUD6_<br>TXFS/TRACE15                | i.MX51: EIM_D31<br>ETH_CTRL: D15 | Peripheral<br>Application<br>Data |          |

| J1:15<br>9 | GPIO18   | EIM_D30/KEY_<br>ROW6/SISG2/AUD6_<br>TXC/TRACE14                  | i.MX51: EIM_D30<br>ETH_CTRL: D14 | Peripheral<br>Application<br>Data |          |

| J1:16<br>0 | GPIO18   | EIM_A17/GPIO2_11                                                 | i.MX51: EIM_A17                  | Not used                          |          |

| J1:16<br>1 | GPIO18   | EIM_A16/GPIO2_10                                                 | i.MX51: EIM_A16                  | Not used                          |          |

| J1:16<br>2 | GPIO18   | EIM_A19/GPIO2_13                                                 | i.MX51: EIM_A19                  | Not used                          |          |

| J1:16<br>3 | GPIO18   | EIM_A18/GPIO2_12                                                 | i.MX51: EIM_A18                  | Not used                          |          |

| Pin        | I/O Type | Signal name                                                           | Use on module                   | Use on<br>development<br>board               | Comments |

|------------|----------|-----------------------------------------------------------------------|---------------------------------|----------------------------------------------|----------|

| J1:16<br>4 | GPIO18   | EIM_A21/GPIO2_15                                                      | i.MX51: EIM_A21                 | Boot<br>Configuration<br>Switch              |          |

| J1:16<br>5 | GPIO18   | EIM_A20/GPIO2_14                                                      | i.MX51: EIM_A20                 | Boot<br>Configuration<br>Switch              |          |

| J1:16<br>6 | GPIO18   | EIM_A23/GPIO2_17                                                      | i.MX51: EIM_A23                 | Not used                                     |          |

| J1:16<br>7 | GPIO18   | EIM_A22/GPIO2_16                                                      | i.MX51: EIM_A22                 | Not used                                     |          |

| J1:16<br>8 | GPIO18   | EIM_A25/GPIO2_<br>19/USBH2_DIR/DI1_PIN4                               | i.MX51: EIM_A25                 | Not used                                     |          |

| J1:16<br>9 | GPIO18   | EIM_A24/GPIO2_<br>18/USBH2_CLK                                        | i.MX51: EIM_A24                 | Not used                                     |          |

| J1:17<br>0 | GPIO18   | EIM_A27/GPIO2_<br>21/USBH2_<br>NXT/SISG1/CSI2_DATA_<br>EN/DI1_PIN1    | i.MX51: EIM_A27                 | XBEE_SLEEP_<br>RQ                            |          |

| J1:17<br>1 | GPIO18   | EIM_A26/GPIO2_<br>20/USBH2_<br>STP/SISG0/CSI1_DATA_<br>EN/DI2_EXT_CLK | i.MX51: EIM_A26                 | Not used                                     |          |

| J1:17<br>2 | GPIO18   | EIM_OE#/GPIO2_24                                                      | i.MX51: EIM_OE<br>ETH_CTRL: RD# | Peripheral<br>Application<br>Output Enable   |          |

| J1:17<br>3 | GPIO18   | EIM_EB0                                                               | i.MX51: EIM_EB0                 | Not used                                     |          |

| J1:17<br>4 | GPIO18   | EIM_RW#                                                               | i.MX51: EIM_RW<br>ETH_CTRL: WR# | Peripheral<br>Application<br>Read / Write    |          |

| J1:17<br>5 | GPIO18   | EIM_EB1                                                               | i.MX51: EIM_EB1                 | Not used                                     |          |

| J1:17<br>6 | GPIO18   | EIM_CRE/GPIO3_2                                                       | i.MX51: EIM_CRE                 | Peripheral<br>Application<br>Interrupt input |          |

| Pin        | I/O Type | Signal name                                                                  | Use on module    | Use on<br>development<br>board             | Comments                                                       |

|------------|----------|------------------------------------------------------------------------------|------------------|--------------------------------------------|----------------------------------------------------------------|

| J1:17<br>7 | GPIO18   | EIM_EB2/GPIO2_<br>22/TRCTL/FEC_<br>MDIO/SISG2/CSI1_<br>D2/AUD5_RXFS/CMPOUT1  | i.MX51: EIM_EB2  | Peripheral<br>Application<br>Byte Enable 2 |                                                                |

| J1:17<br>8 | GPIO18   | EIM_WAIT                                                                     | i.MX51: EIM_WAIT | Not used                                   |                                                                |

| J1:17<br>9 | GPIO18   | EIM_EB3/GPIO2_<br>23/TRCLK/FEC_<br>RDATA1/SISG3/CSI1_<br>D3/AUD5_RXC/CMPOUT2 | i.MX51: EIM_EB3  | Peripheral<br>Application<br>Byte Enable 3 |                                                                |

| J1:18<br>0 | GPIO18   | EIM_BCLK                                                                     | i.MX51: EIM_BCLK | Peripheral<br>Application<br>Clock Burst   | By default<br>not<br>connected<br>on<br>Developmen<br>t Board. |

# J2 pinout

**CAUTION!** Do not connect signals marked NANDF\_\* to GND during boot time if you want to boot from NAND flash.

| Pin   | Туре     | Signal name | Use on module           | Use on<br>development<br>board                       | Comments                                                            |

|-------|----------|-------------|-------------------------|------------------------------------------------------|---------------------------------------------------------------------|

| J2:1  | HSGPIO27 | DISP1_DAT0  | i.MX51: DISP1_<br>DAT0  | HDMI, VGA<br>and LCD1<br>Data                        | On the Development<br>Kit, DISP1 and DISP2<br>are configured at 18- |

| J2:2  | HSGPIO27 | DISP1_DAT1  | i.MX51: DISP1_<br>DAT1  | HDMI, VGA<br>and LCD1<br>Data                        | bit, and connected<br>to 24-bit LCDs.  On the Development           |

| J2:3  | HSGPIO27 | DISP1_DAT2  | i.MX51: DISP1_<br>DAT2  | HDMI, VGA<br>and LCD1<br>Data                        | Kit, some DISP1 signals are used to configure the boot process.     |

| J2:4  | HSGPIO27 | DISP1_DAT3  | i.MX51: DISP1_<br>DAT3  | HDMI, VGA<br>and LCD1<br>Data                        | On the Early<br>Availability Kit,<br>DISP1 and DISP2 are            |

| J2:5  | HSGPIO27 | DISP1_DAT4  | i.MX51: DISP1_<br>DAT4  | HDMI, VGA<br>and LCD1<br>Data                        | configured at 24-bit,<br>and connected to<br>24-bit LCDs.           |

| J2:6  | HSGPIO27 | DISP1_DAT5  | i.MX51: DISP1_<br>DAT5  | HDMI, VGA<br>and LCD1<br>Data                        |                                                                     |

| J2:7  | GPIO27   | DISP1_DAT6  | i.MX51: DISP1_<br>DAT6  | HDMI, VGA<br>and LCD1<br>Data, Boot<br>Configuration |                                                                     |

| J2:8  | GPIO27   | DISP1_DAT7  | i.MX51: DISP1_<br>DAT7  | HDMI, VGA<br>and LCD1<br>Data, Boot<br>Configuration |                                                                     |

| J2:9  | GPIO27   | DISP1_DAT8  | i.MX51: DISP1_<br>DAT8  | HDMI, VGA<br>and LCD1<br>Data, Boot<br>Configuration |                                                                     |

| J2:10 | GPIO27   | DISP1_DAT9  | i.MX51: DISP1_<br>DAT9  | HDMI, VGA<br>and LCD1<br>Data, Boot<br>Configuration |                                                                     |

| J2:11 | GPIO27   | DISP1_DAT10 | i.MX51: DISP1_<br>DAT10 | HDMI, VGA<br>and LCD1<br>Data, Boot<br>Configuration |                                                                     |

| Pin   | Туре   | Signal name | Use on module           | Use on<br>development<br>board                       | Comments                                                                                  |

|-------|--------|-------------|-------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------|

| J2:12 | GPIO27 | DISP1_DAT11 | i.MX51: DISP1_<br>DAT11 | HDMI, VGA<br>and LCD1<br>Data, Boot<br>Configuration |                                                                                           |

| J2:13 | GPIO27 | DISP1_DAT12 | i.MX51: DISP1_<br>DAT12 | HDMI, VGA<br>and LCD1<br>Data, Boot<br>Configuration |                                                                                           |

| J2:14 | GPIO27 | DISP1_DAT13 | i.MX51: DISP1_<br>DAT13 | HDMI, VGA<br>and LCD1<br>Data, Boot<br>Configuration | On the Development<br>Kit, DISP1 and DISP2<br>are configured at 18-<br>bit, and connected |

| J2:15 | GPIO27 | DISP1_DAT14 | i.MX51: DISP1_<br>DAT14 | HDMI, VGA<br>and LCD1<br>Data, Boot<br>Configuration | to 24-bit LCDs.  On the Development Kit, some DISP1 signals are used to                   |

| J2:16 | GPIO27 | DISP1_DAT15 | i.MX51: DISP1_<br>DAT15 | HDMI, VGA<br>and LCD1<br>Data, Boot<br>Configuration | configure the boot process.  On the Early Availability Kit,                               |

| J2:17 | GPIO27 | DISP1_DAT16 | i.MX51: DISP1_<br>DAT16 | HDMI, VGA<br>and LCD1<br>Data, Boot<br>Configuration | DISP1 and DISP2 are configured at 24-bit, and connected to 24-bit LCDs.                   |

| J2:18 | GPI027 | DISP1_DAT17 | i.MX51: DISP1_<br>DAT17 | HDMI, VGA<br>and LCD1<br>Data, Boot<br>Configuration |                                                                                           |

| J2:19 | GPIO27 | DISP1_DAT18 | i.MX51: DISP1_<br>DAT18 | Not used                                             |                                                                                           |

| J2:20 | GPIO27 | DISP1_DAT19 | i.MX51: DISP1_<br>DAT19 | Not used                                             |                                                                                           |

| J2:21 | GPIO27 | DISP1_DAT20 | i.MX51: DISP1_<br>DAT20 | Boot<br>Configuration                                |                                                                                           |

| J2:22 | GPIO27 | DISP1_DAT21 | i.MX51: DISP1_<br>DAT21 | Boot<br>Configuration                                |                                                                                           |

| Pin   | Туре   | Signal name           | Use on module                                | Use on<br>development<br>board               | Comments |

|-------|--------|-----------------------|----------------------------------------------|----------------------------------------------|----------|

| J2:23 | GPIO27 | DISP1_DAT22           | i.MX51: DISP1_<br>DAT22                      | LCD2 Data                                    |          |

| J2:24 | GPIO27 | DISP1_DAT23           | i.MX51: DISP1_<br>DAT23                      | LCD2 Data                                    |          |

| J2:25 | GP1027 | DI1_PIN2              | i.MX51: DI1_PIN2                             | HDMI, VGA<br>and LCD1<br>HSYNC               |          |

| J2:26 | -      | GND                   | -                                            | -                                            |          |

| J2:27 | GPIO27 | DI1_PIN11/GPIO3_<br>0 | i.MX51: DI1_PIN11                            | LCD1<br>PWREN#                               |          |

| J2:28 | GP1027 | DI1_DISP_CLK          | i.MX51: DI1_DISP_<br>CLK                     | HDMI, VGA<br>and LCD1<br>Clock               |          |

| J2:29 | GPIO27 | DI1_PIN13/GPIO3_<br>2 | i.MX51: DI1_PIN13                            | LCD1 and<br>LCD2 GPIO2                       |          |

| J2:30 | GP1027 | DI1_PIN3              | i.MX51: DI1_PIN3                             | HDMI, VGA<br>and LCD1<br>VSYNC               |          |

| J2:31 | GP1027 | DI1_PIN15             | i.MX51: DI1_PIN15                            | HDMI, VGA<br>and LCD1<br>DRDY                |          |

| J2:32 | GPIO27 | DI1_PIN12/GPIO3_<br>1 | i.MX51: DI1_PIN12                            | LCD2<br>PWREN#                               |          |

| J2:33 | GPIO27 | DI_GP2                | i.MX51: DI_GP2                               | Not used                                     |          |

| J2:34 | GPIO27 | DI_GP1                | i.MX51: DI_GP1                               | Not used                                     |          |

| J2:35 | GPIO27 | DI_GP4/MII_RXD2       | i.MX51: DI_GP4<br>LAN8710: RXD2              | LCD2 DRDY                                    |          |

| J2:36 | GP1027 | DI_GP3/MII_TX_ER      | i.MX51: DI_GP3<br>LAN8710:<br>INT#/TXER/TXD4 | Not used                                     |          |

| J2:37 | GPIO27 | DI1_D1_<br>CS/GPIO3_4 | i.MX51: DI_D1_CS                             | LCD1 and<br>LCD2 Touch<br>selection<br>input |          |

| Pin   | Туре           | Signal name           | Use on module                     | Use on<br>development<br>board               | Comments                            |

|-------|----------------|-----------------------|-----------------------------------|----------------------------------------------|-------------------------------------|

| J2:38 | GPI027         | DI1_D0_<br>CS/GPIO3_3 | i.MX51: DI_D0_CS                  | LCD1 and<br>LCD2 Touch<br>selection<br>input |                                     |

| J2:39 | ADIN           | TOUCH_X1              | MC13892: TSX1                     | LCD1 and<br>LCD2 Touch<br>X1                 | Analog input from<br>Touch Screen   |

| J2:40 | ADIN           | ADIN5                 | MC13892: ADIN5                    | Reserved                                     |                                     |

| J2:41 | ADIN           | TOUCH_X2              | MC13892: TSX2                     | LCD1 and<br>LCD2 Touch<br>X2                 | Analog input from<br>Touch Screen   |

| J2:42 | ADIN           | ADIN6                 | MC13892: ADIN6                    | Not used                                     | Analog input                        |

| J2:43 | ADIN           | TOUCH_Y1              | MC13892: TSY1                     | LCD1 and<br>LCD2 Touch<br>Y1                 | Analog input from<br>Touch Screen   |

| J2:44 | ADIN           | ADIN7                 | MC13892: ADIN7                    | Not used                                     | Analog input                        |

| J2:45 | ADIN           | TOUCH_Y2              | MC13892: TSY2                     | LCD1 and<br>LCD2 Touch<br>Y2                 | Analog input from<br>Touch Screen   |

| J2:46 | -              | ADC_GND               | -                                 | -                                            |                                     |

| J2:47 | -              | GND                   | -                                 | -                                            |                                     |

| J2:48 | PMIC_<br>STDBY | ADTRIG                | MC13892: ADTRIG                   | Not used                                     |                                     |

| J2:49 | -              | SWBST                 | MC13892: SWBST<br>MC13892: VINUSB | -                                            | Used on the module to power USB PHY |

| J2:50 | -              | LEDKP                 | MC13892: LEDKP                    | Reserved                                     |                                     |

| J2:51 | PMIC_LED       | LEDR                  | MC13892: LEDR                     | Not used                                     |                                     |

| J2:52 | -              | LEDAD                 | MC13892: LEDAD                    | Reserved                                     |                                     |

| J2:53 | PMIC_LED       | LEDG                  | MC13892: LEDG                     | Not used                                     |                                     |

| J2:54 | -              | LEDMD                 | MC13892: LEDMD                    | Reserved                                     |                                     |

| J2:55 | PMIC_LED       | LEDB                  | MC13892: LEDB                     | Not used                                     |                                     |

| J2:56 | -              | VSWLED                | -                                 | -                                            |                                     |

| J2:57 | GPIO27         | CSI2_D12/GPIO4_9      | i.MX51: CSI2_D12                  | Camera 2<br>Data                             |                                     |

| Pin   | Туре     | Signal name               | Use on module                     | Use on<br>development<br>board | Comments |

|-------|----------|---------------------------|-----------------------------------|--------------------------------|----------|

| J2:58 | GPIO27   | CSI2_D13/GPIO4_<br>10     | i.MX51: CSI2_D13                  | Camera 2<br>Data               |          |

| J2:59 | HSGPIO27 | CSI2_D14                  | i.MX51: CSI2_D14                  | Camera 2<br>Data               |          |

| J2:60 | HSGPIO27 | CSI2_D15                  | i.MX51: CSI2_D15                  | Camera 2<br>Data               |          |

| J2:61 | HSGPIO27 | CSI2_D16                  | i.MX51: CSI2_D16                  | Camera 2<br>Data               |          |

| J2:62 | HSGPIO27 | CSI2_D17                  | i.MX51: CSI2_D17                  | Camera 2<br>Data               |          |

| J2:63 | GPIO27   | CSI2_D18/GPIO4_<br>11     | i.MX51: CSI2_D18                  | Camera 2<br>Data               |          |

| J2:64 | GPIO27   | CSI2_D19/GPIO4_<br>12     | i.MX51: CSI2_D19                  | Camera 2<br>Data               |          |

| J2:65 | GPIO27   | CSI2_<br>VSYNC/GPIO4_13   | i.MX51: CSI2_<br>VSYNC            | Camera 2<br>VSYNC              |          |

| J2:66 | GPIO27   | CSI2_<br>HSYNC/GPIO4_14   | i.MX51: CSI2_<br>HSYNC            | Camera 2<br>HSYNC              |          |

| J2:67 | GPIO27   | CSI2_PIXCLK_<br>GPIO4_15  | i.MX51: CSI2_<br>PIXCLK           | Camera 2<br>PIXCLK             |          |

| J2:68 | -        | GND                       |                                   | -                              |          |

| J2:69 | -        | GND                       |                                   | -                              |          |

| J2:70 | DIG_USB  | USB_OTG_ID                | i.MX51: ID                        | USB OTG ID                     |          |

| J2:71 | AN_USB   | USB_OTG_DP                | i.MX51: DP                        | USB OTG DP                     |          |

| J2:72 | -        | USB_OTG_VBUS              | i.MX51: VBUS                      | USB OTG<br>VBUS                |          |

| J2:73 | AN_USB   | USB_OTG_DN                | i.MX51: DN                        | USB OTG DN                     |          |

| J2:74 | GPIO27   | GPIO1_8/USB_<br>PWR       | i.MX51: GPIO_8                    | Not used                       |          |

| J2:75 | -        | GND                       | -                                 | -                              |          |

| J2:76 | GPIO27   | GPIO1_<br>2/PWM1/I2C2_SCL | i.MX51: GPIO1_2<br>MMA7455LR1:SCL | I <sup>2</sup> C Bus Clock     |          |

| Pin   | Туре     | Signal name                       | Use on module                                 | Use on<br>development<br>board | Comments                                                                                                |

|-------|----------|-----------------------------------|-----------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------|

| J2:77 | GPIO27   | GPIO1_<br>7/MMA7455LR_<br>INT1    | i.MX51: GPIO1_7<br>MMA7455LR1:INT1            | Reserved                       | Accelerometer interrupt                                                                                 |

| J2:78 | GPIO27   | GPIO1_<br>3/PWM2/I2C2_SDA         | i.MX51: GPIO1_3<br>MMA7455LR1:SD              | I <sup>2</sup> C Bus Clock     |                                                                                                         |

| J2:79 | GPIO27   | GPIO1_<br>6/MMA7455LR_<br>INT2    | i.MX51: GPIO1_6<br>MMA7455LR1:INT2            | Reserved                       | Accelerometer<br>Interrupt                                                                              |

| J2:80 | PMIC_INT | CLK32K_PER                        | MC13892: CLK32K                               | Not used                       |                                                                                                         |

| J2:81 | -        | GND                               | -                                             | -                              |                                                                                                         |

| J2:82 | -        | GND                               | -                                             | -                              |                                                                                                         |

| J2:83 | -        | CKIH1                             | i.MX51: CKIH1                                 | Not used                       |                                                                                                         |

| J2:84 | -        | CKIH2                             | i.MX51: CKIH2                                 | Not used                       |                                                                                                         |

| J2:85 | UHVIO33  | SD2_DATA0/SD1_<br>DATA1/CSPI_MISO | i.MX51: SD2_<br>DATA0<br>WLAN: SDIO_<br>DATA0 | Reserved                       | SD bus 2 connected to WLAN.  In modules without WLAN this SD bus can be used in the development boards. |

| J2:86 | UHVIO33  | SD2_CLK/I2C1_<br>SDA/SPI_SCLK     | i.MX51: SD2_CLK<br>WLAN: SDIO_CLK             | Reserved                       |                                                                                                         |

| J2:87 | UHVIO33  | SD2_DATA1/SD1_<br>DATA5           | i.MX51: SD2_<br>DATA1<br>WLAN: SDIO_<br>DATA1 | Reserved                       |                                                                                                         |