AP43781

### USB PD CONTROLLER SUPPORTING DISPLAYPORT OVER TYPE-C ALTERNATE MODE

### **Description**

The AP43781 is a highly integrated USB Type-C<sup>®</sup> power delivery controller targeted for monitor or TV power board with USB Type-C ports. It supports USB power delivery specification Rev3.1 SPR (Standard Power Range) with full range of programmable power supply (PPS).

The AP43781 can support PPS APDO (Augmented Power Data Object) with resolution of 20mV/step in voltage and 50mA/step in current. In addition, cable-loss compensation and e-Marker detection are provided.

After the power negotiation is established, AP43781 can support DisplayPort™ by decoding out the CC signal and then deliver the routing control and signaling information to the high-speed switches and the re-driver/re-timer ICs through I2C interface, where the I2C bus can be assigned as master or slave, and GPIO pins can be programmed for different applications.

The AP43781 can offer comprehensive safety protection schemes, including overvoltage protection (OVP), undervoltage protection (UVP), overcurrent protection (OCP), short-circuit protection (SCP) and/or overtemperature protection (OTP).

A one-time programmable ROM is provided for main firmware, and a multi-time programmable ROM is provided for user configuration data.

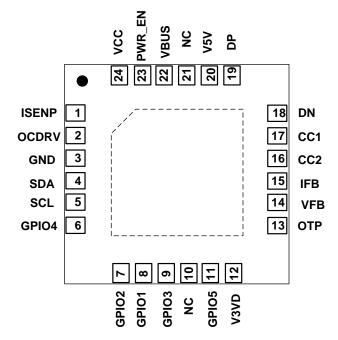

## **Pin Assignments**

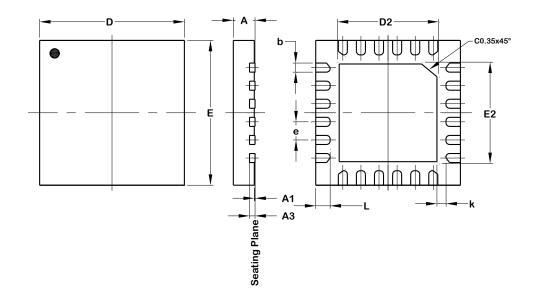

W-QFN4040-24 (Type A1)

### **Features**

- Compatible with USB PD Rev3.1 SPR

- Support Full Range of PPS 3.3V to 21V with Resolution of 20mV/Step in Voltage and 50mA/Step in Current.

- Support Type-C Alternative Mode for DisplayPort

- Built-in Regulator for CV and CC Control

- Support OVP/UVP/OCP/SCP/OTP with Auto Restart

- Support Power Saving Mode

- Driver for Output Enable nMOS Switch

- Support E-Marker Cable Detection

- Support I2C Interface with Master and Slave Flexibility

- Operating Voltage Range: 3.3V to 24V

- OTP (One-Time Programmable) for Main Firmware

- MTP (Multi-Time Programmable) for System Configuration

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative. <a href="https://www.diodes.com/quality/product-definitions/">https://www.diodes.com/quality/product-definitions/</a>

## **Applications**

- Monitors with Type-C ports

- TV power boards with Type-C ports

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

AP43781 1 of 11

Document number: DS45748 Rev. 3 - 2 www.diodes.com © 2023 Copy

### **Typical Applications Circuit**

Virtual monitor with demo board

(12V~18V)

AC Adapter

The AP43781 not only supports USB PD power profile negotiation with the sink controller, but also provides the data link capability to the sink device. Figure 1 illustrates how the AP43781 of the CLM (Type-C-Link-to-Monitor) module is used to play as a PD power source controller with support for DisplayPort application.

When the Type-C attachment is completed between an active CLM module and the NB host, the power profile negotiation is started through the CC commands. After the negotiation is completed, the AP43781 will enable the buck-boost controller to provide the matched power to the NB host.

At the same time, the AP43781 plays as a data down-facing port, and enters the alternative mode support by decoding out the VDM (Vendor Defined Message) CC commands delivered from NB host side. The decoded information is then sent out through the I2C interface to the high-speed switches (i.e. PI3USB31531) and signaling chips (i.e. PI3DPX1207C), so that the data stream can be delivered from host side to the DisplayPort at the right routing path and with correct signaling accordingly.

#### **CLM** board USB 3.1 Device PI4IOE5V9554 USB Type-C<sup>®</sup> Power Source DFP (Down-Facing Port) USB 3.1 PD Charging (100W, 20V@5A) Data Transfer UFP (Up-Facing Port) USB Type-C Alternate Mode TX1 (DisplayPort) USB Lane 0-3 RX2 # USB 31 Gen 1 / Gen 2 Type-C Switch TX2 # Support Pin C. D and E Assignment PI3USB31531 SBU1 Standby Power < 20mWatt</p> Monitor AUX N SBU2 DP-DP DisplayPort E-Marker C-C

PD3.1 SPR Controller (AP43781)

Figure 1. The AP43781 Supports DP Alternative Mode for Data Link During the Power Sourcing

# **Pin Descriptions**

| Pin Number | Pin Name | Function                                                                                                       |

|------------|----------|----------------------------------------------------------------------------------------------------------------|

| 1          | ISENP    | Input Current Sense Positive Node                                                                              |

| 2          | OCDRV    | CC/CV Output. Open-Drain Output for Optocoupler.                                                               |

| 3          | GND      | Ground                                                                                                         |

| 4          | SDA      | GPIO/I2C Data                                                                                                  |

| 5          | SCL      | GPIO/I2C Clock                                                                                                 |

| 6          | GPIO4    | General-Purpose Input or Output                                                                                |

| 7          | GPIO2    | General-Purpose Input or Output                                                                                |

| 8          | GPIO1    | General-Purpose Input or Output                                                                                |

| 9          | GPIO3    | General-Purpose Input or Output                                                                                |

| 10         | NC       | No Connection                                                                                                  |

| 11         | GPIO5    | General-Purpose Input or Output                                                                                |

| 12         | V3VD     | LDO-3V Output                                                                                                  |

| 13         | OTP      | Source Current to External NTC Sensor for OTP (Overtemperature Protection). Current amplitude is programmable. |

| 14         | VFB      | CV Input. Negative Node of CV OPAMP for Optocoupler.                                                           |

| 15         | IFB      | CC Input. Negative Node of CC OPAMP for Optocoupler.                                                           |

| 16         | CC2      | Type-C_CC2                                                                                                     |

| 17         | CC1      | Type-C_CC1                                                                                                     |

| 18         | DN       | Type-C_DN                                                                                                      |

| 19         | DP       | Type-C_DP                                                                                                      |

| 20         | V5V      | LDO-5V Output, Connected to a Decoupling Capacitor.                                                            |

| 21         | NC       | No Connection                                                                                                  |

| 22         | VBUS     | Output Terminal for Discharge Path                                                                             |

| 23         | PWR_EN   | External nMOS Gate Driver. To control external MOS switch, 1: To enable VBUS voltage.  0: Disconnect VBUS.     |

| 24         | VCC      | The Power Supply of The IC, Connected to a Ceramic Capacitor.                                                  |

Table 1. The AP43781 Pinout Description

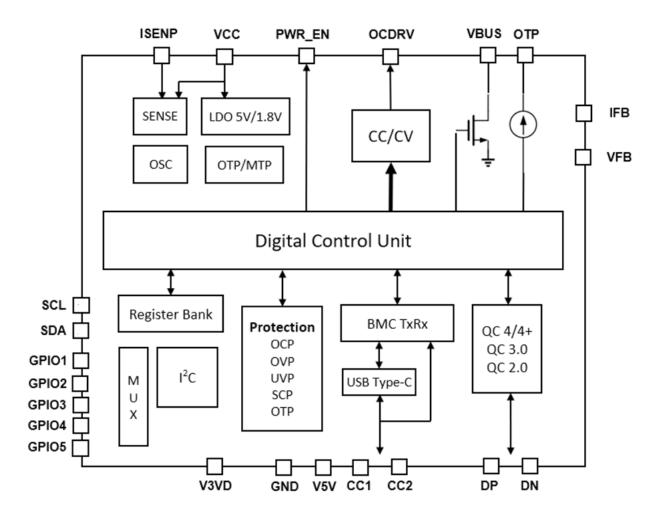

## **Functional Block Diagram**

Figure 2. The AP43781 Block Diagram

## **Absolute Maximum Ratings** (Note 4)

| Symbol                                                                                                                         | Parameter                                                                                                  | Rating                 |           | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------|-----------|------|

| Vvcc                                                                                                                           | Input Voltage at VCC Pin -0.3 to 24                                                                        |                        |           | V    |

| V <sub>VFB</sub> , V <sub>IFB</sub> , V <sub>OTP</sub>                                                                         | Input Voltage at VFB, IFB, OTP Pins                                                                        | -0.3 to 7              |           | V    |

| VVBUS, VPWR_EN, VISENP, VOCDRV                                                                                                 | Input Voltage at VBUS, PWR_EN, ISENP, OCDRV Pins                                                           | -0.3 to 24             |           | V    |

| _                                                                                                                              | Voltage from PWR_EN to VCC Pin                                                                             | -16 to 7               |           | V    |

| V <sub>V5V</sub>                                                                                                               | Input Voltage at V5V Pin                                                                                   | -0.3 to 7              |           | V    |

| VCC1, VCC2                                                                                                                     | Input Voltage at CC1, CC2 Pins                                                                             | -0.3 to 7              |           | V    |

| V <sub>DP</sub> , V <sub>DN</sub>                                                                                              | Input Voltage at DP, DN Pins                                                                               | -0.3 to 7              |           | V    |

| V <sub>GPIO1</sub> - V <sub>GPIO5</sub> , V <sub>SDA</sub> , V <sub>SCL</sub> Input Voltage at GPIO1-5, SDA, SCL Pins (Note 5) |                                                                                                            | -0.3 to 5              | -0.3 to 5 |      |

| TJ                                                                                                                             | Operating Junction Temperature                                                                             | -40 to +150            |           | °C   |

| T <sub>STG</sub>                                                                                                               | Storage Temperature -65 to +150                                                                            |                        |           | °C   |

| T <sub>LEAD</sub> Lead Temperature (Soldering, 10s)                                                                            |                                                                                                            | +300                   |           | °C   |

| θμΑ                                                                                                                            | Thermal Resistance (Junction to Ambient) (Note 6)                                                          | W-QFN4040-24 (Type A1) | 28        | °C/W |

| θ <sub>JC</sub> Thermal Resistance (Junction to Case) (Note 6)                                                                 |                                                                                                            | W-QFN4040-24 (Type A1) | 16        | °C/W |

| _                                                                                                                              | ESD (Human Body Model) Voltage on DP, DN Pins                                                              | 6                      |           | kV   |

| _                                                                                                                              | ESD (Human Body Model) Voltage on<br>VBUS, ISENP, PWR_EN, VCC, OCDRV,<br>OTP, V5V, IFB, VFB, CC1, CC2 Pins | 2                      |           | kV   |

|                                                                                                                                | ESD (Charged Device Model)                                                                                 | 750                    |           | V    |

Notes:

- 4. Stresses greater than those listed under Absolute Maximum Ratings can cause permanent damage to the device. These are stress ratings only, and 4. Stesses greater than inlose listed under *Absolute Maximum Ratings* can cause permitted under *Recommended Operating Conditions* is not implied. Exposure to *Absolute Maximum Ratings* for extended periods can affect device reliability.

5. When GPIO1-5, SDA, and SCL pins are pulled high to a voltage source, it is strongly recommended to series a resistor with minimum 10k value.

6. Test condition: device mounted on FR-4 substrate PC board, 2oz copper, with the minimum footprint.

# **Recommended Operating Conditions**

| Symbol | Parameter                   | Min | Max | Unit |

|--------|-----------------------------|-----|-----|------|

| Vvcc   | Power Supply Voltage        | 3.3 | 24  | V    |

| Тор    | Operating Temperature Range | -40 | +85 | °C   |

## **Electrical Characteristics** (@TA = +25°C, unless otherwise specified.)

| Symbol                                                        | Parameter                                                                                      | Condition                          | Min   | Тур  | Max   | Unit |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------|-------|------|-------|------|

| VCC PIN SECTION                                               |                                                                                                |                                    |       |      |       |      |

| V <sub>ST</sub> Startup Voltage -                             |                                                                                                | _                                  | 2.5   | 2.8  | 3.2   | V    |

| V <sub>UVLO</sub> Minimum Operating Voltage                   |                                                                                                | _                                  | 2.4   | 2.7  | 3     | V    |

| Vvcc_hys                                                      | Vvcc Hysteresis (VsT-VuvLo)                                                                    | _                                  | 0.05  | _    | _     | V    |

| IVCC_DEEP SLEEP                                               | V <sub>IN</sub> Current in Deep Sleep Mode                                                     | CC1/2 Detach after 3s<br>Vvcc = 5V | _     | 550  | 900   | μΑ   |

| I <sub>VCC_OPR</sub>                                          | Operating Supply Current                                                                       | V <sub>VCC</sub> = 5V              | _     | 3.3  | 6     | mA   |

| VOLTAGE CONTROL                                               | LOOP SECTION                                                                                   |                                    |       |      |       |      |

| VREF_CV5                                                      | Reference Voltage for 5V CV Control                                                            | _                                  | 4.85  | 5    | 5.15  | V    |

| VREF_CV9                                                      | Reference Voltage for 9V CV Control                                                            | _                                  | 8.73  | 9    | 9.27  | V    |

| VREF_CV12                                                     | Reference Voltage for 12V CV Control                                                           | _                                  | 11.64 | 12   | 12.36 | V    |

| VCABLE                                                        | Cable Compensation (Note 7)                                                                    | _                                  | 22    | 32   | 42    | mV/A |

| los                                                           | Maximum OCDRV Pin Sink Current                                                                 | Vout = 5V                          | 10    | 16   | 30    | mA   |

| PROTECTION FUNCT                                              | TON SECTION                                                                                    |                                    | •     |      | •     |      |

| V <sub>O</sub> VP5V                                           | OVP_5V Enable Voltage (Note 8)                                                                 | _                                  | 5.6   | 6    | 6.8   | V    |

| V <sub>OVP9V</sub>                                            | OVP_9V Enable Voltage (Note 8)                                                                 | _                                  | 9.9   | 10.8 | 12.1  | V    |

| Vovp12V                                                       | OVP_12V Enable Voltage (Note 8)                                                                | _                                  | 13.2  | 14.4 | 16.2  | V    |

| tdebounce_ovp                                                 | OVP Debounce Time (Note 9)                                                                     | _                                  | _     | 90   | _     | ms   |

| V <sub>UVP5V</sub> UVP_5V Enable Voltage                      |                                                                                                | _                                  | 3.3   | 3.7  | 4.4   | V    |

| Vuvp9v                                                        | UVP_9V Enable Voltage                                                                          | _                                  | 5.9   | 6.8  | 7.7   | V    |

| V <sub>UVP12V</sub>                                           | UVP_12V Enable Voltage                                                                         | _                                  | 7.9   | 9.1  | 10    | V    |

| I <sub>OVD</sub> Overvoltage Discharge Current                |                                                                                                | Vvcc = 5V                          | 150   | 200  | 250   | mA   |

| tocp                                                          | OCP Deglitch Time (Note 10)                                                                    | _                                  | _     | 30   | _     | ms   |

| trestart_interval_scp                                         | Restart Interval Time under SCP (Note 10)                                                      | _                                  | _     | 0.8  | _     | S    |

| Тотр                                                          | Internal OTP Temperature (Note 10)                                                             | _                                  | _     | +140 | _     | °C   |

| I <sub>OTP_EXTERNAL</sub>                                     | External OTP Current                                                                           | _                                  | 90    | 100  | 110   | μA   |

| Thys                                                          | OTP Recovery Hysteresis Temperature (Note 10)                                                  | _                                  | _     | +25  | _     | °C   |

| tsleep                                                        | Enter Sleep Mode Time after Cable Detached (Note 10)                                           | _                                  | _     | 3    | _     | s    |

| tov_delay                                                     | Delay from OVP Threshold Trip to nMOS<br>Gate Turn-Off (Note 10)                               | _                                  | _     | _    | 50    | μs   |

| Delay from UVP Threshold Trip to nMOS Gate Turn-Off (Note 10) |                                                                                                | _                                  | _     | 30   | _     | ms   |

| CC1/CC2, DP/DN PIN                                            |                                                                                                |                                    | _     |      | _     |      |

| V <sub>L_RD3A</sub>                                           | Low Voltage Threshold Used to Distinguish RD Attached or Detached for 3A Delivery              | _                                  | _     | 1.35 | _     | V    |

| V <sub>H_RD3A</sub>                                           | High Voltage Threshold Used to Distinguish R <sub>D</sub> Attached or Detached for 3A Delivery | _                                  | _     | 2.0  | _     | V    |

| lrdза                                                         | CC1/CC2 Current Source for 3A<br>Advertisement                                                 | V <sub>VCC</sub> = 5V              | 304   | 330  | 356   | μΑ   |

| V <sub>OVP_DN</sub>                                           | DN Line Overvoltage Protection Threshold                                                       | _                                  | 4.1   | 4.5  | 4.8   | V    |

| $V_{OVP\_DP}$                                                 | DP Line Overvoltage Protection Threshold                                                       | _                                  | 4.1   | 4.5  | 4.8   | V    |

Notes:

<sup>7.</sup> Cable compensation voltage can be adjusted by setting from 0 to  $V_{CABLE \, {}^{\star} \, N}$  (N: 0 to 7).

<sup>8. 120%</sup> OVP setting & 76% UVP setting.

9. OVP blanking time during V<sub>O</sub> transition from high output voltage to low output voltage, such as 9V to 5V, or 12V to 5V.

10. Guaranteed by design.

### **Performance Characteristics**

#### System Power-On Sequence

Once external power is supplied to the VCC pin, the AP43781 will wake up. All analog control blocks will get ready, and then the digital block and MCU engine will start initialization flow. After the power-on initialization, the system closed loop is established by the AP43781 and the power module is ready for the Type-C PD negotiation process.

### **Cable Attachment and Power On Initialization**

Once the Type-C cable is plugged into the NB or the sink device from the powered PD source, the Rd on the sink side will pull down one of the CC1/CC2 channel to establish a CC routing path, and then the CC/VCONN configuration is completed. After the cable attachment, the source adapter enables VBUS with 5V, and starts VCONN power supply to enable cable e-Marker to check its current handling capability. After that, the PD source adapter starts broadcasting PD source capabilities to the PD sink through CC pin. Meanwhile, the NB or the sink device can decode the CC packet to get the source capability, and then starts a PD negotiation process to request the PD source to output a suitable power profile.

#### **Voltage Transition**

When the sink and source make an acceptable power request deal, the AP43781 will provide the VBUS with the requested voltage and current capability through the VFB control feedback or I2C communication to the DC/DC controller. During the voltage transition, the feedback system stability of AP43781 and DC/DC controller should be carefully designed to guarantee monotonic voltage transition and avoid violating USB PD electrical specification.

#### **DisplayPort Alternate Mode Support**

After the PDO negotiation is completed, the AP43781 plays as a data Upstream Facing Port (UFP), and enter the alternative mode support by decoding out the VDM (Vendor Defined Message) commands delivered by the host side. The AP43781 supports DisplayPort Alternate Mode on USB Type-C standard with Discover Identify, Discover SVIDs, Discover Modes, Enter Mode, DP Status, DP Configure, and Exit Mode. The decoded information is then sent out to the high-speed switches (i.e. PI3USB31531) and signaling chips (i.e. PI3DPX1207C) through the I2C interface, so that the data stream can be delivered from host side to the DisplayPort at the right routing path and correct signaling accordingly.

#### CV/CC

The AP43781 supports Constant Voltage (CV) and Constant Current (CC) functions to control the output voltage and the output current by the control pin OCDRV. During the CV mode, the AP43781 operates in fixed PDO, and the output voltage will be regulated to the request voltage if the output current is below the allowed maximum current. Once the sink device draws more than IoCP, the overcurrent protection occurs. When the CC mode function is enabled, the output voltage drops, and the source current is limited within 150mA whenever output current exceeds the allowed maximum current. When the output voltage drops below UVP, the constant current limit turns off VBUs and starts error recovery procedure. The AP43781 will reset if the voltage continues dropping to the UVLO threshold.

#### Protection

The AP43781 provides OVP/UVP/OCP/SCP/OTP functions and supports Constant Current (CC) function. All of the protection thresholds depend on the requested power profile, and provide the most reliable protection scheme.

The AP43781 provides OVP feature by turning off the power switch when V<sub>BUS</sub> is higher than OVP enable voltage. Meanwhile, it provides an internal discharge path to reduce the overvoltage duration, and terminates discharge current as soon as V<sub>BUS</sub> reaches the target voltage. To prevent the VBUS pin from working abnormally, the AP43781 provides UVP function whenever V<sub>BUS</sub> drops to UVP enable voltage.

To ensure the safe operation of USB PD, the AP43781 provides programmable OCP function to make sure output current will not be higher than the allowed maximum current. Once OCP conditions happen, the AP43781 will shut down the USB PD system and send "Hard Reset" to the host side.

#### MCU and OTP/MTP ROM

The AP43781 has an MCU subsystem, which integrates an 8-bit 8051 processor, SRAM, and OTP ROM. The MCU subsystem is optimized for user configurability of different topologies, supporting different protocols, and low-power consumption at a low cost. With the embedded hardware PHY transceivers offloading MCU processing, the AP43781 can handle PD handshakes efficiently, and be compliant with critical USB Power Delivery specifications.

An OTP ROM is provided to store PD, QC, and FCP protocol firmware, and an MTP ROM is provided for user configuration table. Either in-system programming or offline socket programming are provided for the OTP ROM and MTP ROM.

### **Performance Characteristics** (continued)

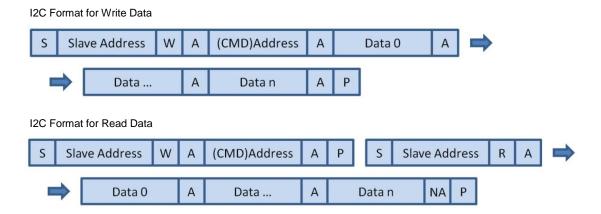

#### **I2C Interface**

The I2C interface pins (SCK, SDA), as shown in below Table 2, are used to communicate between the PD decoder and DC/DC controller/converter to replace analog signal feedback of VFB with much higher noise immunity. I2C commands are supported by firmware so that it can monitors and changes status of other I2C devices

| Pin No. | Pin Name | Pin Function |

|---------|----------|--------------|

| 4       | SDA      | I2C Data     |

| 5       | SCL      | I2C Clock    |

Table 2. I2C Interface of the AP43781 Supports Both Master and Slave Modes

The AP43871 can play as an I2C master or slave device. The I2C read and write operations are supported as below.

All transactions begin with a START (S) and be terminated by a STOP (P). A START condition is defined whenever a HIGH to LOW transition on the SDA while SCL is HIGH. A STOP condition is defined whenever a LOW to HIGH transition on the SDA while SCL is HIGH. The START and STOP conditions are always generated by the master.

Figure 3. The I2C Command Format in AP43781

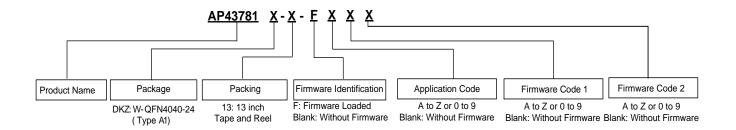

## **Ordering Information**

| Part Number        | Dookers                | Identification Code | Packing |                   |  |

|--------------------|------------------------|---------------------|---------|-------------------|--|

| Part Number        | Package                | Identification Code | Qty.    | Carrier           |  |

| AP43781DKZ-13-FXXX | W-QFN4040-24 (Type A1) | 6K                  | 3000    | 13" Tape and Reel |  |

## **Marking Information**

### W-QFN4040-24 (Type A1)

## (Top View)

6K : Identification Code

$\underline{Y}$ : Year: 0 to 9 (ex: 3 = 2023)  $\underline{W}$ : Week: A to Z: week 1 to 26;

a to z : week 27 to 52; z represents

week 52 and 53  $\underline{X}$ : Internal Code

## **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

### W-QFN4040-24 (Type A1)

| W-QFN4040-24         |           |        |      |  |

|----------------------|-----------|--------|------|--|

|                      | (Type A1) |        |      |  |

| Dim                  | Min       | Max    | Тур  |  |

| Α                    | 0.70      | 0.80   | 0.75 |  |

| A1                   | 0.00      | 0.05   | 0.02 |  |

| A3                   | 0         | .203 R | EF   |  |

| b                    | 0.18      | 0.30   | 0.25 |  |

| D                    | 4.00 BSC  |        |      |  |

| D2                   | 2.65      | 2.75   | 2.70 |  |

| Е                    | 4.00 BSC  |        |      |  |

| E2                   | 2.65      | 2.75   | 2.70 |  |

| е                    | 0.50 BSC  |        |      |  |

| k                    | 0.20      |        |      |  |

| L                    | 0.35      | 0.45   | 0.40 |  |

| All Dimensions in mm |           |        |      |  |

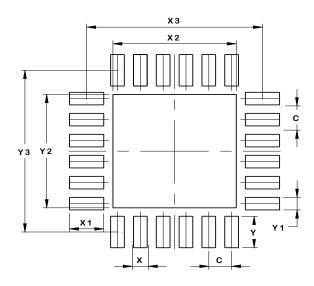

## **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

### W-QFN4040-24 (Type A1)

| Dimensions | Value<br>(in mm) |  |

|------------|------------------|--|

| С          | 0.500            |  |

| Х          | 0.300            |  |

| X1         | 0.750            |  |

| X2         | 2.700            |  |

| Х3         | 3.850            |  |

| Υ          | 0.750            |  |

| Y1         | 0.300            |  |

| Y2         | 2.700            |  |

| Y3         | 3.850            |  |

### **Mechanical Data**

- Moisture Sensitivity: Level 1 per J-STD-020

- Terminals: Finish Matte Tin Plated Leads, Solderable per J-STD-202 @3

- Weight: 0.041 grams (Approximate)

#### **IMPORTANT NOTICE**

- DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

- The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functionalsafety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

- Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

- Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

- products provided subject to Diodes' (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

- While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

- Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

- This Notice may be periodically updated with the most recent version available at https://www.diodes.com/about/company/terms-andconditions/important-notice

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. All other trademarks are the property of their respective owners. © 2023 Diodes Incorporated. All Rights Reserved.

www.diodes.com

11 of 11 AP43781 July 2023 www.diodes.com © 2023 Copyright Diodes Incorporated. All Rights Reserved.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Management Specialised - PMIC category:

Click to view products by Diodes Incorporated manufacturer:

Other Similar products are found below:

FAN7710VN LA5657H-N-TLM-E LM10692RMYR SLG7NT4081VTR SLG7NT4192VTR AS3729B-BWLM MB39C831QN-G-EFE2 RT9026GQW LV56841PVD-XH L9781TR P91E0-I5NHGI S6AE102A0DGN1B200 L9916 AP4306BUKTR-G1 SLG7NT4198V NCP392CSFCCT1G LPTM21L-1ABG100I ISL99390FRZ-TR5935 ISL69234IRAZ-T ISL69259IRAZ ISL69228IRAZ ISL69269IRAZ AXP813 FAN53870UC00X FDMF5085 HPM10-W29A100G NCV97311MW50R2G WL2868C-20/TR TLE9263-3BQX TLE9263QX TEA2095T/1J TEA2017AAT/2Y TPS650940A0RSKR TPS65177ARHAR LTC4417IUF#TRPBF AXP313A SQ24806AQSC RK805-2 RK809-2 MFS2633AMBA0AD MFS2613AMDA3AD AD5522JSVUZ-RL LTC4352CMS#TRPBF LTC4359HDCB#TRPBF LT4321IUF#TRPBF TC1017-2.5VLTTR MFS5600AMMA8ES TEA1716T/2 MC33FS8510D3ESR2 MMPF0100NPAZESR2