#### 2.5Gbps x1 Lane Serial PCI-Express Repeater/Equalizer with Clock Buffer & Signal Detect Feature

#### Features

- → One high-speed PCI-Express lane

- → Adjustable Transmiter De-Emphasis & Amplitude

- → Adjustable Receiver Equalization

- → One Spread Spectrum Reference Clock Buffer Output

- → Input Signal Level Detect and Output Squelch

- → 100 $\Omega$  Differential CML I/O's

- → Low Power (100mW per Channel)

- → Stand-by Mode Power Down State

- → V<sub>DD</sub> Operating Range: 1.8V ±0.1V

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

- $\rightarrow$  For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative.

https://www.diodes.com/guality/product-definitions/

→ Packaging (Pb-free & Green): — 36-pad TQFN (ZF36)

#### Description

Diodes' PI2EQX4401D is a low power, PCI-Express compliant signal re-driver. The device provides programmable equalization, amplification, and de-emphasis by using 4 select bits, SEL[0:3], to optimize performance over a variety of physical mediums by reducing Inter-symbol interference. PI2EQX4401D supports two 100Ω Differential CML data I/O's between the Protocol ASIC to a switch fabric, across a backplane, or extends the signals across other distant data pathways on the user's platform.

The integrated equalization circuitry provides flexibility with signal integrity of the PCI-express signal before the re-driver. Whereas the integrated de-emphasis circuitry provides flexibility with signal integrity of the PCI-express signal after the Re-Driver.

A low-level input signal detection and output squelch function is provided for both channels. Each channel operates fully independently. When a channel is enabled (EN x=1) and operating, that channel's input signal level (on xl+/-) determines whether the output is enabled. If the input level of the channel falls below the active threshold level (Vth-) then the output driver switches off, and the pin is pulled to VDD via a high impedance resistor.

In addition to providing signal re-conditioning, Diodes' PI2EQX4401D also provides power management Stand-by mode operated by a Bus Enable pin. A differential clock buffer is provided for test and other system requirements. This clock function is not used by the data channels.

Notes:

<sup>1.</sup> No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

<sup>2.</sup> See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free. 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm

antimony compounds.

# **Pin Description**

| Pin #            | Pin Name        | I/O | Description                                                                                                                                               |  |

|------------------|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 6, 10, 23, 28 | V <sub>DD</sub> | PWR | 1.8V Supply Voltage                                                                                                                                       |  |

| 2                | AI+             | Ι   | Positive CML Input Channel A with internal 50 $\Omega$ pull down during normal operation (EN_A=1). When EN_A=0, this pin is high-impedance.               |  |

| 3                | AI-             | Ι   | Negative CML Input Channel A with internal 50 $\Omega$ pull down during normal operation (EN_A=1). When EN_A=0, this pin is high-impedance.               |  |

| 4, 9, 20, 25     | GND             | PWR | Supply Ground                                                                                                                                             |  |

| 22               | BI+             | Ι   | Positive CML Input Channel B with internal 50 $\Omega$ pull down during normal operation (EN_B=1). When EN_B=0, this pin is high-impedance.               |  |

| 21               | BI-             | Ι   | Negative CML Input Channel B with internal $50\Omega$ pull down during normal operation (EN_B=1). When EN_B=0, this pin is high-impedance.                |  |

| 34, 33           | SEL[0:1]_A      | Ι   | Selection pins for equalizer (see Amplifier Configuration Table)                                                                                          |  |

| 13, 14           | SEL[0:1]_B      | Ι   | w/ 50K $\Omega$ internal pull up                                                                                                                          |  |

| 32               | SEL[2]_A        | Ι   | Selection pins for amplifier (see Amplifier Configuration Table)                                                                                          |  |

| 15               | SEL[2]_B        | Ι   | w/ 50K $\Omega$ internal pull up                                                                                                                          |  |

| 31               | SEL[3]_A        | Ι   | Selection pins for De-Emphasis (See De-Emphasis Configuration Table)                                                                                      |  |

| 16               | SEL[3]_B        | Ι   | w/ 50K $\Omega$ internal pull up                                                                                                                          |  |

| 27               | AO+             | О   | Positive CML Output Channel A internal $50\Omega$ pull up during normal operation and $2K\Omega$ pull up otherwise.                                       |  |

| 26               | AO-             | О   | Negative CML Output Channel A with internal 50 $\Omega$ pull up during normal opera and 2K $\Omega$ pull up otherwise.                                    |  |

| 7                | BO+             | О   | Positive CML Output Channel B with internal 50 $\Omega$ pull up during normal operati<br>and 2K $\Omega$ pull up otherwise.                               |  |

| 8                | BO-             | 0   | Negative CMLOutput Channel B with internal 50 $\Omega$ pull up during normal operation and 2K $\Omega$ pull up otherwise.                                 |  |

| 30, 29           | EN_[A,B]        | Ι   | EN_[A:B] is the enable pin. A LVCMOS high provides normal operation. A LVC-MOS low selects a low power down mode.                                         |  |

| 12               | CLKIN-          | Ι   | Differential Input Reference Clock. If clock buffer is not used, then both CLKIN+,                                                                        |  |

| 11               | CLKIN+          | Ι   | CLKIN- should be pulled high to VDD.                                                                                                                      |  |

| 17, 18           | OUT+, OUT-      | 0   | Differential Reference Clock Output                                                                                                                       |  |

| 5                | AVDD            | PWR | 1.8V Analog supply voltage                                                                                                                                |  |

| 24               | AGND            | PWR | Analog ground                                                                                                                                             |  |

| 19               | IREF            | 0   | External $475\Omega$ resistor connection to set the differential output current. If the clock buffer is not used, then IREF should be unconnected (open). |  |

| 36, 35           | SIG_A, SIG_B    | 0   | SIG Detector output for channel A-B. Provides a LVCMOS high output when an input signal greater than the threshold is detected                            |  |

**De-emphasis** 0dB

-3.5dB

#### **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                | 65°C to +150°C                |

|------------------------------------|-------------------------------|

| Supply Voltage to Ground Potential |                               |

| DC SIG Voltage                     | 0.5V to V <sub>DD</sub> +0.5V |

| Current Output                     | 25mA to +25mA                 |

| Power Dissipation Continous        | 500mW                         |

| Operating Temperature              | 0 to +70°C                    |

|                                    |                               |

#### Note:

**Output De-emphasis Adjustment**

SEL3 [A:B]

0 1

Stresses greater than those listed under MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Output Swing Control**

| SEL2_[A:B] | Swing |

|------------|-------|

| 0          | 1x    |

| 1          | 1.2x  |

#### **Equalizer Selection**

| SEL0_[A:B] | SEL1_[A:B] | <b>Compliance Channel</b> |

|------------|------------|---------------------------|

| 0          | 0          | no equalization           |

| 0          | 1          | [0:2.5dB] @ 1.25 GHz      |

| 1          | 0          | [2.5:4.5dB] @ 1.25 GHz    |

| 1          | 1          | [4.5:6.5dB] @ 1.25 GHz    |

Note:

Design target specification. Absolute values will be based on characterization. 1.

#### AC/DC Electrical Characteristics ( $V_{DD} = 1.8 \pm 0.1V$ )

| Symbol                  | Parameter                                  | Conditions                  | Min.    | Тур. | Max.  | Units   |  |

|-------------------------|--------------------------------------------|-----------------------------|---------|------|-------|---------|--|

| Da                      | Consta Domon                               | EN = LVCMOS Low             | AOS Low |      | 0.1   |         |  |

| Ps                      | Supply Power                               | EN = LVCMOS High            |         |      | 0.6   | W       |  |

|                         | Latency                                    | From input to output        |         | 2.0  |       | ns      |  |

| CML Receive             | er Input                                   |                             |         |      |       |         |  |

| RL <sub>RX</sub>        | Return Loss                                | 50 MHz to 1.25 GHz          |         | 12   |       | dB      |  |

| V <sub>RX-DIFFP-P</sub> | Differential Input Peak-to-peak<br>Voltage |                             | 0.175   |      | 1.200 | V       |  |

| V <sub>RX-CM-ACP</sub>  | AC Peak Common Mode Input<br>Voltage       |                             |         |      | 150   | mV      |  |

| V <sub>TH-</sub>        | Signal Detection Threshold                 | EN_x=High                   |         | 120  | 175   | mV      |  |

| Z <sub>RX-DIFF-DC</sub> | DC Differential Input<br>Impedance         |                             | 80      | 100  | 120   | Ω       |  |

| Z <sub>RX-DC</sub>      | DC Input Impedance                         |                             | 40      | 50   | 60    |         |  |

| Equalization            |                                            |                             |         |      |       |         |  |

| J <sub>RS</sub>         | Decidual litter                            | Total Jitter <sup>(2)</sup> |         |      | 0.3   | I Ilm - |  |

|                         | Residual Jitter                            | Deterministic jitter        |         |      | 0.2   | Ulp-p   |  |

| J <sub>RM</sub>         | Random Jitter See note 2                   |                             |         | 1.5  |       | psrms   |  |

Notes

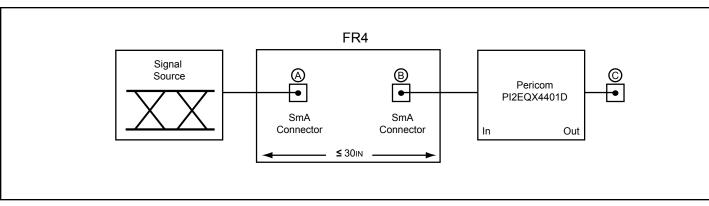

K28.7 pattern is applied differentially at point A as shown in Figure 1. 1

Total jitter does not include the signal source jitter. Total jitter (TJ) =  $(14.1 \times RJ + DJ)$  where RJ is random RMS jitter and DJ is maximum deterministic jitter. Sig-2 nal source is a K28.5  $\pm$  pattern (00 1111 1010 11 0000 0101) for the deterministic jitter test and K28.7 (0011111000) or equivalent for random jitter test. Residual jitter is that which remains after equalizing media-induced losses of the environment of Figure 1 or its equivalent. The deterministic jitter at point B must be from media-induced loss, and not from clock source modulation. JItter is measured at 0V at point C of Figure 1.

Figure 1. Test Condition Referenced in the Electrical Characteristic Table

#### AC/DC Electrical Characteristics ( $T_A = 0$ to 70°C)

| Symbol                          | Parameter                                  | Conditions                                                      | Min.                 | Тур.                 | Max.                 | Units |

|---------------------------------|--------------------------------------------|-----------------------------------------------------------------|----------------------|----------------------|----------------------|-------|

| CML Transm                      | nitter Output (100Ω differential)          |                                                                 |                      |                      |                      |       |

| V <sub>DIFFP</sub>              | Output Voltage Swing                       | Differential Swing<br>  V <sub>TX-D+</sub> - V <sub>TX-D-</sub> | 400                  |                      | 650                  | mVp-p |

| V <sub>TX-C</sub>               | Common-Mode Voltage                        | $ V_{TX-D+} + V_{TX-D-}  / 2$                                   |                      | V <sub>DD</sub> -0.3 |                      |       |

| t <sub>F</sub> , t <sub>R</sub> | Transition Time                            | 20% to 80% <sup>(3)</sup>                                       |                      |                      | 150                  | ps    |

| Z <sub>OUT</sub>                | Output resistance                          | Single ended                                                    | 40                   | 50                   | 60                   | Ω     |

| Z <sub>TX-DIFF-DC</sub>         | DC Differential TX Impedance               |                                                                 | 80                   | 100                  | 120                  | Ω     |

| C <sub>TX</sub>                 | AC Coupling Capacitor                      |                                                                 | 75                   |                      | 200                  | nF    |

| V <sub>TX</sub> -DIFFP-P        | Differential Peak-to-peak Ouput<br>Voltage | $V_{TX-DIFFP-P} = 2 *  V_{TX-D+} - V_{TX-D-} $                  | 0.8                  |                      | 1.3                  | V     |

| LVCMOS Co                       | ontrol Pins                                |                                                                 |                      |                      |                      |       |

| V <sub>IH</sub>                 | Input High Voltage                         |                                                                 | $0.65 \times V_{DD}$ |                      | V <sub>DD</sub>      | v     |

| V <sub>IL</sub>                 | Input Low Voltage                          |                                                                 |                      |                      | $0.35 \times V_{DD}$ | v     |

| I <sub>IH</sub>                 | Input High Current                         |                                                                 |                      |                      | 250                  |       |

| I <sub>IL</sub>                 | Input Low Current                          |                                                                 |                      |                      | 500                  | μA    |

Notes

3. Using K28.7 (0011111000) patern)

4. AC specifications are guaranteed by design and characterization

#### AC Switching Characteristics for Clock Buffer ( $V_{DD} = 1.8 \pm 0.1 V$ , $AV_{DD} = 1.8 \pm 0.1 V$ )

| Symbol                                | Parameters                                             |     | Max. | Units | Notes |

|---------------------------------------|--------------------------------------------------------|-----|------|-------|-------|

| T <sub>rise</sub> / T <sub>fall</sub> | Rise and Fall Time (measured between 0.175V to 0.525V) | 125 | 525  |       | 1     |

| $\Delta T_{rise} / \Delta T_{fall}$   | Rise and Fall Time Variation75                         |     | ps   | 1     |       |

| V <sub>HIGH</sub>                     | Voltage High including overshoot                       |     | 900  |       | 1     |

| V <sub>LOW</sub>                      | Voltage Low including undershoot                       |     |      | mV    | 1     |

| V <sub>CROSS</sub>                    | Absolute crossing point voltages                       |     | 550  | III V | 1     |

| $\Delta V_{CROSS}$                    | Total Variation of Vcross over all edges               |     | 250  |       | 1     |

| T <sub>DC</sub>                       | Duty Cycle (input duty cycle = 50%) 45 55 %            |     | %    | 2     |       |

Notes:

1. Measurement taken from Single Ended waveform.

Measurement taken from Differential waveform. 2.

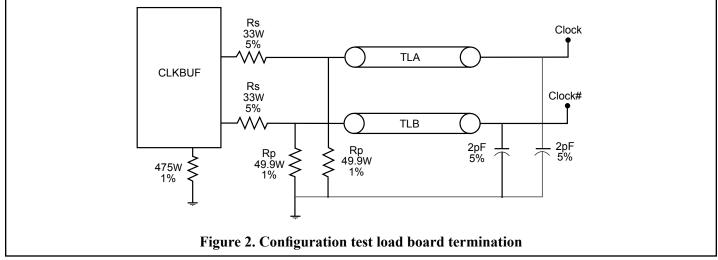

Test configuration is  $R_S = 33.2\Omega$ ,  $Rp = 49.9\Omega$ , and 2pF. 3.

#### **Configuration Test Load Board Termination**

Note: TLA and TLB are 3" transmission lines.

#### Part Marking

ZF Package

W: Die Rev YY: Year WW: Workweek 1st X: Assembly Code 2nd X: Fab Code

# A product Line of Diodes Incorporated

PI2EQX4401D

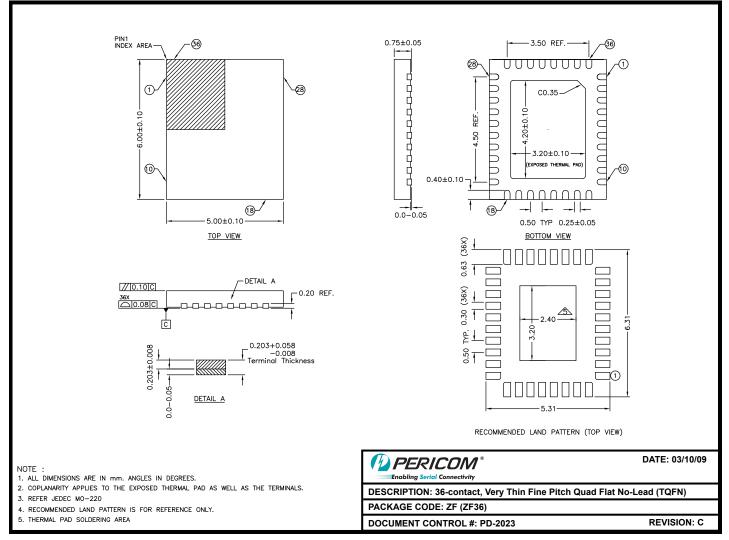

#### Packaging Mechanical: 36-TQFN (ZF)

09-0143

#### For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

## **Ordering Information**

| Ordering Number | Package Code | Package Description                                       |

|-----------------|--------------|-----------------------------------------------------------|

| PI2EQX4401DZFEX | ZF           | 36-contact, Very Thin Fine Pitch Quad Flat No-Lead (TQFN) |

Notes:

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

4. E = Pb-free and Green

5. X suffix = Tape/Reel

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION)

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated www.diodes.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Interface - Signal Buffers, Repeaters category:

Click to view products by Diodes Incorporated manufacturer:

Other Similar products are found below :

PI6ULS5V9509UEX PI3HDMI101-BZHEX PI3EQX12904AZHEX PI6ULS5V9306WEX PI3EQX1004EZTFEX PI6ULS5V9509WEX 48705-3001R2 48705-6501R2 DS280BR820ZBLT PCA9617ADPJ PI6ULS5V9515AWEX PI3HDMI101ZHE LTC4315CDE#PBF LTC4300-1CMS8#PBF DS110DF1610FB/NOPB LTC4301LCDD#PBF LTC4303IDD#PBF LTC4315IMS#TRPBF LTC4304IMS#PBF DS280DF810ABVT LTC4315IDE#PBF LTC4300-1IMS8#PBF LTC4313IMS8-3#TRPBF LTC4300-2IMS8#PBF LTC4300A-1CMS8#PBF PCA9515AD,118 LTC4307CMS8-1#TRPBF LTC4304CDD#PBF PI3EQX1002B1ZLEX LTC4301LIMS8 LTC4313IDD-3#TRPBF LTC4309IGN#PBF LTC4309CGN#PBF MAX9169EUE+ LTC4302IMS-2#PBF LTC4302CMS-1#PBF PI6ULS5V9306UEX LTC4300A-1CMS8#TRPBF P82B715TD,112 PCA9507DP,118 PCA9509DP,118 PCA9509GM,125 PCA9515ADP,118 PCA9517AD,118 PCA9517ADP,118 PCA9517DP,118 P82B715TD,118 PI6ULS5V9511AWEX PI1EQX512AXUAEX PI2EQX502TZHEX