# 5.0Gbps, 1-port, USB3.0 ReDriver™

### **Features**

- → USB 3.0 compatible

- → Full Compliancy to USB3.0 Super Speed Standard

- → Two 5.0Gbps differential signal pairs

- → Adjustable Receiver Equalization

- → 100Ω Differential CML I/O's

- → Pin Configured Output Emphasis Control

- → Input signal level detect and squelch for each channel

- → Automatic Receiver Detect with digital enable/disable

- → Low Power: ~330mW

- → Auto "Slumber" mode for adaptive power management

- → Stand-by Mode Power Down State

- → Industrial Temp Support (-40°C to 85°C)

- → Single Supply Voltage: 3.3V

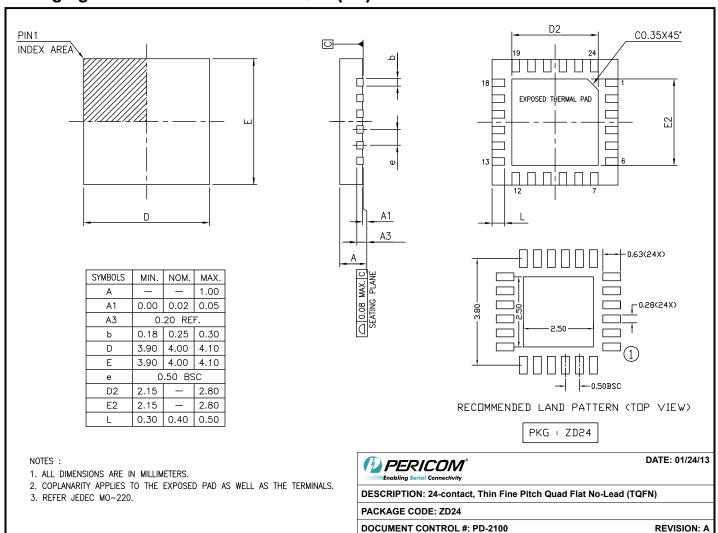

- → Packaging: 24-Pin TQFN (4x4mm)

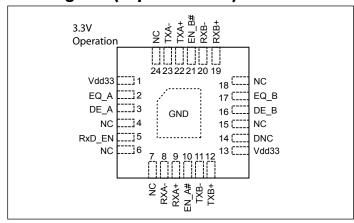

## Pin Diagram (Top Side View)

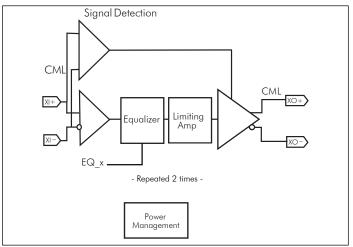

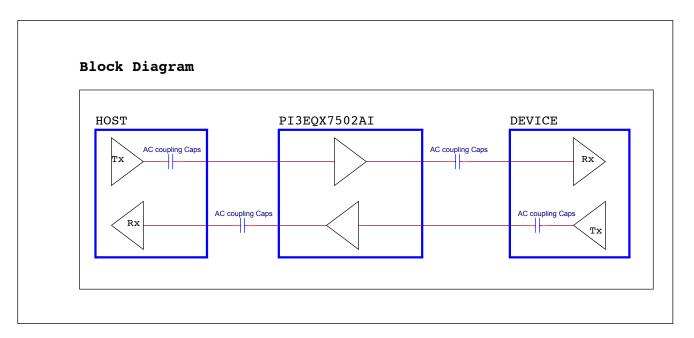

# **Block Diagram**

## **Description**

Pericom Semiconductor's PI3EQX7502AI is a low power, high performance 5.0 Gbps signal ReDriver™ designed specifically for the USB 3.0 protocol. The device provides programmable equalization, De-Emphasis, and input threshold controls to optimize performance over a variety of physical mediums by reducing Inter-Symbol Interference. PI3EQX7502AI supports two  $100\Omega$  Differential CML data I/O's between the Protocol ASIC to a switch fabric, over cable, or to extend the signals across other distant data pathways on the user's platform. The integrated equalization circuitry provides flexibility with signal integrity of the signal before the ReDriver. A low-level input signal detection and output squelch function is provided for each channel. Each channel operates fully independently. When the channels are enabled EN\_x# = 0 and operating, that channels' input signal level (on xI+/-) determines whether the output is active. If the input signal level of the channel falls below the active threshold level (Vth-) then the outputs are driven to the common mode voltage. In addition to signal conditioning, when  $EN_x# = 1$ , the device enters a low power standby mode. The PI3EQX7502AI also includes a fully programmable receiver detect function. When the RXD-EN pin is pulled high, automatic receiver detection will be active. The receiver detection loop will be active again if the corresponding channel's signal detector is idle for longer than 7.3mS. The channel will then move to Unplug Mode if load not detected, or it will return to Low Power Mode (Slumber Mode) due to inactivity.

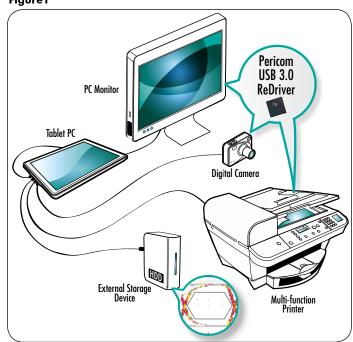

Figure 1

### **Pin Description**

| Pin #                               | Pin Name      | Type                                                                                                                        | Description                                                                                                                                                                                                                                                       |

|-------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>17                             | EQ_A<br>EQ_B  | Input                                                                                                                       | Set the equalization of two channels. These are Tri-level input pins. When set to "HIGH" the pin becomes Logic "1"; when set to "open", the pin becomes "open", when set to "low", the pin becomes logic "0". Please refer to Mode Adjustment on page 3.          |

| 10                                  | EN_A#         | Input                                                                                                                       | Channel A Enable. When the pin is driven "Low" Channel A is in normal operation. When the pin is driven "High", Channel A is in power down mode. With internal $200k\Omega$ pull-down resistor.                                                                   |

| 21                                  | EN_B#         | Input                                                                                                                       | Channel B Enable. When the pin is driven "Low" Channel B is in normal operation. When the pin is driven "High", Channel B is in power down mode. With internal $200k\Omega$ pull-down resistor.                                                                   |

| 9                                   | RXA+          |                                                                                                                             |                                                                                                                                                                                                                                                                   |

| 8                                   | RXA-          | Input                                                                                                                       | CML input channels. With Selectable input termination between $50\Omega$ to internal $V_{bias}$ and                                                                                                                                                               |

| 19                                  | RXB+          | Input                                                                                                                       | $60$ K $\Omega$ to GND. The input pins are pin polarity reversible.                                                                                                                                                                                               |

| 20                                  | RXB-          |                                                                                                                             |                                                                                                                                                                                                                                                                   |

| 22                                  | TXA+          |                                                                                                                             |                                                                                                                                                                                                                                                                   |

| 23                                  | TXA-          | Output Selectable output termination between $50\Omega$ to internal $V_{bi}$ . The output pins are pin polarity reversible. | Selectable output termination between $50\Omega$ to internal $V_{bias}$ and $2k\Omega$ to internal $V_{bias}$ .                                                                                                                                                   |

| 12                                  | TXB+          |                                                                                                                             | The output pins are pin polarity reversible.                                                                                                                                                                                                                      |

| 11                                  | TXB-          |                                                                                                                             |                                                                                                                                                                                                                                                                   |

| 4<br>6<br>7<br>14<br>15<br>18<br>24 | DNC           | DNC                                                                                                                         | No Connect                                                                                                                                                                                                                                                        |

| 1<br>13                             | VDD33         | Power                                                                                                                       | 3.3V Voltage Supply                                                                                                                                                                                                                                               |

| Center Pad                          | GND           | GND                                                                                                                         | Supply Ground.                                                                                                                                                                                                                                                    |

| 3<br>16                             | DE_A,<br>DE_B | Input                                                                                                                       | Set the de-emphasis of the output CML buffer. These are Tri-level input pins. When set to "high", the pin becomes logic "1"; when set to "open", the pin becomes "open"; when set to "low", the pin becomes logic "0". Please refer to Mode Adjustment on page 3. |

| 5                                   | RxD_EN        | Input                                                                                                                       | Set the state of receiver detection of two channels. "Low" means no receiver detection and "high" means the receiver detection is active. With internal $200k\Omega$ pull-up resistor.                                                                            |

# **Power Management**

Notebooks, netbooks, and other power sensitive consumer devices require judicious use of power in order to maximize battery life. In order to minimize the power consumption of our devices, Pericom has added an additional adaptive power management feature. When a signal detector is idle for longer than 1.3ms, the corresponding channel will move to low power mode ONLY. (It means both channels will move to low power mode individually).

In the slumber mode, the signal detector will still be monitoring the input channel. If a channel is in slumber mode and the input signal is detected, the corresponding channel will wake-up immediately. If a channel is in slumber mode and the signal detector is idle longer than 6ms, the receiver detection loop will be active again. If load is not detected, then the Channel will move to Device Unplug Mode and monitor the load continuously. If load is detected, it will return to Slumber Mode and receiver detection will be active again per 6ms.

The device can also be forced into low power standby mode through the use of the EN\_x# pins however this would require the use of GPIO pins to control.

13-0024 2 PS9065 03/14/13

# **Configuration Table**

| EN_x# | R <sub>X</sub> D_EN | Function                                                       | Input R             | Output R  |

|-------|---------------------|----------------------------------------------------------------|---------------------|-----------|

| 1     | X                   | Channel disable if both EN_A#, EN_B# are high, Chip Power Down | Hi-Z                | Hi-Z      |

| 0     | 1                   | Chip and channel enabled, receiver detect is active            | 50Ω / 60K to<br>GND | 50Ω / 2ΚΩ |

| 0     | 0                   | Chip and channel enabled, receiver detect is not active        | 50Ω                 | 50Ω       |

<sup>\*</sup> Refer to pin 19 description

# **Mode Adjustment**

# **Equalization Setting:**

EQ\_A/B are the selection pins for the equalization selection for each direction.

| Equalizer setting |               |  |  |  |

|-------------------|---------------|--|--|--|

| EQ_A/B            | @ 2.5GHz      |  |  |  |

| 0                 | 3 dB          |  |  |  |

| open              | 6dB (Default) |  |  |  |

| 1                 | 9dB           |  |  |  |

# **De-emphasis Setting:**

$\mathrm{DE}\_\mathrm{A/B}$  are the selection pins for the de-emphasis selection for each direction.

| Output de-emphasis setting |                   |  |  |  |

|----------------------------|-------------------|--|--|--|

| DE_A/B                     | De-emphasis       |  |  |  |

| 0                          | 0 dB              |  |  |  |

| open                       | -3.5 dB (default) |  |  |  |

| 1                          | -6 dB             |  |  |  |

# **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                | 65°C to +150°C               |

|------------------------------------|------------------------------|

| Supply Voltage to Ground Potential | 0.5V to +4.6V                |

| DC SIG Voltage                     | $-0.5$ V to $V_{DD} + 0.5$ V |

| Current Output                     | 25mA to +25mA                |

| Power Dissipation Continuous       | 1.0W                         |

| Operating Temperature              | 40°C to +85°C                |

| ESD, Human Body Model              | 7kv to +7kV                  |

| ESD, Machine Model                 | 200V to +200V                |

#### Note:

Stresses greater than those listed under MAXI-MUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### RECOMMENDED OPERATING CONDITIONS

| Symbol                        | Parameter                                | Conditions                                 | Min.     | Тур.     | Max.     | Units |  |

|-------------------------------|------------------------------------------|--------------------------------------------|----------|----------|----------|-------|--|

| DEVICE PARAMET                | DEVICE PARAMETERS                        |                                            |          |          |          |       |  |

| maximum date rate             |                                          |                                            |          |          | 5        | Gbps  |  |

| t <sub>ENB</sub>              | Device enable time                       | ENA/B# H->L<br>with Rx termination present |          |          | 50       | ms    |  |

| t <sub>DIS</sub>              | Device disable time                      | ENA/B# L->H                                |          | 7        |          | ns    |  |

| CONTROL LOGIC                 |                                          |                                            |          |          |          |       |  |

| I <sub>IH</sub>               | Input High Current                       |                                            |          |          | 50       |       |  |

| $I_{IL}$                      | Input LOW Current                        | -50                                        |          |          |          | uA    |  |

| <b>Bi-level Cotrol Pins (</b> | Pin 5, 10, 21)                           |                                            |          |          | •        |       |  |

| V <sub>IH</sub>               | Input High Voltage                       |                                            | 0.65Vdd  |          |          | V     |  |

| V <sub>IL</sub>               | Input Low Voltage                        |                                            |          |          | 0.35Vdd  | V     |  |

| Tri-level Control Pin         | Tri-level Control Pins (Pins: 2,3,16,17) |                                            |          |          |          |       |  |

| V <sub>IH</sub>               | Input High Voltage                       |                                            | 0.8Vdd33 |          |          |       |  |

| V <sub>IL</sub>               | Input Low Voltage                        |                                            |          |          | 0.2Vdd33 | V     |  |

| V <sub>I mid</sub>            | Input Mid Level                          |                                            | 0.4Vdd33 | 0.5Vdd33 | 0.6Vdd33 |       |  |

### **AC/DC Electrical Characteristics**

| Symbol                        | Parameter                         | Conditions                                  | Min. | Тур. | Max. | Units |

|-------------------------------|-----------------------------------|---------------------------------------------|------|------|------|-------|

| 3.3V Power Suppl              | 3.3V Power Supply Characteristics |                                             |      |      |      |       |

| $V_{\mathrm{DD33}}$           | Power Supply Voltage              |                                             | 3.0  |      | 3.6  | V     |

| P <sub>STANDBY33</sub>        | Supply Power Standby              | $EN_{[A:B]}# = 1$                           |      | 0.15 | 1.8  |       |

| P <sub>SLUMBER33</sub>        | Supply Power Slumber              | EN_ [A:B]# = 0, No Input Signal             |      | 58   | 65   |       |

| P <sub>DEVICE_UNPLUG</sub>    | Supply Power Device Unplug        | $EN_[A:B]$ # = 0, Output unterminated       |      | 7.3  |      | mW    |

| P <sub>ACTIVE33</sub>         | Supply Power Active               | $EN_{A:B} = 0, V_{RX-DIFF-P} \ge V_{TH-SD}$ |      | 328  | 450  |       |

| I <sub>DD-STANDBY33</sub>     | Supply Current Standby            | EN_ [A:B]# = 1                              |      |      | 0.5  | mA    |

| I <sub>DD-SLUMBER33</sub>     | Supply Current Slumber            | EN_ [A:B]# = 0, No Input Signal             |      |      | 18   | mA    |

| I <sub>DD-DEVICE_UNPLUG</sub> | Supply Current Device Unplug      | EN_[A:B]# = 0, Output unterminated          |      | 2.2  |      | A     |

| I <sub>DD-ACTIVE33</sub>      | Supply Current Active             | $EN_x# = 0, V_{RX-DIFFP-P} \ge V_{TH-SD}$   |      |      | 125  | mA    |

# AC/DC Electrical Characteristics (Continued..)

| Symbol                           | Parameter                                     | Conditions                                                                                             | Min. | Typ. | Max. | Units |

|----------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Receiver AC/I                    | OC .                                          |                                                                                                        |      |      |      |       |

| V <sub>RX-DIFFP-P</sub>          | Differential Peak-to-Peak Input Voltage       | AC coupled differential RX peak to peak signal                                                         | 175  |      | 1200 | mVppd |

| V <sub>RX-C</sub>                | Common Mode Voltage                           |                                                                                                        |      | 1    |      | V     |

| V <sub>cm_ac</sub>               | RX AC Common Mode Voltage                     | Measured at Rx pins with termination enabled                                                           |      |      | 150  | mVP   |

| Z <sub>DC_RX</sub>               | DC commmon mode inpedance                     |                                                                                                        | 18   |      | 30   |       |

| Z <sub>diff_RX</sub>             | DC differential input impendance              |                                                                                                        | 72   | 100  | 120  | Ω     |

| Z <sub>RX_HIGH_</sub><br>IMP+    | DC Input high impedance                       | Device in unplug, standby modes RX termination not powered measured with respect to GND over 500mV max |      | 67   |      | kΩ    |

| DI                               | D'. (: 1 , 1                                  | 50 MHz-1.25GHz                                                                                         |      | 23   |      | 11    |

| RL <sub>RX-DIFF</sub>            | Differential return loss                      | 1.25 GH-2.5 GHz                                                                                        |      | 13   |      | db    |

| RL <sub>RX-CM</sub>              | Common mode return loss                       | 50 MHz-2.5 GHz                                                                                         |      | 8    |      | db    |

| TH-SD                            | Signal detect Threshold                       | EN_x# = 0                                                                                              | 65   |      | 175  | mVppd |

| Transmitter C                    | Output AC/DC (100Ω differential) <sup>1</sup> |                                                                                                        |      |      |      |       |

| V <sub>TX-DIFFP-P</sub>          | Differential Peak-to-peak Output<br>Voltage   | $V_{TX-DIFFP-P} = 2 *   V_{TX-D+} - V_{TX-D-}  $                                                       | 400  |      | 1200 | mVnnd |

| V <sub>TX-LFPS</sub>             | LFPS Differential Peak-to-peak Output Voltage |                                                                                                        | 800  |      |      | mVppd |

| V <sub>TX-C</sub>                | Common-Mode Voltage                           | $ V_{TX-D+} + V_{TX-D-} /2$                                                                            | 0.5  |      | 1.2  | V     |

|                                  |                                               | DEA/B = 0                                                                                              |      | 0    |      |       |

| DE                               |                                               | DEA/B = NC                                                                                             | -3.0 | -3.5 | -4.0 | dB    |

|                                  |                                               | DEA/B = 1                                                                                              |      | -6.0 |      |       |

| $Z_{diff\_TX}$                   | DC differential impedance                     |                                                                                                        | 72   | 90   | 120  |       |

| Z <sub>CM_TX</sub>               | DC common mode impedance                      | Measured w.r.t to AC ground over 0-500mV                                                               | 18   | 23   | 30   | Ω     |

| DI                               | Diff. it is a                                 | f= 50MHz-1.25 GHz                                                                                      |      | 12   |      | 10    |

| $RL_{diff\_TX}$                  | Differential return loss                      | f= 1.25 GHz-2.5 GHz                                                                                    |      | 8    |      | dB    |

| RL <sub>CM_TX</sub>              | Common mode return loss                       | f= 50 MHz-2.5GHz                                                                                       |      | 10   |      | dB    |

| I <sub>TX_SC</sub>               | TX short circuit current                      | TX± shorted to GND                                                                                     |      | 26   |      | mA    |

| V <sub>TX_CM_AC_</sub><br>Active | TX AC common mode voltage active              |                                                                                                        |      | 30   | 100  | mVpp  |

**AC/DC Electrical Characteristics (Continued..)**

| Symbol                               | Parameter                                             | Conditions                                                     | Min. | Тур. | Max. | Units             |

|--------------------------------------|-------------------------------------------------------|----------------------------------------------------------------|------|------|------|-------------------|

| Transmitter C                        | Output AC/DC (100 $\Omega$ differential) <sup>1</sup> |                                                                |      |      |      |                   |

| V <sub>detect</sub>                  | Voltage change to allow receiver                      | Positive voltage to sense receiver termination                 |      |      | 600  | mV                |

| $t_{R,t_F}$                          | Output rise/fall time                                 | 20%-80% of differental voltage measured 1" from the output pin |      | 90   |      | ps                |

| $T_{ m diff\_LH,}$ $T_{ m diff\_HL}$ | Differential propagation delay                        | Propagation delay between 50% level at input and output        |      | 305  | 370  | ps                |

| Equalization                         |                                                       |                                                                |      |      |      |                   |

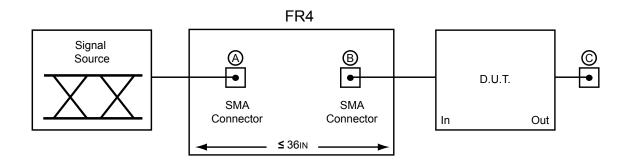

| $T_{TX-EYE}^{(1)(2)}$                | Total jitter(Tj)                                      |                                                                |      | 0.2  | 0.5  | (3)               |

| DJ <sub>TX</sub> <sup>(2)</sup>      | Deterministic jitter(Dj)                              | with 36 inch of inputFR4 trace                                 |      | 0.1  | 0.3  | UI <sup>(3)</sup> |

| RJ <sub>TX</sub> <sup>(2)(4)</sup>   | Random jitter(Rj)                                     |                                                                |      | 0.09 | 0.2  | Pp                |

### Note:

<sup>1.</sup>Includes RJ at 10<sup>-12</sup> BER

<sup>2.</sup>Determininstic jitter measured with PRBS7 pattern, Random jitter measured with 1010 patter VID=1000mVpp, 5Gbps,

<sup>3.</sup>UI = 200ps

<sup>4.</sup>Rj calculated as 14.069 times the RMS random jitter for 10<sup>-12</sup> BER

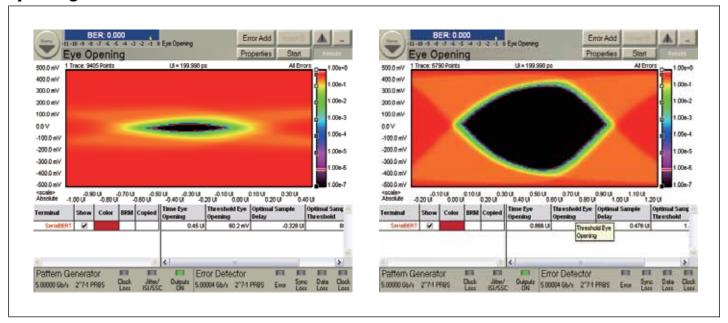

# **Eye Diagram**

Left: Input Eye Diagram, Left: Output Eye Diagram, Trace length: 36-inch, 5.0 Gb/s

**Test Condition Referenced in the Electrical Characteristic Table**

PI3EQX7502AI Application Schematics

# Packaging Mechanical: 24-contact TQFN (ZD)

### **Ordering Information**

| Ordering Number | Package Code | Package Description                   |

|-----------------|--------------|---------------------------------------|

| PI3EQX7502AIZDE | ZD           | Pb-Free and Green 24-pin TQFN (4x4mm) |

### Notes:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- E = Pb-free and Green

- X suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Interface - Signal Buffers, Repeaters category:

Click to view products by Diodes Incorporated manufacturer:

Other Similar products are found below:

PI6ULS5V9509UEX PI3HDMI101-BZHEX PI3EQX12904AZHEX PI6ULS5V9306WEX PI3EQX1004EZTFEX PI6ULS5V9509WEX 48705-3001R2 48705-6501R2 DS280BR820ZBLT PCA9617ADPJ PI6ULS5V9515AWEX PI3HDMI101ZHE LTC4315CDE#PBF LTC4300-1CMS8#PBF DS110DF1610FB/NOPB LTC4301LCDD#PBF LTC4303IDD#PBF LTC4315IMS#TRPBF LTC4304IMS#PBF DS280DF810ABVT LTC4315IDE#PBF LTC4300-1IMS8#PBF LTC4313IMS8-3#TRPBF LTC4300-2IMS8#PBF LTC4300A-1CMS8#PBF PCA9515AD,118 LTC4307CMS8-1#TRPBF LTC4304CDD#PBF PI3EQX1002B1ZLEX LTC4301LIMS8 LTC4313IDD-3#TRPBF LTC4309IGN#PBF LTC4309CGN#PBF MAX9169EUE+ LTC4302IMS-2#PBF LTC4302CMS-1#PBF PI6ULS5V9306UEX LTC4300A-1CMS8#TRPBF P82B715TD,112 PCA9507DP,118 PCA9509DP,118 PCA9509GM,125 PCA9515ADP,118 PCA9517AD,118 PCA9517ADP,118 PCA9517DP,118 P82B715TD,118 PI6ULS5V9511AWEX PI1EQX512AXUAEX PI2EQX502TZHEX