## PI3HDMI301

## 3:1 Active Switch for HDMI<sup>TM</sup> Signals with Optimized Equalization for Enhanced Signal Integrity

## Features

- Supply voltage,  $V_{DD} = 3.3V \pm 5\%$

- Each of the three input ports can support HDMI<sup>™</sup> or DVI signals

- · Supports both AC-coupled and DC-coupled inputs

- Supports DeepColor<sup>™</sup>

- High Performance, up to 2.5 Gbps per channel

- Switching support for 3 side band signals (SCL, SDA and HPD)

- 5V Tolerance on all side band signals

- SCL, SDA, and HPD pins are the only pins that can support HOT INSERTION

- Integrated 50-ohm (±10%) termination resistors at each high speed signal input

- TMDS input termination control on all high speed inputs

- HDCP reset circuitry for quick communication when switching from one port to another

- Configurable output swing control

- Configurable Pre-Emphasis levels

- Configurable De-Emphasis

- Optimized Equalization

- Single default setting will support all cable lengths • 8kV Contact ESD protection on all input data/clock cha

- 8kV Contact ESD protection on all input data/clock channels per IEC61000-4-2

- Propagation delay  $\leq 2ns$

- · High Impedance Outputs when disabled

- Packaging (Pb-free & Green):

- 80-pin LQFP (FF80)

- 64-pin TQFN (ZL64)

#### Description

Pericon Semiconductor's PI3HDMI301 3:1 active switch circuit is targeted for high-resolution video networks that are based on DVI/HDMI<sup>TM</sup> standards and TMDS signal processing. The PI3HDMI301 is an active 3 TMDS to 1 TMDS receiver switch with Hi-Z outputs. The device receives differential signals from selected video components and drives the video display unit. It provides controllable output swings, as well as provides a unique advanced pre-emphasis technique to increase rise and fall times which are reduced during transmission across long distances.

Each complete HDMI/DVI channel also has slower speed, side band signals, that are required to be switched. Pericom's solution provides a complete solution by integrating the side band switch together with the high speed switch in a single solution. Using Equalization at the input of each of the high speed channels, Pericom can successfully eliminate deterministic jitter caused by long cables from the source to the sink. The elimination of the deterministic jitter allows the user to use much longer cables (up to 25 meters).

The maximum DVI/HDMI Bandwidth of 2.5 Gbps provides 36-bit Deep Color<sup>™</sup> support, which is offered by HDMI<sup>™</sup> revision 1.3. Due to its active uni-directional feature, this switch is designed for usage only for the video receiver's side. For consumer video networks, the device sits at the receiver's side to switch between multiple video components, such as PC, DVD, STB, D-VHS, etc. The PI3HDMI301 also provides enhanced robust ESD/EOS protection of 8kV, which is required by many consumer video networks today.

The Optimized Equalization provides the user a single optimal setting that can provide passing results for HDMI jitter tests for all cable lengths: 1meter to 20meters with DeepColor support up to 36bits.

Pericom also offers the ability to fine tune the equalization settings in situations where cable length is known. For example, if 25meter cable length is required, Pericom's solution can be adjusted to 16dB EQ to accept 25meter cable length.

#### PI3HDMI301 3:1 Active Switch for HDMI<sup>™</sup> Signals with Optimized Equalization for Enhanced Signal Integrity

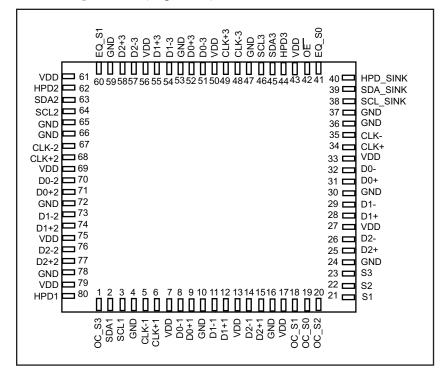

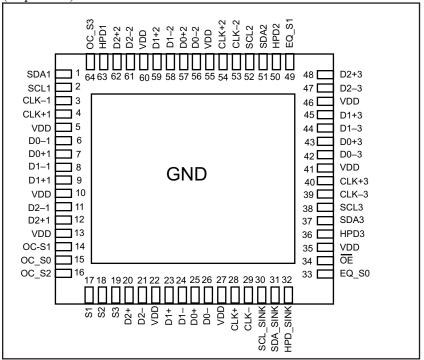

Pin Configuration (Top View)

## (Top View)

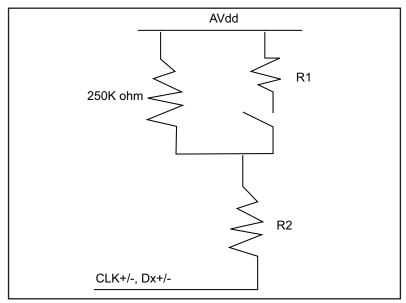

## **Receiver Block**<sup>1</sup>

Each input has integrated equalization that can eliminate deterministic jitter caused by 25meter 24AWG cables. All activity can be configured using pin strapping. The Rx block is designed to receive all relevant signals directly from the HDMI<sup>™</sup> connector without any additional circuitry, 3 High speed TMDS data, 1 pixel clock, 1 HPD signals, and DDC signals. TMDS Channels have following termination scheme for Rx Sense support.

## **Pin Description**

| 80 LQFP Pin #                                               | 64 TQFN Pin #                        | Pin Name                                                       | I/O | Description                                                                                                                                                                                        |

|-------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9, 12, 15, 6                                                | 7, 9,12, 4                           | D <sub>0</sub> +1, D <sub>1</sub> +1, D <sub>2</sub> +1, CLK+1 | Ι   | Port 1 TMDS Positive inputs                                                                                                                                                                        |

| 71, 74, 77, 68                                              | 57, 59, 62, 54                       | D <sub>0</sub> +2, D <sub>1</sub> +2, D <sub>2</sub> +2, CLK+2 | Ι   | Port 2 TMDS Positive inputs                                                                                                                                                                        |

| 52, 55, 58, 49                                              | 43, 45, 48, 40                       | D <sub>0</sub> +3, D <sub>1</sub> +3, D <sub>2</sub> +3, CLK+3 | Ι   | Port 3 TMDS Positive inputs                                                                                                                                                                        |

| 8, 11, 14, 5                                                | 6, 8, 11, 3                          | D <sub>0</sub> -1, D <sub>1</sub> -1, D <sub>2</sub> -1, CLK-1 | Ι   | Port 1 TMDS Negative inputs                                                                                                                                                                        |

| 70, 73, 76, 67                                              | 56, 58, 61, 53                       | D <sub>0</sub> -2, D <sub>1</sub> -2, D <sub>2</sub> -2, CLK-2 | Ι   | Port 2 TMDS Negative inputs                                                                                                                                                                        |

| 51, 54, 57, 48                                              | 42, 44, 47, 39                       | D <sub>0</sub> -3, D <sub>1</sub> -3, D <sub>2</sub> -3, CLK-3 | Ι   | Port 3 TMDS Negative inputs                                                                                                                                                                        |

| 4, 10, 16, 24, 30,<br>36, 37, 47, 53, 59,<br>65, 66, 72, 78 |                                      | GND                                                            |     | Ground                                                                                                                                                                                             |

| 80                                                          | 63                                   | HPD1                                                           | 0   | Port 1 HPD output                                                                                                                                                                                  |

| 62                                                          | 50                                   | HPD2                                                           | 0   | Port 2 HPD output                                                                                                                                                                                  |

| 44                                                          | 36                                   | HPD3                                                           | 0   | Port 3 HPD output                                                                                                                                                                                  |

| 40                                                          | 32                                   | HPD_Sink                                                       | Ι   | Sink side hot plug detector input. High: 5-V<br>power signal asserted from source to sink<br>and EDID is ready.<br>Low: No 5-V power signal asserted from<br>source to sink, or EDID is not ready. |

| 42                                                          | 34                                   | ŌĒ                                                             | Ι   | Output Enable, Active LOW                                                                                                                                                                          |

| 3                                                           | 2                                    | SCL1                                                           | I/O | Port 1 DDC Clock                                                                                                                                                                                   |

| 64                                                          | 52                                   | SCL2                                                           | I/O | Port 2 DDC Clock                                                                                                                                                                                   |

| 46                                                          | 38                                   | SCL3                                                           | I/O | Port 3 DDC Clock                                                                                                                                                                                   |

| 38                                                          | 31                                   | SCL_Sink                                                       | I/O | Sink Side DDC Clock                                                                                                                                                                                |

| 2                                                           | 1                                    | SDA1                                                           | I/O | Port 1 DDC Data                                                                                                                                                                                    |

| 63                                                          | 51                                   | SDA2                                                           | I/O | Port 2 DDC Data                                                                                                                                                                                    |

| 45                                                          | 37                                   | SDA3                                                           | I/O | Port 3 DDC Data                                                                                                                                                                                    |

| 39                                                          | 31                                   | SDA_Sink                                                       | I/O | Sink Side DDC Data                                                                                                                                                                                 |

| 21, 22, 23                                                  | 17, 18, 19                           | S1, S2, S3                                                     | Ι   | Source Input Control                                                                                                                                                                               |

| 7, 13, 17, 27, 33,<br>43, 50, 56, 61, 69,<br>75, 79         | 5, 10, 22, 27, 35,<br>41, 46, 55, 60 | V <sub>DD</sub>                                                |     | 3.3V Power Supply                                                                                                                                                                                  |

| 31, 28, 25, 34                                              | 25, 23, 20, 28                       | D <sub>0</sub> +, D <sub>1</sub> +, D <sub>2</sub> +, CLK+     | 0   | TMDS positive outputs                                                                                                                                                                              |

| 32, 29, 26, 35                                              | 26, 24, 21, 29                       | D <sub>0</sub> -, D <sub>1</sub> -, D <sub>2</sub> -, CLK-     | 0   | TMDS negative outputs                                                                                                                                                                              |

| 41, 60                                                      | 33, 49                               | EQ_S0, EQ_S1                                                   | Ι   | Equalizer controls, both controls have internal pull-ups                                                                                                                                           |

| 19, 18, 20, 1                                               | 15, 14, 16, 64                       | OC_S0, OC_S1,<br>OC_S2, OC_S3                                  | Ι   | Output buffer controls, all control bits have internal pull-ups                                                                                                                                    |

#### PI3HDMI301 3:1 Active Switch for HDMI<sup>™</sup> Signals with Optimized Equalization for Enhanced Signal Integrity

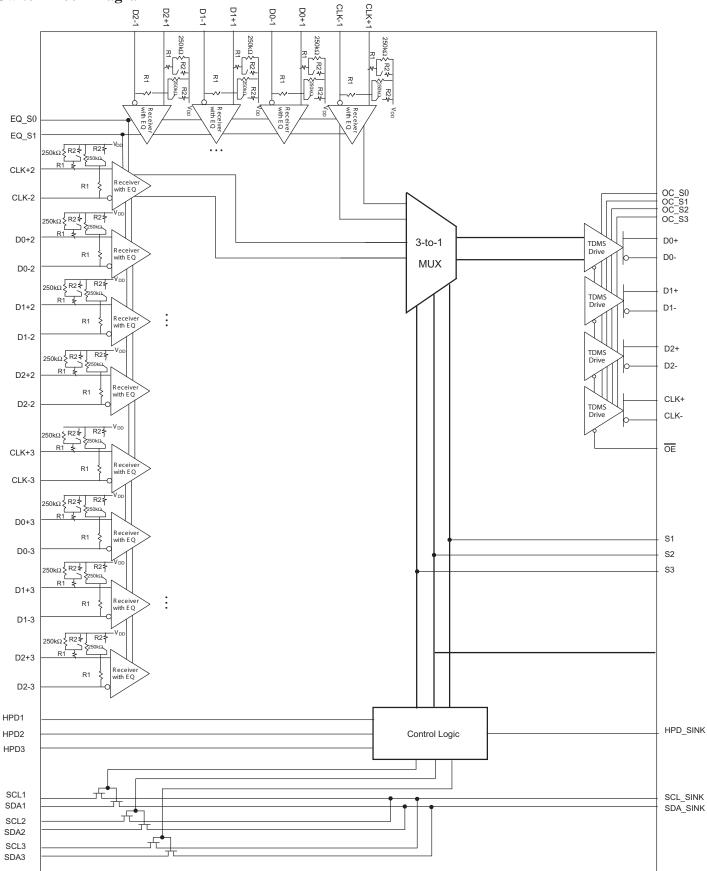

## **Switch Block Diagram**

5

## **Truth Table**

|    | Contro     | l Pins |    | I/O Selected |          | Ho             | t Plug Detect St | tatus            |          |

|----|------------|--------|----|--------------|----------|----------------|------------------|------------------|----------|

| ŌĒ | <b>S</b> 1 | S2     | S3 | TMDS outputs |          | _Sink<br>_Sink | HPD1             | HPD2             | HPD3     |

| L  | Н          | X      | X  | Port1        | SCL1     | SDA1           | HPD_Sink         | L                | L        |

| L  | L          | Н      | х  | Port2        | SCL2     | SDA2           | L                | HPD_Sink         | L        |

| L  | L          | L      | Н  | Port3        | SCL3     | SDA3           | L                | L                | HPD_Sink |

| L  | L          | L      | L  | None (Hi-Z)  | None     | (Hi-Z)         | L                | L                | L        |

| Н  | Х          | Х      | Х  | None (Hi-Z)  | Follow S | S1, S2, S3     | ]                | Follow S1, S2, S | 33       |

## **OC Setting Value Logic Table**

|                      | 0 Input Co           | ontrol Pins          |                      | Setting Value |                                  |  |

|----------------------|----------------------|----------------------|----------------------|---------------|----------------------------------|--|

| OC_S3 <sup>(1)</sup> | OC_S2 <sup>(1)</sup> | OC_S1 <sup>(1)</sup> | OC_S0 <sup>(1)</sup> | Vswing (mV)   | Pre-emphasis/De-emphasis<br>(dB) |  |

| 0                    | 0                    | 0                    | 0                    | 333           | -9.5                             |  |

| 0                    | 0                    | 0                    | 1                    | 500           | -6                               |  |

| 0                    | 0                    | 1                    | 0                    | 666           | -3.5                             |  |

| 0                    | 0                    | 1                    | 1                    | 1000          | 0                                |  |

| 0                    | 1                    | 0                    | 0                    | 160           | -9                               |  |

| 0                    | 1                    | 0                    | 1                    | 270           | -6                               |  |

| 0                    | 1                    | 1                    | 0                    | 340           | -3.5                             |  |

| 0                    | 1                    | 1                    | 1                    | 500           | 0                                |  |

| 1                    | 0                    | 0                    | 0                    | 500           | 6                                |  |

| 1                    | 0                    | 0                    | 1                    | 500           | 3.5                              |  |

| 1                    | 0                    | 1                    | 0                    | 500           | 1.5                              |  |

| 1                    | 0                    | 1                    | 1                    | 500           | 0                                |  |

| 1                    | 1                    | 0                    | 0                    | 600           | 0                                |  |

| 1                    | 1                    | 0                    | 1                    | 1000          | 0                                |  |

| 1                    | 1                    | 1                    | 0                    | 750           | 0                                |  |

| 1                    | 1                    | 1                    | 1                    | 500           | 0                                |  |

## EQ Setting Value Logic Table for high speed data bits (TMDS CLK input is left at 3dB default always)

| EQ_S1(1) | EQ_S0 <sup>(1)</sup> | Setting Value                                                                                                                      |  |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| 0        | 0                    | 15dB on all high speed data inputs                                                                                                 |  |

| 0        | 1                    | 3dB on all high speed data inputs                                                                                                  |  |

| 1        | 0                    | 8dB on all high speed data inputs                                                                                                  |  |

| 1        | 1                    | Optimized Equalization on all high speed data inputs (Default setting which can support all cable lengths from 1meter to 20meters) |  |

Notes:

1) Integrated internal pull-ups

#### **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature<br>Supply Voltage to Ground Potential<br>DC Input Voltage<br>DC Output Current | -0.5V to +4.0V<br>-0.5V to V <sub>DD</sub> |

|----------------------------------------------------------------------------------------------------|--------------------------------------------|

| DC Output Current                                                                                  |                                            |

| Power Dissipation                                                                                  |                                            |

Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Recommended Operating Conditions**

| Symbol              | Parameter                                        | Min.                  | Typ. | Max.            | Units |  |

|---------------------|--------------------------------------------------|-----------------------|------|-----------------|-------|--|

| V <sub>DD</sub>     | Supply Voltage                                   | 3.135                 | 3.3  | 3.465           | V     |  |

| T <sub>A</sub>      | Operating free-air temperature                   | 0                     |      | 70              | °C    |  |

| TMDS Dif            | ferential PinS                                   |                       |      | -               |       |  |

| V <sub>ID</sub>     | Receiver peak-to-peak differential input voltage | 150                   |      | 1560            | mVp-p |  |

| V <sub>IC</sub>     | Input common mode voltage                        | 2                     |      | $V_{DD} + 0.01$ | V     |  |

| V <sub>DD</sub>     | TMDS output termination voltage                  | 3.135                 | 3.3  | 3.465           | V     |  |

| R <sub>T</sub>      | Termination resistance                           | 45                    | 50   | 55              | ohm   |  |

|                     | Signaling rate                                   | 0.25                  |      | 2.5             | Gbps  |  |

| Control Pi          | $ns (OC_Sx, EQ_Sx, Sx, \overline{OE})$           |                       |      | -               |       |  |

| V <sub>IH</sub>     | LVTTL High-level input voltage                   | 2                     |      | V <sub>DD</sub> | N     |  |

| V <sub>IL</sub>     | LVTTL Low-level input voltage                    | vel input voltage GND |      | 0.8             | V     |  |

| <b>DDC Pins</b>     | (SCLx, SCL_SINK, SDAx, SDA_SINK)                 |                       | •    |                 | •     |  |

| V <sub>I(DDC)</sub> | Input voltage                                    | GND                   |      | 5.5             | V     |  |

| Status Pins         | (HPD_SINK)                                       |                       |      |                 |       |  |

| V <sub>IH</sub>     | LVTTL High-level input voltage                   | 2                     |      | 5.3             | N/    |  |

| V <sub>IL</sub>     | LVTTL Low-level input voltage                    | GND                   |      | 0.8             | V     |  |

## **TMDS Compliance Test Results**

| Item                                                                                                                      | <b>HDMI</b> <sup>™</sup> <b>1.3 Spec</b>                                   | Pericom Product Spec                                                                                                                      |  |

|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operating Conditions                                                                                                      | l                                                                          |                                                                                                                                           |  |

| Termination Supply Voltage, V <sub>DD</sub>                                                                               | $3.3V \le 5\%$                                                             | 3.30 ± 5%                                                                                                                                 |  |

| Terminal Resistance                                                                                                       | 50-ohm ± 10%                                                               | 45 to 55-ohm                                                                                                                              |  |

| Source DC Characteristics at TP1                                                                                          | l                                                                          |                                                                                                                                           |  |

| Single-ended high level output voltage, VH                                                                                | $V_{DD} \pm 10 mV$                                                         | V <sub>DD</sub> ±10mV                                                                                                                     |  |

| Single-ended low level output voltage, VL $(V_{DD} - 600mV) \le VL \le (V_{DD} - 400mV)$ $(V_{DD} - 600mV) \le 400mV)$    |                                                                            |                                                                                                                                           |  |

| Single-ended output swing voltage, Vswing                                                                                 | $400 \text{mV} \le \text{Vswing} \le 600 \text{mV}$                        | $400 \text{mV} \le \text{Vswing} \le 600 \text{mV}$                                                                                       |  |

| Single-ended standby (off) output voltage, Voff                                                                           | $V_{DD} \pm 10 mV$                                                         | $V_{DD} \pm 10 mV$                                                                                                                        |  |

| Transmitter AC Characteristics at TP1                                                                                     |                                                                            |                                                                                                                                           |  |

| Risetime/Falltime (20%-80%) $75ps \le Risetime/Falltime \le 0.4$ Tbit<br>$(75ps \le tr/tf \le 242ps)$ @ 1.65 Gbps $240ps$ |                                                                            | 240ps                                                                                                                                     |  |

| Intra-Pair Skew at Transmitter Connector, max                                                                             | 0.15 Tbit<br>(90.9ps @ 1.65 Gbps)                                          | 60ps max                                                                                                                                  |  |

| Inter-Pair Skew at Transmitter Connector, max                                                                             | 0.2 Tpixel<br>(1.2ns @ 1.65 Gbps)                                          | 100ps max                                                                                                                                 |  |

| Clock Jitter, max                                                                                                         | 0.25 Tbit<br>(151.5ps @ 1.65 Gbps)                                         | 82ps max                                                                                                                                  |  |

| Sink Operating DC Characteristics at TP2                                                                                  | 1                                                                          |                                                                                                                                           |  |

| Input Differential Voltage Level, Vdiff                                                                                   | $150 \le V diff \le 1200 mV$                                               | $150mV \le V_{DIFF} \le 1200mV$                                                                                                           |  |

| Input Common Mode Voltage Level, V <sub>ICM</sub>                                                                         | $(V_{DD} - 300mV) \le Vicm \le (V_{DD}-37.5mV)$<br>Or<br>$V_{DD} \pm 10\%$ | $\begin{array}{l} (\ V_{DD} \mbox{-} \ 300mV) \leq Vicm \leq \\ (\ V_{DD} \mbox{-} \ 37.5mV) \\ Or \\ V_{DD} \mbox{=} \ 10\% \end{array}$ |  |

| Sink DC Characteristics When Source Disable                                                                               | ed or Disconnected at TP2                                                  |                                                                                                                                           |  |

| Differential Voltage Level                                                                                                | $V_{DD} \pm 10 mV$                                                         | $V_{DD} \pm 10 mV$                                                                                                                        |  |

| Symbol               | Parameter                                                                     | Test Conditions                                                                                                                  | Min.                    | <b>Typ.</b> <sup>(1)</sup> | Max.                     | Units              |

|----------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|--------------------------|--------------------|

| I <sub>CC</sub>      | Supply Current                                                                | $V_{IH} = V_{DD}, V_{IL} = V_{DD} - 0.4V,$<br>$R_T = 50$ -ohm, $V_{DD} = 3.3V$<br>Data Input = 1.65 Gbps HDMI <sup>TM</sup> data |                         | 200                        |                          | mA                 |

| P <sub>D</sub>       | Power Dissipation                                                             | pattern<br>CLK Input = 165 MHz clock                                                                                             |                         | 660                        |                          | mW                 |

| I <sub>CCQ</sub>     | Standby Current                                                               | $\overline{OE}$ = HIGH, S1 = S2 = S3 = LOW                                                                                       |                         | 8                          |                          | mA                 |

| TMDS Di              | fferential Pins                                                               | -                                                                                                                                |                         |                            |                          |                    |

| V <sub>OH</sub>      | Single-ended high-level output voltage                                        |                                                                                                                                  | V <sub>DD</sub> -<br>10 |                            | V <sub>DD</sub> + 10     |                    |

| V <sub>OL</sub>      | Single-ended low-level output voltage                                         |                                                                                                                                  | V <sub>DD</sub> - 600   |                            | V <sub>DD</sub> -<br>400 | mV                 |

| V <sub>swing</sub>   | Single-ended output swing voltage                                             |                                                                                                                                  | 400                     |                            | 600                      | 1                  |

| V <sub>OD(O)</sub>   | Overshoot of output differential voltage                                      | $V_{DD} = 3.3V, R_T = 50$ -ohm<br>Pre-emphasis/De-emphasis = 0dB                                                                 |                         | 6%                         | 15%                      | 2x                 |

| V <sub>OD(U)</sub>   | Undershoot of output differential voltage                                     |                                                                                                                                  |                         | 12%                        | 25%                      | V <sub>swing</sub> |

| $\Delta V_{OC(SS)}$  | Change in steady-state common-<br>mode output voltage between logic<br>states |                                                                                                                                  |                         | 0.5                        | 5                        | mV                 |

| I <sub>(OS)</sub>    | Short circuit output current                                                  |                                                                                                                                  |                         | 1                          | 12                       | mA                 |

| V <sub>ODE(SS)</sub> | Steady state output differential voltage                                      | OC_Sx = GND, Data Input = 250<br>Mbps HDMI <sup>™</sup> data pattern                                                             | 560                     |                            | 840                      | · mVp-p            |

| V <sub>ODE(PP)</sub> | Peak-to-peak output differential voltage                                      | CLK Input = 25 MHz clock<br>x = 0, 1, 2, 3                                                                                       | 800                     |                            | 1200                     |                    |

| V <sub>I(open)</sub> | Single-ended input voltage under<br>high impedance input or open input        | $I_I = 10 \mu A$                                                                                                                 | V <sub>DD</sub> -<br>10 |                            | V <sub>DD</sub> + 10     | mV                 |

| R <sub>INT</sub>     | Input termination resistance                                                  | $V_{IN} = 2.9V$                                                                                                                  | 45                      | 50                         | 55                       | ohm                |

| DDC I/O              | Pins (SCLx, SCL_SINK, SDAx, SDA                                               | SINK)                                                                                                                            |                         |                            |                          | -                  |

| IT I                 | T (1 1 )                                                                      | $V_{I} = 5.5V$                                                                                                                   | -50                     |                            | 50                       |                    |

| I <sub>lkg</sub>     | Input leakage current                                                         | $V_{I} = V_{DD}$                                                                                                                 | -10                     | 1                          | 10                       | μA                 |

| C <sub>IO</sub>      | Input/output capacitance                                                      | $V_{I} = 0V$                                                                                                                     |                         | 7.5                        |                          | pF                 |

| R <sub>ON</sub>      | Switch resistance                                                             | $I_{\rm O} = 3 {\rm mA}, V_{\rm O} = 0.4 {\rm V}$                                                                                |                         | 25                         | 50                       | ohm                |

| VPASS                | Switch output voltage                                                         | $V_{I} = 3.3V, I_{I} = 100\mu A$                                                                                                 | 1.5(2)                  | 2.0                        | 2.5(3)                   | V                  |

| Status Pin           | s (HPD)                                                                       | •                                                                                                                                |                         |                            |                          |                    |

| V <sub>OH(TTL)</sub> | TTL High-level output voltage                                                 | $I_{OH} = -4mA$                                                                                                                  | 2.4                     |                            |                          | V                  |

| V <sub>OL(TTL)</sub> | TTL Low-level output voltage                                                  | $I_{OL} = 4mA$                                                                                                                   | 1                       | 1                          | 0.4                      | V                  |

#### Electrical Characteristics (over recommended operating conditions unless otherwise noted)

(Table Continued)

## Electrical Characteristics (Continued)

| Symbol                              | Parameter                                                           | Test Conditions                     | Min. | <b>Typ.</b> <sup>(1)</sup> | Max. | Units |  |

|-------------------------------------|---------------------------------------------------------------------|-------------------------------------|------|----------------------------|------|-------|--|

| Control Pins (OC_Sx, EQ_Sx, Sx, OE) |                                                                     |                                     |      |                            |      |       |  |

| I <sub>IH</sub>                     | High-level digital input current                                    | $V_{IH}$ = 2.0V or $V_{DD}$         | -10  |                            | 10   |       |  |

| I <sub>IL</sub>                     | Low-level digital input current $V_{IL} = GND \text{ or } 0.8V$ -10 |                                     | 10   | μA                         |      |       |  |

| Status Pir                          | Status Pins (HPD_SINK)                                              |                                     |      |                            |      |       |  |

| I                                   | High lovel digital input current                                    | $V_{\rm IH} = 5.3 V$                | -50  |                            | 50   |       |  |

| I <sub>IH</sub>                     | High-level digital input current                                    | $V_{\rm IH}$ = 2.0V or $V_{\rm DD}$ | -10  |                            | 10   | μA    |  |

| I <sub>IL</sub>                     | Low-level digital input current                                     | $V_{IL} = GND \text{ or } 0.8V$     | -10  |                            | 10   |       |  |

Notes:

1. All typical values are at 25°C and with a 3.3V supply.

2. The value is tested in full temperature range at 3.0V.

3. The value is tested in full temperature range at 3.6V.

| <b>Switching Characteristics</b> | (over recommended operatin | ng conditions unless otherwise noted) |

|----------------------------------|----------------------------|---------------------------------------|

|----------------------------------|----------------------------|---------------------------------------|

| Symbol                   | Parameter                                                                             | Test Conditions                                                                                            | Min. | <b>Typ.</b> <sup>(1)</sup> | Max. | Units |

|--------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|----------------------------|------|-------|

| TMDS Diffe               | rential Pins                                                                          |                                                                                                            |      | •                          | •    |       |

| tpd                      | Propagation delay                                                                     |                                                                                                            |      |                            | 2000 |       |

| t <sub>r</sub>           | Differential output signal rise time (20% - 80%)                                      |                                                                                                            | 75   |                            | 140  |       |

| tf                       | Differential output signal fall time (20% - 80%)                                      | $V_{DD} = 3.3V, R_T = 50$ -ohm,<br>pre-emphasis/de-emphasis = 0dB                                          | 75   |                            | 140  | 1     |

| t <sub>sk(p)</sub>       | Pulse skew                                                                            |                                                                                                            |      | 10                         | 50   |       |

| t <sub>sk(D)</sub>       | Intra-pair differential skew                                                          |                                                                                                            |      | 23                         | 50   |       |

| t <sub>sk(0)</sub>       | Inter-pair differential skew <sup>(2)</sup>                                           |                                                                                                            |      |                            | 100  | ps    |

| TCLK <sub>jit(pp)</sub>  | Peak-to-peak output jitter from<br>TMDS CLK channel residual jitter                   | pre-emphasis/de-emphasis = 0dB,<br>Data Input = 1.65 Gbps HDMI <sup>™</sup> data                           |      | 15                         | 30   |       |

| TDATA <sub>jit(pp)</sub> | Peak-to-peak output jitter from<br>TMDS data residual jitter                          | pattern<br>CLK Input = 165 MHz clock                                                                       |      | 18                         | 50   |       |

| t <sub>DE</sub>          | De-emphasis duration                                                                  | de-emphasis = -3.5dB,<br>Data Input = 250 Mbps HDMI <sup>™</sup> data<br>pattern, CLK Input = 25 MHz clock |      | 240                        |      |       |

| t <sub>SX</sub>          | Select to switch output                                                               |                                                                                                            |      |                            | 10   |       |

| t <sub>en</sub>          | Enable time                                                                           |                                                                                                            |      |                            | 200  | ns    |

| t <sub>dis</sub>         | Disable time                                                                          |                                                                                                            |      |                            | 10   |       |

| DDC I/O Pin              | s (SCLx, SCL_SINK, SDAx, SDA_SI                                                       | ·<br>NK)                                                                                                   |      | •                          |      |       |

| t <sub>pd(DDC)</sub>     | Propagation delay from SCLn to<br>SCL_SINK or SDAx to SDA_SINK<br>or SDA_SINK to SDAx | $C_L = 10 pF$                                                                                              |      | 0.4                        | 2.5  | ns    |

| Control and              | Status Pins (OC_SX, EQ_SX, Sx, HPI                                                    | D_SINK, HPDx)                                                                                              |      |                            |      |       |

| t <sub>pd(HPD)</sub>     | Propagation delay (from HPD_SINK to the active port of HPDx)                          | C - 10-F                                                                                                   |      | 2                          | 6.0  |       |

| t <sub>sx(HPD)</sub>     | Switch time (from port select to the latest valid status of HPDx)                     | $C_L = 10 pF$                                                                                              |      | 3                          | 6.5  | ns    |

Notes:

1. All typical values are at 25°C and with a 3.3V supply.

2.  $t_{sk(o)}$  is the magnitude of the difference in propagation delay times between any specified terminals of channel 2 to 4 of a device when inputs are tied together.

## **Application Information**

#### Supply Voltage

All  $V_{DD}$  pins are recommended to have a  $0.01 \mu F$  capacitor tied from  $V_{DD}$  to GND to filter supply noise

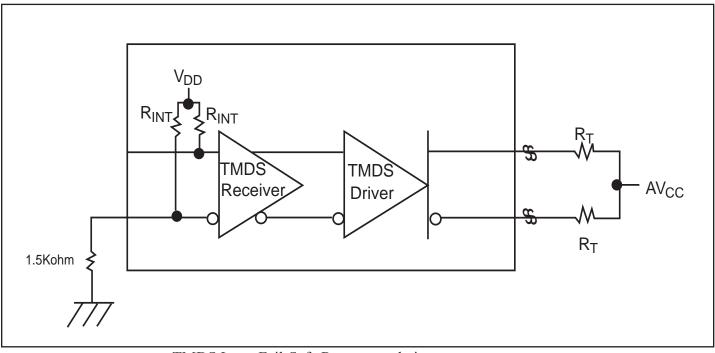

#### TMDS inputs

Standard TMDS terminations have already been integrated into Pericom's PI3HDMI301 device. Therefore, external terminations are not required. Any unused port must be left floating and not tied to GND.

### TMDS output oscillation elimination

The TMDS inputs do not incorporate a squelch circuit. Therefore, we reccomend the input to be externally biased to prevent output oscillation. One pin will be pulled high to  $V_{DD}$  with the other grounded through a 1.5K-Ohm resistor as shown.

TMDS Input Fail-Safe Recommendation

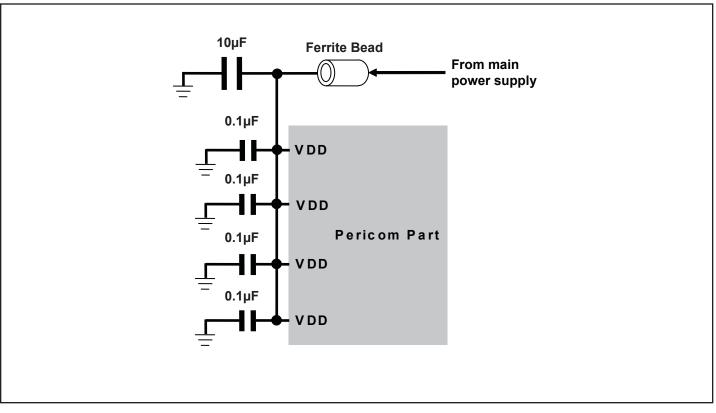

#### **Recommended Power Supply Decoupling Circuit**

Figure 1 is the recommended power supply decoupling circuit configuration. It is recommended to put  $0.1\mu$ F decoupling capacitors on each V<sub>DD</sub> pins of our part, there are four  $0.1\mu$ F decoupling capacitors are put in Figure 1 with an assumption of only four V<sub>DD</sub> pins on our part, if there is more or less V<sub>DD</sub> pins on our Pericom parts, the number of  $0.1\mu$ F decoupling capacitors should be adjusted according to the actual number of V<sub>DD</sub> pins. On top of  $0.1\mu$ F decoupling capacitors on each V<sub>DD</sub> pins, it is recommended to put a  $10\mu$ F decoupling capacitor near our part's V<sub>DD</sub>, it is for stabilizing the power supply for our part. Ferrite bead is also recommended for isolating the power supply for our part and other power supplies in other parts of the circuit. But, it is optional and depends on the power supply conditions of other circuits.

Figure 1 Recommended Power Supply Decoupling Circuit Diagram

#### **Requirements on the Decoupling Capacitors**

There is no special requirement on the material of the capacitors. Ceramic capacitors are generally being used with typically materials of X5R or X7R.

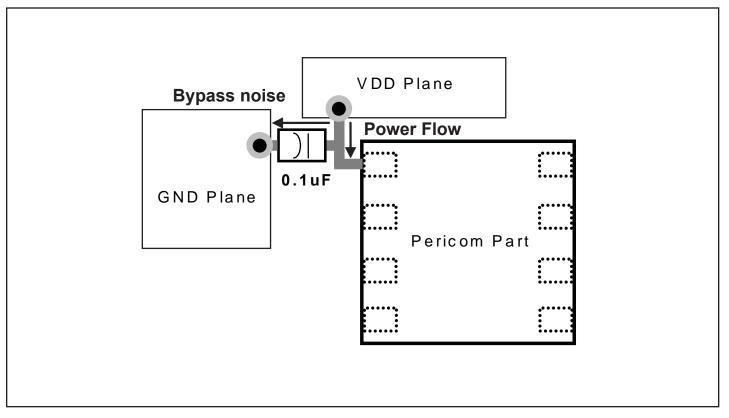

#### Layout and Decoupling CapacitorPlacement Consideration

- i. Each  $0.1\mu F$  decoupling capacitor should be placed as close as possible to each V<sub>DD</sub> pin.

- ii. V<sub>DD</sub> and GND planes should be used to provide a low impedance path for power and ground.

- iii. Via holes should be placed to connect to V<sub>DD</sub> and GND planes directly.

- iv. Trace should be as wide as possible

- v. Trace should be as short as possible.

- vi. The placement of decoupling capacitor and the way of routing trace should consider the power flowing criteria.

- vii. 10µF capacitor should also be placed closed to our part and should be placed in the middle location of 0.1µF capacitors.

- viii. Avoid the large current circuit placed close to our part; especially when it is shared the same V<sub>DD</sub> and GND planes. Since large current flowing on our V<sub>DD</sub> or GND planes will generate a potential variation on the V<sub>DD</sub> or GND of our part.

Figure 2 Layout and Decoupling Capacitor Placement Diagram

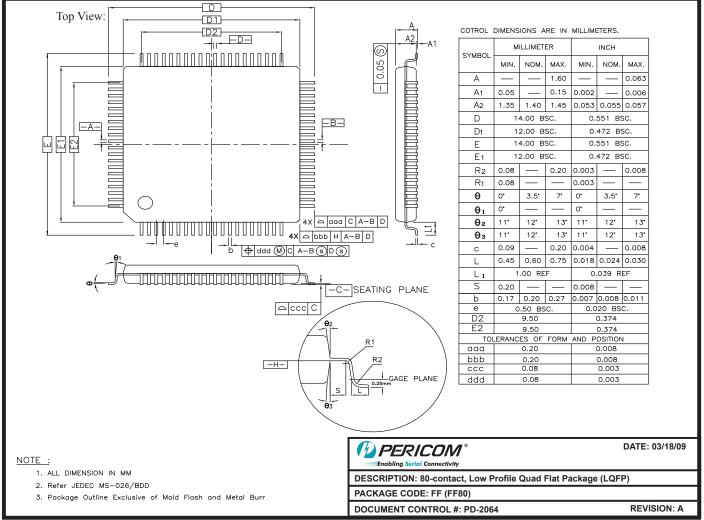

## Package Mechanical: 80-pin, Low Profile Quad Flat Package (FF80)

07-0100

#### Note:

• For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

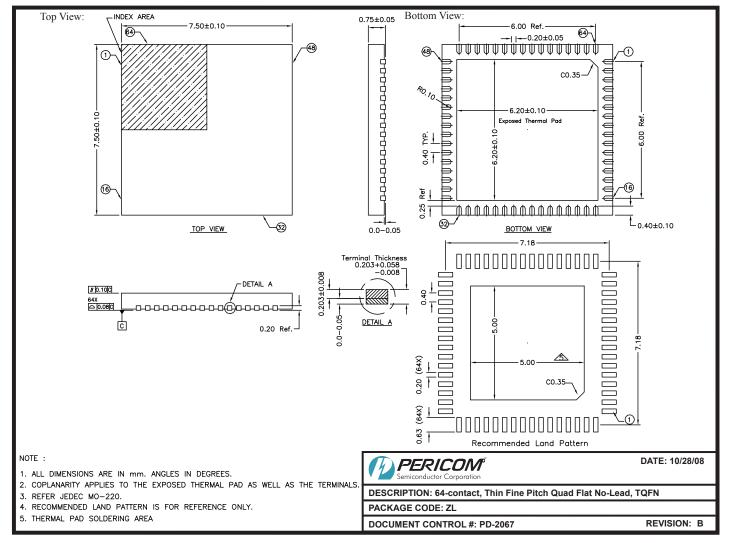

#### Package Mechanical: 64-pin, Quad Flat Package (ZL64)

08-0530

Note:

• For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

#### **Ordering Information**

| Ordering Code | Package Code | Package Description          |

|---------------|--------------|------------------------------|

| PI3HDMI301FFE | FF           | 80-pin, Pb-free & Green LQFP |

| PI3HDMI301ZLE | ZL           | 64-pin, Pb-free & Green TQFN |

Notes:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- E = Pb-free and Green

- Adding an X Suffix = Tape/Reel

#### Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Interface - Specialised category:

Click to view products by Diodes Incorporated manufacturer:

Other Similar products are found below :

CY7C910-51LMB MEC1632-AUE RKSAS4 HMC677G32 LPC47N207-JV FTP-637DSL633R SM712GX04LF04-BA MCW1001A-I/SS HOA6241-001 SC74HC4066ADTR2G NCN5120MNTWG NCN5150DR2G NCN8025MTTBG C100N50Z4A DG407AK/883B SRT2-ATT01 TDA8035HN/C1/S1J LTC1694CS5#TRMPBF DS90UB947TRGCRQ1 SP510ECF-L NCS2300MUTAG ADG1404YCPZ-REEL HMC677LP5E HMC677LP5ETR LTC1756EGN#PBF LTC1955EUH#PBF LT3669EUFD-2#PBF LTC6820HMS#3ZZTRPBF MXL1543BCAI MAX3170CAI+ XL1192D KTU1109EFAA-TR CH368L CH7307C-DEF LTC1694-1IS5#TRMPBF LTC1694CS5#TRPBF LTC1694IS5#TRM LTS 25-NP 73S8024RN-20IMF 73S8024RN-IL/F DS2413P+ DS2413P+T&R DS28E17Q+ DS8113-RNG+ MAX13036ATI+ MAX13174ECAG+ MAX216CWN+ MAX3172CAI+ AS8222-HSSM MAX6618AUB+