### PI3HDMI412AD

## **1:2** Active HDMI<sup>TM</sup> Compatible DeMux with Advanced Re-Driver Functionality for Enhanced Signal Integrity

#### Features

- Supply voltage,  $V_{DD} = 3.3V \pm 5\%$

- Compatible w/ DVI, HDMI<sup>TM</sup> 1.1, 1.2, and 1.3 signals

- · Supports both AC-coupled and DC-coupled inputs

- 1:2 Demux

- Supports Deep Color<sup>™</sup> Signals

- Configurable output swing control (500mV, 750mV, 1000mV)

- Configurable Pre-Emphasis levels (0dB, 1.5dB, 3.5dB, 6.0dB)

- Configurable De-Emphasis (0dB, -1.5dB, -3.5dB, -6.0dB)

- Configurable Equalization (1dB,3.5dB, 6dB, 8dB)

- Data Rate = 2.5Gbps (Max)

- Inputs w/ built-in termination

- Propagation delay < 2ns input

- Uni-Directional

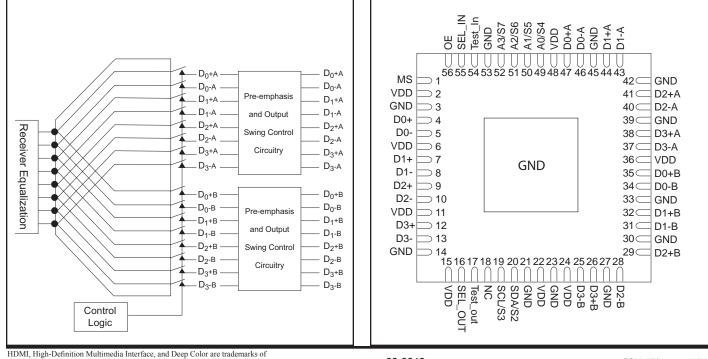

**Block Diagram**

- 10kV HBM ESD protection on all high speed data channels (Supplemental contact ESD test results are available upon request)

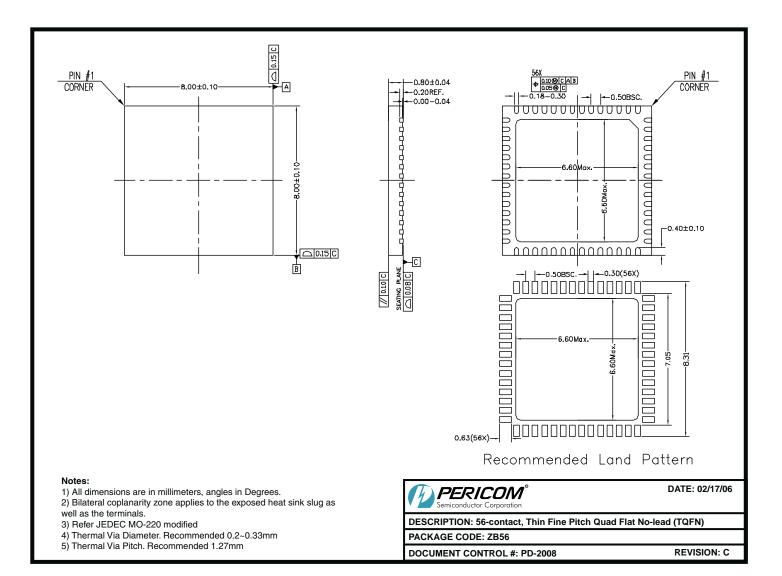

- Packaging (Pb-free & Green): 56-pad TQFN (ZB56)

#### Description

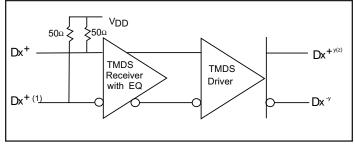

Pericom Semiconductor's PI3HDMI412AD, active-drive switch solution is targeted for high-resolution video networks that are based on DVI/HDMI<sup>TM</sup> standards, and TMDS signal processing. The PI3HDMI412AD is an active single TMDS channel to two TMDS channel DeMux with Hi-Z outputs. The device drives differential signals to multiple video display units. It provides three controllable output swing levels that can be controlled through pin control or I<sup>2</sup>C control, depending on the mode select pin. The swing levels are 500mV, 700mV & 1000mV. This solution also provides a unique advanced pre-emphasis technique to increase rise and fall times which are reduced during transmission across long distances.

The maximum DVI/HDMI<sup>TM</sup> data rate of 1.65Gbps provides a 1920x1080 resolution required by the next Gen HDTV and PC graphics products. Due to its active uni-directional feature, this switch is de-signed for usage only for the video driver's side. For PC graphics application, the device sits at the driver's side to switch between multiple display units, such as PC LCD monitor, projector, TV, etc.

PI3HDMI412AD is the industry's first active DVI/HDMI<sup>™</sup> compliant switch, which ensures transmitting high bandwidth video streams from PC graphics source to end display units. PI3HDMI412AD will also provide enhanced robust ESD/EOS protection, which is required by many consumer video networks today.

#### **Pin Configuration**

1

#### **Function Block Description**

**Notes:** 1. X = 0,1,2,3 2. Y = A,B

#### **Pin Description**

**Maximum Ratings** (Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature65              | °C to +150°C           |

|------------------------------------|------------------------|

| Supply Voltage to Ground Potential |                        |

| DC Input Voltage0.5                | $\delta V$ to $V_{DD}$ |

| DC Output Current120               | mA                     |

| Power Dissipation1.0               | W                      |

**Note:** Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

| Pin #                                                             | Pin<br>Name       | I/O   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------|-------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2, 6, 11, 15, 22, 24, 36, 48                                      | V <sub>DD</sub>   | Power | 3.3V power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3, 14, 21, 23, 27, 30, 33, 39,<br>42, 45, 53                      | GND               | Power | 0V power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 16                                                                | SEL_Out           | 0     | Output bit, that provides information to user as to which port is active, if SEL_<br>OUT = 'LOW', then Port A is active, if SEL_OUT = 'HIGH', then Port B is<br>active. Only used when MS pin is 'HIGH'                                                                                                                                                                                                                                                                                         |

| 19                                                                | SCL               | Ι     | I <sup>2</sup> C Clock Input Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 20                                                                | SDA               | I/O   | I <sup>2</sup> C Data Input/Output Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18                                                                | NC                | N/A   | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1                                                                 | MS                | Ι     | Mode Select Pin. If MS = 'HIGH', then I <sup>2</sup> C control is active. Pins 49-52 are I <sup>2</sup> C address and pin 19 is SCL and pin 20 is SDA. If MS = 'LOW', then I <sup>2</sup> C control is inactive and pin programmability is active. Pins 49-52 are control pins only for Port A, S4-S7 and pin 19 is S2 and pin 20 is S3. If 'MS' = "LOW", Port B cannot be configured and is left as default. Port B default value is 0dB pre-emphasis, 0dB de-emphasis, and 500mV output swing |

| 55                                                                | SEL_IN            | Ι     | Output port select. (Logically similar to I <sup>2</sup> C bit S1 - see page 3)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 54                                                                | Test_in           | Ι     | Input pin for internal testing. Tie to GND for normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 56                                                                | OE                | Ι     | Output is enabled and normal when $OE = 'HIGH'$ . If $OE = 'LOW'$ , both outputs, A and B, are disabled and at Hi-Z                                                                                                                                                                                                                                                                                                                                                                             |

| 17                                                                | Test_Out          | 0     | Output pin for internal testing. Not used for normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4, 5, 7, 8, 9, 10, 12, 13                                         | Dx                | Ι     | Input TMDS high speed signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 28, 29, 31, 32, 34, 35, 40, 41,<br>43, 44, 46, 47, 25, 26, 37, 38 | Dx <sup>y</sup>   | 0     | Output TMDS high speed signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 49,50, 51, 52                                                     | A0, A1,<br>A2, A3 | Ι     | $I^2C$ address inputs if MS = 'HIGH'.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 49,50, 51, 52                                                     | S4, S5,<br>S6, S7 | Ι     | If MS = 'LOW', then pins 49-52 are control bits S4-S7 for port A only, as shown in truth table on page 3 of datasheet                                                                                                                                                                                                                                                                                                                                                                           |

| 19                                                                | S3                | Ι     | If $MS = LOW'$ , then pins 19 is control bit S3, as shown in the truth table on page 3                                                                                                                                                                                                                                                                                                                                                                                                          |

| 20                                                                | S2                | Ι     | If MS = 'LOW', then pins 20 is control bit S2, as shown in the truth table on page 3                                                                                                                                                                                                                                                                                                                                                                                                            |

HDMI, High-Definition Multimedia Interface, and Deep Color are trademarks of

#### I<sup>2</sup>C Truth Table

(At power up, default values are: Port A is active, signal swing is set to 500mV, pre-emphasis and de-emphasis are at 0dB, and equalization is at 1dB)

| Byte 2: S[7:0]=0000000 | )1     | Byte 3: S[7:0]=00000001             |

|------------------------|--------|-------------------------------------|

| Output Swing:          | 500mV  | Output Swing: Defined by Byte 2     |

| Pre-emphasis:          | 0dB    | Pre-emphasis:                       |

| De-Emphasis:           | 0dB    | De-Emphasis:                        |

| Equalization:          | 1dB    | Active Port: port A, in normal mode |

| Active Port:           | port A |                                     |

#### **BYTE 1 (Address Assignment)**

| Address | A6 | A5 | A4 | A3 | A2 | A1 | A0 | R/W     |

|---------|----|----|----|----|----|----|----|---------|

| Value   | 1  | 1  | 0  | A3 | A2 | A1 | A0 | R=1/W=0 |

#### BYTE 2 (1st Data byte - Port A control and input control)

| Port A and Input   | <b>S7</b> | <b>S6</b> | <b>S</b> 5 | <b>S4</b> | <b>S</b> 3 | <b>S2</b> | <b>S1</b> | <b>S0</b> |             | Result            |                  |  |

|--------------------|-----------|-----------|------------|-----------|------------|-----------|-----------|-----------|-------------|-------------------|------------------|--|

| Control            |           |           |            |           |            |           |           |           | Swing (mV)  | Pre-emphasis (dB) | De-emphasis (dB) |  |

| Swing Control      | 0         | 0         | 0          | 0         | X          | X         | x         | x         | 500         | 0                 | 0                |  |

|                    | 0         | 0         | 0          | 1         | X          | X         | x         | x         | 750         | 0                 | 0                |  |

|                    | 0         | 0         | 1          | 0         | x          | x         | x         | x         | 1000        | 0                 | 0                |  |

|                    | 0         | 0         | 1          | 1         | x          | x         | x         | x         | N/A         | N/A               | N/A              |  |

| Pre-Emphasis       | 0         | 1         | 0          | 0         | X          | X         | x         | X         | 500         | 0                 | 0                |  |

|                    | 0         | 1         | 0          | 1         | X          | X         | x         | X         | 500         | 1.5               | 0                |  |

|                    | 0         | 1         | 1          | 0         | X          | X         | x         | X         | 500         | 3.5               | 0                |  |

|                    | 0         | 1         | 1          | 1         | X          | X         | x         | X         | 500         | 6.0               | 0                |  |

| De-Emphasis        | 1         | 0         | 0          | 0         | x          | x         | x         | X         | 750         | 0                 | 0                |  |

|                    | 1         | 0         | 0          | 1         | X          | X         | x         | X         | 750         | 0                 | -1.5             |  |

|                    | 1         | 0         | 1          | 0         | x          | x         | x         | X         | 750         | 0                 | -3.5             |  |

|                    | 1         | 0         | 1          | 1         | x          | x         | x         | X         | 750         | 0                 | -6.0             |  |

| Output Port Select | X         | x         | x          | x         | x          | x         | 0         | 1         |             |                   | Port A is active |  |

|                    | X         | x         | х          | х         | x          | x         | 1         | 1         |             |                   | Port B is active |  |

|                    | X         | x         | x          | x         | x          | x         | x         | 0         | Port A = Hi |                   |                  |  |

| Equalization (dB)  | X         | x         | x          | x         | 0          | 0         | x         | X         | 1           |                   |                  |  |

|                    | X         | x         | х          | х         | 0          | 1         | x         | x         |             |                   | 3.5              |  |

|                    | X         | x         | х          | x         | 1          | 0         | x         | x         |             |                   | 6                |  |

|                    | x         | x         | X          | X         | 1          | 1         | x         | x         |             |                   | 8                |  |

#### PI3HDMI412AD 1:2 Active HDMI™ Compatible DeMux with Advanced Re-Driver Functionality for Enhanced Signal Integrity

#### BYTE 3 (2nd Data byte - Port B control)

| Port B Control only | <b>S7</b> | <b>S6</b> | <b>S</b> 5 | <b>S4</b> | <b>S</b> 3 | S2 | <b>S1</b> | <b>S0</b> |            | Result            |                  |

|---------------------|-----------|-----------|------------|-----------|------------|----|-----------|-----------|------------|-------------------|------------------|

|                     |           |           |            |           |            |    |           |           | Swing (mV) | Pre-emphasis (dB) | De-emphasis (dB) |

| Swing Control       | 0         | 0         | 0          | 0         | X          | X  | X         | X         | 500        | 0                 | 0                |

|                     | 0         | 0         | 0          | 1         | X          | X  | X         | X         | 750        | 0                 | 0                |

|                     | 0         | 0         | 1          | 0         | x          | x  | X         | X         | 1000       | 0                 | 0                |

|                     | 0         | 0         | 1          | 1         | X          | X  | X         | X         | N/A        | N/A               | N/A              |

| Pre-Emphasis        | 0         | 1         | 0          | 0         | X          | X  | X         | X         | 500        | 0                 | 0                |

|                     | 0         | 1         | 0          | 1         | x          | X  | X         | X         | 500        | 1.5               | 0                |

|                     | 0         | 1         | 1          | 0         | X          | X  | X         | X         | 500        | 3.5               | 0                |

|                     | 0         | 1         | 1          | 1         | x          | x  | X         | X         | 500        | 6.0               | 0                |

| De-Emphasis         | 1         | 0         | 0          | 0         | X          | X  | X         | X         | 750        | 0                 | 0                |

|                     | 1         | 0         | 0          | 1         | X          | X  | X         | X         | 750        | 0                 | -1.5             |

|                     | 1         | 0         | 1          | 0         | x          | x  | x         | X         | 750        | 0                 | -3.5             |

|                     | 1         | 0         | 1          | 1         | X          | X  | X         | X         | 750        | 0                 | -6.0             |

| Output Port Select  | x         | x         | x          | х         | X          | X  | 0         | 1         | Norm       |                   |                  |

|                     | x         | x         | x          | x         | x          | x  | 1         | 1         |            |                   | TEST MODE        |

|                     | x         | х         | х          | х         | X          | X  | X         | 0         |            |                   | Port B = Hi-Z    |

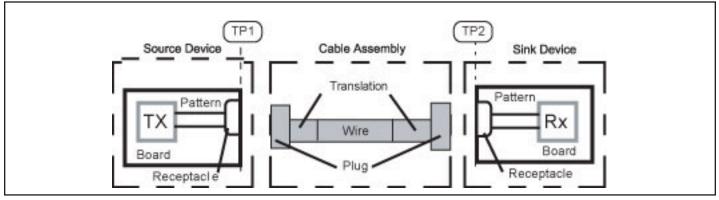

#### **TMDS** Compliance Test Results

| Item                                                 | HDMI <sup>TM</sup> 1.3 Spec                                                                                                     | Pericom TMDS Product Spec                                                                                                      |  |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Operating Conditions                                 | •                                                                                                                               |                                                                                                                                |  |

| Termination Supply Voltage, AVDD                     | $3.3V \leq 5\%$                                                                                                                 | 3.30 ± 5%                                                                                                                      |  |

| Terminal Resistance                                  | $50 \text{ Ohm} \le 10\%$                                                                                                       | 45 to 55 Ohm                                                                                                                   |  |

| Source DC Characteristics at TP1                     | ·                                                                                                                               |                                                                                                                                |  |

| Single-ended high level output voltage, $V_{\rm H}$  | $A_{VDD} \le 10 mV$                                                                                                             | $A_{VDD} \leq 10 mV$                                                                                                           |  |

| Single-ended low level output voltage, $V_{\rm L}$   | $(A_{VDD} - 600 \text{mV}) \le \text{VL} \le (A_{VDD} - 400 \text{mV})$                                                         | $(A_{VDD} - 600mV) \le VL \le (A_{VDD} - 400mV)$                                                                               |  |

| Single-ended output swing voltage, $V_{swing}$       | $400mV \le V_{swing} \le 600mV$                                                                                                 | $400mV \le V_{swing} \le 600mV$                                                                                                |  |

| Single-ended standby (off) output voltage, $V_{off}$ | $A_{VDD} \pm 10 mV$                                                                                                             | $A_{VDD} \pm 10 mV$                                                                                                            |  |

| Single-ended standby (off) output current, Ioff      | I <sub>OFF</sub>   < 10uA                                                                                                       | I <sub>OFF</sub>   <10uA                                                                                                       |  |

| Transmitter AC Characteristics at TP1                |                                                                                                                                 | I                                                                                                                              |  |

| Risetime/Falltime (20%-80%)                          | $75ps \le Risetime/Falltime \le 0.4$ Tbit $(75ps \le tr/tf \le 242ps)$ @ 1.65Gbps                                               | 240ps                                                                                                                          |  |

| Intra-Pair Skew at Transmitter Connector, max        | 0.15 Tbit<br>(90.9ps @ 1.65Gbps)                                                                                                | 60ps max                                                                                                                       |  |

| Inter-Pair Skew at Transmitter Connector, max        | 0.2 Tpixel<br>(1.2ns @ 1.65Gbps)                                                                                                | 100ps max                                                                                                                      |  |

| Clock Jitter, max                                    | 0.25 Tbit<br>(151.5ps @ 1.65Gbps)                                                                                               | 82ps max                                                                                                                       |  |

| Sink Operating DC Characteristics at TP2             | ·                                                                                                                               | •                                                                                                                              |  |

| Input Differential Voltage Level, V <sub>diff</sub>  | $150 \le V diff \le 1200 mV$                                                                                                    | $150mV \le V_{DIFF} \le 1200mV$                                                                                                |  |

| Input Common Mode Voltage Level, $V_{ICM}$           | $\begin{array}{l} A_{VDD} \mbox{-}300mV \leq V_{ICM} < A_{VDD} \mbox{-}37.5mV \\ \mbox{or } A_{VDD} \mbox{\pm}10\% \end{array}$ | $\begin{array}{l} A_{VDD} \text{ -} 300mV \leq V_{ICM} < A_{VDD} \text{ -} \\ 37.5mV \text{ or } A_{VDD} \pm 10\% \end{array}$ |  |

| Sink DC Characteristics When Source Disable          | ed or Disconnected at TP2                                                                                                       |                                                                                                                                |  |

| Differential Voltage Level                           | $A_{VDD} \pm 10 mV$                                                                                                             | $A_{VDD} \pm 10 mV$                                                                                                            |  |

| Symbol           | Parameter                                 | Test<br>Condition <sup>(1)</sup> | Min.              | <b>Typ.</b> <sup>(2)</sup> | Max.                    | Units |

|------------------|-------------------------------------------|----------------------------------|-------------------|----------------------------|-------------------------|-------|

| V <sub>H</sub>   | Single-ended high level output voltage    |                                  | $V_{DD} - 10 mV$  | V <sub>DD</sub>            | $V_{DD} + 10mV$         | V     |

| VL               | Single-ended low level output voltage     |                                  | $V_{DD} - 600 mV$ |                            | V <sub>DD</sub> - 400mV | V     |

| Vswing           | Single-ended output swing voltage         |                                  | 400               |                            | 600                     | mV    |

| V <sub>OFF</sub> | Single-ended standby (off) output voltage |                                  | $V_{DD} - 10mV$   | V <sub>DD</sub>            | $V_{DD} + 10mV$         | V     |

| I <sub>OFF</sub> | Single-ended standby (off) output current |                                  |                   |                            | 10                      | μs    |

| V <sub>OS</sub>  | Offset Voltage                            |                                  |                   |                            | $V_{DD} - 250 mV$       | V     |

| V <sub>IH</sub>  | Minimum Input High Voltage                |                                  | 1.8               |                            |                         | v     |

| V <sub>IL</sub>  | Minimum Input Low Voltage                 |                                  |                   |                            | 0.8                     | v     |

| I <sub>CC</sub>  | Power Supply Current                      |                                  |                   |                            | 280                     | mA    |

#### **DC Electrical Characteristics** ( $T_A = -40^{\circ}C$ to +85°C, unless otherwise noted. $V_{DD} = 3.3V \pm 0.3V$ )

#### AC Electrical Characteristics $(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, V_{DD} = 3.3V \pm 0.3V)$

| Symbol             | Paramter                                                  | Test<br>Conditions <sup>(1)</sup> | Min. | <b>Typ.</b> <sup>(2)</sup> | Max.                          | Units |

|--------------------|-----------------------------------------------------------|-----------------------------------|------|----------------------------|-------------------------------|-------|

| T <sub>20-80</sub> | Rise time/fall time (20% - 80%)                           |                                   | 75   |                            | 240                           | ps    |

|                    | Overshoot                                                 |                                   |      |                            | 15% of V <sub>swing</sub> * 2 |       |

|                    | Undershoot                                                |                                   |      |                            | 25% of V <sub>swing</sub> * 2 |       |

|                    | Intra-Pair Skew at Source Connector                       |                                   |      |                            | 60                            | ps    |

|                    | Inter-Pair Skew at Connector                              |                                   |      |                            | 100                           | ps    |

|                    | Clock duty cycle                                          |                                   | 40%  | 50%                        | 60%                           |       |

|                    | Through connection impedance                              |                                   | 85   | 100                        | 115                           | ps    |

|                    | TMDS differential clock Jitter                            |                                   |      |                            | 82                            | ps    |

|                    | At Termination impedance                                  |                                   | 90   | 100                        | 110                           | ps    |

| t <sub>PHLD</sub>  | Differenital Propagation Delay High to Low                |                                   |      | 1.0                        |                               | ns    |

| t <sub>PLHD</sub>  | Differential Propagation Delay Low to High                |                                   |      | 1.0                        |                               | ns    |

| t <sub>SKD</sub>   | Differential Skew   t <sub>PHLD</sub> - t <sub>PLHD</sub> |                                   |      | 25                         |                               | ps    |

| t <sub>PHZ</sub>   | Disable Time High to Z                                    |                                   |      | 5                          |                               |       |

| t <sub>PLZ</sub>   | Disable Time Low to Z                                     |                                   |      | 5                          |                               | ns    |

| t <sub>PZH</sub>   | Enable Time Z to High                                     |                                   |      | 1                          |                               |       |

| t <sub>PZL</sub>   | Enable Time Z to Low                                      |                                   |      | 1                          |                               | μs    |

Notes:

For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device type. 1.

Typical values are at  $V_{DD} = 3.3V$ ,  $T_A = 25^{\circ}C$  ambient and maximum loading. 2.

#### **Power Supply Characteristics**

| $V_{DD} = Max., V_{IN} = V_{DD} OE =$                  |    |

|--------------------------------------------------------|----|

| I <sub>CC</sub> Quiescent Power Supply Current 'LOW' 1 | mA |

Notes:

1. For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device type. Typical values are at  $V_{DD} = 3.3V$ ,  $T_A = 25^{\circ}C$  ambient and maximum loading. 2.

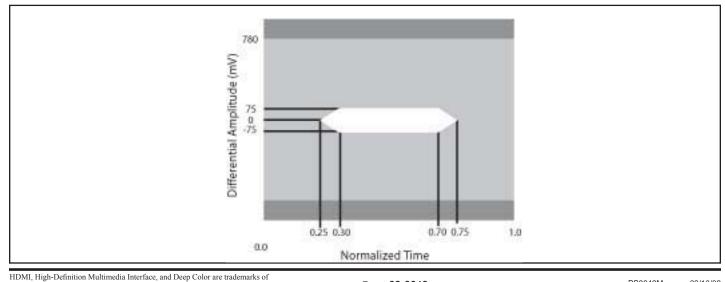

#### **TMDS Link Test Points**

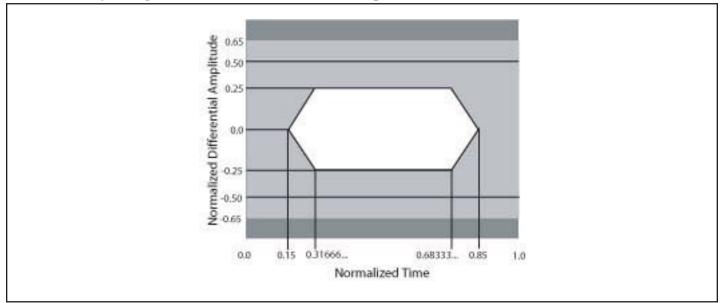

Normalized Eye Diagram Mask at TP1 for Source Requirements

Absolute Eye Diagram Mask at TP2 for Sink Requirements

HDMI Licensing, LLC in the United States and other countries.

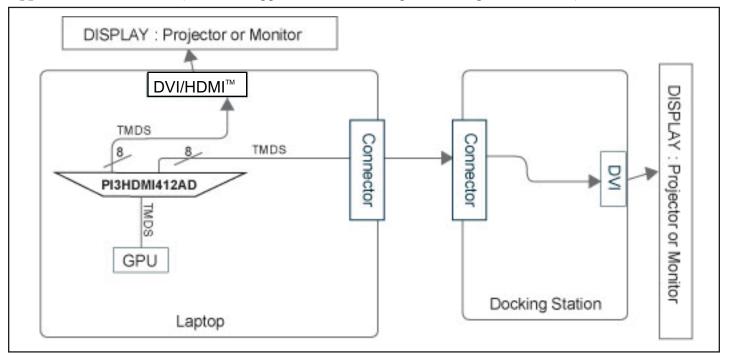

Application Information (Please see application note for important design information.)

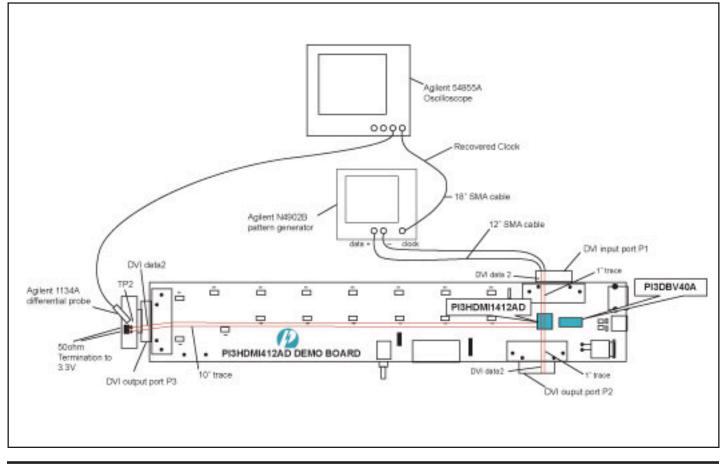

#### DVI TP2 (Tx) Compliance Test Setup

HDMI, High-Definition Multimedia Interface, and Deep Color are trademarks of HDMI Licensing, LLC in the United States and other countries.

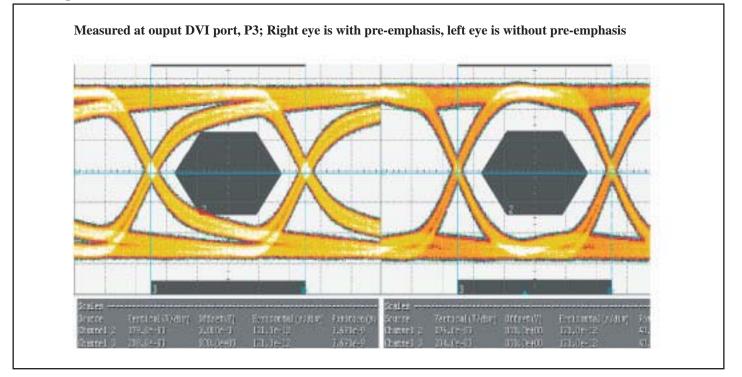

#### **Pre-Emphasis Validation**

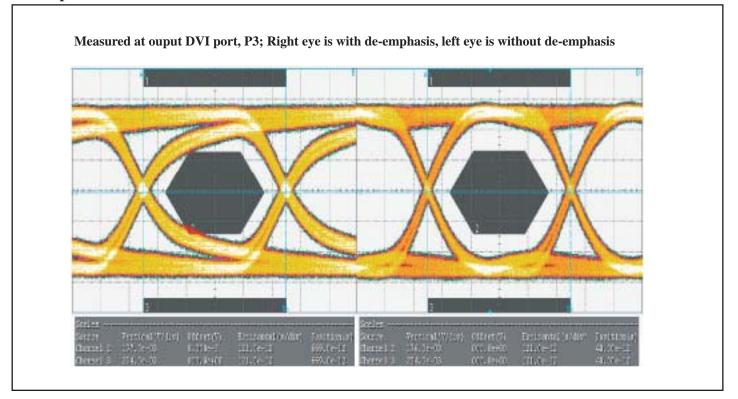

#### **De-Emphasis Validation**

HDMI, High-Definition Multimedia Interface, and Deep Color are trademarks of

## PI3HDMI412AD **PERICOM**<sup>®</sup> 1:2 Active HDMI<sup>™</sup> Compatible DeMux with Advanced Re-Driver Functionality for Enhanced Signal Integrity

#### **Ordering Information**

| Ordering Code   | Package Code | Package Description          |

|-----------------|--------------|------------------------------|

| PI3HDMI412ADZBE | ZB           | 56-pin, Pb-free & Green TQFN |

Notes:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- E = Pb-free and Green

- Adding an X Suffix = Tape/Reel

- HDMI & Deep Color are trademarks of Silicon Image

#### Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com

#

#### PI3HDMI412AD 1:2 Active HDMI™ Compatible DeMux with Advanced Re-Driver Functionality for Enhanced Signal Integrity

HDMI Licensing, LLC, a wholly owned subsidiary of Silicon Image, Inc., is the agent responsible for licensing the HDMI Specification, promoting the HDMI standard and providing education on the benefits of HDMI to retailers and consumers. The HDMI Specification was developed by Sony, Hitachi, Thomson (RCA), Philips, Matsushita (Panasonic), Toshiba and Silicon Image as the digital interface standard for the consumer electronics market. The HDMI specification combines uncompressed high-definition video and multi-channel audio in a single digital interface to provide crystal-clear digital quality over a single cable. For more information about HDMI, please visit www.hdmi.org

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Video Switch ICs category:

Click to view products by Diodes Incorporated manufacturer:

Other Similar products are found below :

PI3HDX621FBE PI3HDMI2410FFE PI3VDP12412NEE HD3SS212ZQER PI3HDMI412ADZBEX AD8191ASTZ LT6555IGN#PBF AD8190ACPZ HD3SS215IZQER MAX4567CSE+ MAX4566ESE+ MAX4566CSE+ MAX4567ESE+ PI3HDX412BDZBEX NJM2244M LT1203CN8#PBF MAX4885ETJ+T MAX4589CAP+ MAX4565EAP+ MAX4565CAP+ MAX4545EAP+ MAX4545CAP+ MAX4529CUT+T MAX4545CWP+ MAX4547CEE+ MAX4565EAP+ MAX4562CEE+ MAX4562EEE+ MAX4563CEE+ MAX4563CEE+ MAX4563CEE+ MAX4566CEE+ MAX4567EEE+ MAX4573CAI+ MAX4584EUB+ MAX4586EUB+ MAX4587EUB+ MAX4588CAI+ EL4340IUZ MAX4885EETG+CK2 MAX4565CPP+ MAX4545EPP+ NJM2246M NJM2279D NJM2249M FSAV330MTCX FSAV430MTCX FSAV430QSCX FSAV433MTCX FSAV450BQX FSHDMI08MTDX