# 2:1 Active HDMI™1.4 Source-side Switch with Integrated ARC and Fast Switching Support

#### **Features**

- → HDMI 1.4 compliant

- → Operation up to 3.4 Gbps per lane (340 MHz pixel clock) to support 4K x 2K @24Hz (297 MHz) and 3D video format (1080p, 1080i and 720p)

- → Support up to 48-bit per pixel Deep Color<sup>TM</sup>

- → Integrated ARC(Audio Return Channel) and Rx Sense function

- → Fast switching between two HDMI input ports

- → Programmable equalizer, emphasis and amplitude settings to achieve optimized HDMI signal integrity

- → Each input can be AC coupled or DC coupled, while the output will maintain TMDS compliance DC coupled, current steering signals

- → Idle clock detection function for output squelch and auto standby

- → Integrated ESD protection on I/O pins to connector

- □ 8 KV contact per IEC61000-4-2, level 4

- □ 8 KV HBM

- → Industrial temperature coverage

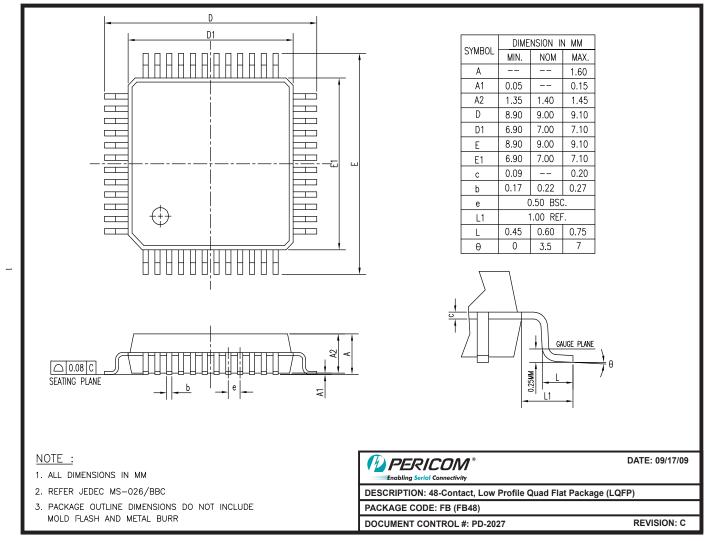

- → Packaging (Pb-free & Green): 48-contact LQFP (FB)

#### **Description**

PI3HDMI521 is 2:1 active switch that supports HDMI 1.4 specification with data rate up to 3.4 Gbps.

The I<sup>2</sup>C configuration function with multiple system control signal integration of DDC channel MUX, Hot Plug Detection DEMUX, cable plug-unplug detection and HDMI 1.4 ARC transmitter help to save the extra requirement of GPIO control pins or control chip and provide optimized trace routing and component reduction.

Programmable termination settings at TMDS inputs help to avoid the compatibility issue caused by non standard HDMI source to determine the connection status of TMDS channel with proper termination voltage setting. The programmable output termination setting supports double termination option between PI3HDMI521 and the HDMI receiver chip to ease the reflection effect caused by improper impedance matching design and reducing jittery signals.

PI3HDMI521 integrates ARC and supports video fast switching among HDMI ports.

The device is fully compatible with HDMI 1.4 and supports backward compatibility to the DVI 1.0 standard.

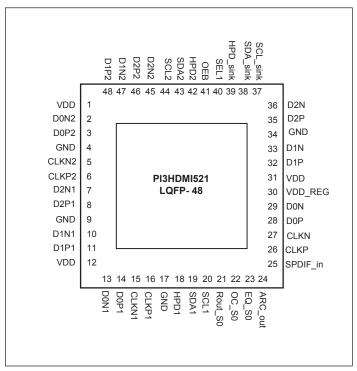

## **Pin Configuration**

1

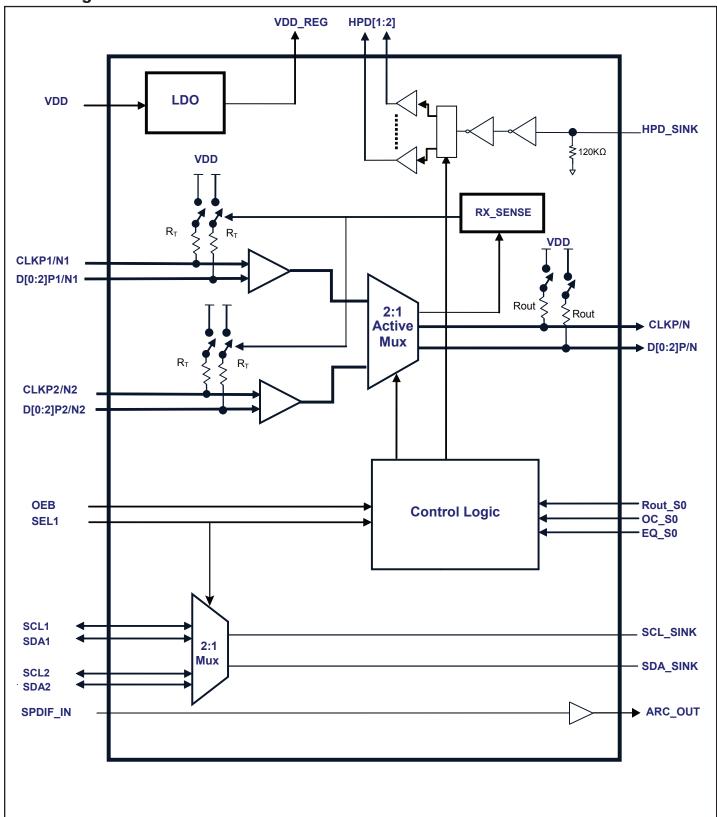

## **Block Diagram**

08/30/12

## **Pin Description**

| Pin# | Pin Name | Type <sup>1</sup> | Description                                                                                                                                                     |  |  |  |  |

|------|----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7    | D2N1     |                   |                                                                                                                                                                 |  |  |  |  |

| 8    | D2P1     |                   |                                                                                                                                                                 |  |  |  |  |

| 10   | D1N1     |                   |                                                                                                                                                                 |  |  |  |  |

| 11   | D1P1     |                   | D (1 TMDC)                                                                                                                                                      |  |  |  |  |

| 13   | D0N1     | I                 | Port 1 TMDS inputs. Rt = 50 Ohm                                                                                                                                 |  |  |  |  |

| 14   | D0P1     |                   |                                                                                                                                                                 |  |  |  |  |

| 15   | CLKN1    |                   |                                                                                                                                                                 |  |  |  |  |

| 16   | CLKP1    |                   |                                                                                                                                                                 |  |  |  |  |

| 45   | D2N2     |                   |                                                                                                                                                                 |  |  |  |  |

| 46   | D2P2     |                   |                                                                                                                                                                 |  |  |  |  |

| 47   | D1N2     |                   |                                                                                                                                                                 |  |  |  |  |

| 48   | D1P2     |                   | Port 2 TMDC inputs Dt. 50 Ohm                                                                                                                                   |  |  |  |  |

| 2    | D0N2     | I                 | Port 2 TMDS inputs. Rt = 50 Ohm                                                                                                                                 |  |  |  |  |

| 3    | D0P2     |                   |                                                                                                                                                                 |  |  |  |  |

| 5    | CLKN2    |                   |                                                                                                                                                                 |  |  |  |  |

| 6    | CLKP2    |                   |                                                                                                                                                                 |  |  |  |  |

| 36   | D2N      |                   |                                                                                                                                                                 |  |  |  |  |

| 35   | D2P      |                   |                                                                                                                                                                 |  |  |  |  |

| 33   | D1N      |                   |                                                                                                                                                                 |  |  |  |  |

| 32   | D1P      | 0                 | TMDS Outputs. Rout = 50 Ohm when Rout_S0 = High                                                                                                                 |  |  |  |  |

| 29   | D0N      |                   | TMD3 Outputs. Rout = 50 Offili when Rout_50 = Flight                                                                                                            |  |  |  |  |

| 28   | D0P      |                   |                                                                                                                                                                 |  |  |  |  |

| 27   | CLKN     |                   |                                                                                                                                                                 |  |  |  |  |

| 26   | CLKP     |                   |                                                                                                                                                                 |  |  |  |  |

| 39   | HPD_SINK | I                 | Sink side hot plug detector input; internal pull-down at 120 KOhm.                                                                                              |  |  |  |  |

| 18   | HPD1     | О                 | Port 1 HPD output                                                                                                                                               |  |  |  |  |

| 42   | HPD2     | О                 | Port 2 HPD output                                                                                                                                               |  |  |  |  |

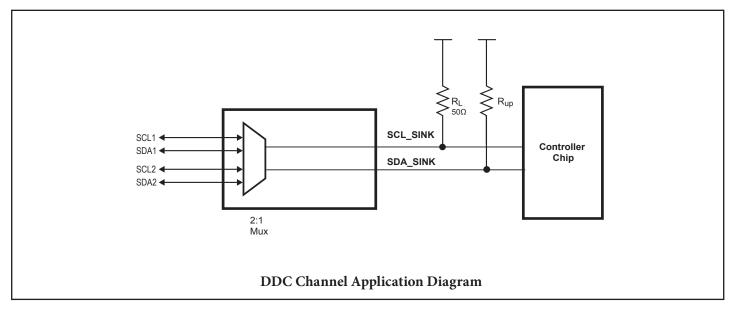

| 19   | SDA1     | IO                | Port 1 DDC Data                                                                                                                                                 |  |  |  |  |

| 20   | SCL1     | IO                | Port 1 DDC Clock                                                                                                                                                |  |  |  |  |

| 43   | SDA2     | IO                | Port 2 DDC Data                                                                                                                                                 |  |  |  |  |

| 44   | SCL2     | IO                | Port 2 DDC Clock                                                                                                                                                |  |  |  |  |

| 37   | SCL_SINK | IO                | Sink side DDC Clock                                                                                                                                             |  |  |  |  |

| 38   | SDA_SINK | IO                | Sink side DDC Data                                                                                                                                              |  |  |  |  |

|      |          |                   | TMDS output termination selection.                                                                                                                              |  |  |  |  |

| 21   | Rout_S0  | I                 | If HIGH or floating, then 50 Ohm is present on TMDS output pins. if LOW, then 50 Ohm is not present on TMDS output pins. This pin has internal 100 KOhm pull-up |  |  |  |  |

| 41   | OEB      | I                 | Output Enable control. Active low. Internal 100 KOhm pull-down. See truth table for functionality.                                                              |  |  |  |  |

# **Pin Description**

| Pin#            | Pin Name | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                      |

|-----------------|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22              | OC_S0    | I                 | TMDS output pre-emphasis selection. See OC_S0 truth table for functionality.  This pin has internal 100 KOhm pull-up                                                                                                                                             |

| 23              | EQ_S0    | I                 | TMDS input equalization selection.  If LOW or floating, EQ is set at 9 dB for all TMDS data inputs  If HIGH, EQ is set at 15 dB for all TMDS data inputs (please note, TMDS clock inputs are always set to 3 dB eq).  This pin has an internal 100 KOhm pull-low |

| 40              | SEL1     | I                 | PORT1 or PORT2 selection. Please see truth table for functionality This pin has an internal 100 KOhm pull-up                                                                                                                                                     |

| 25              | SPDIF_IN | I                 | Single mode ARC signal input                                                                                                                                                                                                                                     |

| 24              | ARC_OUT  | О                 | Single mode ARC signal output                                                                                                                                                                                                                                    |

| 1, 12, 31       | VDD      | PWR               | 3.3V power supply                                                                                                                                                                                                                                                |

| 30              | VDD_REG  | PWR               | LDO output for internal core supplier. External capacitor 2.2 to 4.7 $\mu F$ should be added to GND.                                                                                                                                                             |

| 4, 9, 17,<br>34 | GND      | GND               | Supply Ground                                                                                                                                                                                                                                                    |

#### Note:

$1. \ \ I = Input, O = Output, IO = Bidirectional \ Input/Output, PWR = \ Power, \quad GND = Ground$

## **Description of Operation**

#### **Squelch function:**

Squelch control is using low frequency signal detection. When TMDS input clock frequency is less than 10 MHz, power-down mode will initiate to save power.

#### **Rx-sense detector:**

This device searches for 50 Ohm termination present in the other side of HDMI Receiver. If the 50 Ohm is not present in the other side, the device determine no valid HDMI receiver chip is connected. Then, this device will turn off 50 Ohm input termination resistors for all TMDS data and clock pairs and enter into the power-down mode.

#### OC\_S0 Truth Table (Swing setting 500 mV as default)

| TMDS output pre-emphasis   | s setting                | Setting Value          |                          |

|----------------------------|--------------------------|------------------------|--------------------------|

| Rout_S0 (internal pull-up) | OC_S0 (internal pull-up) | Single-end Vswing (mV) | Pre-emphasis (dB)        |

| 0                          | 0                        | 500                    | 0 (open drain)           |

| 0                          | 1                        | 500                    | 2.5 (open drain)         |

| 1                          | 0                        | 500                    | 0 (double termination)   |

| 1                          | 1                        | 500                    | 2.5 (double termination) |

#### Note

#### **Port Selection Truth Table**

| OEB (Internal pull-down) | SEL1 | TMDS port                       | DDC port    | HPD port    |

|--------------------------|------|---------------------------------|-------------|-------------|

| 0                        | 1    | CLKN/P1, D0N/P1, D1N/P1,D2N/P1  | SCL1/SDA1   | HPD1        |

| 0                        | 0    | CLKN/P2, D0N/P2, D1N/P2, D2N/P2 | SCL2/SDA2   | HPD2        |

| 1                        | X    | OFF                             | Follow SEL1 | Follow SEL1 |

#### EQ\_S0 Truth Table

| EQ_S0 (Internal pull-down) | Operation |

|----------------------------|-----------|

| 0                          | 9 dB      |

| 1                          | 15 dB     |

#### Note

1. For TMDS CLK channels, the EQ value is fixed to 3dB.

<sup>1.</sup> open drain (Rout off); double termination (Rout on).

<sup>2.</sup> TMDS CLK pre-emphasis value is fixed to 0 dB.

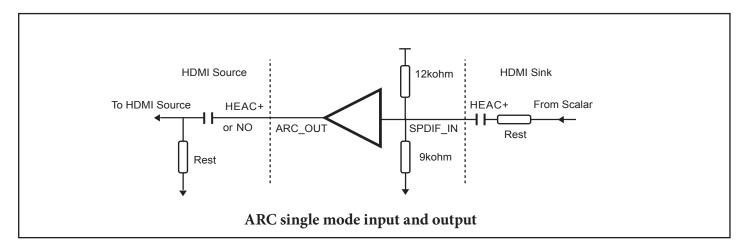

#### **Audio Return Channel:**

There are two ARC input modes, common mode and single mode input. This device can supports "single mode input" only.

# **Absolute Maximum Ratings**

| Item                               | Rating                         |

|------------------------------------|--------------------------------|

| Supply Voltage to Ground Potential | 5.5V                           |

| All Inputs and Outputs             | -0.5V to V <sub>DD</sub> +0.5V |

| Ambient Operating Temperature      | -40 to +85°C                   |

| Storage Temperature                | -65 to +150°C                  |

| Junction Temperature               | 150°C                          |

| Soldering Temperature              | 260°C                          |

Note: Stress beyond those lists under "Absolute Maximum Ratings" may cause permanent damage to the device

## **Recommended Operation Conditions**

| Parameter                                         | Min. | Тур. | Max. | Unit |

|---------------------------------------------------|------|------|------|------|

| Ambient Operating Temperature                     | -40  |      | 85   | °C   |

| Power Supply Voltage (measured in respect to GND) |      |      | 3.6  | V    |

## **DC Specification** ( $V_{DD} = 3.3 \pm 10\%$ )

| Parameter            | Parameter                                       | Conditions                                                                 | Min. | Тур. | Max. | Unit |  |

|----------------------|-------------------------------------------------|----------------------------------------------------------------------------|------|------|------|------|--|

| $V_{\mathrm{DD}}$    | Operating Voltage                               |                                                                            | 3.0  | 3.3  | 3.6  | V    |  |

|                      |                                                 | Output Enable (open drain 500 mV single-ended 0 dB pre-emphasis)           |      | 120  | 150  | mA   |  |

| $I_{DD}$             | VDD Supply Current                              | Output Enable ( double termination, 500 mV single-ended 0 dB pre-emphasis) |      | 190  | 230  | mA   |  |

| Idd_Squelch          | Supply Current in squelch mode                  | Input TMDS signal is not valid                                             |      | 11   | 13   | mA   |  |

| Idd_Rx sense         | supply current when no 50<br>Ohm detected in Rx | input TMDS is valid, but 50 Ohm Rx is not detected                         |      | 4    | 5    | mA   |  |

| I <sub>stb</sub>     | Standby mode                                    | V <sub>DD</sub> =3.6V, HPD_x=0, ARC_OUT=0, OEB = High                      |      | 4    | 5    | mA   |  |

| V <sub>OL_HPD</sub>  | Open Drain Output Low<br>Voltage                | $I_{OL} = 4 \text{ mA}$                                                    | 0    |      | 0.4  | V    |  |

| т.                   | Officely as automat                             | V <sub>DD</sub> =0, V <sub>IN</sub> =3.6V                                  |      |      | 20   |      |  |

| I <sub>OFF_HPD</sub> | Off leakage current                             | $V_{\mathrm{DD}}$ =0, $V_{\mathrm{IN}}$ =5.5 $V$                           |      |      | 40   | ] ^  |  |

| Iog von              | Open drain Output leak-                         | $V_{\rm DD}$ =3.6, $V_{\rm IN}$ =3.6 $V$                                   |      |      | 20   | μA   |  |

| I <sub>OZ_HPD</sub>  | age current                                     | $V_{\rm DD}$ =3.6, $V_{\rm IN}$ =5.5 $V$                                   |      |      | 40   |      |  |

08/30/12

### HPD\_SINK

| Symbol            | Parameter                        | Conditions           | Min. | Тур. | Max. | Units |

|-------------------|----------------------------------|----------------------|------|------|------|-------|

| $I_{IH}$          | High level digital input current | V <sub>IH</sub> =VDD | 25   |      | 40   | μΑ    |

| $I_{IL}$          | Low level digital input current  | $V_{IL} = GND$       | -10  |      | 10   | μΑ    |

| $V_{IH}$          | High level digital input voltage | $V_{\rm DD} = 3.3 V$ | 2.0  |      |      | V     |

| $V_{\mathrm{IL}}$ | Low level digital input voltage  |                      | 0    |      | 0.8  | V     |

### **Control Pin (OEB)**

| Symbol       | Parameter                        | Conditions     | Min. | Тур. | Max. | Units |

|--------------|----------------------------------|----------------|------|------|------|-------|

| $I_{IH}$     | High level digital input current | $V_{IH} = VDD$ | 30   |      | 45   | μΑ    |

| $I_{IL}$     | Low level digital input current  | $V_{IL} = GND$ | -10  |      | 10   | μΑ    |

| $V_{IH}$     | High level digital input voltage |                | 2.0  |      |      | V     |

| $V_{\rm IL}$ | Low level digital input voltage  |                | 0    |      | 0.8  | V     |

#### **DDC Channel Block**

| Symbol                | Parameter                         | Conditions                                                                           | Min.                | Тур. | Max. | Units |

|-----------------------|-----------------------------------|--------------------------------------------------------------------------------------|---------------------|------|------|-------|

| $I_{LK}$              | Input leakage current             | DDC switch is off                                                                    | -10                 |      | 40   | μΑ    |

| C <sub>IO</sub>       | Input/Output capacitance          | V <sub>I</sub> peak-peak = 1V, 100 KHz                                               |                     | 10   |      | pF    |

| R <sub>ON</sub>       | On resistance                     | $I_O = 3 \text{ mA}, V_O = 0.4 \text{ V}$                                            |                     | 25   | 50   | Ω     |

| V <sub>pass</sub>     | Switch Output voltage             | V <sub>I</sub> =3.3V, I <sub>I</sub> =100 uA<br>V <sub>DD</sub> =3.3V                | 1.5                 | 2.0  | 2.5  | V     |

| VOH_DDC (source/sink) | DDC Switch Output High<br>Voltage | $V_{IN}$ =3.3V. External pull-up Rup to $V_{DD}$ from 1.5 K $\Omega$ to 5 K $\Omega$ | V <sub>DD</sub> - 1 |      |      | V     |

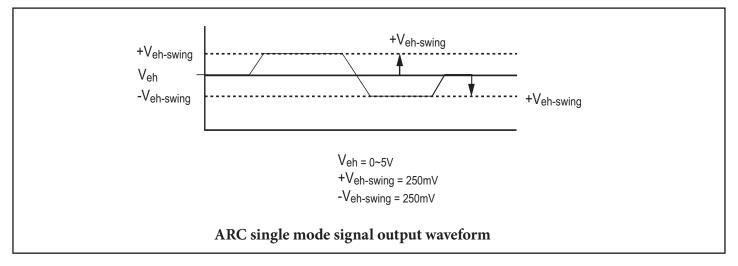

#### SPDIF & ARC Pins, See ARC single mode waveform

| Symbol                | Parameter                                        | Conditions                       | Min. | Typ. | Max. | Units |

|-----------------------|--------------------------------------------------|----------------------------------|------|------|------|-------|

| I <sub>IH_SPDIF</sub> | High level input current                         | $VDD = 3.6V, V_{IH} = 3.6V$      |      | 500  |      | μΑ    |

| I <sub>IL_SPDIF</sub> | Low level input current                          | $VDD = 3.6V, V_{IL} = GND$       |      | -350 |      | μΑ    |

| Vel                   | Single mode input/output<br>Vel DC voltage level |                                  | 0    |      | 5.0  | V     |

| Vel swing SPDIF       | Single mode input swing                          |                                  | 0.2  |      | 0.6  | V     |

| Vel swing ARC_<br>OUT | Single mode ARC output swing                     |                                  | 0.4  | 0.5  | 0.6  | V     |

| RO                    | Output resistance of ARC output stage            |                                  |      | 55   |      | Ω     |

| t <sub>r</sub>        | ARC output rise time (10% to 90%)                | $< 0.4UI (f_{clock} = 6.144MHz)$ |      |      | 25   | ns    |

| $t_{f}$               | ARC output fall time (10% to 90%)                | $< 0.4UI (f_{clock} = 6.144MHz)$ |      |      | 25   | ns    |

| $T_{Jpp}$             | ARC signal peak to peak jitter                   | $< 0.4UI (f_{clock} = 6.144MHz)$ |      |      | 3    | ns    |

#### **TMDS Differential Pins**

| Symbol               | Parameter                                                       | Conditions                           | Min.                 | Тур. | Max.                 | Units |

|----------------------|-----------------------------------------------------------------|--------------------------------------|----------------------|------|----------------------|-------|

| V <sub>OH</sub>      | Single-ended high level output voltage                          |                                      | V <sub>DD</sub> -10  |      | V <sub>DD</sub> +10  | mV    |

| V <sub>OL</sub>      | Single-ended low level output voltage                           |                                      | V <sub>DD</sub> -600 |      | V <sub>DD</sub> -400 | mV    |

| V <sub>swing</sub>   | Single-ended output swing voltage                               | V 2.2V D                             | 400                  |      | 600                  | mV    |

| V <sub>OD(O)</sub>   | Overshoot of output differential voltage <sup>1</sup>           | $V_{DD} = 3.3V$ , Rout $= 50 \Omega$ |                      |      | 180                  | mV    |

| V <sub>OD(U)</sub>   | Undershoot of output differential voltage <sup>2</sup>          |                                      |                      |      | 200                  | mV    |

| V <sub>OD(U)</sub>   | Change in steady-state common-mode output voltage between logic |                                      |                      |      | 5                    | mV    |

|                      | Short Circuit output current                                    |                                      | -12                  |      | 12                   | mA    |

| I <sub>OS</sub>      | Short Circuit output current at double termination mode         |                                      | -24                  |      | 24                   | mA    |

| V <sub>I(open)</sub> | Single-ended input voltage under high impedance input or open   | $I_{I} = 10uA$                       | V <sub>DD</sub> -10  |      | V <sub>DD</sub> +10  | mV    |

| R <sub>T</sub>       | Input termination resistance                                    | $V_{IN} = 2.9V$                      | 45                   | 50   | 55                   | Ω     |

| I <sub>OZ</sub>      | Leakage current with Hi-Z I/O                                   | $V_{\rm DD} = 3.6 \text{V},$         |                      |      | 10                   | μΑ    |

#### Note:

- 1. Overshoot of output differential voltage  $V_{\rm OD(O)}$  =  $(V_{\rm SWING(MAX)}*2)*15\%$

- 2. Undershoot of output differential voltage  $V_{\rm OD(O)}$  =  $(V_{\rm SWING(MIN)} * 2) * 25\%$

## AC Characteristics (Over recommended operating conditions unless otherwise noted)

#### **TMDS Differential Pins**

| Symbol               | Parameter                                          | Conditions                     | Min. | Typ. | Max. | Units |

|----------------------|----------------------------------------------------|--------------------------------|------|------|------|-------|

| t <sub>pd</sub>      | Propagation delay                                  |                                |      |      | 2000 |       |

| t <sub>r</sub>       | Differential output signal rise time (20% - 80%)   | $V_{DD}$ = 3.3V, Rout = 50 Ohm |      |      | 190  |       |

| $t_{\mathrm{f}}$     | Differential output signal fall time (20% - 80%)   |                                |      |      | 190  |       |

| t <sub>sk(p)</sub>   | Pulse skew                                         |                                |      | 10   | 50   |       |

| t <sub>sk(D)</sub>   | Intra-pair differential skew                       |                                |      | 23   | 50   | ps    |

| t <sub>sk(o)</sub>   | Inter-pair differential skew                       |                                |      |      | 100  |       |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter<br>CLK residual jitter  | CLK Input = 165 MHz            |      | 15   | 30   |       |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter<br>DATA Residual Jitter |                                |      | 18   | 50   |       |

| t <sub>SX</sub>      | Select to switch output                            |                                |      |      | 10   | 1     |

| t <sub>en</sub>      | Enable time                                        |                                |      |      | 1000 | ns    |

| t <sub>dis</sub>     | Disable time                                       |                                |      |      | 10   | ns    |

#### DDC I/O Pins (SCL, SCL\_SINK, SDA, SDA\_SINK)

| Symbol               | Parameter         | Conditions                  | Min. | Typ. | Max. | Units |

|----------------------|-------------------|-----------------------------|------|------|------|-------|

| t <sub>pd(DDC)</sub> | Propagation Delay | $C_{\rm L} = 10 \text{ pF}$ |      | 0.4  | 2.5  | ns    |

### Control and Status Pins (HPD\_SINK, HPD)

| Symbol               | Parameter               | Conditions                | Min. | Тур. | Max. | Units |

|----------------------|-------------------------|---------------------------|------|------|------|-------|

| t <sub>pd(HPD)</sub> | Propagation Delay       | $C_L = 10 \text{ pF},$    |      | 10   |      | ns    |

| t <sub>sx(HPD)</sub> | Select to switch output | Pull-up resistor = 1 KOhm |      | 10   |      | ne    |

|                      | Select to switch output | Open drain output         |      | 10   |      | ns    |

## Packaging Mechanical: 48-contact LQFP (FB)

09-0012

Please check for the latest package information on the Pericom web site at www.pericom.com/packaging/

08/30/12

08/30/12

### **Related Products**

| Part Number                                                                                         | Product Description                                                                                    |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| PI3EQXDP1201                                                                                        | DisplayPort 1.2 Re-driver with built-in AUX listener                                                   |

| PI3VDP1430 Dual Mode DisplayPort to HDMI Level Shifter and Re-driver                                |                                                                                                        |

| PI3HDMI511 3.4Gbps HDMI 1.4 Re-driver for Source-side application, supporting Dual Mode DisplayPort |                                                                                                        |

| PI3HDMI611 3.4Gbps HDMI 1.4 Re-driver for Sink-side application, supporting Dual Mode DisplayPort   |                                                                                                        |

| PI3VDP3212 2-Lane DisplayPort 1.2 Compliant Switch                                                  |                                                                                                        |

| PI3VDP12412 4-Lane DisplayPort 1.2 Compliant Switch                                                 |                                                                                                        |

| PI3HDMI412AD 1:2 Active 3.4Gbps HDMI 1.4 compliant Splitter/Re-driver                               |                                                                                                        |

| PI3HDMI621                                                                                          | 2:1 Active 3.4Gbps HDMI 1.4 Switch with built-in ARC and Fast Switching support for sink-side Applica- |

| PI3HDWH021                                                                                          | tion                                                                                                   |

| PI3HDMI336                                                                                          | 3:1 Active 3.4Gbps HDMI 1.4 Switch/Re-driver with I <sup>2</sup> C control and ARC Transmitter         |

### **Reference Information**

| Document | Description                                                                                                         |

|----------|---------------------------------------------------------------------------------------------------------------------|

|          | VESA DisplayPort Standard Version 1 Revision 2, Video Electronics Standards Association, January 5, 2010            |

| VESA     | VESA DisplayPort Dual-Mode Standard Version 1, Video Electronics Standards Association, February 10, 2012           |

|          | VESA DisplayPort Interoperability Guideline Version 1.1a, Video Electronics Standards Association, February 5, 2009 |

| HDMI     | High-Definition Multimedia Interface Specification Version 1.4, HDMI Licensing, LLC, June 5, 2009                   |

# **Ordering Information**

| Ordering Number | Package Code | Package Description             |

|-----------------|--------------|---------------------------------|

| PI3HDMI521FBE   | FB           | Pb-free & Green 48-Contact LQFP |

$<sup>\</sup>bullet \ Thermal\ characteristics\ can\ be\ found\ on\ the\ company\ web\ site\ at\ www.pericom.com/packaging/$

- E = Pb-free and Green

- X suffix = Tape/Reel

## PI3HDMI521

2:1 Active HDMI™1.4 Source-side Switch with Integrated ARC and Fast Switching Support

# **Revision History**

| Date | Changes |

|------|---------|

|      |         |

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Video ICs category:

Click to view products by Diodes Incorporated manufacturer:

Other Similar products are found below:

M21328G-12 TW2964-LA2-CR TW9903-FB TW9919-PE1-GR ADV8003KBCZ-7T PI3HDX511DZLEX M23428G-33

PI7VD9008ABHFDE ADV7186BBCZ-TL ADV7186BBCZ-T-RL ADV8003KBCZ-7C PI3VDP411LSAZBEX PI3VDP411LSTZBEX

M23145G-14 PI3VDP411LSRZBEX BH76912GU-E2 CM5100-01CP ADV7181DBCPZ-RL TVP5160PNP TVP5151PBSR BA7603F-E2

LMH1208RTVT BH76106HFV-TR BH76206HFV-TR ADV7179WBCPZ ADV7611BSWZ-P-RL ADV7180KCP32Z ADV7180WBCP32Z

ADV7280KCPZ ADV7280WBCPZ-M ADV7281WBCPZ-MA ADV7283WBCPZ ADV7283BCPZ ADV7282WBCPZ-M ADV7280KCPZ-M ADV7280WBCPZ-RL ADV7180KCP32Z-RL ADV7180BCP32Z-RL ADV7180WBCPZ-ADV7182AWBCPZ ADV728ARUZ

ADV7611BSWZ ADV7181DWBCPZ-RL ADV7173KSTZ-REEL ADV7180WBST48Z-RL ADA4411-3ARQZ ADA4411-3ARQZ ADA4411-3ARQZ-R7

ADA4417-3ARMZ ADA4417-3ARMZ-R7 ADA4424-6ARUZ