# HDMI 1.4B 1:2 Active Splitter/Demux for 3.4Gbps Data Rate with Equalization and Pre-emphasis

### **Description**

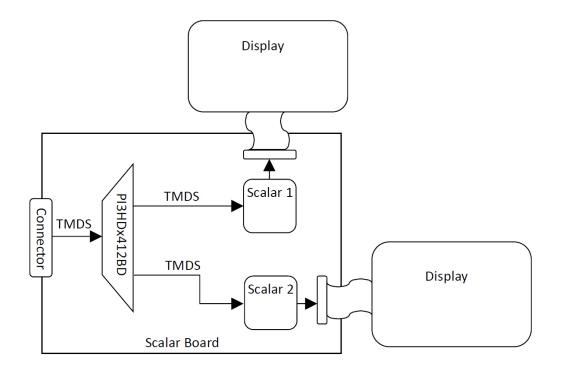

PI3HDX412BD, active-drive switch solution is targeted for high-resolution video networks that are based on  ${\rm HDMI}^{\rm TM}/{\rm DVI}$  standards, and TMDS signal processing.

The PI3HDX412BD is an active single TMDS channel to two TMDS channel Splitter and DeMux with Hi-Z outputs. The device drives differential signals to multiple video display units.

It provides controllable output swing levels that can be controlled through pin control or I2C control, depending on the mode select pin. This solution also provides a unique advanced pre-emphasis technique to increase rise and fall times.

The maximum HDMI<sup>TM</sup>/DVI data rate of 3.4Gbps provides 1920x1080 @60Hz resolution or 4K @30Hz required for 4K HDTV and PC graphics products. Due to its active uni-directional feature, this switch is designed for usage only for the video driver's side. For PC graphics application, the device sits at the driver's side to switch between multiple display units, such as PC LCD monitor, projector, TV, etc.

PI3HDX412BD ensures transmitting high bandwidth video streams from PC graphics source to end display units. It will also provide enhanced robust ESD/EOS protection, which is required by many consumer video networks today.

### **Features**

- Support up to 3.4Gbps TMDS Serial Link Compliant with HDMI 1.4b requirement

- Data rate per channel support 4096 x 2160 pixel resolution, color 8-bit YCbCr 4:2:0 format.

- HDMI 1:2 Splitter-mode or 1:2 DeMux-mode with Equalization & Pre-emphasis up to 340 MHz Clock

- AC or DC-coupled Differential Signal Input for TMDS and DP++

- Configurable TMDS Output Signal with Port Selection, Pre-emphasis, Voltage Swing, Slew Rate Control with I2C control mode

- Support TMDS power-down Squelch Mode with Built-in Clock detector

- Control Status Register controlled by Pin strap or I<sup>2</sup>C mode programming

- ESD Protection on I/O pins to connector: 8KV Contact per IEC6100-4-2 and 2KV HBM

- Supply Voltage: 3.3V

- Industrial Temperature Range: -40°C to 85°C

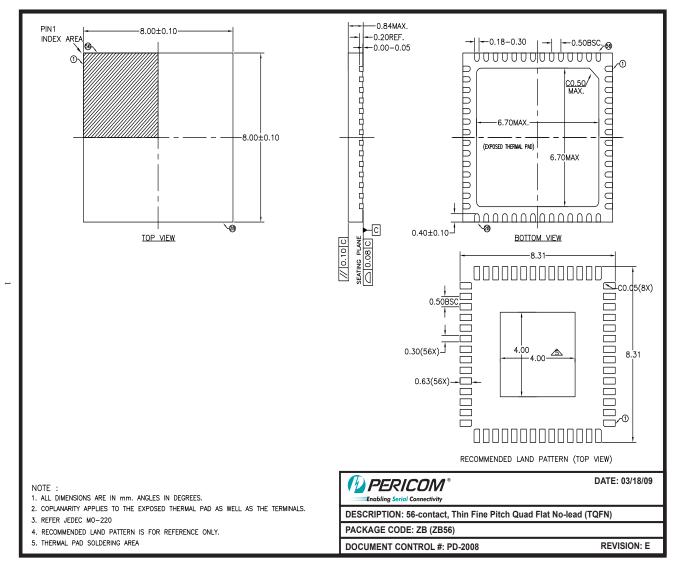

- Packaging (Pb-free & Green): 56-contact TQFN (ZB56)

### **Applications**

- Display Peripheral Box

- Digital Signage Display

- Video Processing Devices

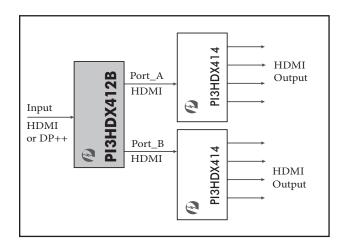

**Application Block Diagram**

### **Ordering Information**

| Ordering<br>Code    | Package<br>Code | Package Description                             |

|---------------------|-----------------|-------------------------------------------------|

| PI3HDX412BD<br>ZBEX | ZB              | 56-pin, Pb-free & Green TQFN,<br>Tape/Reel Type |

Suffix: E = Pb-free and Green, X = Tape/Reel Type

## **Revision History**

| Version  | Changes                                |

|----------|----------------------------------------|

| Feb 2014 | Release                                |

| Oct 2016 | Add Diodes company logo and Disclaimer |

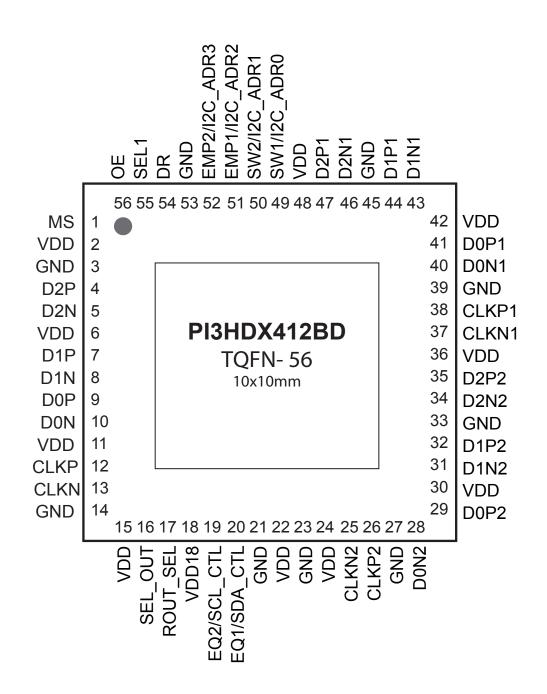

Package Pin-out

PI3HDX412BD Package & Pinout

### TMDS In/Out Pin Assignment

| Pin # | Pin Name         | Type                                                                                                                                                                                                                                                                                                 | Description                                                                 |  |  |  |  |  |

|-------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| 4     | D2P              | I                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 5     | D2N              | I Input Port. TMDS Clock and Data Input pins. When Input Termination Resist 50 Ohm) tied to VDD or GND, Rpd=200 kOhm shall be "OFF" state.  I I I2C registers can control Rt and Rpd ON/OFF state.  I I O O O O O O O O O Termination Resistor (Rout=50 Ohm).  O O O O O O O O O O O O O O O O O O O |                                                                             |  |  |  |  |  |

| 7     | D1P              | I                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 8     | D1N              | Input Port. TMDS Clock and Data Input pins. When Input Termination Resistor 50 Ohm) tied to VDD or GND, Rpd=200 kOhm shall be "OFF" state.  I                                                                                                                                                        |                                                                             |  |  |  |  |  |

| 9     | D0P              |                                                                                                                                                                                                                                                                                                      |                                                                             |  |  |  |  |  |

| 10    | D0N              |                                                                                                                                                                                                                                                                                                      | 120 registers can control it and topa of 1,011 state.                       |  |  |  |  |  |

| 12    | CLKP             |                                                                                                                                                                                                                                                                                                      |                                                                             |  |  |  |  |  |

| 13    | CLKN             | I                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 25    | CLKN2            | О                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 26    | CLKP2            | О                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 28    | D0N2 O<br>D0P2 O | О                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 29    | D0P2             | О                                                                                                                                                                                                                                                                                                    | Output Port 2. TMDS Clock and Data Output pins. ROUT_SEL pin enables Output |  |  |  |  |  |

| 31    | D1N2             | O Output Port 2. TMDS Clock and Data Output pins. ROUT_SEL pin en O Termination Resistor (Rout=50 Ohm).                                                                                                                                                                                              | Termination Resistor (Rout=50 Ohm).                                         |  |  |  |  |  |

| 32    | D1P2             | О                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 34    | D2N2             | О                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 35    | D2P2             | О                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 37    | CLKN1            | О                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 38    | CLKP1            | О                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 40    | D0N1             | О                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 41    | D0P1             | O Output Port 1. TMDS Clock and Data Output pins. ROUT_SEL pin enables Output Termination Resistor (Rout=50 Ohm).                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 43    | D1N1             |                                                                                                                                                                                                                                                                                                      |                                                                             |  |  |  |  |  |

| 44    | D1P1             | О                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 46    | D2N1             | О                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

| 47    | D2P1             | О                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |

Note: In TMDS Data and Clock Differential Pair, the polarity +/- (or P/N) of each pair can use interchangeably. When input TMDS Input Clock polarity +/- pin swaps, output TMDS Clock of port 1 and port 2 shall swapped accordingly.

### **Control Pins**

| Pin#                 | Pin Name                                                       | Type | Description                                                                                                                                                                                                                                                                                                                                                   | •                                                                                                                           |                                                      |                    |       |  |  |  |

|----------------------|----------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------|-------|--|--|--|

|                      |                                                                | I    | Mode Selection Pin. Internal pull-up at 100K Ohm.                                                                                                                                                                                                                                                                                                             |                                                                                                                             |                                                      |                    |       |  |  |  |

| 1                    | MS                                                             |      | "High" : I <sup>2</sup> C Control Mode Selection                                                                                                                                                                                                                                                                                                              |                                                                                                                             |                                                      |                    |       |  |  |  |

|                      |                                                                |      | "Low": Pin Cont                                                                                                                                                                                                                                                                                                                                               | rol Mode Selection                                                                                                          | n                                                    |                    |       |  |  |  |

| 19<br>20             | EQ2/SCL_CTL<br>EQ1/SDA_CTL                                     | IO   | Pin#1 MS sets "H<br>Pin#1 MS sets "L<br>Internally Pull-U                                                                                                                                                                                                                                                                                                     | pin or I <sup>2</sup> C Clock to 400 Kbps.  (igh": Pin#19 assign pat 100 Kohm and etting table is show  EQ2  (Pin#19)  0  M | ns to SCL_CTL p<br>ns to EQ2 pin<br>d Pull-Down at 1 | 00 Kohm.           | Z-Bus |  |  |  |

|                      |                                                                |      | "Low"                                                                                                                                                                                                                                                                                                                                                         | M 1                                                                                                                         | M<br>0<br>M                                          | 12.5<br>15<br>17.5 |       |  |  |  |

|                      |                                                                |      |                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                           | 1                                                    | 20                 |       |  |  |  |

| 49<br>50<br>51<br>52 | SW1/I2C_ADR0<br>SW2/I2C_ADR1<br>EMP1/I2C_ADR2<br>EMP2/I2C_ADR3 | I    | Shared Pin. SW or EMP or I2C_ADR pins.  When Pin#1 MS="High": These Shared Pins assign to I2C_ADR[3:0] When Pin#1 MS="Low": These Shared Pins assign to SW1/2 and EMP1/2  These SW2 and SW1 pins control output voltage swing adjustment as follow: These SW pins have internal Pull-Up 100K Ohm.  SW2 (Pin#50) SW1 (Pin#49) Output Voltage Swing  0 0 500 mV |                                                                                                                             |                                                      |                    |       |  |  |  |

|                      |                                                                |      | 0                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                           | -10 %                                                |                    |       |  |  |  |

|                      |                                                                |      | 1                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                           | +10 %                                                |                    |       |  |  |  |

|                      |                                                                |      | 1                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                           | +20 %                                                |                    |       |  |  |  |

| Pin# | Pin Name                      | Type | Description                                                                                                                                                                                  | Description       |                                                                                  |     |  |  |

|------|-------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------|-----|--|--|

|      |                               |      | EMP2 and EMP1 pins control output voltage pre-emphasis. These pins have internally Pull-Up 100 Kohm.                                                                                         |                   |                                                                                  |     |  |  |

| 49   | 50<br>51<br>(Continued)<br>52 |      | EMP2 (Pin#52)                                                                                                                                                                                | EMP1 (Pin#51)     | Pre-emphasis Setting (dB)                                                        |     |  |  |

| 50   |                               | I    | 0                                                                                                                                                                                            | 0                 | 0                                                                                |     |  |  |

|      |                               |      | 0                                                                                                                                                                                            | 1                 | 1.5                                                                              |     |  |  |

| 52   |                               |      | 1                                                                                                                                                                                            | 0                 | 2.5                                                                              |     |  |  |

|      |                               |      | 1                                                                                                                                                                                            | 1                 | 3.5                                                                              |     |  |  |

| 56   | OE                            | I    | Output Enable Control pin. Internally pull-up at 100 Kohm.  "High": Output Port Enable "Low": Turn off Rout and Rt(termination resistor). TMDS Receiver and TMDS On Drivers are "OFF" state. |                   |                                                                                  |     |  |  |

| 54   | DR                            | I    | Direction Control pin  "High": All ports are Active at same time  "Low": Output Ports are controlled by SEL1 (Pin#55) control                                                                |                   |                                                                                  |     |  |  |

| 55   | SEL1                          | I    | Port 1 or Port 2 O  "High": Enable O  "Low": Enable Ov                                                                                                                                       | utput Port 2      | ction pin. Internal pull-up at 100 Kc                                            | hm. |  |  |

| 16   | SEL_OUT                       | 0    | Offset 0x00 Bit[5]                                                                                                                                                                           | ="1" : Enable Out | 0x00 Bit[5] can control this pin statu<br>put Port 1 Output<br>put Port 1 Output | is. |  |  |

| 17   | ROUT_SEL                      | I    | "High" : Source Te                                                                                                                                                                           | ermination Outpu  | t (Rout) Resistor is "ON", connect to  (Rout) Resistor is "OFF". Open-Dra        | -   |  |  |

#### Power/Ground Pins

| Pin #        | Pin Name | Type   | Description                                                                     |

|--------------|----------|--------|---------------------------------------------------------------------------------|

| 18           | VDD18    | Power  | LDO Output Pin for internal core supplier. Add external 4.7 uF capacitor to GND |

| 3,14,21,23,  |          |        |                                                                                 |

| 27,33,39,45, | GND      | Ground | Ground Pins                                                                     |

| 53, ePad     |          |        |                                                                                 |

| 2,6,11,15,   |          |        |                                                                                 |

| 22,24,30,36, | VDD      | Power  | 3.3V Power Supply                                                               |

| 42,48        |          |        |                                                                                 |

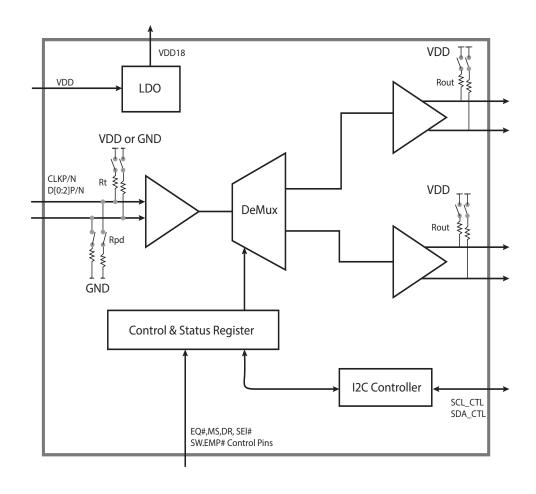

### **Block Diagram**

### **Functional Description**

### **Squelch Mode:**

Output Disable (Squelch) Mode uses TMDS Clock channel signal detection. When low voltage levels on the TMDS input clock signals are detected, Squelch state enables and TMDS output port signals shall disable; when the TMDS clock input signal levels are above a pre-determined threshold voltage, output ports shall return to the normal voltage swing levels.

When enable Squelch mode, input termination resistor will be enabled together. When Squelch is disabled through I2C register programming RX\_SET[1]="1" and no TMDS input signal condition, TMDS D[0:2]P/N will be undetermined status. In Squelch state, TMDS output is high impedance state or TMDS output port shall 50 Ohm pull-up at source termination output.

#### **Function Control Table**

| OE        | MS        | DR | SEL2 | SEL1 | HDMI Outputs         | HPD_SRC Function (with external 1 Kohm Pull-up resistor) |

|-----------|-----------|----|------|------|----------------------|----------------------------------------------------------|

| 0         | X         | X  | X    | X    | All Port Disable     | 0                                                        |

| Pin Cotro | ol Mode   |    |      |      |                      |                                                          |

| 1         | 0         | 1  | X    | X    | All Ports Enable     | (HPD1+HPD2+HPD3+HPD4)                                    |

| 1         | 0         | 0  | 0    | 0    | Enable Port 1        | HPD1                                                     |

| 1         | 0         | 0  | 0    | 1    | Enable Port 2        | HPD2                                                     |

| I2C Cont  | trol Mode |    |      |      |                      |                                                          |

| 1         | 1         | X  | X    | x    | I2C Programming Mode | ( HPD1 * Port1 EN + HPD2 * Port2 EN )                    |

#### HPD Control Mode

| TMDS Selection (Input) | HPDx(Input) | Description         | Notes                                    |

|------------------------|-------------|---------------------|------------------------------------------|

| Port[x] Select         | 1           | Port[x] is enabled  |                                          |

| Port[x] Select         | 0           | Port[x] is Disabled | 1) x=1, 2. x is consistent for one port. |

## I<sup>2</sup>C Register Control Programming

### **I2C Register Control**

| Pin Name                  | I/O | Description                                                      |

|---------------------------|-----|------------------------------------------------------------------|

| SCL_CTL                   | I   | I2C Clock, compatible with I2C-bus specification, up to 400 kb/s |

| SDA_CTL                   | IO  | I2C Data, compatible with I2C-bus specification, up to 400 kb/s  |

| I2C_ADR[3:0]              | I   | I2C Control Address Setting                                      |

| Byte output : 0x00 - 0x07 | О   | I2C Control registers output                                     |

## I<sup>2</sup>C Address Byte

|              | b[7]<br>MSB | b[6] | b[5] | b[4] | b[3] | b[2] | b[1] | b[0]<br>(R/W) |

|--------------|-------------|------|------|------|------|------|------|---------------|

| Address Byte | 1           | 0    | 1    | A3   | A2   | A1   | A0   | 1/0*          |

Note: Read "1", Write "0"

| Offset | Name                                                                                                                                                                                                                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                           | Power Up<br>Condition | Туре |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|

| 0x00   | CONFIG[7:0]                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li>[7] Enable TMDS Standby mode.  In standby mode, TMDS equalizer and output driver shall power down.  "0": Standby mode  "1": Normal mode</li> <li>[6] Reserved</li> <li>[5] Output TMDS Port 1 Select  "0": Disable  "1": Enable</li> <li>[4] Output TMDS Port 2 Selected  "0": Disable  "1": Enable</li> <li>[3] Reserved</li> <li>[2:0] Reserved</li> </ul> | 0xFF                  | R/W  |

|        | TMDS Receiver Equalization Setting Registers  [7] Disable Input Port input termination resistors  "0": Enable Rpd connection  "1": Disable Rpd connection  [6] TMDS Input termination V-bias selection  "0": Connect to GND  "1": Connect to VDD  [5] V-bias register selection enable  "0": bit[6] control disable  "1": bit[6] control enable  [4:2] EQ programmable setting |                                                                                                                                                                                                                                                                                                                                                                       |                       |      |

|        |                                                                                                                                                                                                                                                                                                                                                                                | b[4:2] EQ Setting (dB)                                                                                                                                                                                                                                                                                                                                                |                       |      |

| 0.03   | DW ODES 01                                                                                                                                                                                                                                                                                                                                                                     | 000 2.5                                                                                                                                                                                                                                                                                                                                                               | 0.00                  | D/M  |

| 0x01   | RX_SET[7:0]                                                                                                                                                                                                                                                                                                                                                                    | 001 5                                                                                                                                                                                                                                                                                                                                                                 | 0x00                  | R/W  |

|        |                                                                                                                                                                                                                                                                                                                                                                                | 010 7.5                                                                                                                                                                                                                                                                                                                                                               |                       |      |

|        |                                                                                                                                                                                                                                                                                                                                                                                | 011 10                                                                                                                                                                                                                                                                                                                                                                |                       |      |

|        |                                                                                                                                                                                                                                                                                                                                                                                | 100 12.5                                                                                                                                                                                                                                                                                                                                                              |                       |      |

|        |                                                                                                                                                                                                                                                                                                                                                                                | 101 15                                                                                                                                                                                                                                                                                                                                                                |                       |      |

|        |                                                                                                                                                                                                                                                                                                                                                                                | 110 17.5                                                                                                                                                                                                                                                                                                                                                              |                       |      |

|        |                                                                                                                                                                                                                                                                                                                                                                                | [1] Squelch Control Bit                                                                                                                                                                                                                                                                                                                                               |                       |      |

|        |                                                                                                                                                                                                                                                                                                                                                                                | "0": Squelch enable                                                                                                                                                                                                                                                                                                                                                   |                       |      |

|        |                                                                                                                                                                                                                                                                                                                                                                                | "1": Squelch disable [0] Reserved                                                                                                                                                                                                                                                                                                                                     |                       |      |

| 0x02   | Reserved                                                                                                                                                                                                                                                                                                                                                                       | [7:0] Reserved                                                                                                                                                                                                                                                                                                                                                        | 0x00                  | R/W  |

| Offset       | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Power Up<br>Condition | Туре       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------|

| 0x03         | TX_SET[7:0] for port1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TMDS Port 1 Output setting  [7] TMDS output control  "0": Open drain  "1": Double termination  [6:4] TMDS output Pre-emphasis control  "000": 0 dB  "001": 1.5 dB  "010": 2.5 dB  "011": 3.5 dB  "1xx": 6 dB (750 mVpp swing)  [3:2] Reserved by test only  TMDS output swing setting  "00": 500 mV as default  "01": -10%  "10": +10%  "11": +20%  [1:0] Reserved by test adjust  TMDS output slew rate setting  "00": as default  "01" / "10": +5%  "11": +10%                          | 0x00                  | R/W        |

| 0x04         | TX_SET[7:0] for port2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TMDS Port 2 Output setting  [7] TMDS output control  "0": Open drain  "1": Double termination  [6:4] TMDS output Pre-emphasis control  "000": 0 dB  "001": 1.5 dB  "010": 2.5 dB  "011": 3.5 dB  "1xx": 6 dB ( 750 mVpp swing)  [3:2] Reserved by test only  TMDS output swing setting  "00": 500 mV as default setting  "01": -10%  "10": +10%  "11": +20%  [1:0] Reserved by test adjust  TMDS output slew rate setting  "00": Default setting  "00": Default setting  "01" / "10": +5% | 0x00                  | R/W        |

|              | The second secon | "11": +10%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |            |

| 0x05         | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | [7:0] Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x00                  | R/W        |

| 0x05<br>0x06 | Reserved Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x00<br>0x0F          | R/W<br>R/W |

12

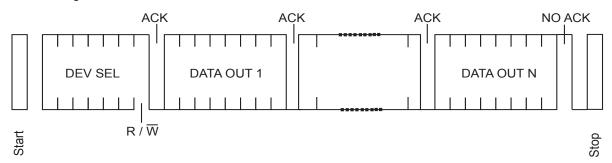

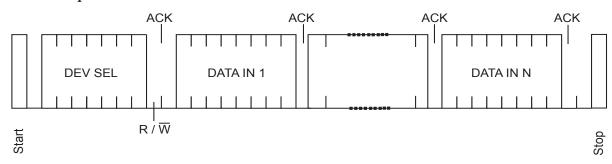

### I<sup>2</sup>C Data Transfer

### 1. Read Sequence

### 2. Write Sequence

## **Absolute Maximum Ratings**

| Supply Voltage to Ground Potential | 4.5V                           |

|------------------------------------|--------------------------------|

| DC SIG Voltage                     | $\dots -0.5V$ to $V_{DD}+0.5V$ |

| Storage Temperature                | 65°C to +150°C                 |

| Operating Temperature              | 40 to +85°C                    |

Note:

Stresses greater than those listed under MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Thermal Characteristics**

| Symbol          | Parameter                               | Ratings | Units |

|-----------------|-----------------------------------------|---------|-------|

| $T_{Jmax}$      | Junction Temperature                    | 125     | °C    |

| $R_{	heta JC}$  | Thermal Resistance, Junction to Case    | 5       | °C/W  |

| $R_{\theta JA}$ | Thermal Resistance, Junction to Ambient | 24      |       |

## **Electrical Characteristics** T<sub>J</sub>=25 °C unless otherwise noted

### **DC Specifications**

| Symbol            | Parameter                                                                      | Test<br>Conditions         | Min.    | Тур. | Max.    | Units |

|-------------------|--------------------------------------------------------------------------------|----------------------------|---------|------|---------|-------|

| $V_{\mathrm{DD}}$ | Operation Voltage                                                              |                            | 3.0     | 3.3  | 3.6     | V     |

| $I_{DD}$          | VDD Supply Current                                                             |                            |         | 250  | 290     | mA    |

| $I_{DDQ}$         | VDD Quiescent Current                                                          | OE = 1, No<br>input signal |         | 50   | 80      | mA    |

| I <sub>STB</sub>  | Standby mode                                                                   | OE = 0                     |         | 1    | 5       | mA    |

| TMDS Diffe        | erential Pins                                                                  |                            |         |      |         |       |

| V <sub>OH</sub>   | Single-ended high level output voltage                                         | VDD = 3.3  V, Rout=50 Ω    | VDD-10  |      | VDD+10  | mV    |

| VOL               | Single-ended low level output voltage                                          |                            | VDD-600 |      | VDD-400 | mV    |

| Vswing            | Single-ended output swing voltage                                              |                            | 400     |      | 600     | mV    |

| VOD(O)            | O(O) Overshoot of output differential voltage                                  |                            |         |      | 180     | mV    |

| VOD(U)            | U) Undershoot of output differential voltage 2                                 |                            | 200     | mV   |         |       |

| VOC(SS)           | OC(SS) Change in steady-state common- mode output voltage between logic states |                            |         |      | 5       | mV    |

| IOS               | Short Circuit output current                                                   |                            | -12     |      | 12      | mA    |

| IOS               | Short Circuit output current at double termination mode                        |                            | -24     |      | 24      | mA    |

| VI(open)          | Single-ended input voltage under high impedance input or open input            | IL = 10 uA                 | VDD-10  |      | VDD+10  | mV    |

| Symbol          | Parameter                                         | Test<br>Conditions               | Min. | Тур. | Max. | Units |

|-----------------|---------------------------------------------------|----------------------------------|------|------|------|-------|

| RT              | Input termination resistance                      | VIN = 2.9 V                      | 45   | 50   | 55   | Ohm   |

| IOZ             | Leakage current with Hi-Z I/O                     | VDD = 3.6 V,<br>OE = 0           |      | 30   | 100  | μΑ    |

| Control pins    | Control pins (OE, SEL1, EMP2, EMP1, SW2, SW1, MS) |                                  |      |      |      |       |

| $I_{IH}$        | High level digital input current                  | V <sub>IH</sub> =V <sub>DD</sub> | -10  |      | 10   | μΑ    |

| I <sub>IL</sub> | Low level digital input current                   | $V_{IL} = GND$                   | -50  |      | 10   | μΑ    |

| $V_{IH}$        | High level digital input voltage                  |                                  | 2.4  |      |      | V     |

| $V_{\rm IL}$    | Low level digital input voltage                   |                                  | 0    |      | 0.8  | V     |

## **AC Specifications**

| Symbol             | Parameter                                                           | Test<br>Conditions             | Min. | Тур. | Max. | Units |

|--------------------|---------------------------------------------------------------------|--------------------------------|------|------|------|-------|

| tpd                | Propagation delay                                                   |                                |      |      | 2000 | ps    |

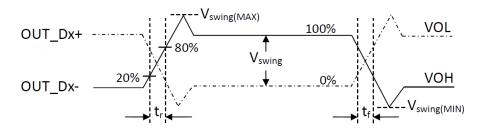

| t <sub>r</sub>     | Differential output signal rise time (20% - 80%), 0 dB / Open drain | VDD=3.3V,<br>ROUT=50 ohm       |      | 117  |      | ps    |

| $t_{\mathrm{f}}$   | Differential output signal fall time (20% - 80%), 0 dB / Open drain |                                |      | 117  |      | ps    |

| t <sub>sk(p)</sub> | Pulse skew                                                          |                                |      | 15   | 50   | ps    |

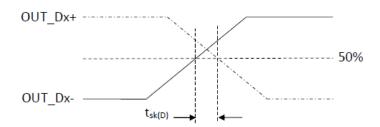

| t <sub>sk(D)</sub> | Intra-pair differential skew                                        |                                |      | 25   | 50   | ps    |

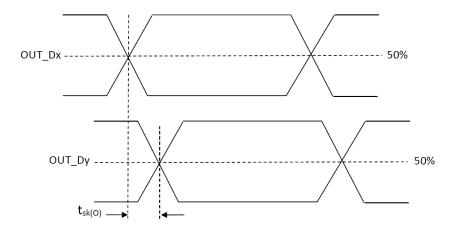

| t <sub>sk(O)</sub> | Inter-pair differential skew                                        |                                |      |      | 100  | ps    |

| t <sub>sx</sub>    | Select to switch output                                             |                                |      |      | 550  | ns    |

| t <sub>en</sub>    | Enable time                                                         |                                |      | 1    | 10   | us    |

| t <sub>dis</sub>   | Disable time                                                        |                                |      |      | 50   | ns    |

| tjit_clk(pp)       | Peak-to-peak output jitter CLK residual jitter                      | Data: 3.4 Gbps<br>data pattern |      | 10   |      | ps    |

| tjit_data(pp)      | Peak-to-peak output jitter Date residual jitter                     | Clock: 340 MHz                 |      | 28   |      | ps    |

15

<sup>1.</sup> Overshoot of output differential voltage  $V_{OD(O)} = (V_{SWING(MAX)} *2) * 15\%$ 2. Undershoot of output differential voltage  $V_{OD(O)} = (V_{SWING(MIN)} *2) * 25\%$

### **Inter-pair Skew Definition**

### **Intra-pair Skew Definition**

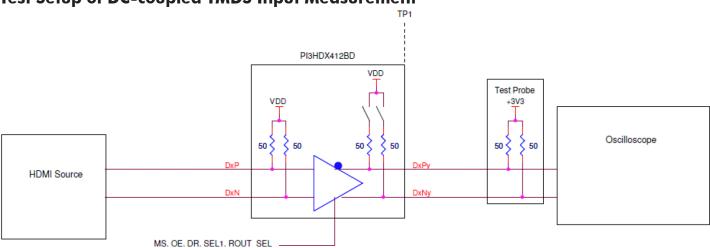

### **Test Setup of DC-coupled TMDS Input Measurement**

16

www.diodes.com

## Rise/Fall Time and Single-ended Swing Voltage

## **Typical Splitter Application**

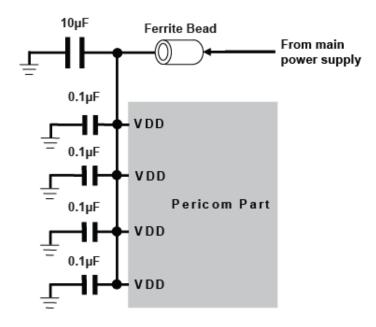

## **Power Supply Decoupling Circuit**

It is recommended to put 0.1  $\mu$ F decoupling capacitors on each VDD pins of our part, there are four 0.1  $\mu$ F decoupling capacitors are put in Figure 1 with an assumption of only four VDD pins on our part, if there is more or less VDD pins on our Pericom parts, the number of 0.1  $\mu$ F decoupling capacitors should be adjusted according to the actual number of VDD pins. On top of 0.1  $\mu$ F decoupling capacitors on each VDD pins, it is recommended to put a 10  $\mu$ F decoupling capacitor near our part's VDD, it is for stabilizing the power supply for our part. Ferrite bead is also recommended for isolating the power supply for our part and other power supplies in other parts of the circuit. But, it is optional and depends on the power supply conditions of other circuits.

Recommended Power Supply Decoupling Capacitor Diagram

### Requirements on the De-coupling Capacitors

There is no special requirement on the material of the capacitors. Ceramic capacitors are generally being used with typically materials of X5R or X7R.

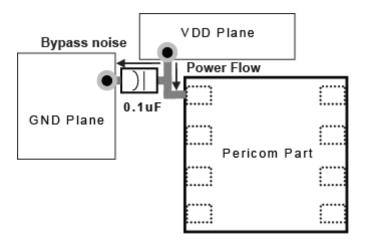

### **Layout and Decoupling Capacitor Placement Consideration**

- Each 0.1 µF decoupling capacitor should be placed as close as possible to each VDD pin.

- VDD and GND planes should be used to provide a low impedance path for power and ground.

- Via holes should be placed to connect to VDD and GND planes directly.

- Trace should be as wide as possible

- Trace should be as short as possible.

- The placement of decoupling capacitor and the way of routing trace should consider the power flowing criteria.

- 10 µF Capacitor should also be placed closed to our part and should be placed in the middle location of 0.1 µF capacitors.

- Avoid the large current circuit placed close to our part; especially when it is shared the same VDD and GND planes. Since large current flowing on our VDD or GND planes will generate a potential variation on the VDD or GND of our part.

Decoupling Capacitor Placement Diagram

### Package Mechanical: 56-pin TQFN (ZB56)

#### Note:

For latest package info, please check: http://www.pericom.com/products/packaging

### **Related Products Information**

| Part Number  | Product Description                                                                 |  |  |

|--------------|-------------------------------------------------------------------------------------|--|--|

| PI3HDX414    | HDMI 1.4b 3.4Gbps Splitter 1:4 with Signal Conditioning                             |  |  |

| PI3HDX1204   | HDMI 2.0 Redriver for 6Gbps Application                                             |  |  |

| PI3HDS20412  | Wide Voltage Range DisplayPort & HDMI 2.0 Video Switch                              |  |  |

| PI3HDX511A   | HDMI 1.4b 3.4Gbps Redriver and DP++ Level Shifter                                   |  |  |

| PI3EQXDP1201 | DisplayPort 1.2 Re-driver with Built-in AUX Listener                                |  |  |

| PI3VDP1430   | Dual Mode DisplayPort to HDMI Level Shifter and Re-driver                           |  |  |

| PI3VDP3212   | 2-Lane DisplayPort1.2 Compliant Passive Switch                                      |  |  |

| PI3VDP12412  | 4-Lane DisplayPort1.2 Compliant Passive Switch                                      |  |  |

| PI3HDMI521   | HDMI 1.4b 3.4Gbps 2:1 Switch/Re-driver with built-in ARC and Fast Switching support |  |  |

| PI3HDMI336   | Active HDMI 3:1 Switch/Re-driver with I <sup>2</sup> C control and ARC Transmitter  |  |  |

### **PRODUCT STATUS DEFINITIONS**

| Datasheet<br>Identification | <b>Product Status</b> | Definition                                                                                                                                                                                       |

|-----------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced<br>Information     | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                    |

| Preliminary                 | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Diodes Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification<br>Needed | Full Production       | Datasheet contains final specifications. Diodes Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                    | Not In Production     | Datasheet contains specifications on a product that is discontinued by Diodes Semiconductor. The datasheet is for reference information only.                                                    |

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated www.diodes.com

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Video Switch ICs category:

Click to view products by Diodes Incorporated manufacturer:

Other Similar products are found below:

PI3HDX621FBE PI3HDMI2410FFE PI3VDP12412NEE HD3SS212ZQER PI3HDMI412ADZBEX AD8191ASTZ LT6555IGN#PBF

AD8190ACPZ HD3SS215IZQER MAX4567CSE+ MAX4566ESE+ MAX4566CSE+ MAX4567ESE+ PI3HDX412BDZBEX NJM2244M

LT1203CN8#PBF MAX4885ETJ+T MAX4589CAP+ MAX4565EAP+ MAX4565CAP+ MAX4545EAP+ MAX4545CAP+

MAX4529CUT+T MAX4545CWP+ MAX4547CEE+ MAX4547EEE+ MAX4562CEE+ MAX4562EEE+ MAX4563CEE+ MAX4563EEE+

MAX4566CEE+ MAX4567EEE+ MAX4573CAI+ MAX4584EUB+ MAX4586EUB+ MAX4587EUB+ MAX4588CAI+ EL4340IUZ

MAX4885EETG+CK2 MAX4565CPP+ MAX4545EPP+ NJM2246M NJM2279D NJM2249M FSAV330MTCX FSAV430MTCX

FSAV430QSCX FSAV433MTCX FSAV450BQX FSHDMI08MTDX