3.3V, PCI Express® 3.0 2-Lane, 2:1 Mux/DeMux Switch, with Single Enable

### **Features**

- → 4 Differential Channel, 2:1 Mux/DeMux

- → PCI Express<sup>®</sup> 3.0 Performance, 8.0Gbps

- → Bi-directional Operation

- → Low Bit-to-Bit Skew, 10ps max

- → Low channel-to-channel skew, 20ps max

- → Low Crosstalk: -35dB@4 GHz

- → High Off Isolation: -22dB@4 GHz (8.0Gbps)

- → Low insertion loss: -1.3dB@4 GHz (8.0Gbps)

- → Return loss: -21dB@4 GHz

- → ESD:1.5KV HBM

- → Support for DP1.2 HBR2, HBR, RBR

- → Supply Voltage 3.3V

- → Industrial Temperature Range: -40°C to 85°C

- → Packaging (Pb-free & Green):

- 42-contact, TQFN (ZH42), 3.5 x 9mm

- 40-contact, TQFN (ZL40), 3 x 6mm

### **Description**

The PI3PCIE3412A is an 8 to 4 differential channel multiplexer/demultiplexer switch. This solution can switch 2 full PCI Express® 3.0, lanes to one of two locations. Using a unique design technique, Diodes Incorporated has been able to minimize the impedance of the switch such that the attenuation observed through the switch is minimal. The unique design technique also offers a layout targeted for PCI Express signals, which minimizes the channel to channel skew as well as channel to channel crosstalk as required by the PCI Express specification.

The PI3PCIE3412A can also be used for application up to 12Gbps.

### **Application**

Routing of PCI Express 3.0, DP1.2, USB3.0, SAS2.0, SATA3.0, XAUI, RXAUI signals with low signal attenuation.

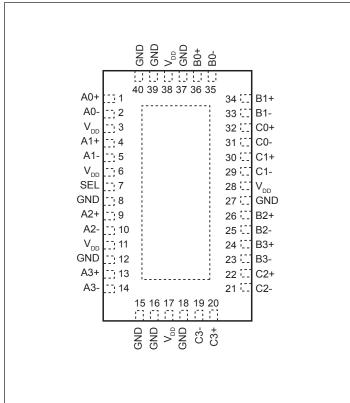

## Pin Configuration 40-Contact TQFN

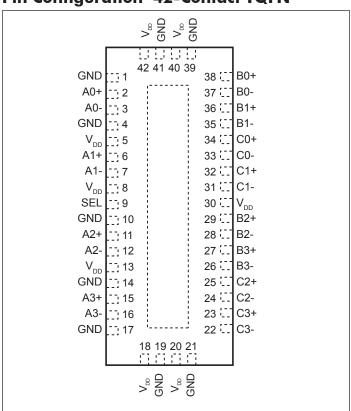

## Pin Configuration 42-Contact TQFN

1

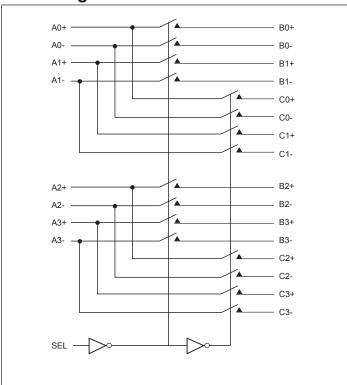

## **Block Diagram**

### **Truth Table**

| Function                         | SEL |

|----------------------------------|-----|

| A <sub>N</sub> to B <sub>N</sub> | L   |

| A <sub>N</sub> to C <sub>N</sub> | Н   |

# **Pin Description**

| Pin #                                                 |                                         |                   |                                                           |                                              |  |  |  |

|-------------------------------------------------------|-----------------------------------------|-------------------|-----------------------------------------------------------|----------------------------------------------|--|--|--|

| 42-TQFN                                               | 40-TQFN                                 | Pin Name          | I/O                                                       | Description                                  |  |  |  |

| 2                                                     | 1                                       | A0+               | T/O                                                       | C: LUO CI LO D. (A                           |  |  |  |

| 3                                                     | 2                                       | A0-               | I/O                                                       | Signal I/O, Channel 0, Port A                |  |  |  |

| 6                                                     | 4                                       | A1+               | I/O                                                       | Cianal I/O Chamal I Dant A                   |  |  |  |

| 7                                                     | 5                                       | A1-               | I/O                                                       | Signal I/O, Channel 1, Port A                |  |  |  |

| 11                                                    | 9                                       | A2+               | I/O                                                       | Cincil I/O Chamala Bant A                    |  |  |  |

| 12                                                    | 10                                      | A2-               | I/O                                                       | Signal I/O, Channel 2, Port A                |  |  |  |

| 15                                                    | 13                                      | A3+               | I/O                                                       | Signal I/O Chammal 2 Point A                 |  |  |  |

| 16                                                    | 14                                      | A3-               | 1/0                                                       | Signal I/O, Channel 3, Port A                |  |  |  |

| 38                                                    | 36                                      | B0+               | I/O                                                       | Cianal I/O Chamalo Bart B                    |  |  |  |

| 37                                                    | 35                                      | В0-               | I/O                                                       | Signal I/O, Channel 0, Port B                |  |  |  |

| 36                                                    | 34                                      | B1+               | I/O                                                       | Signal I/O, Channel 1, Port B                |  |  |  |

| 35                                                    | 33                                      | B1-               | I/O                                                       | Signal I/O, Channel I, Port b                |  |  |  |

| 29                                                    | 26                                      | B2+               | I/O                                                       | Signal I/O Chammal 2 Part P                  |  |  |  |

| 28                                                    | 25                                      | B2-               | 1/0                                                       | Signal I/O, Channel 2, Port B                |  |  |  |

| 27                                                    | 24                                      | B3+               | I/O                                                       | Signal I/O Channel 2 Pout P                  |  |  |  |

| 26                                                    | 23                                      | В3-               | 1/0                                                       | Signal I/O, Channel 3, Port B                |  |  |  |

| 34                                                    | 32                                      | C0+               | I/O                                                       | Signal I/O Channel O Port C                  |  |  |  |

| 33                                                    | 31                                      | C0-               | 1/0                                                       | Signal I/O, Channel 0, Port C                |  |  |  |

| 32                                                    | 30                                      | C1+               | I/O                                                       | Signal I/O, Channel 1, Port C                |  |  |  |

| 31                                                    | 29                                      | C1-               | 1/0                                                       | Signal 1/O, Channel 1, Port C                |  |  |  |

| 25                                                    | 22                                      | C2+               | I/O                                                       | Signal I/O, Channel 2, Port C                |  |  |  |

| 24                                                    | 21                                      | C2-               | 1/0                                                       | Signal 1/O, Chamiel 2, Fort C                |  |  |  |

| 23                                                    | 20                                      | C3+               | I/O                                                       | Signal I/O, Channel 3, Port C                |  |  |  |

| 22                                                    | 19                                      | C3-               | 1/0                                                       | Signal 1/O, Chamiel 3, 1 of t C              |  |  |  |

| 9                                                     | 7                                       | SEL               | I Operation mode Select (when SEL=0: A→B, when SEL=1: A→C |                                              |  |  |  |

| 5, 8, 13,18,<br>20, 30, 40,<br>42                     | 3, 6, 11, 17,<br>28, 38                 | $V_{\mathrm{DD}}$ | Pwr                                                       | $3.3\mathrm{V}$ ±10% Positive Supply Voltage |  |  |  |

| 1, 4, 10, 14,<br>17, 19, 21, 39,<br>41, Center<br>Pad | 8, 12, 15, 16,<br>18, 27, 37,<br>39, 40 | GND               | Pwr                                                       | Power ground                                 |  |  |  |

3

### **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| <u> </u>                           |                |

|------------------------------------|----------------|

| Storage Temperature                | 65°C to +150°C |

| Supply Voltage to Ground Potential | 0.5V to +3.7V  |

| Channel DC Input Voltage           | 0.5V to 1.5V   |

| DC Output Current                  | 120mA          |

| Power Dissipation                  | 0.5W           |

| SEL DC Input Voltage               | 0.5V to 3.7V   |

| Junction Temperature               | 125°C          |

|                                    |                |

**Note:** Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Electrical Characteristics**

**Recommended Operating Conditions**

| Symbol                | Parameter                                      | Conditions                    | Min. | Тур. | Max. | Units            |

|-----------------------|------------------------------------------------|-------------------------------|------|------|------|------------------|

| $V_{\mathrm{DD}}$     | 3.3V Power Supply                              |                               | 3.0  | 3.3  | 3.6  | V                |

| I <sub>DD</sub>       | Total current from V <sub>DD</sub> 3.3V supply | $SEL = 0V \text{ or } V_{DD}$ |      | 0.15 | 1    | mA               |

| V <sub>I/O</sub> -DIF | Differential Voltage (differential pins)       |                               |      |      | 1.6  | V <sub>ppd</sub> |

| V <sub>I/O-CM</sub>   | Common Mode Voltage (differiential pins)       |                               | 0    |      | 0.8  | V                |

| T <sub>A</sub>        | Operating temperature range                    |                               | -40  |      | 85   | °C               |

## DC Electrical Characteristics for Switching over Operating Range

| Parameters            | Description                                                          | Test Conditions <sup>(1)</sup>                                                      | Min. | Typ.(1) | Max. | Units |

|-----------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|---------|------|-------|

| V <sub>IH</sub> - SEL | Input HIGH Voltage, SEL Input                                        |                                                                                     | 2    |         | 3.6  |       |

| V <sub>IL</sub> - SEL | Input LOW Voltage, SEL Input                                         |                                                                                     | 0    |         | 0.8  | V     |

| $v_{IK}$              | Clamp Diode Voltage                                                  | $V_{\mathrm{DD}} = \mathrm{Max.}$ , $I_{\mathrm{IN}} = -18\mathrm{mA}$              |      | -0.7    | -1.2 |       |

| IIH                   | Input HIGH Current, SEL                                              | $V_{DD} = Max., V_{IN} = V_{DD}$                                                    |      |         | ±5   |       |

| $II\Gamma$            | Input LOW Current, SEL                                               | $V_{\mathrm{DD}} = \mathrm{Max.},  V_{\mathrm{IN}} = 0\mathrm{V}$                   |      |         | ±5   | μΑ    |

| I <sub>IN</sub> - SEL | Input Leakage Current, SEL Input                                     | $V_{IN} = V_{IH}$ - SEL Max or $V_{IL}$ - SEL Min                                   | -10  |         | +10  | μΑ    |

| IIH                   | Input HIGH Current, A <sub>X</sub> , B <sub>X</sub> , C <sub>X</sub> | $V_{\mathrm{DD}} = \mathrm{Max.},  V_{\mathrm{IN}} = 1.5 \mathrm{V}$                | -10  |         | +10  | 4     |

| $I_{IL}$              | Input LOW Current, A <sub>X</sub> , B <sub>X</sub> , C <sub>X</sub>  | $V_{\mathrm{DD}} = \mathrm{Max.},  V_{\mathrm{IN}} = 0\mathrm{V}$                   | -10  |         | +10  | μΑ    |

| IOZH                  | HighZ HIGH Current, B <sub>X</sub> , C <sub>X</sub>                  | $V_{DD} = Max., V_{IN} = 1.5V$                                                      | -10  |         | +10  | μΑ    |

| IOZL                  | HighZ LOW Current, B <sub>X</sub> , C <sub>X</sub>                   | $V_{\mathrm{DD}} = \mathrm{Max.},  V_{\mathrm{IN}} = 0 \mathrm{V}$                  | -10  |         | +10  | μΑ    |

| C <sub>I/O-ON</sub>   | ON state I/O capacitance                                             |                                                                                     |      | 1.5     |      | pF    |

| RON                   | ON state resistance                                                  | $V_{\rm DD} = 3.3 \text{V},  \mathrm{IO} = 8 \text{mA},  V_{\rm IN} = 0.8 \text{V}$ |      | 5       |      | Ω     |

#### Note:

<sup>1.</sup> Typical values are at  $V_{DD}$  = 3.3V,  $T_A$  = 25°C ambient and maximum loading.

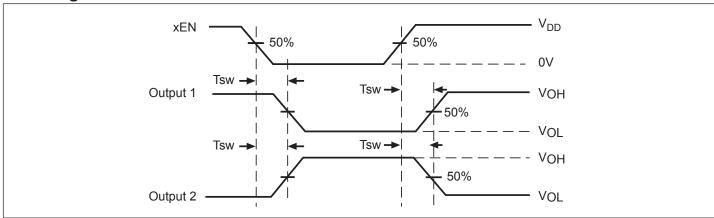

## **Switching Characteristics**

| Parameters         | Description                                                                 | <b>Test Conditions</b> | Min. | Тур. | Max.  | Units |

|--------------------|-----------------------------------------------------------------------------|------------------------|------|------|-------|-------|

| tpZH, tpZL         | Line Enable Time - SEL to A <sub>N</sub> , B <sub>N</sub> , C <sub>N</sub>  |                        | 2    | 20   | 25    |       |

| tpHZ, tPLZ         | Line Disable Time - SEL to A <sub>N</sub> , B <sub>N</sub> , C <sub>N</sub> |                        | 0.5  | 5    | 25 ns |       |

| t <sub>b-b</sub>   | Bit-to-bit skew within the same differential pair 5 10                      |                        | 10   | ps   |       |       |

| t <sub>ch-ch</sub> | Channel-to-channel skew                                                     |                        |      |      | 20    | ps    |

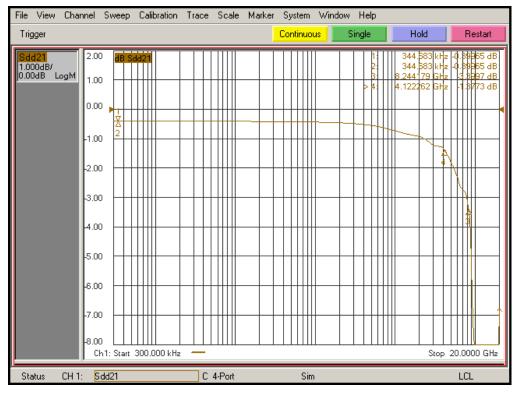

# **Dynamic Electrical Characteristics**

| Parameter           | Description                   | <b>Test Conditions</b>                                      | Min.  | Typ.(1) | Max. | Units |

|---------------------|-------------------------------|-------------------------------------------------------------|-------|---------|------|-------|

|                     |                               | f= 50MHz - 1,25GHz                                          |       | -0.8    | -1   |       |

| DDII                | Differential Insertion Loss   | f=1.25GHz - 2.5GHz                                          |       | -1.0    | -1.2 | dB    |

| DDIL                | $(V_{IN} = -10 dBm, DC = 0V)$ | f=2.5GHz - 4GHz                                             |       | -1.3    | -1.6 | ав    |

|                     |                               | f=5GHz                                                      |       | -1.8    | -2.2 |       |

|                     |                               | f= 50MHz - 1.25GHz                                          | -26.3 | -32.9   |      |       |

| DDII                | Differential Off Isolation    | f=1.25GHz - 2.5GHz                                          | -21.4 | -26.7   |      | dB    |

| DDIL <sub>OFF</sub> | Differential Off Isolation    | f=2.5GHz - 4GHz                                             | -17.6 | -22     |      | ав    |

|                     |                               | f=5GHz                                                      | -16   | -20     |      |       |

|                     | Differential Return Loss      | f= 50MHz - 1.25GHz                                          | -20   | -25     |      |       |

| DDRL                |                               | f=1.25GHz - 2.5GHz                                          | -18.4 | -23     |      | dB    |

| DDKL                |                               | f=2.5GHz - 4GHz                                             | -16.8 | -21     |      | ub    |

|                     |                               | f=5GHz                                                      | -9.6  | -12     |      |       |

|                     |                               | f= 50MHz - 1.25GHz                                          | -34.1 | -42.6   |      |       |

| DDNEXT              | Near End Crosstalk            | f=1.25GHz - 2.5GHz                                          | -30.5 | -38.1   |      | dB    |

| DDNEXI              | Near Elia Crosstark           | f=2.5GHz - 4GHz                                             | -28.1 | -35.1   |      |       |

|                     |                               | f=5GHz                                                      | -27.2 | -34     |      |       |

|                     | Max Signal Frequency Range    | Insertion loss 1.5dB,<br>V <sub>IN</sub> =0.623Vpp, DC=0V   |       | 4.0     |      |       |

| V <sub>IF</sub>     |                               | Insertion loss 1.5dB,<br>V <sub>IN</sub> =0.623Vpp, DC=0.9V |       | 4.0     |      | CH    |

|                     |                               | Insertion loss 3dB,<br>V <sub>IN</sub> =0.623Vpp, DC=0V     |       | 8.0     |      | GHz   |

|                     |                               | Insertion loss 3dB,<br>V <sub>IN</sub> =0.623Vpp, DC=0.9V   |       | 8.0     |      |       |

| BW                  | -3dB Bandwidth                |                                                             |       | 8.2     |      | GHz   |

#### Notes:

1. Guaranteed by design. Typical values are at  $V_{DD} = 3.3 \text{V}$ ,  $T_A = 25^{\circ}\text{C}$  ambient and maximum loading.

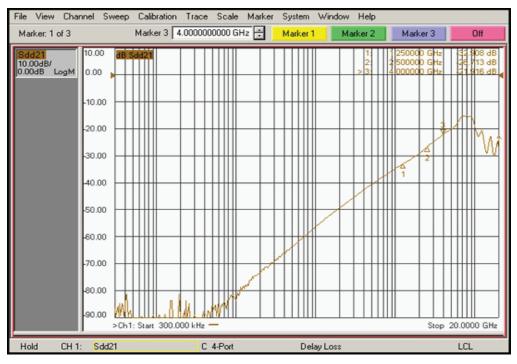

**Differential Insertion Loss**

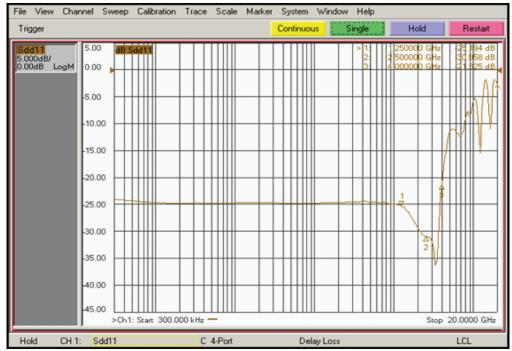

**Differential Return Loss**

6

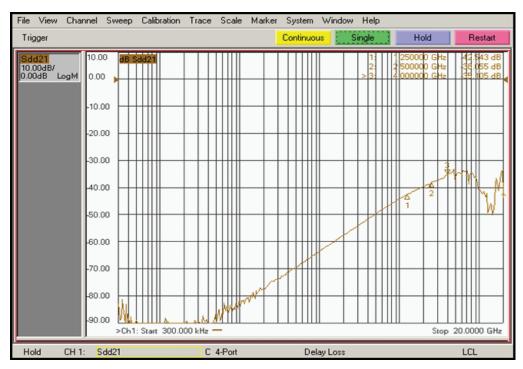

**Differential Off Isolation**

**Differential Crosstalk**

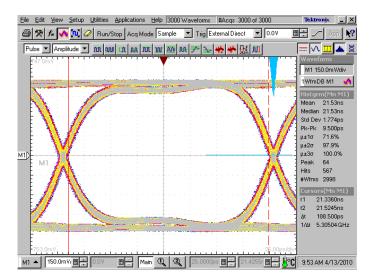

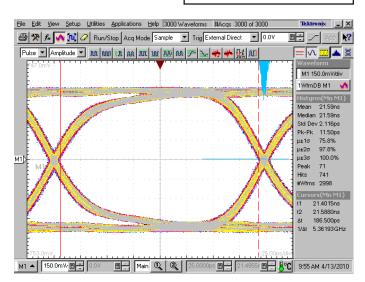

5.0 Gbps RX signal eye without PI3PCIE3412A

5.0 Gbps RX signal eye with PI3PCIE3412A

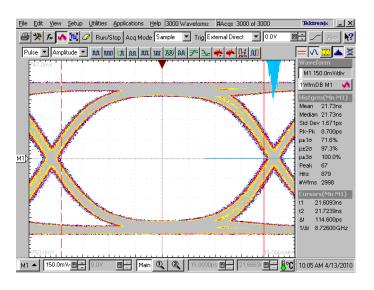

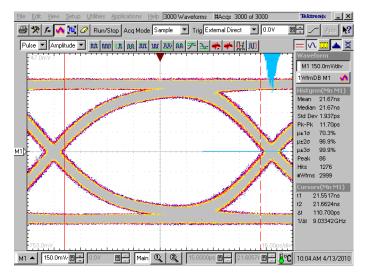

8.0 Gbps RX signal eye without PI3PCIE3412A

8.0 Gbps RX signal eye with PI3PCIE3412A

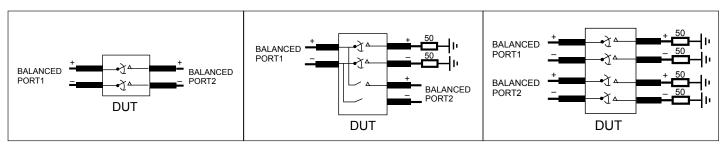

Diff. Insertion Loss and Return Test Circuit

**Diff. Off Isolation Test Circuit**

Diff. Near End Xtalk Test Circuit

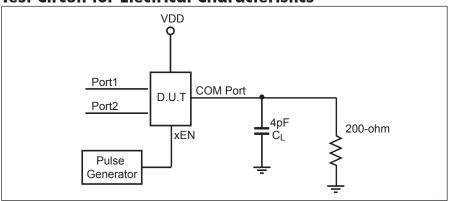

# Test Circuit for Electrical Characteristics $^{(1-5)}$

#### Notes

- 1.  $C_L = Load$  capacitance: includes jig and probe capacitance.

- 2.  $R_T$  = Termination resistance: should be equal to  $Z_{OUT}$  of the Pulse Generator

- 3. Output 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Output 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- 4. All input impulses are supplied by generators having the following characteristics:  $PRR \le MHz$ ,  $Z_O = 50\Omega$ ,  $t_R \le 2.5 ns$ ,  $t_F \le 2.5 ns$ .

- 5. The outputs are measured one at a time with one transition per measurement.

### **Switch Positions**

| Test                                | Switch |

|-------------------------------------|--------|

| tpLZ, tpZL                          | 3.0V   |

| t <sub>PHZ</sub> , t <sub>PZH</sub> | GND    |

| Prop Delay                          | Open   |

## **Switching Waveforms**

**Voltage Waveforms Enable and Disable Times**

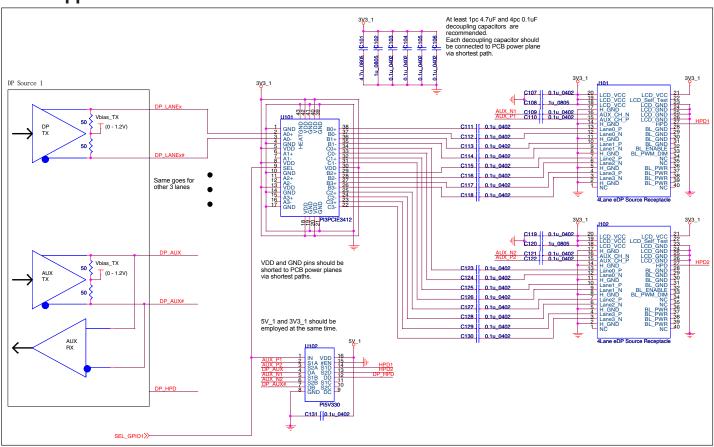

## **DP1.2 Application**

## **Part Marking Information**

### **ZH Package**

PI3PCIE 3412AZHE O YYWWXX

Y : Year

W : Workweek

1st X: Assembly Code

2nd X: Fab Code

### **ZL Package**

PI3PCIE 3412AZLE O YYWWXX

Y: Year

W : Workweek

1st X: Assembly Code

2nd X: Fab Code

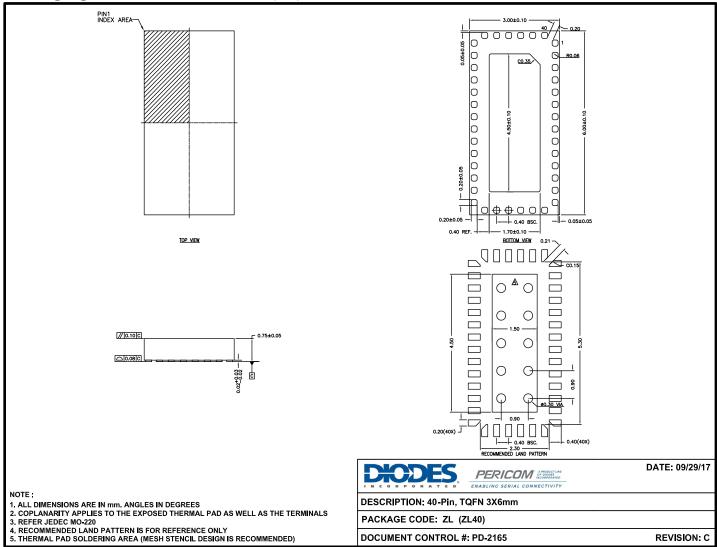

# Packaging Mechanical: 40-TQFN (ZL)

17-0681

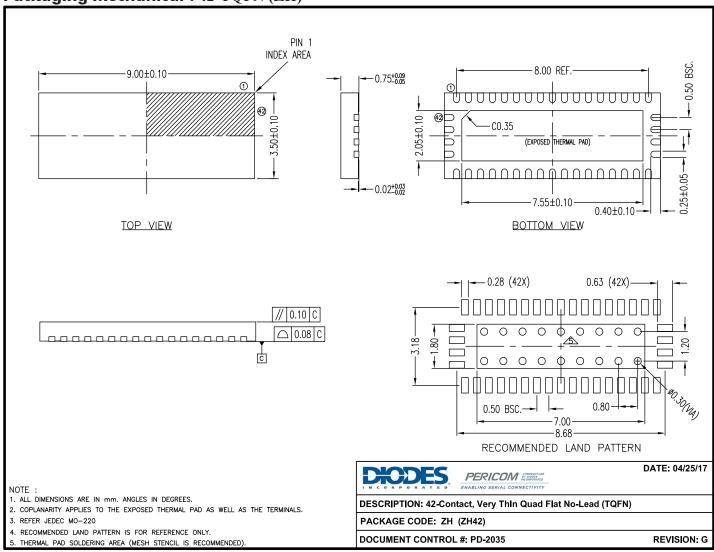

## Packaging Mechanical: 42-TQFN (ZH)

#### For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

### **Ordering Information**

| Ordering Code    | Package Code | Package Description                            |

|------------------|--------------|------------------------------------------------|

| PI3PCIE3412AZLEX | ZL           | 40-pin, 3x6mm(TQFN)                            |

| PI3PCIE3412AZHEX | ZH           | 42-contact, Very Thin Quad Flat No-Lead (TQFN) |

#### Notes:

- Thermal characteristics can be found on the company web site at www.diodes.com/design/support/packaging/

- E = Pb-free and Green

- X suffix = Tape/Reel

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated

www.diodes.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Encoders, Decoders, Multiplexers & Demultiplexers category:

Click to view products by Diodes Incorporated manufacturer:

Other Similar products are found below:

MC74HC163ADTG 74HC253N NLV74VHC1G01DFT1G NLVHC4851ADTR2G TC74AC138P(F) NLV14051BDR2G

NLV74HC238ADTR2G COMX-CAR-210 5962-8607001EA 5962-8756601EA SN74LS148N 8CA3052APGGI8 TC74HC4051AF(EL,F)

TC74VHC138F(EL,K,F PI3B3251LE PI3B3251QE NLV74HC4851AMNTWG MC74LVX257DG M74HCT4851ADWR2G

MC74LVX257DTR2G 74VHC4066AFT(BJ) 74VHCT138AFT(BJ) 74HC158D.652 74HC4052D(BJ) 74VHC138MTC COMX-CAR-P1

JM38510/65852BEA JM38510/30702BEA 74VHC138MTCX 74HC138D(BJ) NL7SZ19DFT2G 74AHCT138T16-13 74LCX138FT(AJ)

74LCX157FT(AJ) NL7SZ18MUR2G PCA9540BD,118 SNJ54HC251J SN54LS139AJ SN74CBTLV3257PWG4 SN74ALS156DR

SN74AHCT139PWR 74HC251D.652 74HC257D.652 74HCT153D.652 74HC253D.652 74HCT139D.652 TC74HC4052AFT(EL)

SN74LVC257AMPWREP 74HC138DB.112 74HC157PW.112