### 4 Channel I2C bus Switch with Reset

### **Features**

- 1-of-4 bidirectional translating multiplexer

- I2C-bus interface logic

- Operating power supply voltage: 1.65 V to 5.5 V

- Allows voltage level translation between 1.2V, 1.8V,2.5

V, 3.3 V and 5 V buses

- Low standby current

- · Low Ron switches

- · Channel selection via I2C bus

- Power-up with all multiplexer channels deselected

- Capacitance isolation when channel disabled

- No glitch on power-up

- Supports hot insertion

- 5 V tolerant inputs

- 0 Hz to 400 kHz clock frequency

- ESD protection exceeds 8000 V HBM per JESD22-A114, and 1000 V CDM per JESD22-C101

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

- Packages offered: SOIC-16W,TSSOP-16L, TQFN4\*4-16ZY

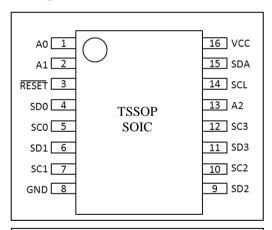

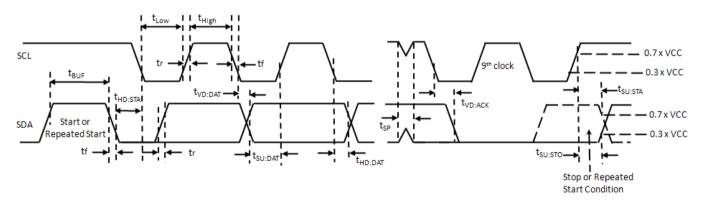

# **Pin Configuration**

## **Description**

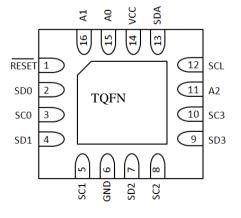

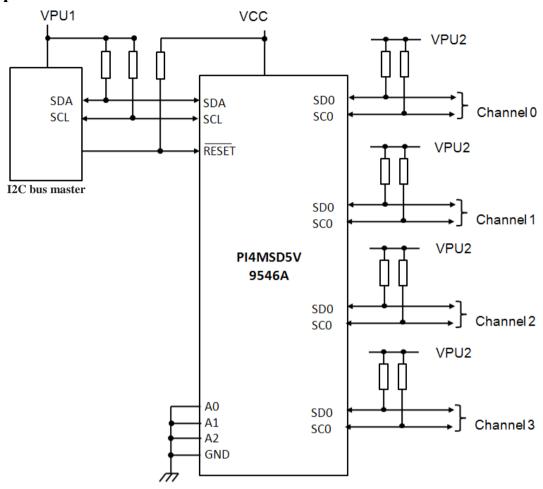

The PI4MSD5V9546A is a quad bidirectional translating switch controlled via the I2C bus. The SCL/SDA upstream pair fans out to four downstream pairs, or channels. Any individual SCx/SDx channel or combination of channels can be selected, determined by the contents of the programmable control register.

An active LOW reset input allows the PI4MSD5V-9546A to recover from a situation where one of the downstream buses is stuck in a LOW state. Pulling the RESET pin LOW resets the I2C bus state machine and causes all the channels to be deselected as does the internal Power-On Reset (POR) function.

The pass gates of the switches are constructed such that the VCC pin can be used to limit the maximum high voltage which is passed by the PI4MSD5V9546A. This allows the use of different bus voltages on each pair, so that 1.2V, 1.8 V or 2.5 V or 3.3 V parts can communicate with 5 V parts without any additional protection. External pull-up resistors pull the bus up to the desired voltage level for each channel. All I/O pins are 5 V tolerant.

## **Pin Description**

| Pin No.<br>(TSSOP,<br>SOIC) | Pin No.<br>(TQFN) | Pin<br>Name | Туре   | Description          |

|-----------------------------|-------------------|-------------|--------|----------------------|

| 1                           | 15                | A0          | Input  | address input 0      |

| 2                           | 16                | A1          | Input  | address input 1      |

| 3                           | 1                 | RESET       | Input  | active LOW reset pin |

| 4                           | 2                 | SD0         | I/O    | serial data 0        |

| 5                           | 3                 | SC0         | I/O    | serial clock 0       |

| 6                           | 4                 | SD1         | I/O    | serial data 1        |

| 7                           | 5                 | SC1         | I/O    | serial clock 1       |

| 8                           | 6                 | GND         | Ground | supply ground        |

| 9                           | 7                 | SD2         | I/O    | serial data 2        |

| 10                          | 8                 | SC2         | I/O    | serial clock 2       |

| 11                          | 9                 | SD3         | I/O    | serial data 3        |

| 12                          | 10                | SC3         | I/O    | serial clock 3       |

| 13                          | 11                | A2          | Input  | address input 2      |

| 14                          | 12                | SCL         | I/O    | serial clock line    |

| 15                          | 13                | SDA         | I/O    | serial data line     |

| 16                          | 14                | VCC         | Power  | supply voltage       |

# **Block Diagram**

Figure 1: Block Diagram

# **Maximum Ratings**

| i                               |                |

|---------------------------------|----------------|

| Storage Temperature             | 55 ℃ to +125 ℃ |

| Supply Voltage port B           | 0.5V to +6.0V  |

| Supply Voltage port A           | 0.5V to +6.0V  |

| DC Input Voltage                |                |

| Control Input Voltage (EN)      |                |

| Total power dissipation (1)     | 100mW          |

| Input current(EN,VCCA,VCCB,GND) |                |

| ESD: HBM Mode                   | 8000V          |

|                                 |                |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

**Recommended operation conditions**

| Symbol                | Parameter                                   | Min  | Тур | Max | Unit         |

|-----------------------|---------------------------------------------|------|-----|-----|--------------|

| $V_{CC}$              | V <sub>CCA</sub> Positive DC Supply Voltage | 1.65 | ı   | 5.5 | V            |

| $V_{EN}$              | Enable Control Pin Voltage                  | GND  | -   | 5.5 | V            |

| $V_{IO}$              | I/O Pin Voltage                             | GND  | -   | 5.5 | V            |

| $\Delta t / \Delta V$ | Input transition rise or fall time          | -    | -   | 10  | ns/V         |

| $T_A$                 | Operating Temperature Range                 | -40  | -   | +85 | $\mathcal C$ |

# **DC** Electrical Characteristics

Unless otherwise specified,  $-40^{\circ}\text{C} \le T_A \le 85 \text{ C}$ ,  $1.1\text{V} \le \text{Vcc} \le 3.6\text{V}$

| Symbol              | Parameter                 | Conditions                                                                                             | VCC              | Min              | Тур | Max                 | Unit |

|---------------------|---------------------------|--------------------------------------------------------------------------------------------------------|------------------|------------------|-----|---------------------|------|

| Supply              |                           |                                                                                                        |                  |                  | •   | -                   | •    |

| VCC                 | Supply Voltage            |                                                                                                        |                  | 1.65             |     | 5.5                 | V    |

| ICC                 |                           | operating mode;                                                                                        | 3.6V to 5.5V     |                  | 65  | 100                 | uA   |

|                     | supply current            | no load;<br>V <sub>I</sub> = VCC or GND;                                                               | 2.3V to 3.6V     |                  | 20  | 50                  | uA   |

|                     |                           | fSCL = 100  kHz                                                                                        | 1.65V to 2.3V    |                  | 10  | 30                  | uA   |

|                     |                           | standby mode; VCC =                                                                                    | 3.6V to 5.5V     |                  | 0.3 | 1                   | uA   |

| Istb                | standby current           | $\begin{vmatrix} 3.6 \text{ V}; \\ \text{no load}; \text{ V}_{\text{I}} = \text{VCC or} \end{vmatrix}$ | 2.3V to 3.6V     |                  | 0.1 | 1                   | uA   |

|                     |                           | GND;<br>fSCL = 0 kHz                                                                                   | 1.65V to 2.3V    |                  | 0.1 | 1                   | uA   |

| VPOR <sup>[1]</sup> | power-on reset voltage    | no load; $V_I = VCC$ or GND                                                                            | 3.6V to 5.5V     |                  | 1.3 | 1.5                 | V    |

| Input SCL           | ; input/output SDA        |                                                                                                        |                  |                  |     |                     |      |

| $V_{\rm IL}$        | LOW-level input voltage   |                                                                                                        | 1.65V to 5.5V    | -0.5             |     | +0.3V <sub>CC</sub> | V    |

| $V_{IH}$            | HIGH-level input voltage  |                                                                                                        | 1.65V to 2V      | $0.75V_{CC}$     |     | 6                   | V    |

| V IH                | Thori-level input voltage |                                                                                                        | 2V to 5.5V       | $0.7V_{CC}$      |     | 6                   | V    |

| т                   | I OW level output augment | $V_{OL} = 0.4 \text{ V}$                                                                               | 1.65V to 5.5V 3  |                  |     | -                   | mA   |

| $I_{OL}$            | LOW-level output current  | $V_{OL} = 0.6 \text{ V}$                                                                               | 1.65V to 5.5V 6  |                  |     | -                   | mA   |

| I <sub>IL</sub>     | LOW-level input current   | $V_I = GND$                                                                                            | 1.65V to 5.5V -1 |                  |     | +1                  | uA   |

| I <sub>IH</sub>     | HIGH-level input current  | $V_I = VCC$                                                                                            | 1.65V to 5.5V    | -1               |     | +1                  | uA   |

| Ci                  | input capacitance         | VI = GND                                                                                               | 1.65V to 5.5V    | -                | 12  | 13                  | pF   |

| Pass Gate           |                           |                                                                                                        |                  |                  |     |                     |      |

| 1 uss Gate          |                           | $V_{O} = 0.4 \text{ V};$                                                                               | 4.5 V to 5.5 V   | 4                | 9   | 24                  | Ω    |

| Dom                 | ON state resistance       | $I_O = 15 \text{ mA}$                                                                                  | 3V to 3.6V       | 5                | 11  | 31                  | Ω    |

| Ron                 | ON-state resistance       | $V_{O} = 0.4 \text{ V};$                                                                               | 2.3V to 2.7V 7   |                  | 16  | 55                  | Ω    |

|                     |                           | $I_O = 10 \text{mA}$                                                                                   | 1.65V to 2V 9    |                  | 20  | 70                  | Ω    |

|                     |                           |                                                                                                        | 5V               |                  | 3.6 |                     | V    |

|                     |                           |                                                                                                        | 4.5 V to 5.5 V   | 2.8              |     | 4.5                 | V    |

|                     |                           |                                                                                                        | 3.3V             |                  | 2.2 |                     | V    |

| Vanas               | and the automorphism      | Vin =VCC;                                                                                              | 3V to 3.6V       | 1.6              |     | 2.8                 | V    |

| Vpass               | switch output voltage     | Iout = -100uA                                                                                          | 2.5V             |                  | 1.5 |                     | V    |

|                     |                           |                                                                                                        | 2.3V to 2.7V 1.1 |                  |     | 2                   | V    |

|                     |                           |                                                                                                        | 1.8V             |                  | 0.9 |                     | V    |

|                     |                           |                                                                                                        | 1.65V to 2V      | 1.65V to 2V 0.54 |     | 1.3                 | V    |

| $I_{L}$             | leakage current           | VI = VCC or GND                                                                                        | 1.65V to 5.5V    | -1               |     | +1                  | uA   |

| Cio                 | input/output capacitance  | VI = VCC or GND                                                                                        | 1.65V to 5.5V    |                  | 3   | 5                   | pF   |

To be continued

#### Continued

| Symbol                   | Parameter                | Conditions  | VCC           | Min         | Тур | Max                 | Unit |

|--------------------------|--------------------------|-------------|---------------|-------------|-----|---------------------|------|

| Select inputs A0, A1, A2 |                          |             |               |             |     |                     |      |

| $V_{\rm IL}$             | LOW-level input voltage  |             | 1.65V to 5.5V | -0.5        |     | +0.3V <sub>CC</sub> | V    |

| $V_{\mathrm{IH}}$        | HIGH-level input voltage |             | 1.65V to 5.5V | $0.7V_{CC}$ |     | 6                   | V    |

| $I_{IL}$                 | LOW-level input current  | $V_I = GND$ | 1.65V to 5.5V | -1          |     | +1                  | uA   |

| Ci                       | input capacitance        | $V_I = GND$ | 1.65V to 5.5V |             | 3   | 5                   | pF   |

Note: VCC must be lowered to 0.2 V for at least 5 us in order to reset part.

## **AC** Electrical characteristics

Tamb = -40 ° C to +85 ° C; unless otherwise specified.

| Symbol                         | Parameter                        | Conditions                        | VCC           | Min | Тур | Max | Unit |

|--------------------------------|----------------------------------|-----------------------------------|---------------|-----|-----|-----|------|

| t <sub>PD</sub> <sup>[1]</sup> | propagation delay                | from SDA to SDx,<br>or SCL to SCx | 1.65V to 5.5V |     |     | 0.3 | ns   |

| RESET                          |                                  |                                   |               |     |     |     |      |

| tw(rst)L                       | LOW-level reset time             |                                   |               | 4   |     |     | ns   |

| trst                           | reset time                       | SDA clear                         |               | 500 |     |     | ns   |

| t <sub>REC;STA</sub>           | recovery time to START condition |                                   |               | 0   |     |     | ns   |

#### Note

<sup>[1]</sup>Pass gate propagation delay is calculated from the  $20\Omega$  typical Ron and the 15 pF load capacitance.

<sup>[2]</sup> Measurements taken with 1 k $\Omega$ pull-up resistor and 50 pF load.

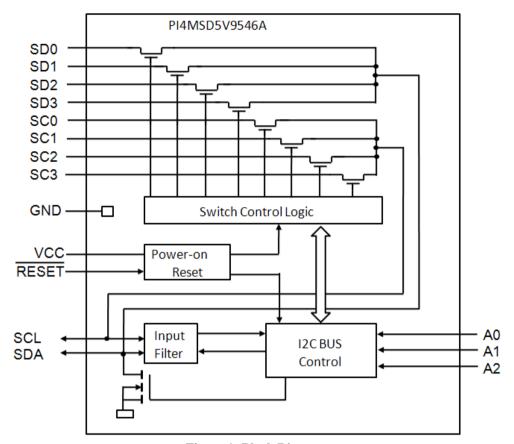

# **I2C Interface Timing Requirements**

| Symbol              | Parameter                                                                     | STANDAR<br>I <sup>2</sup> C E |      | FAST M | UNIT |     |

|---------------------|-------------------------------------------------------------------------------|-------------------------------|------|--------|------|-----|

| J                   |                                                                               | MIN                           | MAX  | MIN    | MAX  |     |

| fscl                | I2C clock frequency                                                           | 0                             | 100  | 0      | 400  | kHz |

| $t_{\rm Low}$       | I2C clock high time                                                           | 4.7                           |      | 1.3    |      | μs  |

| t <sub>High</sub>   | I2C clock low time                                                            | 4                             |      | 0.6    |      | μs  |

| $t_{SP}$            | I2C spike time                                                                |                               | 50   |        | 50   | ns  |

| t <sub>SU:DAT</sub> | I2C serial-data setup time                                                    | 250                           |      | 100    |      | ns  |

| t <sub>HD:DAT</sub> | I2C serial-data hold time                                                     | 0 [1]                         |      | 0 [1]  |      | μs  |

| tr                  | I2C input rise time                                                           |                               | 1000 |        | 300  | ns  |

| tf                  | I2C input fall time                                                           |                               | 300  |        | 300  | ns  |

| t <sub>BUF</sub>    | I2C bus free time between stop and start                                      | 4.7                           |      | 1.3    |      | μs  |

| t <sub>SU:STA</sub> | I2C start or repeated start condition setup                                   | 4.7                           |      | 0.6    |      | μs  |

| t <sub>HD:STA</sub> | I2C start or repeated start condition hold                                    | 4                             |      | 0.6    |      | μs  |

| t <sub>SU:STO</sub> | I2C stop condition setup                                                      | 4                             |      | 0.6    |      | μs  |

| t <sub>VD:DAT</sub> | Valid-data time (high to low) [2]<br>SCL low to SDA output low valid          |                               | 1    |        | 1    | μs  |

|                     | Valid-data time (low to high) [2]<br>SCL low to SDA output high valid         |                               | 0.6  |        | 0.6  | μs  |

| t <sub>VD:ACK</sub> | Valid-data time of ACK condition<br>ACK signal from SCL low to SDA output low |                               | 1    |        | 1    | μs  |

| Cb                  | I2C bus capacitive load                                                       |                               | 400  |        | 400  | pF  |

#### Notes:

- [1] A device internally must provide a hold time of at least 300 ns for the SDA signal (referred to as the VIH min of the SCL signal), in order to bridge the undefined region of the falling edge of SCL.

- [2] Data taken using a 1-k $\Omega$  pullup resistor and 50-pF load Notes

Figure 2. Definition of timing on the I2C-bus

# **Application**

Figure 3. Typical Application

| VCC  | VPU1      | VPU2      |

|------|-----------|-----------|

| 1.8V | 1.5V-5.5V | 1.2V-5.5V |

| 2.5V | 1.8V-5.5V | 1.8V-5.5V |

| 3.3V | 2.7V-5.5V | 2.7V-5.5V |

| 5V   | 4.5V-5.5V | 4.5V-5.5V |

#### Note:

If the device generating the interrupt has an open-drain output structure or can be 3-stated, a pull-up resistor is required. If the device generating the interrupt has a totem pole output structure and cannot be 3-stated, a pull-up resistor is not required. The interrupt inputs should not be left floating.

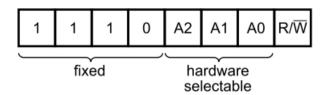

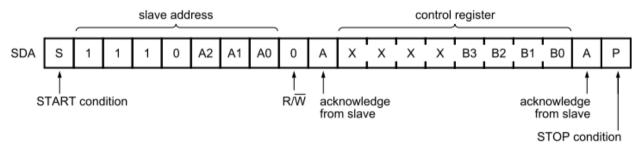

# **Device addressing**

Following a START condition, the bus master must output the address of the slave it is accessing. The address of the PI4MSD5V9546A is shown in Figure 4. To conserve power, no internal pull-up resistors are incorporated on the hardware selectable address pins and they must be pulled HIGH or LOW.

The last bit of the slave address defines the operation to be performed. When set to logic 1, a read is selected while a logic 0 selects a write operation.

Figure 4:Device address

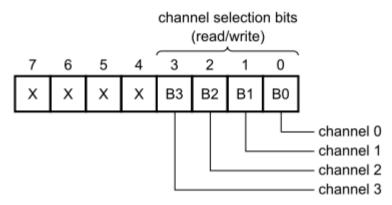

## **Control register**

Following the successful acknowledgement of the slave address, the bus master sends a byte to the PI4MSD5V9546A, which is stored in the control register. If the PI4MSD5V9546A receives multiple bytes, it saves the last byte received. This register can be written and read via the I2C-bus.bus.

Figure 5: Control register

#### **Control register definition**

One or several SCx/SDx downstream pair, or channel, is selected by the contents of the control register. This register is written after the PI4MSD5V9546A has been addressed. The 4 LSBs of the control byte are used to determine which channel is to be selected. When a channel is selected, the channel will become active after a STOP condition has been placed on the I2C-bus. This ensures that all SCx/SDx lines are in a HIGH state when the channel is made active, so that no false conditions are generated at the time of connection.

| D7 | D6 | D5 | D4 | В3 | B2 | B1 | В0 | Command                                              |

|----|----|----|----|----|----|----|----|------------------------------------------------------|

| X  | X  | X  | X  | X  | X  | X  | 0  | channel 0 disabled                                   |

|    |    |    |    |    |    |    | 1  | channel 0 enabled                                    |

| X  | X  | X  | X  | X  | X  | 0  | X  | channel 1 disabled                                   |

|    |    |    |    |    |    | 1  |    | channel 1 enabled                                    |

| X  | X  | X  | X  | X  | 0  | X  | X  | channel 2 disabled                                   |

|    |    |    |    |    | 1  |    |    | channel 2 enabled                                    |

| X  | X  | X  | X  | 0  | X  | X  | X  | channel 3 disabled                                   |

|    |    |    |    | 1  |    |    |    | channel 3 enabled                                    |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | no channel selected;<br>power-up/reset default state |

Control register: Write—channel selection; Read—channel status.

Remark: Several channels can be enabled at the same time. Example: B3 = 0, B2 = 1, B1 = 1, B0 = 0, means that channel 0 and channel 3 are disabled and channel 1 and channel 2 are enabled. Care should be taken not to exceed the maximum bus capacitance.

# **RESET** input

The RESET input is an active LOW signal which may be used to recover from a bus fault condition. By asserting this signal LOW for a minimum of tw(rst)L, the PI4MSD5V9546A will reset its registers and I2C-bus state machine and will deselect all channels. The RESET input must be connected to VCC through a pull-up resistor.

#### Power-on reset

When power is applied to VCC, an internal Power-On Reset (POR) holds the PI4MSD5V9546A in a reset condition until VCC has reached VPOR. At this point, the reset condition is released and the PI4MSD5V9546A registers and I2C-bus state machine are initialized to their default states (all zeroes) causing all the channels to be deselected. Thereafter, VCC must be lowered below 0.2 V to reset the device.

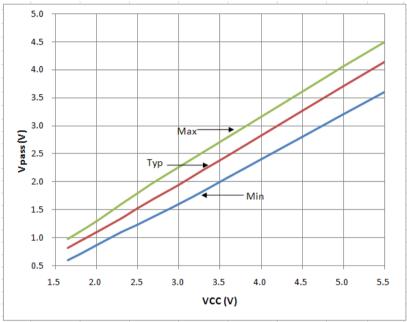

## Voltage translation

The pass gate transistors of the PI4MSD5V9546A are constructed such that the VCC voltage can be used to limit the maximum voltage that is passed from one I2C-bus to another.

Figure 6:Vpass voltage VS Vcc

Figure 6 shows the voltage characteristics of the pass gate transistors (note that the graph was generated using the data specified in Section "DC Electrical characteristics" of this data sheet).

In order for the PI4MSD5V9546A to act as a voltage translator, the Vpass voltage should be equal to, or lower than the lowest bus voltage. For example, if the main bus was running at 5 V, and the downstream buses were 3.3 V and 2.7 V, then Vpass should be equal to or below 2.7 V to clamp the downstream bus voltages effectively.

Looking at Figure 6, we see that Vpass (max) is at 2.7 V when the PI4MSD5V9546A supply voltage is 3.5 V or lower so the PI4MSD5V9546A supply voltage could be set to 3.3 V. Pull-up resistors can then be used to bring the bus voltages to their appropriate levels

## **I2C BUS**

The I2C-bus is for 2-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

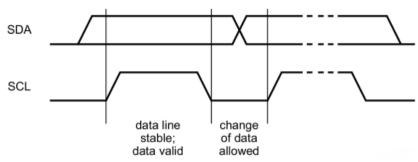

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time are interpreted as control signals

Figure 7: Bit Transfer

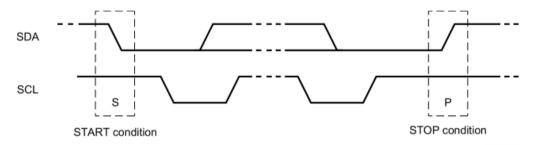

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line while the clock is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P)

Figure 8. Definition of Start and Stop Conditions

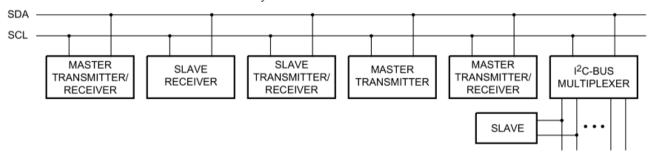

A device generating a message is a 'transmitter', a device receiving is the 'receiver'. The device that controls the message is the 'master' and the devices which are controlled by the master are the 'slaves'

Figure 9. System Configuration

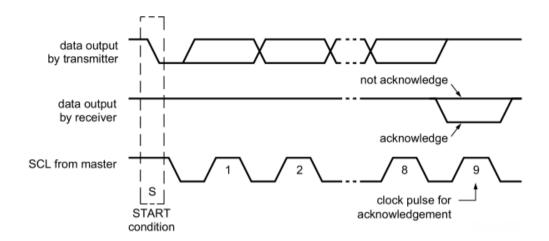

The number of data bytes transferred between the START and the STOP conditions from transmitter to receiver is not limited. Each byte of 8 bits is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter, whereas the master generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also, a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse; set-up and hold times must be taken into account.

A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event, the transmitter must leave the data line HIGH to enable the master to generate a STOP condition.

Figure 10. Acknowledgment on I2C Bus

Data is transmitted to the PI4MSD5V9546A control register using the write mode shown in bellow

Figure 11. Write Control Register

Data is transmitted to the PI4MSD5V9546A control register using the write mode shown in bellow

Figure 12. Read Control Register

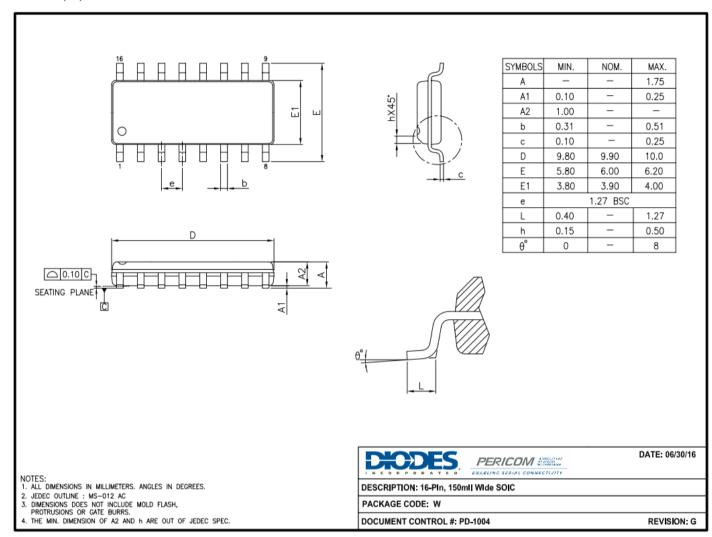

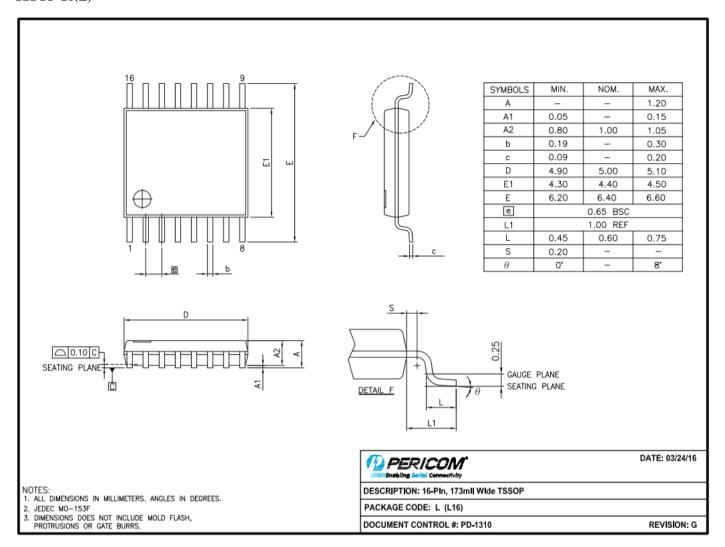

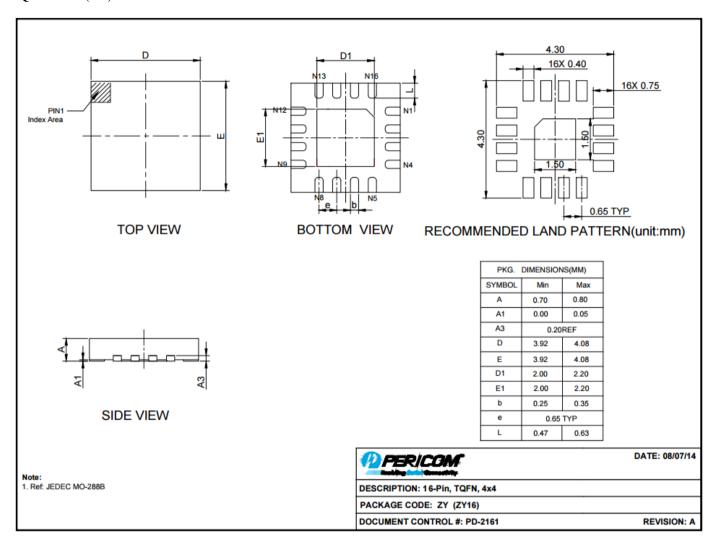

# **Mechanical Information**

SOIC-16(W)

### TSSOP-16(L)

### **TQFN4\*4-16(ZY)**

Note: For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

# **Ordering Information**

| Part No.          | Package Code | Package                                  |

|-------------------|--------------|------------------------------------------|

| PI4MSD5V9546AWE   | W            | 16-Pin,150 mil Wide (SOIC)               |

| PI4MSD5V9546AWEX  | W            | 16-Pin,150 mil Wide (SOIC), Tape & Reel  |

| PI4MSD5V9546ALE   | L            | 16-Pin,173 mil Wide (TSSOP)              |

| PI4MSD5V9546ALEX  | L            | 16-Pin,173 mil Wide (TSSOP), Tape & Reel |

| PI4MSD5V9546AZYEX | ZY           | 16-Pin, 4x4 (TQFN), Tape & Reel          |

#### Note:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- E = Pb-free and Green

- X suffix = Tape/Reel

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated www.diodes.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Multiplexer Switch ICs category:

Click to view products by Diodes Incorporated manufacturer:

Other Similar products are found below:

NLV74HC4066ADR2G HEF4051BP MC74HC4067ADTG DG508AAK/883B NLV14051BDG 016400E PI3V512QE 7705201EC

PI2SSD3212NCE PI3L100QE NLAS3257CMX2TCG PI5A3157BC6EX PI3V512QEX PI3DBS16213ZLEX PI3DBS16415ZHEX

PS509LEX MUX36S16IRSNR 74LVC1G3157GM-Q10X TC7W53FK,LF CD4053BM96 MC74HC4053ADWR2G MAX4051AEEE+

PI3L720ZHEX ADG1404YRUZ-REEL7 ADG1208YRZ-REEL7 CD4053BPWRG4 ADG658TRUZ-EP FSA1256L8X\_F113 PI5V330QE

PI5V331QE 5962-8771601EA ADG5249FBRUZ ADG1438BRUZ ADG5207BCPZ-RL7 ADW54003-0 AD7506JNZ AD7506KNZ

AD7506SQ AD8170AR AD8183ARUZ AD8184ANZ AD8185ARUZ AD8187ARUZ AD8188ARUZ AD8189ARUZ ADG1208YRUZ-REEL7 ADG1409YCPZ-REEL7 ADG5209FBRUZ ADG1408YRUZ-REEL7 ADG659YRUZ-REEL7