#### High Performance 1.62V To 3.6V Quad Uart with 64-Byte FIFO

#### **Features**

- → 1.62V to 3.6V with 5V Tolerant Serial Inputs

- → Programmable Sleep Mode with automatic wake-up

- Intel or Motorola Data Bus Interface select

- → Each UART is independently controlled with:

- □ 16C550 Compatible Register Set

- 64-byte Transmit and Receive FIFOs

- Transmit and Receive FIFO Level Counters

- Programmable TX and RX FIFO Trigger Levels for DMA and Interrupt Generation

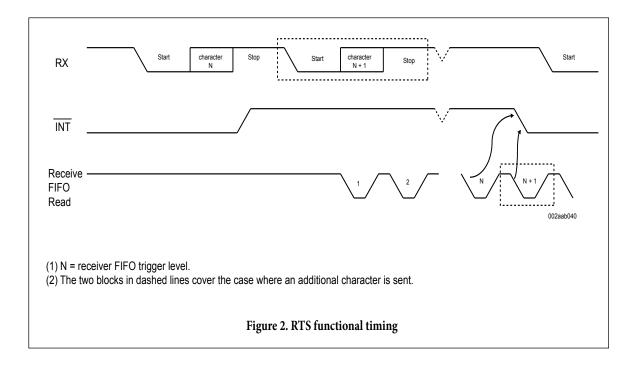

- → Programmable Receive FIFO Trigger Levels for Software/Hardware Flow Control

- → Programmable hysteresis(Table A-D) for Software/ Hardware Flow Control

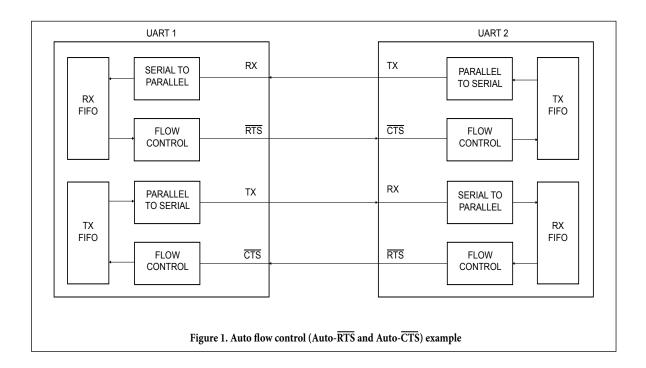

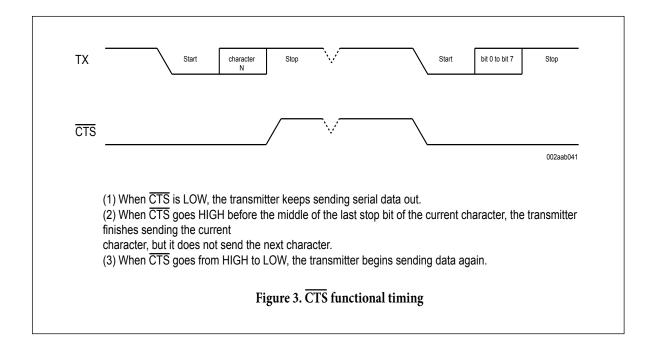

- Automatic RTS/CTS Flow Control

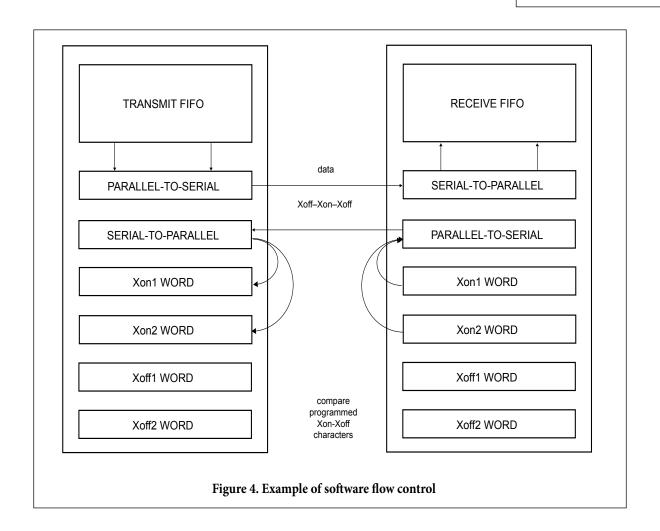

- Automatic Xon/Xoff Software Flow Control with Optional Data Flow Resume by Xon Any Character

- → DMA Signaling Capability for both Received and Transmitted Data

- RS485 HDX Control Output

- RS485 auto address detection

- □ Infrared (IrDA 1.0/1.1) Data Encoder/Decoder

- Programmable Data Rate with Prescaler

- → Up to 16 Mbps Serial Data Rate with 64MHz external clock input

- → Crystal oscillator(up to 24MHz) or external clock(up to 80MHz) input

- → Built in Power-On-Reset circuit

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

#### Description

The PI7C9X754 (754), is a 1.62V to 3.6V quad Universal Asynchronous Receiver and Transmitter (UART) with 5V tolerant serial (modem) inputs. The highly integrated device is designed for high bandwidth requirement in communication systems. Each UART has its own 16C550 compatible set of configuration registers, TX and RX FIFOs of 64 bytes, fully programmable transmit and receive FIFO trigger levels, TX and RX FIFO level counters, automatic RTS/CTS hardware flow control with programmable hysteresis, automatic software (Xon/Xoff) flow control, RS-485 half-duplex direction control, Intel or Motorola bus interface and sleep mode for power saving.

## **Application**

- → Remote Access Servers

- → Ethernet Network to Serial Ports

- → Network Management

- → Factory Automation and Process Control

- → Point-of-Sale Systems

- → Multi-port RS-232/RS-422/RS-485 Cards

#### Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

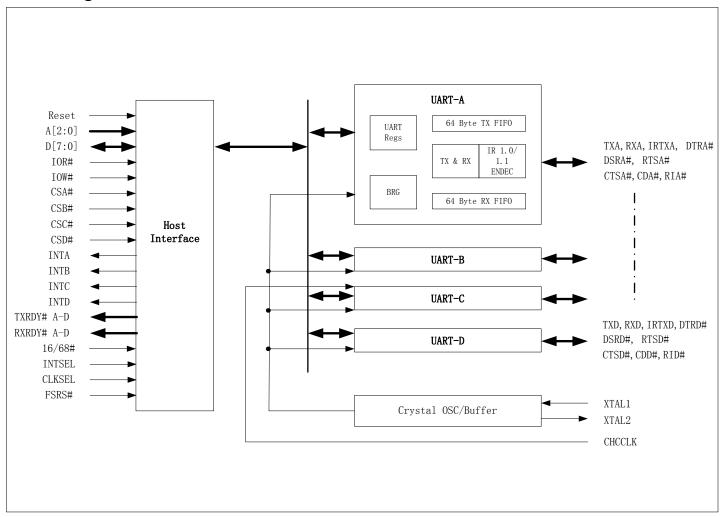

# **Block Diagram**

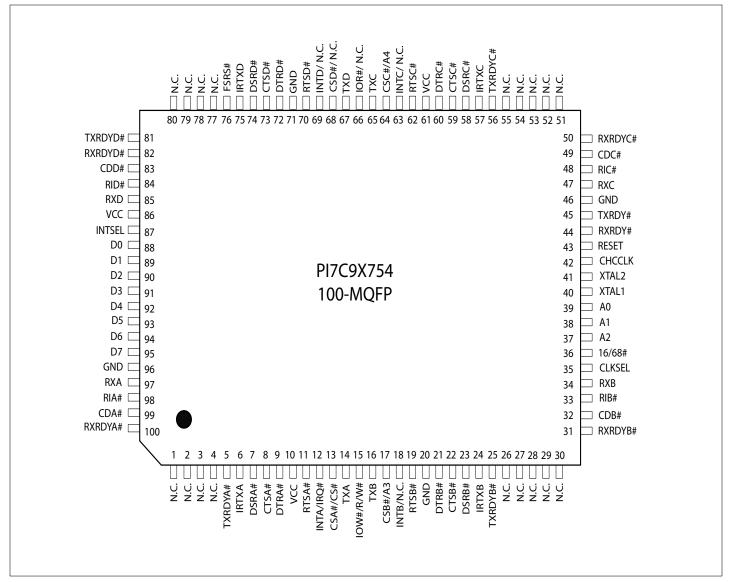

# **Pin Configuration 100-MQFP**

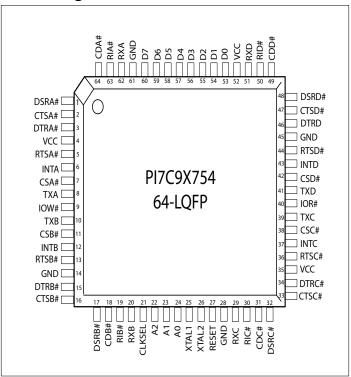

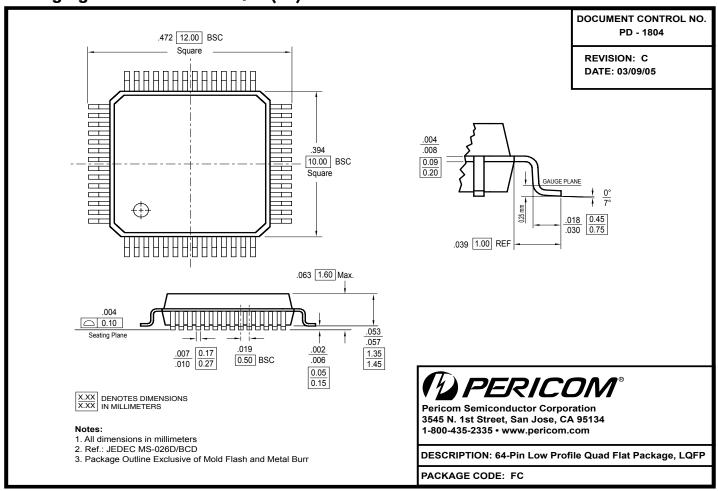

# **Pin Configuration 64-LQFP**

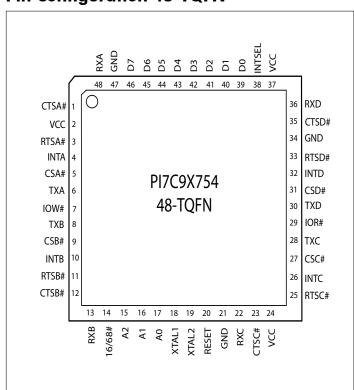

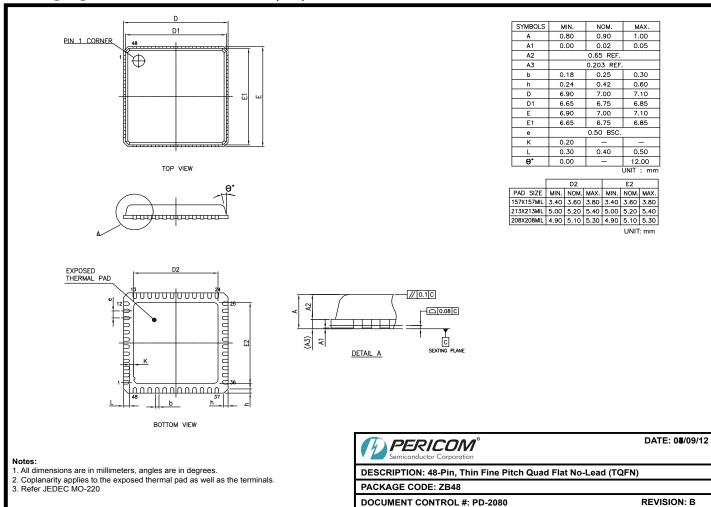

# **Pin Configuration 48-TQFN**

4

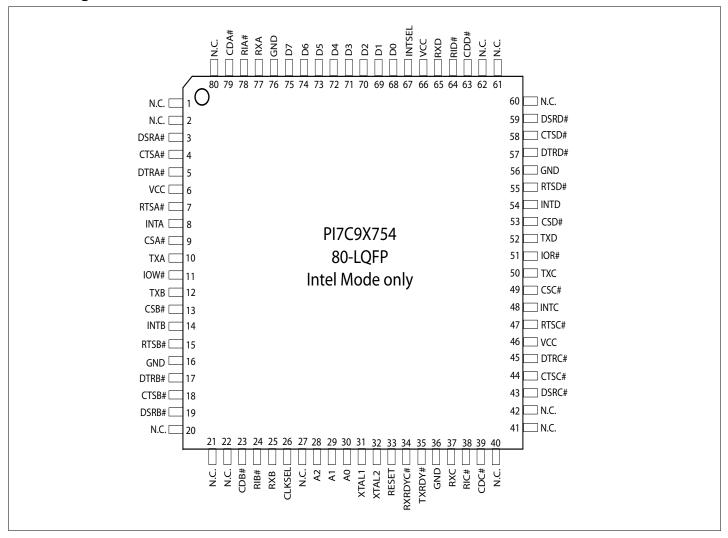

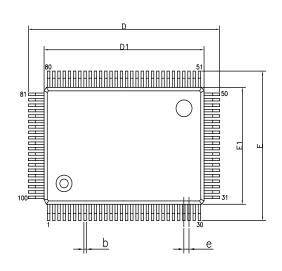

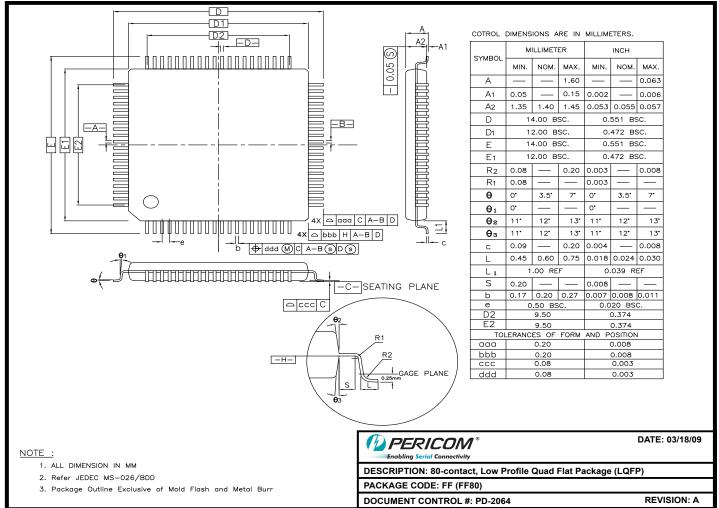

# **Pin Configuration 80-LQFP**

**Pin Description**

| Pin            | 48-QFP   | 64-QFP | 80-QFP | 100-<br>QFP |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|----------|--------|--------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name           | Pin#     | Pin#   | Pin#   | Pin#        | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Data Bus I     | nterface |        | '      |             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A2             | 15       | 22     | 28     | 37          |      | Address data lines [2:0]. These 3 address lines select one of                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A1             | 16       | 23     | 29     | 38          | I    | the internal registers in UART channel A-D during a data bus                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A0             | 17       | 24     | 30     | 39          |      | transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D7             | 46       | 60     | 75     | 95          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D6             | 45       | 59     | 74     | 94          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D5             | 44       | 58     | 73     | 93          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D4             | 43       | 57     | 72     | 92          | I/O  | Data bus lines [7:0] (bidirectional).                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D3             | 42       | 56     | 71     | 91          | 1/0  | Data bus files [7.0] (bluffectional).                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D2             | 41       | 55     | 70     | 90          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D1             | 40       | 54     | 69     | 89          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D0             | 39       | 53     | 68     | 88          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IOR#           | 29       | 40     | 51     | 66          | I    | When 16/68# pin is HIGH, the Intel bus interface is selected and this input becomes read strobe (active low). The falling edge instigates an internal read cycle and retrieves the data byte on the data bus to allow the host processor to read it on the rising edge.  When 16/68# pin is LOW, the Motorola bus interface is                                                                                                                                                          |

| IOW#<br>(R/W#) | 7        | 9      | 11     | 15          | I    | selected and this input is not used and should be connected to VCC.  When 16/68# pin is HIGH, it selects Intel bus interface and this input becomes write strobe (active low). The falling edge instigates the internal write cycle and the rising edge transfers the data byte on the data bus to an internal register pointed by the address lines.  When 16/68# pin is LOW, the Motorola bus interface is selected and this input becomes read (logic 1) and write (logic 0) signal. |

| CSA#(CS#)      | 5        | 7      | 9      | 12          | I    | When 16/68# pin is HIGH, this input is chip select A (active low) to enable channel A in the device.  When 16/68# pin is LOW, this input becomes the chip selected (active low) for the Motorola bus interface.                                                                                                                                                                                                                                                                         |

| CSB#(A3)       | 9        | 11     | 13     | 17          | I    | When 16/68# pin is HIGH, this input is chip select B (active low) to enable channel B in the device.  When 16/68# pin is LOW, this input becomes address line A3 which is used for channel selection in the Motorola bus interface.                                                                                                                                                                                                                                                     |

| Pin<br>Name                     | 48-QFP<br>Pin# | 64-QFP<br>Pin# | 80-QFP<br>Pin# | 100-<br>QFP<br>Pin# | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------|----------------|----------------|----------------|---------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSC#(A4)                        | 27             | 38             | 49             | 64                  | I      | When 16/68# pin is HIGH, this input is chip selected C (active low) to enable channel C in the device.  When 16/68# pin is LOW, this input becomes address line A4 which is used for channel selection in the Motorola bus                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CSD#<br>(VCC)                   | 31             | 42             | 53             | 68                  | I      | interface.  When 16/68# pin is HIGH, this input is chip select D (active low) to enable channel D in the device.  When 16/68# pin is LOW, this input is not used and should be connected VCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| INTA<br>(IRQ#)                  | 4              | 6              | 8              | 12                  | O (OD) | When 16/68# pin is HIGH for Intel bus interface, this output becomes channel A interrupt output. The output state is defined by the user and through the software setting of MCR[3]. INTA is set to a logic 0 (default). See MCR[3].                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| (IRQ#)                          |                |                |                |                     |        | When 16/68# pin is LOW for Motorola bus interface this output becomes device interrupt output (active low, open drain). An external pull-up resistor is required for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| INTB<br>INTC<br>INTD<br>(N.C.)  | 10<br>26<br>32 | 12<br>37<br>43 | 14<br>48<br>54 | 18<br>63<br>69      | О      | When 16/68# pin is HIGH for Intel bus interface, these outputs become the interrupt output for channel B, C and D. The output state is defined by the user through the software setting of MCR[3]. The interrupt outputs are set to the active mode when MCR[3] is set to a logic 1 and are set to the three state mode when MCR[3] is set to a logic 0 (default). See MCR[3].                                                                                                                                                                                                                                                                                                    |

|                                 |                |                |                |                     |        | When 16/68# pin is LOW for Motorola bus interface, these outputs ate unused and will stay at logic zero level. Leave these outputs unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INTSEL                          | 38             | -              | 67             | 87                  | I      | Interrupt Select (active high, input with internal pull-down.) When 16/68# pin is HIGH for Intel bus interface, this pin can be used in conjunction with MCR bit-3 to enable the interrupt outputs. Interrupt outputs are enabled continuously when this pin is HIGH. MCR bit-3 enables and disables the interrupt output pins. In this mode, MCR bit-3 is set to a logic 1 to enable the continuous outputs. See MCR bit-3 description for full detail. This pin must be LOW in the Motorola bus interface mode. For the 64 pin packages, this pin is bonded to GND internally in the PI7C9X754 and therefore requires setting MCR bit-3 for enabling the interrupt output pins. |

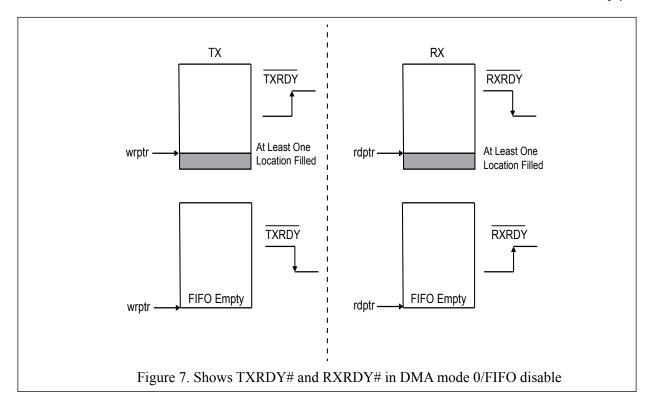

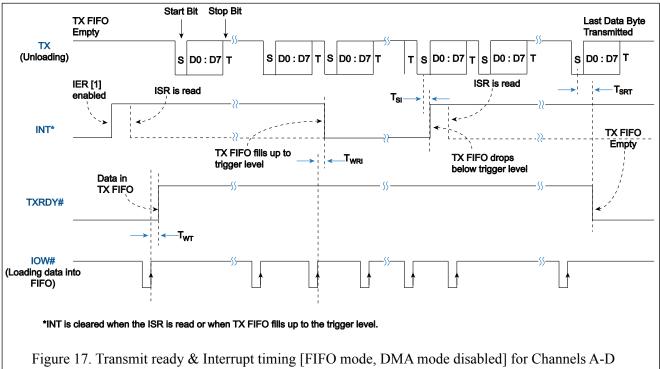

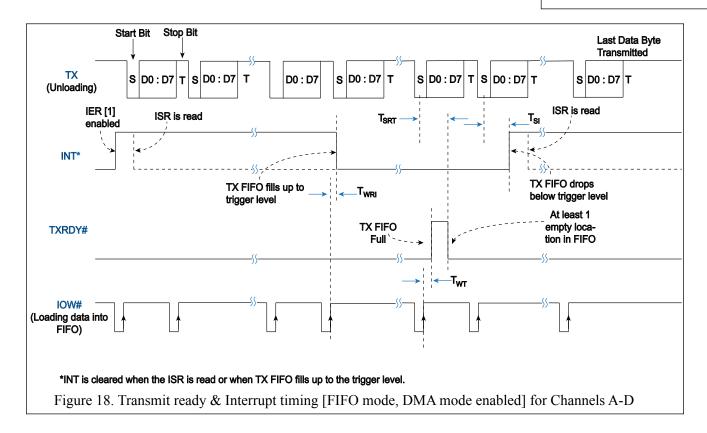

| TXRDYA# TXRDYB# TXRDYC# TXRDYD# | -              | -<br>-<br>-    | -              | 5<br>25<br>56<br>81 | 0      | UART channels A-D Transmitter Ready (active low). The outputs provide the TXFIFO/THR status for transmit channels A-D. If these outputs are unused, leave them unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

April 2019

| Pin<br>Name             | 48-QFP<br>Pin#     | 64-QFP<br>Pin#      | 80-QFP<br>Pin#       | 100-<br>QFP<br>Pin#  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------|--------------------|---------------------|----------------------|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

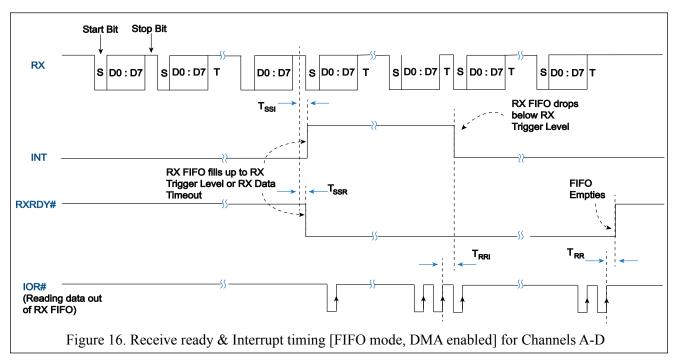

| RXRDYA#                 | -                  | -                   | -                    | 100                  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RXRDYB#                 | -                  | -                   | -                    | 31                   | _    | UART channels A-D Receiver Ready (active low). This output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RXRDYC#                 | _                  | _                   | -                    | 50                   | О    | provides the RXFIFO/RHR status for receive channels A-D. If these outputs are unused, leave them unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RXRDYD#                 | _                  | _                   | -                    | 82                   |      | these outputs are unused, leave them unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TXRDY#                  | -                  | -                   | 35                   | 45                   | О    | Transmitter Ready (active low). This output is a logically ANDed status of TXRDY# A-D. If this output is unused, leave it unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RXRDY#                  | -                  | -                   | 34                   | 44                   | О    | Transmitter Ready (active low). This output is a logically ANDed status of RXRDY# A-D. If this output is unused, leave it unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                         |                    |                     |                      |                      |      | FIFO Status Register Select (active low input with internal pull-up)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FSRS#                   | -                  | -                   | -                    | 76 I                 |      | The content of the FSTAT register is placed on the data bus when this pin becomes active. However it should be noted, D0-D3 contain the inverted logic states of TXRDY# A-D pins and D4-D7 the logic states (uninverted) of RXRDY# A-D pins. A valid address is not required when reading this status register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Modem Or                | Serial I/C         | ) Interface         | !                    |                      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TXA TXB TXC TXD         | 6<br>8<br>28<br>30 | 8<br>10<br>39<br>41 | 10<br>12<br>50<br>52 | 14<br>16<br>65<br>67 | О    | UART channels A-D Transmit Data and infrared transmit data. Standard transmit and receive interface is enabled when ASR[1] = 0. In this mode, the TX signal will be a logic 1 during reset, or idle (no data). Infrared IrDA transmit and receive interface is enabled when ASR[1] = 1. In the infrared mode, the inactive state (no data) for the Infrared encoder/decoder interface is a logic 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IRTXA IRTXB IRTXC IRTXD | -<br>-<br>-        | -<br>-<br>-         | -                    | 6<br>24<br>57<br>75  | О    | UART channel A-D Infrared Transmit Data. The inactive state (no data) for the Infrared encoder/decoder interface is LOW. Regardless of the logic state of ASR bit-1, this pin will be operating in the Infrared mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RXA                     | 48                 | 62                  | 77                   | 97                   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RXB                     | 13                 | 20                  | 25                   | 34                   |      | UART channel A-D Receive Data or infrared receive data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RXC                     | 22                 | 29                  | 37                   | 47                   | I    | Normal receive data input must idle HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RXD                     | 36                 | 51                  | 65                   | 85                   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RTSA#                   | 3                  | 5                   | 7                    | 11                   |      | HADE I LADD AND A CONTROL OF THE CON |

| RTSB#                   | 11                 | 13                  | 15                   | 19                   |      | UART channels A-D Request-to-Send (active low) or general purpose output. This output must be asserted prior to using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RTSC#                   | 25                 | 36                  | 47                   | 62                   | О    | auto RTS flow control, see EFR[6], MCR[1], and IER[6]. If                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RTSD#                   | 33                 | 44                  | 55                   | 70                   |      | these outputs are not used, leave them unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                         | 33                 | 1.1                 | 33                   | ı. <b>V</b>          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Pin<br>Name | 48-QFP<br>Pin# | 64-QFP<br>Pin# | 80-QFP<br>Pin# | 100-<br>QFP<br>Pin# | Туре | Description                                                                                                                                                                                                                                                                 |

|-------------|----------------|----------------|----------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTSA#       | 1              | 2              | 4              | 8                   |      | LIDAT shampels A.D. Class to Cond (active law) on general                                                                                                                                                                                                                   |

| CTSB#       | 12             | 16             | 18             | 22                  | _    | URAT channels A-D Clear-to-Send (active low) or general purpose input. It can be used for auto CTS flow control, see                                                                                                                                                        |

| CTSC#       | 23             | 33             | 44             | 59                  | I    | EFR[7], and IER[7]. These input should be connected to VCC                                                                                                                                                                                                                  |

| CTSD#       | 35             | 47             | 58             | 73                  |      | when not used.                                                                                                                                                                                                                                                              |

| DTRA#       | -              | 3              | 5              | 9                   |      |                                                                                                                                                                                                                                                                             |

| DTRB#       | -              | 15             | 17             | 21                  |      | UART channels A-D Data-Terminal-Ready (active low) or                                                                                                                                                                                                                       |

| DTRC#       | -              | 34             | 45             | 60                  | О    | general purpose output. If these outputs are not used, leave them unconnected.                                                                                                                                                                                              |

| DTRD#       | -              | 46             | 57             | 72                  |      | them unconnected.                                                                                                                                                                                                                                                           |

| DSRA#       | -              | 1              | 3              | 7                   |      |                                                                                                                                                                                                                                                                             |

| DSRB#       | _              | 17             | 19             | 23                  |      | UART channels A-D Data-Set-Ready (active low) or general                                                                                                                                                                                                                    |

| DSRC#       | _              | 32             | 43             | 58                  | I    | purpose input. This input should be connected to VCC when not used. This input has no effect on the UART.                                                                                                                                                                   |

| DSRD#       | -              | 48             | 59             | 74                  |      | not used. This input has no effect on the OAKI.                                                                                                                                                                                                                             |

| CDA#        | _              | 64             | 79             | 99                  |      |                                                                                                                                                                                                                                                                             |

| CDB#        | _              | 18             | 23             | 32                  |      | UART channels A-D Carrier-Detect (active low) or general                                                                                                                                                                                                                    |

| CDC#        | _              | 31             | 39             | 49                  | I    | purpose input. This input should be connected to VCC when not used. This input has no effect on the UART.                                                                                                                                                                   |

| CDD#        | -              | 49             | 63             | 83                  |      |                                                                                                                                                                                                                                                                             |

| RIA#        | _              | 63             | 78             | 98                  |      |                                                                                                                                                                                                                                                                             |

| RIB#        | _              | 19             | 24             | 33                  | _    | UART channels A-D Ring-Indicator (active low) or general                                                                                                                                                                                                                    |

| RIC#        | _              | 30             | 38             | 48                  | I    | purpose input. This input should be connected to VCC when not used. This input has no effect on the UART.                                                                                                                                                                   |

| RID#        | -              | 50             | 64             | 84                  |      | not used. This input has no effect on the OAKI.                                                                                                                                                                                                                             |

| Ancillary   | Signals        | 1              |                |                     |      |                                                                                                                                                                                                                                                                             |

| XTAL1       | 18             | 25             | 31             | 40                  | I    | Crystal or external clock input. Caution: this input is not 5V tolerant.                                                                                                                                                                                                    |

| XTAL2       | 19             | 26             | 32             | 41                  | О    | Crystal or buffered clock output.                                                                                                                                                                                                                                           |

|             |                | 20             | 32             | 11                  |      | Intel or Motorola Bus Select (input with internal pull-up).                                                                                                                                                                                                                 |

|             |                |                |                |                     |      | When 16/68# pin is HIGH, 16 or Intel Mode, the device will operate in the Intel bus type of interface.                                                                                                                                                                      |

| 16/68#      | 14             | -              | -              | 36                  | I    | When 16/68# pin is LOW, 68 or Motorola mode, the device will operate in the Motorola bus type of interface.                                                                                                                                                                 |

|             |                |                |                |                     |      | Motorola bus interface is not available on the 64 pin package.                                                                                                                                                                                                              |

| CLKSEL      | -              | 21             | 26             | 35                  | I    | Baud-Rate-Generator Input Clock Prescaler Select for channels A-D. This input is only sampled during power up or a reset. Connect to VCC for divide by 1 (default) and GND for divide by 4. MCR[7] can over-ride the state of this pin following a reset of initialization. |

| Pin<br>Name       | 48-QFP<br>Pin# | 64-QFP<br>Pin#    | 80-QFP<br>Pin#    | 100-<br>QFP<br>Pin# | Туре                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|----------------|-------------------|-------------------|---------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|