Real-time Clock Module (I<sup>2</sup>C Bus)

#### **Features**

- → Using external 32.768kHz quartz crystal for PT7C4337A

- → Using internal 32.768kHz quartz crystal for PT7C4337AC

- → Supports I<sup>2</sup>C-Bus's high speed mode (400 kHz)

- → Includes time (Hour/Minute/Second) and calendar (Year/Month/Date/Day) counter functions (BCD code)

- → Programmable square wave output signal

- → Two Time-of-Day Alarms

- → Oscillator Stop Flag

- → Operating range: 1.8V to 5.5V

- → Timekeeping range: 1.2V to 1.8V

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

- → For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative.

https://www.diodes.com/quality/product-definitions/

- → Packaging

- 8-Pin, SOIC (W)

- 8-Pin, MSOP (U)

- 8-Pin, TSSOP (L)

- 16-Pin, SOIC (S)

### **Description**

The PT7C4337A/4337AC serial real-time clock is a low-power clock/calendar with two programmable time-of-day alarms and a programmable square-wave output.

Address and data are transferred serially via a 2-wire, bidirectional bus. The clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with AM/PM indicator.

The device is fully accessible through the serial interface while VCC is between 1.8V and 5.5V. I2C operation is not guaranteed below 1.8V. Timekeeping operation is maintained with VCC as low as 1.2V.

Table 1 shows the basic functions of PT7C4337A/ 4337AC. More details are shown in section: overview of functions.

Table 1. Basic functions of PT7C4337A/4337AC

| Item                                        | Function                               |                                 |                            | PT7C4337A                  | PT7C4337AC         |

|---------------------------------------------|----------------------------------------|---------------------------------|----------------------------|----------------------------|--------------------|

|                                             |                                        | Source                          | Crystal(32.768KHz)         | External crystal           | Integrated Crystal |

| 1                                           | Oscillator                             | Oscillator ena                  | able/disable               | V                          | √                  |

|                                             |                                        | Oscillator fail detect          |                            | √                          | √                  |

|                                             | Time                                   | Time                            | 12-hour                    | √                          | √                  |

| 2                                           |                                        | display                         | 24-hour                    | √                          | √                  |

| 2                                           |                                        | Century bit                     |                            | √                          | √                  |

|                                             |                                        | Time count chain enable/disable |                            | √                          | $\checkmark$       |

| 3                                           | Interrupt                              | Alarm interru                   | pt output                  | √2                         | √2                 |

| 4                                           | 4 Programmable square wave output (Hz) |                                 | 1, 4.096k, 8.192k, 32.768k | 1, 4.096k, 8.192k, 32.768k |                    |

| 5 Communication 2-wire I <sup>2</sup> C bus |                                        | V                               | V                          |                            |                    |

#### Notes

<sup>1.</sup> No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

<sup>2.</sup> See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

August 2020

© Diodes Incorporated

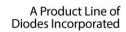

# **Pin Configuration**

### **Pin Description**

|               | •                      |          |      |                                                                                                                                                                                                      |

|---------------|------------------------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4337A<br>Pin# | 4337AC<br>SOIC<br>Pin# | Pin      | Type | Description                                                                                                                                                                                          |

| 1             | /                      | X1       | I    | <b>Oscillator Circuit Input.</b> Together with X1, 32.768kHz crystal is connected between them. Or external clock input.                                                                             |

| 2             | /                      | X2       | О    | <b>Oscillator Circuit Output.</b> Together with X1, 32.768kHz crystal is connected between them. When 32.768kHz external input, X2 must be float.                                                    |

| 6             | 1                      | SCL      | I    | <b>Serial Clock Input.</b> SCL is used to synchronize data movement on the I <sup>2</sup> C serial interface.                                                                                        |

| 5             | 16                     | SDA      | I/O  | <b>Serial Data Input/Output.</b> SDA is the input/output pin for the 2-wire serial interface. The SDA pin is open-drain output and requires an external pull-up resistor.                            |

| 3             | 14                     | ĪNTA     | О    | <b>Interrupt Output.</b> When enabled, INTA is asserted low when the time matches the values set in the alarm registers. This pin is an open-drain output and requires an external pull up resistor. |

| 7             | 2                      | SQW/INTB | О    | <b>Square-Wave/Interrupt Output.</b> Programmable square-wave or interrupt output signal. It is an open-drain output and requires an external pull up resistor.                                      |

| 8             | 3                      | VCC      | P    | <b>Power.</b> Primary power for PT7C4337A.                                                                                                                                                           |

| 4             | 15                     | GND      | P    | Ground.                                                                                                                                                                                              |

| /             | 5-13                   | NC       |      | <b>No Connect.</b> These pins are not connected internally, but must be grounded for proper operation.                                                                                               |

### **Maximum Ratings**

| Storage Temperature                                      | 65°C to +150°C           |

|----------------------------------------------------------|--------------------------|

| Supply Voltage to Ground Potential (V <sub>CC</sub> to C | GND)0.3V to +6.5V        |

| DC Input (All Other Inputs except Vcc & GND)             | -0.3V to (Vcc +0.3V)     |

| DC Output Voltage (SDA, /INTA, /INTB pins)               | -0.3V to +6.5V           |

| DC Output Current (FOUT)                                 | 0.3V to (Vcc +0.3V)      |

| Power Dissipation                                        | 320mW(depend on package) |

| Junction Temperature                                     | 125°C max                |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Operating Mode**

The amount of current consumed by the PT7C4337A is determined, in part, by the  $I^2C$  interface and oscillator operation. The following table shows the relationship between the operating mode and the corresponding  $I_{CC}$  parameter.

| Operating Mode                                           | $\mathbf{V}_{\mathrm{CC}}$ | Power                                       |

|----------------------------------------------------------|----------------------------|---------------------------------------------|

| I <sup>2</sup> C Interface Active                        | $1.8V \le V_{CC} \le 5.5V$ | I <sub>CC</sub> Active (I <sub>CCA</sub> )  |

| I <sup>2</sup> C Interface Inactive                      | $1.8V \le V_{CC} \le 5.5V$ | I <sub>CC</sub> Standby (I <sub>CCS</sub> ) |

| I <sup>2</sup> C Interface Inactive                      | $1.2V \le V_{CC} \le 1.8V$ | Timekeeping (I <sub>CCTOSC</sub> )          |

| I <sup>2</sup> C Interface Inactive, Oscillator Disabled | $1.2V \le V_{CC} \le 1.8V$ | Data Retention (I <sub>CCTDDR</sub> )       |

**Recommended Operating Conditions**

| Part No.                | Sym.             | Descri                         | Description    |             | Type | Max                  | Unit       |

|-------------------------|------------------|--------------------------------|----------------|-------------|------|----------------------|------------|

|                         | $V_{CC}$         | V supply voltage               | 1.8            | 3.3         | 5.5  | V                    |            |

|                         | V <sub>CCT</sub> | V <sub>CC</sub> supply voltage | 1.2            | -           | 1.8  |                      |            |

|                         | $V_{OSC}$        | Oscillator start up voltage    | 1.2            | -           | 5.5  |                      |            |

| PT7C4337A<br>PT7C4337AC | $V_{IH}$         | Input high level               | SCL, SDA       | $0.7V_{CC}$ | -    | V <sub>CC</sub> +0.3 |            |

|                         |                  |                                | ĪNTĀ, SQW/ĪNTB | -           | -    | 5.5                  |            |

|                         | $V_{\rm IL}$     | Input low level                |                | -0.3        | -    | $0.3V_{CC}$          |            |

| -                       | $T_A$            | Operating temperature          |                | -40         | -    | 85                   | $^{\circ}$ |

### **DC** Electrical Characteristics

Unless otherwise specified,  $V_{CC} = 1.8 \sim 5.5 \text{V}$ ,  $T_A = -40 \text{ °C to } +85 \text{ °C}$

| Sym.             | Item                     | Pin               | Condition            | Min         | Тур  | Max                  | Unit |

|------------------|--------------------------|-------------------|----------------------|-------------|------|----------------------|------|

| V <sub>CC</sub>  | Supply voltage           | V <sub>CC</sub>   | Full operation       | 1.8         | -    | 5.5                  | V    |

| V <sub>CCT</sub> | Supply voltage           | V CC              | Timekeeping (Note 5) | 1.2         | -    | 1.8                  |      |

| V <sub>OSC</sub> | Oscillator voltage       | V <sub>CC</sub>   |                      | 1.2         | -    | 5.5                  | V    |

| $V_{IL1}$        | Low-level input voltage  | SCL               |                      | -0.3        | -    | $0.3V_{CC}$          | V    |

| $V_{\rm IH1}$    | High-level input voltage | SCL               |                      | $0.7V_{CC}$ | -    | V <sub>CC</sub> +0.3 | •    |

| $V_{IL2}$        | Low-level input voltage  | X1                |                      | -           | 0.53 | -                    | V    |

| V <sub>IH2</sub> | High-level input voltage | X1                |                      | -           | 0.53 | -                    | •    |

| I <sub>OL</sub>  | Low-level output current | SDA, /INTA, /INTB | $V_{OL} = 0.4V$      | 3           | -    | -                    | mA   |

| $I_{IL}$         | Input leakage current    | SCL               |                      | -1          | -    | 1                    | μΑ   |

| $I_{OZ}$         | Output current when OFF  | SDA, /INTA, /INTB |                      | -1          | -    | 1                    | μΑ   |

### **DC Electrical Characteristics**

| Sym.                | Item                                                                                                                    | Pin             | Condition    | Min | Тур | Max | Unit |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|-----|-----|-----|------|--|--|

| Unless oth          | Juless otherwise specified, $V_{CC} = 1.3 \sim 1.8 \text{V}$ , $T_A = -40  ^{\circ}\text{C}$ to $+85  ^{\circ}\text{C}$ |                 |              |     |     |     |      |  |  |

| I <sub>CCTOSC</sub> | Timekeeping current                                                                                                     | V <sub>CC</sub> | Note 2, 4, 5 | -   | 450 | 800 | nA   |  |  |

| I <sub>CCTDDR</sub> | Data retention current                                                                                                  | V <sub>CC</sub> | Note 2,4,5,6 | -   | -   | 160 | IIA  |  |  |

| Unless of           | Unless otherwise specified, $V_{CC} = 1.8 \sim 3.6 \text{V}$ , $T_A = -40  ^{\circ}\text{C}$ to $+85  ^{\circ}\text{C}$ |                 |              |     |     |     |      |  |  |

| $I_{CCA}$           | Active supply current                                                                                                   | V <sub>CC</sub> | Note 1, 5    | -   | -   | 100 | ^    |  |  |

| $I_{CCS}$           | Standby current                                                                                                         | V <sub>CC</sub> | Note 2, 3, 5 | -   | 0.6 | 1.0 | μΑ   |  |  |

| Unless of           | Unless otherwise specified, $V_{CC} = 3.6 \sim 5.5 \text{V}$ , $T_A = -40 ^{\circ}\text{C}$ to $+85 ^{\circ}\text{C}$   |                 |              |     |     |     |      |  |  |

| $I_{CCA}$           | Active supply current                                                                                                   | V <sub>CC</sub> | Note 1, 5    | -   | -   | 150 | ^    |  |  |

| $I_{CCS}$           | Standby current                                                                                                         | V <sub>CC</sub> | Note 2, 3, 5 | -   | 1.0 | 1.8 | μΑ   |  |  |

#### Note:

- SCL clocking at max frequency = 400 kHz,  $V_{IL} = 0.0 \text{V}$ ,  $V_{IH} = \text{VCC}$ . Specified with 2-wire bus inactive,  $V_{IL} = 0.0 \text{V}$ ,  $V_{IH} = \text{VCC}$ . 1.

- 2.

- 3. SOW enabled.

- 4. Specified with the SQW function disabled by setting INTCN = 1. Using recommended crystal on X1 and X2.

- 5.

- Crystal oscillator is disabled.

### **Frequency Characteristics**

### **PT4337AC**

| Sym.           | Description                           | Condition                                                     | Rating               | Unit                          |

|----------------|---------------------------------------|---------------------------------------------------------------|----------------------|-------------------------------|

| $\Delta f / f$ | Frequency tolerance                   | $T_A = +25$ °C<br>$V_{DD} = 3.3$ V                            | Stability AC: 0 ± 30 | × 10 <sup>-6</sup>            |

| f/V            | Frequency voltage characteristics     | $T_A = +25 ^{\circ}C$ $V_{DD} = 2 \text{ V to 5 V}$           | ± 2 Max.             | $\times$ 10 <sup>-6</sup> / V |

| Тор            | Frequency temperature characteristics | $T_A = -10$ °C to +70°C,<br>$V_{DD} = 3.3$ V; +25°C reference | +10 / -120           | × 10 <sup>-6</sup>            |

| $t_{STA}$      | Oscillation start up time             | $T_A = +25$ °C<br>$V_{DD} = 3.3$ V                            | 3 Max.               | S                             |

| fa             | Aging                                 | $T_A = +25$ °C<br>$V_{DD}=3.0$ V; first year                  | ± 5 Max.             | × 10 <sup>-6</sup> / year     |

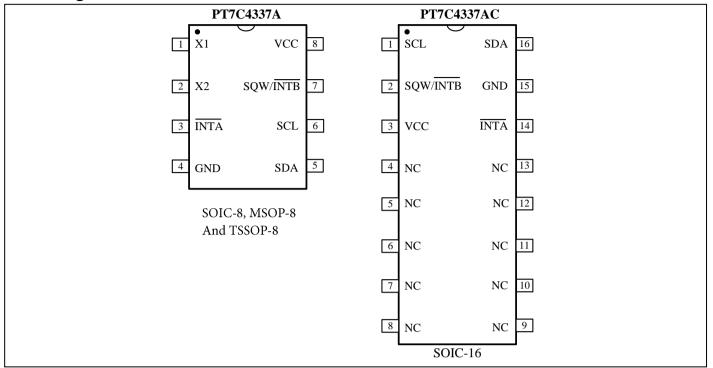

### Recommended Layout for Crystal (Only for PT7C4337A)

### **Built-in Capacitors Specifications and Recommended External Capacitors**

| Parameter                           |           | Symbol           | Тур | Unit |

|-------------------------------------|-----------|------------------|-----|------|

| Duild in conscitors                 | X1 to GND | $C_{\mathrm{G}}$ | 12  | pF   |

| Build-in capacitors                 | X2 to GND | $C_{\mathrm{D}}$ | 12  | pF   |

| Recommended External capacitors for | X1 to GND | $C_1$            | 12  | pF   |

| crystal C <sub>L</sub> =12.5pF      | X2 to GND | $C_2$            | 12  | pF   |

| Recommended External capacitors for | X1 to GND | $C_1$            | 0   | pF   |

| crystal C <sub>L</sub> =6pF         | X2 to GND | $C_2$            | 0   | pF   |

**Note**: The frequency of crystal can be optimized by external capacitor  $C_1$  and  $C_2$ , for frequency=32.768KHz,  $C_1$  and  $C_2$  should meet the equation as below:

$Cpar + [(C_1+C_G)*(C_2+C_D)]/[(C_1+C_G)+(C_2+C_D)] = C_L$

### Cpar is all parasitical capacitor between X1 and X2.

C<sub>L</sub> is crystal's load capacitance.

### **Crystal Specifications**

| Parameter         | Symbol           | Min | Тур    | Max | Unit |

|-------------------|------------------|-----|--------|-----|------|

| Nominal Frequency | $f_{O}$          | =   | 32.768 | -   | kHz  |

| Series Resistance | ESR              | -   | -      | 70  | kΩ   |

| Load Capacitance  | $C_{\mathrm{L}}$ | =   | 6/12.5 | -   | pF   |

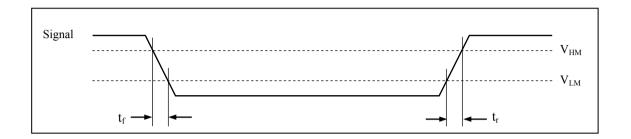

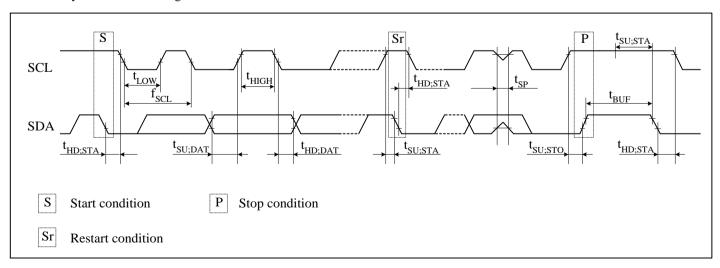

### **AC Electrical Characteristics**

|   | Sym               | Description                               | Value                 | Unit |

|---|-------------------|-------------------------------------------|-----------------------|------|

|   | $V_{\mathrm{HM}}$ | Rising and falling threshold voltage high | $0.8~\mathrm{V_{CC}}$ | V    |

| ĺ | $V_{ m HL}$       | Rising and falling threshold voltage low  | $0.2~\mathrm{V_{CC}}$ | V    |

#### Over the operating range

| Symbol               | Item                                             | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------------------|------|------|------|------|

| $f_{SCL}$            | SCL clock frequency                              | -    | -    | 400  | kHz  |

| t <sub>SU;STA</sub>  | START condition set-up time                      | 0.6  | -    | -    | μs   |

| t <sub>HD;STA</sub>  | START condition hold time                        | 0.6  | -    | -    | μs   |

| $t_{SU;DAT}$         | Data set-up time (RTC read/write)                | 200  | -    | -    | ns   |

| $t_{\rm HD;DAT1}$    | Data hold time (RTC write)                       | 35   | -    | -    | ns   |

| t <sub>HD;DAT2</sub> | Data hold time (RTC read)                        | 0    | -    | -    | μs   |

| $t_{\rm SU;STO}$     | STOP condition setup time                        | 0.6  | -    | -    | μs   |

| t <sub>BUF</sub>     | Bus idle time between a START and STOP condition | 1.3  | -    | -    | μs   |

| $t_{LOW}$            | When SCL = "L"                                   | 1.3  | -    | -    | μs   |

| t <sub>HIGH</sub>    | When SCL = "H"                                   | 0.6  | -    | -    | μs   |

| t <sub>r</sub>       | Rise time for SCL and SDA                        | -    | -    | 0.3  | μs   |

| $t_{\mathrm{f}}$     | Fall time for SCL and SDA                        | -    | -    | 0.3  | μs   |

| t <sub>SP</sub> *    | Allowable spike time on bus                      | -    | -    | 50   | ns   |

| $C_B$                | Capacitance load for each bus line               | -    | -    | 400  | pF   |

| C <sub>I/O</sub> *   | I/O Capacitance (SDA, SCL)                       | -    | -    | 10   | pF   |

| $T_{OSF}$            | Oscillator Stop Flag (OSF) Delay                 | -    | -    | 100  | ms   |

<sup>\*</sup> Note: only reference for design

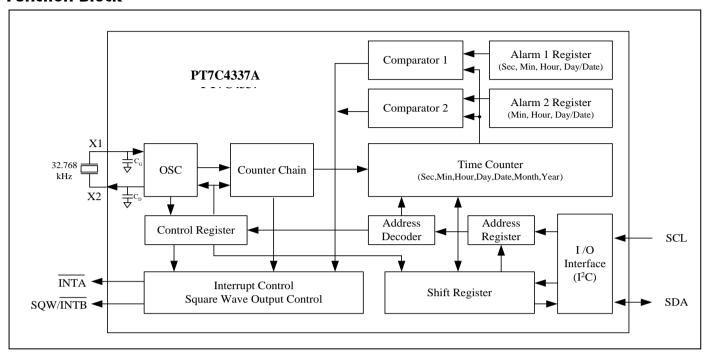

#### **Function Block**

#### **Oscillator Circuit**

#### PT7C4337A

The PT7C4337A uses an external 32.768 kHz crystal. Table2 specifies several crystal parameters for the external crystal. The *Block Diagram* shows a functional schematic of the oscillator circuit. The startup time is usually less than 1 second when using a crystal with the specified characteristics.

**Table 2. Crystal Specifications**

| Parameter         | Symbol  | Min | Тур    | Max | Unit      |

|-------------------|---------|-----|--------|-----|-----------|

| Nominal Frequency | $f_{O}$ | -   | 32.768 | =   | kHz       |

| Series Resistance | ESR     | -   | -      | 70  | $k\Omega$ |

| Load Capacitance  | $C_{L}$ | -   | 6/12.5 | =   | pF        |

Note: The crystal, traces, and crystal input pins should be isolated from RF generating signals.

#### **Clock Accuracy**

The accuracy of the clock is dependent upon the accuracy of the crystal and the accuracy of the match between the capacitive load of the oscillator circuit and the capacitive load for which the crystal was trimmed. Crystal frequency drift caused by temperature shifts creates additional error. External circuit noise coupled into the oscillator circuit can result in the clock running fast. Figure 1 shows a typical PC board layout for isolating the crystal and oscillator from noise.

### **PT7C4337AC**

The PT7C4337AC integrates a standard 32,768Hz crystal in the package. Typical accuracy at nominal VCC and  $+25^{\circ}$ C is approximately  $\pm 10$ ppm.

### **Function Description**

### **Overview of Functions**

#### **Clock Function**

CPU can read or write data including the year (last two digits), month, date, day, hour, minute, and second. Any (two-digit) year that is a multiple of 4 is treated as a leap year and calculated automatically as such until the year 2100. On a power-on reset (POR), the time and date are set to 00:00:00 01/01/00 (hh:mm:ss DD/MM/YY) and the Day register is set to 01.

#### **Alarm Function**

This device has two alarm system (Alarm 1 and Alarm 2) that outputs interrupt signals from INTA or INTB to CPU when the date, day of the week, hour, minute or second correspond to the setting. Each of them may output interrupt signal separately at a specified time. The alarm is be selectable between on and off for matching alarm or repeating alarm.

#### **Programmable Square Wave Output**

A square wave output enable bit controls square wave output at pin 7. Frequencies are selectable: 1, 4.096k, 8.192k, 32.768k Hz.

#### **Interface with CPU**

Data is read and written via the I<sup>2</sup>C bus interface using two signal lines: SCL (clock) and SDA (data).

Since the output of the I/O pin SDA is open drain, a pull-up resistor should be used on the circuit board if the CPU output I/O is also open drain.

The SCL's maximum clock frequency is 400 kHz, which supports the I<sup>2</sup>C bus's high-speed mode.

#### **Oscillator Fail Detect**

When oscillator fail, PT7C4337A OSF bit will be set.

#### Oscillator Enable/Disable

Oscillator and time count chain can be enabled or disabled at the same time by /ETIME bit.

#### **Registers**

Allocation of registers

| Addr.   | Function                 |         |               |              | Register  | definition |           |           |            |

|---------|--------------------------|---------|---------------|--------------|-----------|------------|-----------|-----------|------------|

| (hex)*1 | Function                 | Bit 7   | Bit 6         | Bit 5        | Bit 4     | Bit 3      | Bit 2     | Bit 1     | Bit 0      |

| 00      | Seconds (00-59)          | 0       | S40           | S20          | S10       | S8         | S4        | S2        | <b>S</b> 1 |

| 01      | Minutes (00-59)          | 0       | M40           | M20          | M10       | M8         | M4        | M2        | M1         |

| 02      | Hours (00-23 / 01-12)    | 0       | 12, /24       | H20 or P, /A | H10       | Н8         | H4        | Н2        | H1         |

| 03      | Days of the week (01-07) | 0       | 0             | 0            | 0         | 0          | W4        | W2        | W1         |

| 04      | Dates (01-31)            | 0       | 0             | D20          | D10       | D8         | D4        | D2        | D1         |

| 05      | Months (01-12)           | Century | 0             | 0            | MO10      | MO8        | MO4       | MO2       | MO1        |

| 06      | Years (00-99)            | Y80     | Y40           | Y20          | Y10       | Y8         | Y4        | Y2        | Y1         |

| 07      | Alarm 1: Seconds         | A1M1*2  | S40           | S20          | S10       | S8         | S4        | S2        | S1         |

| 08      | Alarm 1: Minutes         | A1M2*2  | M40           | M20          | M10       | M8         | M4        | M2        | M1         |

| 09      | Alarm 1: Hours           | A1M3*2  | 12, /24       | H20 or P, /A | H10       | Н8         | H4        | Н2        | H1         |

| 0A      | Alarm 1: Day, Date       | A1M4*2  | Day,<br>/Date | 0,<br>D20    | 0,<br>D10 | 0,<br>D8   | W4,<br>D4 | W2,<br>D2 | W1,<br>D1  |

| 0B      | Alarm 2: Minutes         | A2M2*3  | M40           | M20          | M10       | M8         | M4        | M2        | M1         |

| 0C      | Alarm 2: Hours           | A2M3*3  | 12, /24       | H20 or P, /A | H10       | Н8         | H4        | Н2        | H1         |

# A Product Line of Diodes Incorporated

### PT7C4337A/4337AC

| Addr.   | Function           | Register definition |               |           |           |          |           |           |           |  |

|---------|--------------------|---------------------|---------------|-----------|-----------|----------|-----------|-----------|-----------|--|

| (hex)*1 | Function           | Bit 7               | Bit 6         | Bit 5     | Bit 4     | Bit 3    | Bit 2     | Bit 1     | Bit 0     |  |

| 0D      | Alarm 2: Day, Date | A2M4*3              | Day,<br>/Date | 0,<br>D20 | 0,<br>D10 | 0,<br>D8 | W4,<br>D4 | W2,<br>D2 | W1,<br>D1 |  |

| 0E      | Control            | /ETIME*4            | 0             | 0         | RS2*5     | RS1*5    | INTCN*6   | A2IE*7    | A1IE*7    |  |

| 0F      | Status             | OSF <sup>*9</sup>   | 0             | 0         | 0         | 0        | 0         | A2F*8     | A1F*8     |  |

#### Caution points:

- \*1. PT7C4337A uses 8 bits for address. For excess 0FH address, PT7C4337A will not respond (no acknowledge signal was given).

- \*2. Alarm 1 mask bits. Select alarm repeated rate when an alarm occurs.

- \*3. Alarm 2 mask bits. Select alarm repeated rate when an alarm occurs.

- \*4. Oscillator and time count chain enable/disable bit.

- \*5. Square wave output frequency select.

- \*6. Interrupt output pin select bit.

- \*7. Alarm 1 and alarm 2 enable bits.

- \*8. Alarm 1 and alarm 2 flag bits.

- \*9. Oscillator stops flag.

- \*10. All bits marked with "0" are read-only bits. Their value when read is always "0".

### **Control and Status Register**

|             | 201101010101010101010101010101010101010 |           |    |    |     |     |       |           |           |  |  |  |

|-------------|-----------------------------------------|-----------|----|----|-----|-----|-------|-----------|-----------|--|--|--|

| Addr. (hex) | Description                             | <b>D7</b> | D6 | D5 | D4  | D3  | D2    | D1        | D0        |  |  |  |

| 0E          | Control                                 | /ETIME    | 0  | 0  | RS2 | RS1 | INTCN | A2IE      | A1IE      |  |  |  |

| UE          | (default)                               | 0         | 0  | 0  | 1   | 1   | 0     | 0         | 0         |  |  |  |

| 0F          | Status                                  | OSF       | 0  | 0  | 0   | 0   | 0     | A2F       | A1F       |  |  |  |

| UF          | (default)                               | 1         | 0  | 0  | 0   | 0   | 0     | Undefined | Undefined |  |  |  |

#### **Oscillator Related Bits**

#### • /ETIME

Enable oscillator and time count chain bit.

| /ETIME       | Data | Description                              |         |  |  |  |  |  |

|--------------|------|------------------------------------------|---------|--|--|--|--|--|

| Read / Write | 0    | Enable oscillator and time count chain.  | Default |  |  |  |  |  |

| Read / Wille | 1    | Disable oscillator and time count chain. |         |  |  |  |  |  |

#### OSF

### Oscillator Stops Flag.

A logic 1 in this bit indicates that the oscillator either is stopped or was stopped for some period of time and may be used to judge the validity of the clock and calendar data. This bit is set to logic 1 anytime that the oscillator stops. The following are examples of conditions that can cause the OSF bit to be set:

- 1) The first time power is applied.

- 2) The voltage present on VCC is insufficient to support oscillation.

- 3) The /ETIME bit is turned off.

- 4) External influences on the crystal (e.g., noise, leakage, etc.).

This bit remains at logic 1 until written to logic 0.

### **Square Wave Frequency Selection Bits**

#### • RS2, RS1

Square wave Rate Select. These bits control the frequency of the square-wave output when the square wave has been enabled.

| RS2, RS1     | Data | SQW output freq. (Hz) |         |

|--------------|------|-----------------------|---------|

|              | 00   | 1                     |         |

| Read / Write | 01   | 4.096k                |         |

| Read / Wille | 10   | 8.192k                |         |

|              | 11   | 32.768k               | Default |

#### **Interrupt Related Bits**

#### INTCN

Interrupt Output pin select bit. This bit controls the relationship between the two alarms and the interrupt output pins.

| INTCN  | Data | Description                                                                                                                                                                                                                                                    |

|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read / | 1    | A match between the timekeeping registers and the alarm 1 registers activates the INTA pin (if the alarm 1 is <u>enabled</u> ) and a match between the timekeeping registers and the alarm 2 registers activates the SQW/INTB pin (if the alarm 2 is enabled). |

| Write  | 0    | A match between the timekeeping registers and either alarm 1 or alarm 2 registers activates the INTA pin (if the alarms are enabled). In this configuration, a square wave is output on the SQW/INTB pin.                                                      |

#### A1IE

Alarm 1 Interrupt Enable.

| A1IE                                                          | Data | Description                                                               |  |  |  |

|---------------------------------------------------------------|------|---------------------------------------------------------------------------|--|--|--|

| Read / Write 0 The A1F bit does not initiate the INTA signal. |      |                                                                           |  |  |  |

|                                                               | 1    | Permits the alarm 1 flag (A1F) bit in the status register to assert INTA. |  |  |  |

### • A1F

Alarm 1 Flag.

| A1F          | Data | Description                                                                                                                                                                                  |         |

|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Read / Write | 0    | The time do not match the alarm 1 registers.                                                                                                                                                 | Default |

| Read         | 1    | Indicates that the time matched the alarm 1 registers. If the A1IE bit is also logic 1, the INT low. A1F is cleared when written to logic 0. Attempting to write to logic 1 leaves the value |         |

#### • **A2IE**

Alarm 2 Interrupt Enable.

| A2IE   | Data | Description                                                                                                                                                |       |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Read / | 0    | The A2F bit does not initiate an interrupt signal.                                                                                                         | fault |

| Write  | 1    | Permits the alarm 2 flag (A2F) bit in the status register to assert $\overline{INTA}$ (when INTCN = 0) or to asser $\overline{SQW/INTB}$ (when INTCN = 1). | t     |

### • A2F

Alarm 2 Flag.

| A1F             | Data | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read /<br>Write | 0    | The time do not match the alarm 2 registers.  Default                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Read            | 1    | Indicates that the time matched the alarm 1 registers. This flag can be used to generate an interrupt on either $\overline{\text{INTA}}$ or $\overline{\text{SQW/INTB}}$ depending on the status of the INTCN bit. If the INTCN = 0 and A2F = 1 (and A2IE = 1), the $\overline{\text{INTA}}$ pin goes low. If the INTCN = 1 and A2F = 1 (and A2IE = 1), the $\overline{\text{SQW/INTB}}$ pin goes low. A2F is cleared when written to logic 0. Attempting to write to logic 1 leaves the value unchanged. |

### **Time Counter**

Time digit display (in BCD code):

- Second digits: Range from 00 to 59 and carried to minute digits when incremented from 59 to 00.

- Minute digits: Range from 00 to 59 and carried to hour digits when incremented from 59 to 00.

- Hour digits: See description on the /12, 24 bit. Carried to day and day-of-the-week digits when incremented from 11 p.m. to 12 a.m. or 23 to 00.

| Addr. (hex) | Description | D7 | D6      | D5          | D4  | D3 | D2 | D1 | D0 |

|-------------|-------------|----|---------|-------------|-----|----|----|----|----|

| 00          | Seconds     | 0  | S40     | S20         | S10 | S8 | S4 | S2 | S1 |

| 00          | (default)   | 0  | 0       | 0           | 0   | 0  | 0  | 0  | 0  |

| 01          | Minutes     | 0  | M40     | M20         | M10 | M8 | M4 | M2 | M1 |

| 01          | (default)   | 0  | 0       | 0           | 0   | 0  | 0  | 0  | 0  |

| 02          | Hours       | 0  | 12, /24 | H20 or P,/A | H10 | Н8 | H4 | H2 | H1 |

|             | (default)   | 0  | 0       | 0           | 0   | 0  | 0  | 0  | 0  |

Note: Any registered imaginary time should be replaced with correct time, otherwise it will cause the clock counter malfunction.

### • 12, /24 bit

This bit is used to select between 12-hour clock system and 24-hour clock system.

| 12, /24      | Data | Description    |

|--------------|------|----------------|

| Read / Write | 0    | 24-hour system |

| Read / Write | 1    | 12-hour system |

This bit is used to select between 12-hour clock operation and 24-hour clock operation.

| 12, /24 | Description          |               | Hours         | register      |               |

|---------|----------------------|---------------|---------------|---------------|---------------|

|         |                      | 24-hour clock | 12-hour clock | 24-hour clock | 12-hour clock |

|         |                      | 00            | 52 ( AM 12 )  | 12            | 72 ( PM 12)   |

| 0       | 24 hove time display | 01            | 41 ( AM 01 )  | 13            | 61 ( PM 01 )  |

| U       | 24-hour time display | 02            | 42 ( AM 02 )  | 14            | 62 ( PM 02 )  |

|         |                      | 03            | 43 ( AM 03 )  | 15            | 63 ( PM 03 )  |

|         |                      | 04            | 44 ( AM 04 )  | 16            | 64 ( PM 04 )  |

|         |                      | 05            | 45 ( AM 05 )  | 17            | 65 ( PM 05 )  |

|         |                      | 06            | 46 ( AM 06 )  | 18            | 66 ( PM 06 )  |

|         |                      | 07            | 47 ( AM 07 )  | 19            | 67 ( PM 07 )  |

| 1       | 10.1                 | 08            | 48 ( AM 08 )  | 20            | 68 ( PM 08 )  |

| 1       | 12-hour time display | 09            | 49 ( AM 09 )  | 21            | 69 ( PM 09 )  |

|         |                      | 10            | 50 ( AM 10 )  | 22            | 70 ( PM 10 )  |

|         |                      | 11            | 51 ( AM 11 )  | 23            | 71 ( PM 11 )  |

<sup>\*</sup> Be sure to select between 12-hour and 24-hour clock operation before writing the time data.

### Days of the week Counter

The day counter is a divide-by-7 counter that counts from 01 to 07 and up 07 before starting again from 01. Values that correspond to the day of week are user defined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on). Illogical time and date entries result in undefined operation.

| Addr. (hex) | Description      | D7 | D6 | D5 | D4 | D3 | D2 | D1 | <b>D</b> 0 |

|-------------|------------------|----|----|----|----|----|----|----|------------|

| 03          | Days of the week | 0  | 0  | 0  | 0  | 0  | W4 | W2 | W1         |

| 0.5         | (default)        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1          |

#### **Calendar Counter**

The data format is BCD format.

• Day digits: Range from 1 to 31 (for January, March, May, July, August, October and December).

Range from 1 to 30 (for April, June, September and November).

Range from 1 to 29 (for February in leap years).

Range from 1 to 28 (for February in ordinary years).

Carried to month digits when cycled to 1.

- Month digits: Range from 1 to 12 and carried to year digits when cycled to 1.

- Year digits: Range from 00 to 99 and 00, 04, 08, ..., 92 and 96 are counted as leap years.

| Addr. (hex) | Description | D7        | D6  | D5  | D4  | D3 | D2 | D1 | <b>D</b> 0 |

|-------------|-------------|-----------|-----|-----|-----|----|----|----|------------|

| 04          | Dates       | 0         | 0   | D20 | D10 | D8 | D4 | D2 | D1         |

| 04          | (default)   | 0         | 0   | 0   | 0   | 0  | 0  | 0  | 1          |

| 05          | Months      | Century*1 | 0   | 0   | M10 | M8 | M4 | M2 | M1         |

|             | (default)   | 0         | 0   | 0   | 0   | 0  | 0  | 0  | 1          |

| 06          | Years       | Y80       | Y40 | Y20 | Y10 | Y8 | Y4 | Y2 | Y1         |

|             | (default)   | 0         | 0   | 0   | 0   | 0  | 0  | 0  | 0          |

<sup>\*1:</sup> The century bit is toggled when the years register overflows from 99 to 00.

### **Alarm Register**

### Alarm 1, Alarm 2 Register

| Addr. | Description        | <b>D7</b> | D6                          | D5          | D4        | D3        | D2        | D1        | <b>D</b> 0 |

|-------|--------------------|-----------|-----------------------------|-------------|-----------|-----------|-----------|-----------|------------|

| 07    | Alarm 1: Seconds   | A1M1*1    | S40                         | S20         | S10       | S8        | S4        | S2        | S1         |

| 07    | (default)          | Undefined | Undefined                   | Undefined   | Undefined | Undefined | Undefined | Undefined | Undefined  |

| 08    | Alarm 1: Minutes   | A1M2*1    | M40                         | M20         | M10       | M8        | M4        | M2        | M1         |

| 08    | (default)          | Undefined | Undefined                   | Undefined   | Undefined | Undefined | Undefined | Undefined | Undefined  |

| 09    | Alarm 1: Hours     | A1M3*1    | 12, /24                     | H20 or P,/A | H10       | Н8        | H4        | H2        | H1         |

| 09    | (default)          | Undefined | Undefined                   | Undefined   | Undefined | Undefined | Undefined | Undefined | Undefined  |

| 0.4   | Alarm 1: Day, Date | A1M4*1    | Day,<br>/Date <sup>*1</sup> | 0,<br>D20   | 0,<br>D10 | 0,<br>D8  | W4,<br>D4 | W2,<br>D2 | W1,<br>D1  |

| 0A    | (default)          | Undefined | Undefined                   | Undefined   | Undefined | Undefined | Undefined | Undefined | Undefined  |

| OD    | Alarm 2: Minutes   | A2M2*2    | M40                         | M20         | M10       | M8        | M4        | M2        | M1         |

| 0B    | (default)          | Undefined | Undefined                   | Undefined   | Undefined | Undefined | Undefined | Undefined | Undefined  |

| 00    | Alarm 2: Hours     | A2M3*2    | 12, /24                     | H20 or P,/A | H10       | Н8        | H4        | H2        | H1         |

| 0C    | (default)          | Undefined | Undefined                   | Undefined   | Undefined | Undefined | Undefined | Undefined | Undefined  |

| 0D    | Alarm 2: Day, Date | A2M4*2    | Day,<br>/Date <sup>*2</sup> | 0,<br>D20   | 0,<br>D10 | 0,<br>D8  | W4,<br>D4 | W2,<br>D2 | W1,<br>D1  |

|       | (default)          | Undefined | Undefined                   | Undefined   | Undefined | Undefined | Undefined | Undefined | Undefined  |

<sup>\*1</sup> Note: Alarm mask bit, using to select Alarm 1 alarm rate.

### **Alarm Function** Related Register

| Addr. | E                  |        |               |                 | Register  | definition |           |           |           |

|-------|--------------------|--------|---------------|-----------------|-----------|------------|-----------|-----------|-----------|

| (hex) | Function           | Bit 7  | Bit 6         | Bit 5           | Bit 4     | Bit 3      | Bit 2     | Bit 1     | Bit 0     |

| 00    | Seconds            | 0      | S40           | S20             | S10       | S8         | S4        | S2        | S1        |

| 01    | Minutes            | 0      | M40           | M20             | M10       | M8         | M4        | M2        | M1        |

| 02    | Hours              | 0      | 12, /24       | H20 or<br>A, /P | H10       | Н8         | H4        | Н2        | H1        |

| 03    | Days of the week   | 0      | 0             | 0               | 0         | 0          | W4        | W2        | W1        |

| 04    | Dates              | 0      | 0             | D20             | D10       | D8         | D4        | D2        | D1        |

| 07    | Alarm 1: Seconds   | A1M1   | S40           | S20             | S10       | S8         | S4        | S2        | S1        |

| 08    | Alarm 1: Minutes   | A1M2   | M40           | M20             | M10       | M8         | M4        | M2        | M1        |

| 09    | Alarm 1: Hours     | A1M3   | 12, /24       | H20 or<br>A, /P | H10       | Н8         | H4        | H2        | H1        |

| 0A    | Alarm 1: Day, Date | A1M4   | Day,<br>/Date | 0,<br>D20       | 0,<br>D10 | 0,<br>D8   | W4,<br>D4 | W2,<br>D2 | W1,<br>D1 |

| 0B    | Alarm 2: Minutes   | A2M2   | M40           | M20             | M10       | M8         | M4        | M2        | M1        |

| 0C    | Alarm 2: Hours     | A2M3   | 12, /24       | H20 or<br>A, /P | H10       | Н8         | H4        | Н2        | H1        |

| 0D    | Alarm 2: Day, Date | A2M4   | Day,<br>/Date | 0,<br>D20       | 0,<br>D10 | 0,<br>D8   | W4,<br>D4 | W2,<br>D2 | W1,<br>D1 |

| 0E    | Control            | /ETIME | 0             | 0               | RS2       | RS1        | INTCN     | A2IE      | A1IE      |

| 0F    | Status             | OSF    | 0             | 0               | 0         | 0          | 0         | A2F       | A1F       |

Note: Alarm function does not support different hour system adopted in time and alarm register.

<sup>\*2</sup> Note: Alarm mask bit, using to select Alarm 2 alarm rate.

The PT7C4337A contains two time-of-day/date alarms. The alarms can be programmed (by the INTCN bit of the control register) to operate in two different modes - each alarm can drive its own separate interrupt output or both alarms can drive a common interrupt output. Bit 7 of each of the time-of-day/date alarm registers are mask bits.

When all of the mask bits for each alarm are logic 0, an alarm only occurs when the values in the timekeeping registers  $00h \sim 04h$  match the values stored in the time-of-day/date alarm registers. The alarms can also be programmed to repeat every second, minute, hour, day, or date. Table 2 and Table 3 show the possible settings.

The Day, /Date bits (bit 6 of the alarm day/date registers) control whether the alarm value stored in bits  $0 \sim 5$  of that register reflects the day of the week or the date of the month. If the bit is written to logic 0, the alarm is the result of a match with date of the month. If the bit is written to logic 1, the alarm is the result of a match with day of the week.

When the PT7C4337A register values match alarm register settings, the corresponding alarm flag (A1F or A2F) bit is set to logic 1. If the corresponding alarm interrupt enable (A1IE or A2IE) is also set to logic 1, the alarm condition activates one of the interrupt output (INTA or SQW/INTB) signals. The match is tested on the once-per-second update of the time and date registers.

Table 3. Alarm 1 Mask Bits

| Day,  | Ala  | rm 1 regis | ster mask | bits | Alarm Rate                                         |

|-------|------|------------|-----------|------|----------------------------------------------------|

| /Date | A1M4 | A1M3       | A1M2      | A1M1 | Alai iii Kate                                      |

| ×     | 1    | 1          | 1         | 1    | Alarm once per second                              |

| ×     | 1    | 1          | 1         | 0    | Alarm when seconds match                           |

| ×     | 1    | 1          | 0         | 0    | Alarm when minutes and seconds match               |

| ×     | 1    | 0          | 0         | 0    | Alarm when hours, minutes, and seconds match       |

| 0     | 0    | 0          | 0         | 0    | Alarm when date, hours, minutes, and seconds match |

| 1     | 0    | 0          | 0         | 0    | Alarm when day, hours, minutes, and seconds match  |

|       |      | Others     |           |      | Ignored.                                           |

Table 4. Alarm 2 Mask Bits

| Day,  | Alarn | 2 register m | ask bits | Alarm Rate                                         |

|-------|-------|--------------|----------|----------------------------------------------------|

| /Date | A2M4  | A2M3         | A2M2     | Alariii Kate                                       |

| ×     | 1     | 1            | 1        | Alarm once per minute (00 seconds of every minute) |

| ×     | 1     | 1            | 0        | Alarm when minutes match                           |

| ×     | 1     | 0            | 0        | Alarm when hours, minutes                          |

| 0     | 0     | 0            | 0        | Alarm when date, hours, and minutes match          |

| 1     | 0     | 0            | 0        | Alarm when day, hours, and minutes match           |

|       | (     | Others       | 1        | Ignored.                                           |

### I<sup>2</sup>C Bus Interface

### Overview of I<sup>2</sup>C-BUS

The I<sup>2</sup>C bus supports bi-directional communications via two signal lines: the SDA (data) line and SCL (clock) line. A combination of these two signals is used to transmit and receive communication start/stop signals, data signals, acknowledge signals, and so on. Both the SCL and SDA signals are held at high level whenever communications are not being performed. The starting and stopping of communications is controlled at the rising edge or falling edge of SDA while SCL is at high level. During data transfers, data changes that occur on the SDA line are performed while the SCL line is at low level, and on the receiving side the data is captured while the SCL line is at high level. In either case, the data is transferred via the SCL line at a rate of one bit per clock pulse. The I<sup>2</sup>C bus device does not include a chip select pin such as is found in ordinary logic devices. Instead of using a chip select pin, slave addresses are allocated to each device and the receiving device responds to communications only when its slave address matches the slave address in the received data.

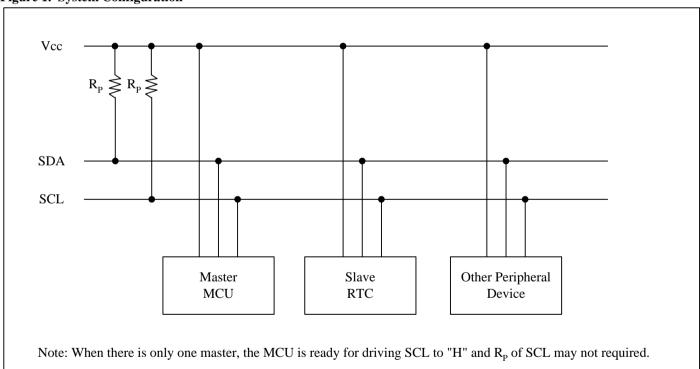

### **System Configuration**

All ports connected to the I<sup>2</sup>C bus must be either open drain or open collector ports in order to enable AND connections to multiple devices.

SCL and SDA are both connected to the VDD line via a pull-up resistance. Consequently, SCL and SDA are both held at high level when the bus is released (when communication is not being performed).

Figure 1. System Configuration

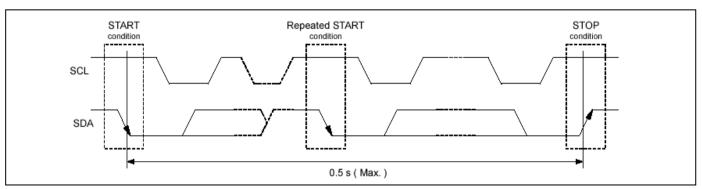

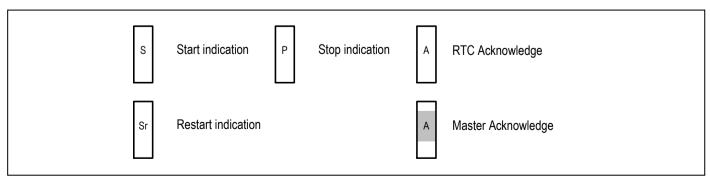

## Starting and Stopping I<sup>2</sup>C Bus Communications

Figure 2. Starting and Stopping on I<sup>2</sup>C Bus

#### 1) START Condition, Repeated START Condition, and STOP Condition

- a) START condition

- SDA level changes from high to low while SCL is at high level

- b) STOP condition

- SDA level changes from low to high while SCL is at high level

- c) Repeated START condition (RESTART condition)

In some cases, the START condition occurs between a previous START condition and the next STOP condition, in which case the second START condition is distinguished as a RESTART condition. Since the required status is the same as for the START condition, the SDA level changes from high to low while SCL is at high level.

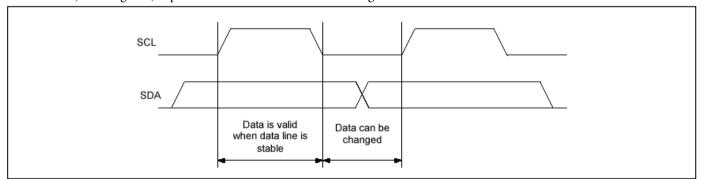

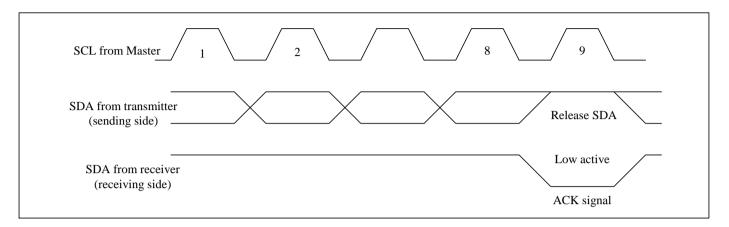

### 2) Data Transfers and Acknowledge Responses during I<sup>2</sup>C-BUS Communication

#### a) Data Transfers

Data transfers are performed in 8-bit (1 byte) units once the START condition has occurred. There is no limit on the amount (bytes) of data that are transferred between the START condition and STOP condition.

The address auto increment function operates during both write and read operations.

Updating of data on the transmitter (transmitting side)'s SDA line is performed while the SCL line is at low level. The receiver (receiving side) captures data while the SCL line is at high level.

<sup>\*</sup>Note with caution that if the SDA data is changed while the SCL line is at high level, it will be treated as a START, RESTART, or STOP condition.

### b) Data Acknowledge Response (ACK signal)

When transferring data, the receiver generates a confirmation response (ACK signal, low active) each time an 8-bit data segment is received. If there is no ACK signal from the receiver, it indicates that normal communication has not been established. (This does not include instances where the master device intentionally does not generate an ACK signal.)

Immediately after the falling edge of the clock pulse corresponding to the 8th bit of data on the SCL line, the transmitter releases the SDA line and the receiver sets the SDA line to low (= acknowledge) level.

After transmitting the ACK signal, if the Master remains the receiver for transfer of the next byte, the SDA is released at the falling edge of the clock corresponding to the 9th bit of data on the SCL line. Data transfer resumes when the Master becomes the transmitter.

When the Master is the receiver, if the Master does not send an ACK signal in response to the last byte sent from the slave, that indicates to the transmitter that data transfer has ended. At that point, the transmitter continues to release the SDA and awaits a STOP condition from the Master.

### **Slave Address**

The I<sup>2</sup>C bus device does not include a chip select pin such as is found in ordinary logic devices. Instead of using a chip select pin, slave addresses are allocated to each device.

All communications begin with transmitting the [START condition] + [slave address (+  $\overline{R/W}$  specification)]. The receiving device responds to this communication only when the specified slave address it has received matches its own slave address.

Slave addresses have a fixed length of 7 bits. See table for the details.

An  $R/\overline{W}$  bit is added to each 7-bit slave address during 8-bit transfers.

| Ī | Operation | Transfer data |       |       | Sl    | ave addre | ess   |       |       | R/W bit     |

|---|-----------|---------------|-------|-------|-------|-----------|-------|-------|-------|-------------|

|   | Operation | Transfer data | bit 7 | bit 6 | bit 5 | bit 4     | bit 3 | bit 2 | bit 1 | bit 0       |

|   | Read      | D1 h          | 1     | 1     | 0     | 1         | n     | 0     | 0     | 1 (= Read)  |

| Ī | Write     | D0 h          | 1     | 1     | U     | 1         | U     | U     | U     | 0 (= Write) |

#### I<sup>2</sup>C Bus's Basic Transfer Format

### Write via I<sup>2</sup>C Bus

| s     |     | Sla   | ve a | ddres  | s (7   | bits)   | •      | write | Α           | '          |  | Addr.   | setti  | ing   | •     |     | A           | bit | bit   | bit | bit | bit | bit | bit | bit | Α           | Р    |

|-------|-----|-------|------|--------|--------|---------|--------|-------|-------------|------------|--|---------|--------|-------|-------|-----|-------------|-----|-------|-----|-----|-----|-----|-----|-----|-------------|------|

|       | 1   | 1     | 0    | 1      | 0      | 0       | 0      | 0     |             |            |  |         | I      | I     | ĺ     |     |             | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |             | -    |

| Start | Sla | ve ad | dres | s + wr | ite sp | pecific | cation |       | A<br>C<br>K | Add<br>Spe |  | e write | e star | rt ac | ddres | ss. | A<br>C<br>K | Wri | te da | ta  |     |     |     |     |     | A<br>C<br>K | Stop |

### Read via I<sup>2</sup>C bus

#### **Standard Read**

| s     |       | Sla      | ve ad | dress      | (7 b        | its)    |       | write     | Α           |          |                 | '<br>/   | ۱<br>Addr. | setti    | ing   | •        | •        | A           | l     |          |          |       |          |          |          |          |    |   |

|-------|-------|----------|-------|------------|-------------|---------|-------|-----------|-------------|----------|-----------------|----------|------------|----------|-------|----------|----------|-------------|-------|----------|----------|-------|----------|----------|----------|----------|----|---|

|       | 1     | 1        | 0     | 1          | 0           | 0       | 0     | 0         |             |          |                 |          |            |          |       |          |          |             |       |          |          |       |          |          |          |          |    |   |

| Start |       | ve ad    | dress | + wri      | te sp       | ecifica | ation |           | A<br>C<br>K |          | lress<br>cifies | the r    | ead :      | start a  | addre | ess.     |          | A<br>C<br>K | -     |          |          |       |          |          |          |          |    |   |

|       |       |          |       |            |             |         |       |           |             |          |                 |          |            |          |       |          |          |             |       |          |          |       |          |          |          |          |    |   |

| Sr    | <br>T | T<br>Sla | I I   | T<br>dress | 1<br>s (7 b | its)    |       | Read      | Α           | bit 7    | bit             | bit 5    | bit        | bit<br>3 |       | bit<br>1 | bit<br>O | A           | bit   |          | bit 5    | bit   | bit<br>3 | bit<br>2 | bit<br>1 | bit<br>O | /A | Р |

| Sr    | 1     | Sla      | ve ad | dress      |             | nits)   | 0     | Read<br>1 | A           | bit<br>7 | bit<br>6        | bit<br>5 | bit 4      | bit<br>3 | bit 2 | bit<br>1 | bit<br>0 | A           | bit 7 | bit<br>6 | bit<br>5 | bit 4 | bit 3    | bit<br>2 | bit<br>1 | bit<br>0 | /A | P |

#### b) **Simplified Read**

| s     |    | Sla    | ı<br>ve ac | ı<br>ddres | ı<br>s (7 b | ı<br>oits) |        | _         | Α           | bit  | bit    | bit                            | bit  | bit   | bit   | bit | bit | Α           | bit | bit   | bit    | bit                        | bit     | bit  | bit | bit | /A        | P   |

|-------|----|--------|------------|------------|-------------|------------|--------|-----------|-------------|------|--------|--------------------------------|------|-------|-------|-----|-----|-------------|-----|-------|--------|----------------------------|---------|------|-----|-----|-----------|-----|

|       | 1  | 1      | 0          | 1          | 0           | 0          | 0      | Read<br>1 | , ,         | 7    | 6      | 5                              | 4    | 3     | 2     | 1   | 0   | , · ·       | 7   | 6     | 5      | 4                          | 3       | 2    | 1   | 0   | ,, (      | ľ   |

| Start | SI | ave ad | ddres      | s + re     | ad sp       | pecific    | cation |           | A<br>C<br>K | by t | he int | [<br>ead fr<br>ernal<br>auto i | addr | ess r | dress |     |     | A<br>C<br>K |     | addre | regist | ata re<br>ter au<br>or the | ito inc | reme |     |     | N O A C K | Sto |

#### Note:

- The above steps are an example of transfers of one or two bytes only. There is no limit to the number of bytes transferred during actual communications. 49H, 4AH are used as test mode address. Customer should not use the addresses.

### **Part Marking**

### PT7C4337A

W Package

PT7C 4337AWE SYWXX

S: Die Rev

Y: Date Code (Year)

W: Date Code (Workweek) 2nd X: Assembly Site Code

3rd X: Fab Site Code

#### U and L Package

Top mark not available at this time. To obtain advance information regarding the top mark, please contact your local sales representative.

### PT7C4337AC

### S Package

S: Die Rev

YYWW: Date Code (Year & Workweek)

1st G: Assembly Site Code 2nd G: Wafer Fab Site Code

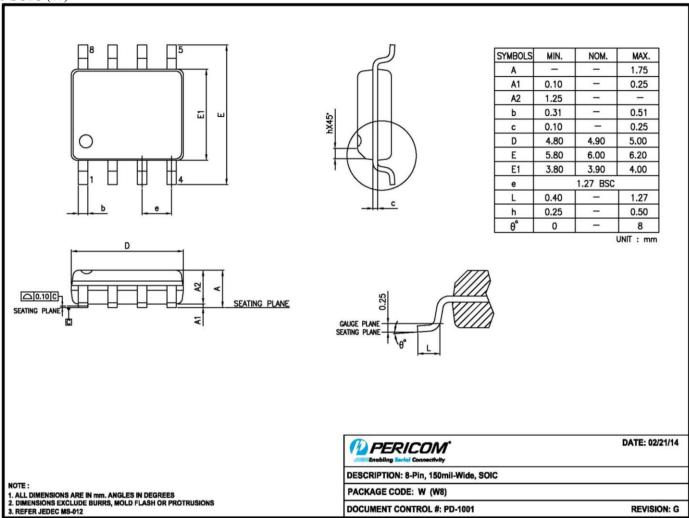

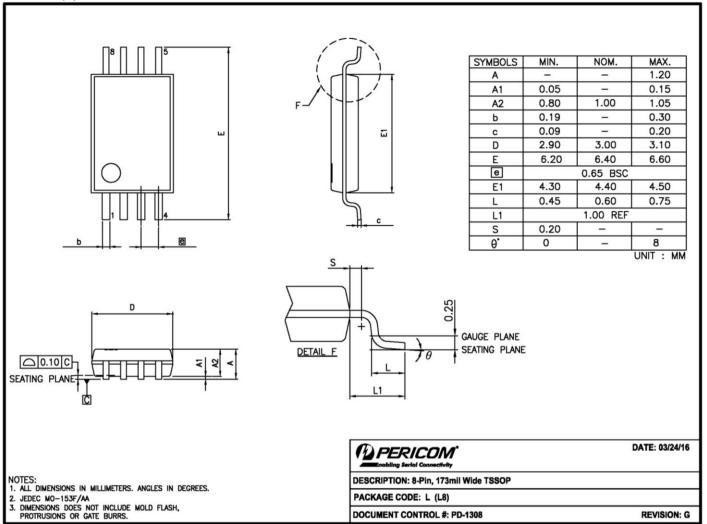

# **Packaging Mechanical**

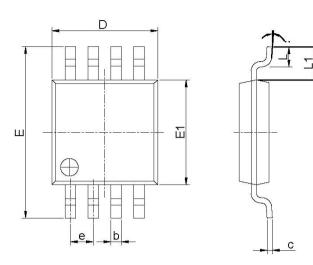

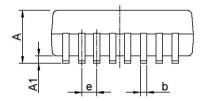

### 8-MSOP (U)

| PKG D  | IMENSION | S(MM) |  |

|--------|----------|-------|--|

| SYMBOL | Min.     | Max.  |  |

| А      | -        | 1.10  |  |

| A1     | 0.00     | 0.15  |  |

| A2     | 0.75     | 0.95  |  |

| b      |          | 0.38  |  |

| С      |          | 0.23  |  |

| D      | 2.80     | 3.20  |  |

| Е      | 4.65     | 5.15  |  |

| E1     | 2.80     | 3.20  |  |

| е      | 0.65 BSC |       |  |

| L      | 0.40     | 0.80  |  |

| L1     | 0.95 REF |       |  |

| θ      | 0°       | 8°    |  |

RECOMMENDED LAND PATTERN(unit:mm)

- NOTE:

1. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES IN DEGREES.

2. REFER JEDEC MO-187F/AA

3. PACKAGE OUTLINE DIMENSIONS DO NOT INCLUDE MOLD FLASH AND METAL BURR.

4. LAND PATTERN REFERENCE DIODES MSOP-8 PACKAGE INFORMATION.

| DIODES. PERICOM LEGISLATION ENABLING BETAL CONNECTIVITY | DATE: 11/04/19 |  |  |  |

|---------------------------------------------------------|----------------|--|--|--|

| DESCRIPTION: 8-Pin, Mini Small Outline Package, MSOP    |                |  |  |  |

| PACKAGE CODE: U (U8)                                    |                |  |  |  |

| DOCUMENT CONTROL #: PD-1261                             | REVISION: H    |  |  |  |

19-1147

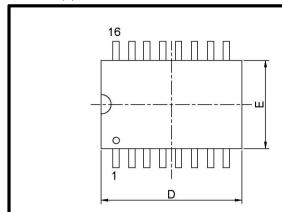

### 16-SOIC (S)

| PKG. DIMENSIONS(MM) |          |       |  |  |

|---------------------|----------|-------|--|--|

| SYMBOL              | Min      | Max   |  |  |

| Α                   | 2.35     | 2.64  |  |  |

| A1                  | 0.10     | 0.30  |  |  |

| b                   | 0.33     | 0.51  |  |  |

| С                   | 0.23     | 0.32  |  |  |

| D                   | 10.10    | 10.50 |  |  |

| Е                   | 7.40     | 7.60  |  |  |

| E1                  | 10.00    | 10.65 |  |  |

| е                   | 1.27 BSC |       |  |  |

| L                   | 0.41     | 1.27  |  |  |

| θ                   | 0°       | 8°    |  |  |

|                     |          |       |  |  |

Note:

Note: 1. Ref: JEDEC MS-013 AA PERICOM\*

Enabling Serial Connectivity

DATE: 08/29/14

DESCRIPTION: 16-Pin, SOIC (300 MIL WIDE)

PACKAGE CODE: S (S16)

DOCUMENT CONTROL #: PD-1005 REVISION: E

14-0238

### For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

### **Ordering Information**

| Part Number   | Package Code | Package Description                      |

|---------------|--------------|------------------------------------------|

| PT7C4337AWEX  | W            | 8-Pin, 150mil-Wide (SOIC)                |

| PT7C4337AUEX  | U            | 8-Pin, Mini Small Outline Package (MSOP) |

| PT7C4337ALEX  | L            | 8-Pin, 173mil Wide (TSSOP)               |

| PT7C4337ACSEX | S            | 16-Pin, 300mil Wide (SOIC)               |

#### Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

- E = Pb-free and Green

- 5. X suffix = Tape/Reel

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2020, Diodes Incorporated www.diodes.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Real Time Clock category:

Click to view products by Diodes Incorporated manufacturer:

Other Similar products are found below:

DS1302Z-LF 710029X 879047C 405800G PT7C43390LE RV-3029-C2-32.768k-OPTION-B-TB-QA RV-2123-C2-32.768k-20PPM-TA-QA RV-3029-C2-32.768k-OPTION-A-TB-QA PT7C4563UEX RV-3029-C3-32.768k-OPTION-A-TB-QA RV-2123-C2-32.768kHz-20PPM-TA-QC RX-4035LC:B3 PURE SN RX-8564LC:B PURE SN RX-8803LCUB PURE SN BULK BQ32002D RTC-8564JE MCP7940M-I/P DS3231SN#T&R DS1391U-18+ DS1347T+T&R RX-8564LC:B3 PURE SN DS1338Z-33+T RX-4571SA:B3 PURE SN DS1340U-33+T&R RX-8571LC:B3 PURE SN S-35190A-J8T1U RTC-4543SAB RTC-72421A RX-8803LC:UB3 PURE SN S-35390A-T8T1 AB1815-T3 AB-RTCMC-32.768kHz-AIGZ-S7-T AB-RTCMC-32.768kHz-B5GA-S3-T AB-RTCMC-32.768kHz-B5ZE-S3-T AB-RTCMC-32.768kHz-EOA9-S3-D-B-T AB-RTCMC-32.768kHz-EOZ9-S3-D-B-T AB-RTCMC-32.768kHz-EOZ9-S3-HAT AB-RTCMC-32.768kHz-EOZ9-S3-T DS1672U-33+ DS1337U+T&R DS1339AU+ FM33256B-G DS1673E-5-LF DS1672U-3+ DS1672U-33+T&R HYM1307N HYM1302 HYM1302N PCF8563N DS1302N