|           |               |         |                                |       |        |                  |                                                                                                          | R      | EVISI | ONS |    |        |                |      |        |                |       |        |      |    |

|-----------|---------------|---------|--------------------------------|-------|--------|------------------|----------------------------------------------------------------------------------------------------------|--------|-------|-----|----|--------|----------------|------|--------|----------------|-------|--------|------|----|

| LTR       | DESCRIPTION   |         |                                |       |        |                  |                                                                                                          |        |       |     | DA | TE (YI | R-MO-          | DA)  |        | APPF           | ROVE  | C      |      |    |

| А         | Boilerp       | olate ι | update                         | and p | art of | five ye          | ear rev                                                                                                  | iew. t | cr    |     |    |        |                | 07-0 | )4-04  |                | Rob   | ert M. | Hebe | r  |

|           |               |         |                                |       |        |                  |                                                                                                          |        |       |     |    |        |                |      |        |                |       |        |      |    |

|           |               |         | i                              | i     | i      | i                | i                                                                                                        | i      | i     | ł   | i  | i      | i              | i    | ł      | ł              |       |        | i    | 1  |

| REV       |               |         |                                |       |        |                  |                                                                                                          |        |       |     |    |        |                |      |        |                |       |        |      |    |

| SHEET     |               |         |                                |       |        |                  |                                                                                                          |        |       |     |    |        |                |      |        |                |       |        |      |    |

| REV       | A             | A       | A                              | A     | A      | A                | A                                                                                                        | A      | A     | A   | A  | A      | A              | A    | A      | A              |       |        |      |    |

| SHEET     | 15            | 16      | 17                             | 18    | 19     | 20               | 21                                                                                                       | 22     | 23    | 24  | 25 | 26     | 27             | 28   | 29     | 30             | •     | •      | •    | •  |

| REV STATU |               |         |                                | RE\   |        |                  | A                                                                                                        | A      | A     | A   | A  | A      | A              | A    | A      | A              | A     | A      | A    | A  |

| OF SHEETS |               |         |                                | SHE   |        |                  | 1                                                                                                        | 2      | 3     | 4   | 5  | 6      | 7              | 8    | 9      | 10             | 11    | 12     | 13   | 14 |

| PMIC N/A  |               |         |                                |       |        | ED BY<br>owling  |                                                                                                          |        |       |     |    |        |                |      |        |                |       |        |      |    |

|           |               |         |                                |       | -      | 5                |                                                                                                          |        |       |     | DI | EFEN   | SE S           | UPPL | Y CE   | NTEF           |       | UMB    | US   |    |

| MICRO     | NDAR<br>DCIRC | UIT     |                                |       | CKED   |                  |                                                                                                          |        |       | -   |    |        | OLUN           | IBUS | , OHIO | D 432<br>cc.dl | 218-3 |        |      |    |

|           |               |         | APPROVED BY<br>Michael A. Frye |       |        |                  | MICROCIRCUIT, MEMORY, DIGITAL,<br>CMOS, 2K X 8-DUAL PORT STATIC RANE<br>ACCESS MEMORY (SRAM), MONOLITHIC |        |       |     |    |        | 1              |      |        |                |       |        |      |    |

| AND AGE   |               |         |                                | DRA   |        | 6 APPI<br>8-03-1 |                                                                                                          | L DAT  | E     |     |    |        |                |      |        |                |       |        |      |    |

| AM        | SC N/A        | L.      |                                | REV   | ISION  | I LEVE           | EL<br>A                                                                                                  |        |       |     | ZE |        | GE CC<br>67268 |      |        | 5              | 5962· | -906   | 20   |    |

|           |               |         |                                |       |        |                  |                                                                                                          |        |       | SHE | ET |        | 1              | OF   | 30     |                |       |        |      |    |

## 1. SCOPE

1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device classes Q and M) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

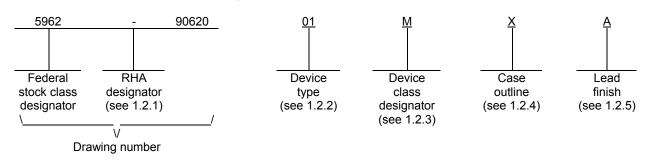

1.2 PIN. The PIN is as shown in the following example:

1.2.1 <u>RHA designator</u>. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

1.2.2 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | Generic number | Circuit function              | Access time |

|-------------|----------------|-------------------------------|-------------|

| 01          | 7C132          | 2K X 8 Dual port SRAM, MASTER | 55 ns       |

| 02          | 7C132          | 2K X 8 Dual port SRAM, MASTER | 45 ns       |

| 03          | 7C132          | 2K X 8 Dual port SRAM, MASTER | 35 ns       |

| 04          | 7C142          | 2K X 8 Dual port SRAM, SLAVE  | 55 ns       |

| 05          | 7C142          | 2K X 8 Dual port SRAM, SLAVE  | 45 ns       |

| 06          | 7C142          | 2K X 8 Dual port SRAM, SLAVE  | 35 ns       |

| 07          | 7C136          | 2K X 8 Dual port SRAM, MASTER | 55 ns       |

| 08          | 7C136          | 2K X 8 Dual port SRAM, MASTER | 45 ns       |

| 09          | 7C136          | 2K X 8 Dual port SRAM, MASTER | 35 ns       |

| 10          | 7C146          | 2K X 8 Dual port SRAM, SLAVE  | 55 ns       |

| 11          | 7C146          | 2K X 8 Dual port SRAM, SLAVE  | 45 ns       |

| 12          | 7C146          | 2K X 8 Dual port SRAM, SLAVE  | 35 ns       |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as

| follows:          |                  | <u> </u>                         | J                                        |                                                                                                                                     | .,                       |            |  |  |  |

|-------------------|------------------|----------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------|--|--|--|

|                   | <u>ce class</u>  |                                  | Device r                                 | equiremer                                                                                                                           | nts documentation        |            |  |  |  |

|                   | М                |                                  |                                          | ertification to the requirements for MIL-STD-883 compliant, non-<br>el B microcircuits in accordance with MIL-PRF-38535, appendix A |                          |            |  |  |  |

| C                 | ) or V           | Certificati                      | ation and qualification to MIL-PRF-38535 |                                                                                                                                     |                          |            |  |  |  |

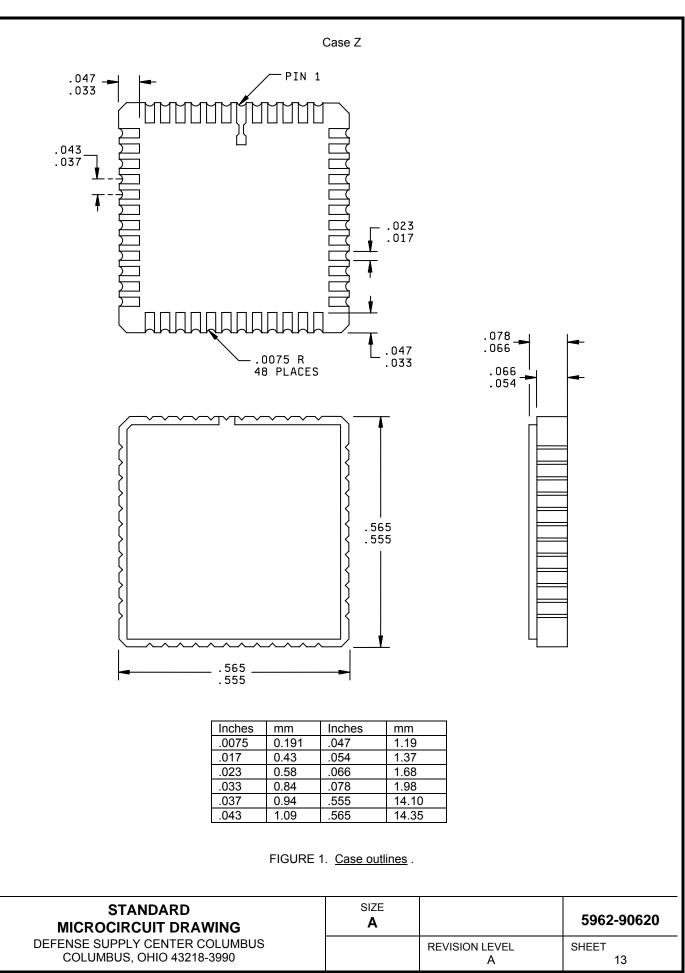

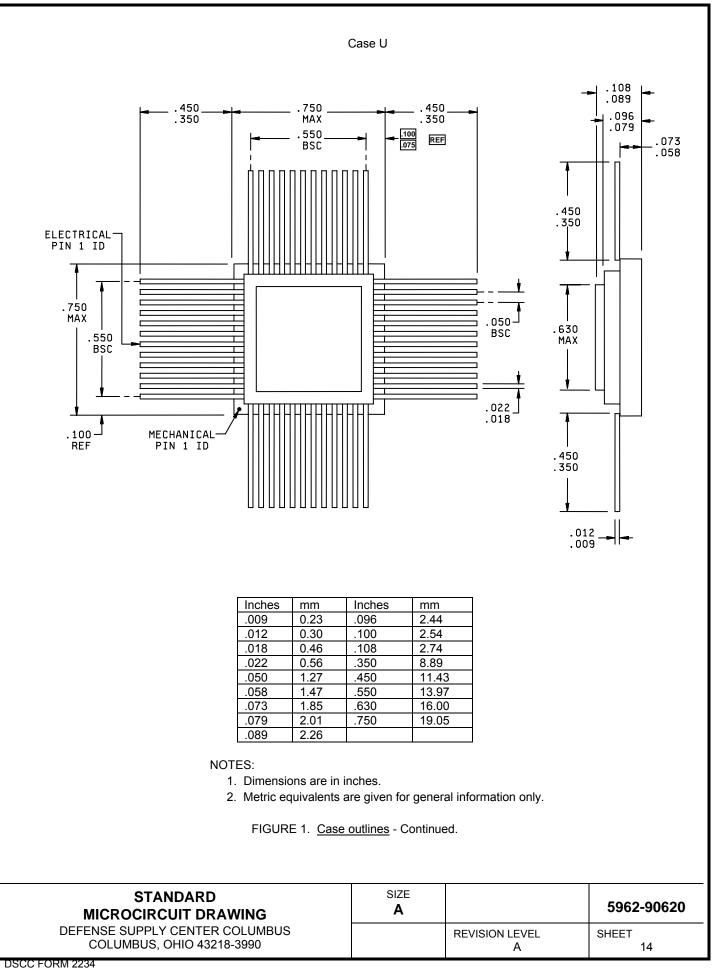

| 1.2.4 <u>Case</u> | outline(s).      | The case outline(s) are as desig | nated in MIL-                            | STD-1835                                                                                                                            | and as follows:          |            |  |  |  |

| Outlin            | <u>ie letter</u> | Descriptive designator           | <u>Terminals</u>                         | <u>Pa</u>                                                                                                                           | ckage style              |            |  |  |  |

| х                 |                  | CQCC1-N52                        | 52                                       | Squa                                                                                                                                | re leadless chip carrier |            |  |  |  |

| Y                 |                  | GDIP1-T48 or CDIP2-T48           | 48                                       | Dual-                                                                                                                               | in-line                  |            |  |  |  |

| Z                 |                  | See figure 1                     | 48                                       | Squa                                                                                                                                | re leadless chip carrier |            |  |  |  |

| U                 |                  | See figure 1                     | 48                                       | Flat p                                                                                                                              | •                        |            |  |  |  |

|                   |                  |                                  |                                          |                                                                                                                                     |                          |            |  |  |  |

| Ν                 | -                | TANDARD<br>IRCUIT DRAWING        | S                                        | BIZE<br><b>A</b>                                                                                                                    |                          | 5962-90620 |  |  |  |

| DEFE              | NSE SUP          | PLY CENTER COLUMBUS              |                                          |                                                                                                                                     | REVISION LEVEL           | SHEET      |  |  |  |

А

2

COLUMBUS, OHIO 43218-3990

1.2.5 <u>Lead finish</u>. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V or MIL-PRF-38535, appendix A for device class M.

1.3 Absolute maximum ratings. 1/

| Supply voltage range (V <sub>CC</sub> )                 |                       |

|---------------------------------------------------------|-----------------------|

| DC voltage range applied to outputs in high Z state     |                       |

| DC Input voltage range                                  | 3.0 V dc to +7.0 V dc |

| DC output current                                       | 20 mA                 |

| Maximum power dissipation <u>1</u> /                    | 1.0 W                 |

| Lead temperature (soldering, 10 seconds)                | +260°C                |

| Thermal resistance, junction-to-case ( $\theta_{JC}$ ): |                       |

| Cases X and Y                                           | See MIL-STD-1835      |

| Cases Z and U                                           | 10°C/W <u>2</u> /     |

| Junction temperature (T <sub>J</sub> )                  | +175°C                |

| Storage temperature range                               | 65°C to +150°C        |

| Temperature under bias range                            | 55°C to +125°C        |

## 1.4 Recommended operating conditions.

| Supply voltage range (V <sub>CC</sub> )            | +4.5 V dc to +5.5 V dc |

|----------------------------------------------------|------------------------|

| Ground voltage (GND)                               | 0 V dc                 |

| Input high voltage range ( $V_{IH}$ )              |                        |

| Input low voltage range $(V_{\parallel})$ 3/       |                        |

| Case operating temperature range (T <sub>c</sub> ) |                        |

## 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

#### DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

DEPARTMENT OF DEFENSE STANDARDS

| MIL-STD-883 -  | Test Method Standard Microcircuits.                    |

|----------------|--------------------------------------------------------|

| MIL-STD-1835 - | Interface Standard Electronic Component Case Outlines. |

1/ Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

- 2/ When a thermal resistance for this case is specified in MIL-STD-1835 that value shall supersede the value indicated herein.

- 3/ Negative undershoots to a minimum of -3.0 V are allowed with a maximum of 20 ns pulse width.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-90620 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | A              | 3          |

## DEPARTMENT OF DEFENSE HANDBOOKS

MIL-HDBK-103 - List of Standard Microcircuit Drawings. MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at <u>http://assist.daps.dla.mil/quicksearch/</u> or <u>http://assist.daps.dla.mil</u> or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Non-Government publications</u>. The following documents form a part of this document to the extent specified herein. Unless otherwise specified, the issues of the documents are the issues of the documents cited in the solicitation.

AMERICAN SOCIETY FOR TESTING AND MATERIALS (ASTM)

ASTM Standard F1192-00 - Standard Guide for the Measurement of Single Event Phenomena (SEP) induced by Heavy Ion Irradiation of Semiconductor Devices.

(Applications for copies of ASTM publications should be addressed to: ASTM International, PO Box C700, 100 Barr Harbor Drive, West Conshohocken, PA 19428-2959; <u>http://www.astm.org</u>.)

## ELECTRONICS INDUSTRIES ALLIANCE (EIA)

JEDEC Standard EIA/JESD 78 - IC Latch-Up Test.

(Applications for copies should be addressed to the Electronics Industries Alliance, 2500 Wilson Boulevard, Arlington, VA 22201; <u>http://www.jedec.org</u>.)

(Non-Government standards and other publications are normally available from the organizations that prepare or distribute the documents. These documents also may be available in or through libraries or other informational services.)

2.3 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

#### 3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V or MIL-PRF-38535, appendix A and herein for device class M.

3.2.1 <u>Case outlines</u>. The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-90620 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | A              | 4          |

3.2.3 <u>Truth table</u>. The truth table shall be as specified on figure 3.

3.2.4 <u>Die overcoat</u>. Polyimide and silicone coatings are allowable as an overcoat on the die for alpha particle protection only. Each coated microcircuit inspection lot (see inspection lot as defined in MIL-PRF-38535) shall be subjected to and pass the internal moisture content test at 5000 ppm (method 1018 of MIL-STD-883). The frequency of the internal water vapor testing shall not be decreased unless approved by the preparing activity for class M. The TRB will ascertain the requirements as provided by MIL-PRF-38535 for classes Q and V. Samples may be pulled any time after seal.

3.2.5 <u>Functional tests</u>. Various functional tests used to test this device are contained in the appendix. If the test patterns cannot be implemented due to test equipment limitations, alternate test patterns to accomplish the same results shall be allowed. For device class M, alternate test patterns shall be maintained under document revision level control by the manufacturer and shall be made available to the preparing or acquiring activity upon request. For device classes Q and V alternate test patterns shall be under the control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL- PRF -38535 and shall be made available to the preparing or acquiring activity upon request.

3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table I.

3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535. Marking for device class M shall be in accordance with MIL-PRF-38535, appendix A.

3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, appendix A.

3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6.2 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 or for device class M in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

3.8 <u>Notification of change for device class M</u>. For device class M, notification to DSCC-VA of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change that affects this drawing.

3.9 <u>Verification and review for device class M</u>. For device class M, DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 41 (see MIL-PRF-38535, appendix A).

3.11 Serialization for device classes V. Class V shall be serialized in accordance with MIL- PRF -38535.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-90620 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | A              | 5          |

#### 4. VERIFICATION

4.1 <u>Sampling and inspection</u>. For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-PRF-38535 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. For device class M, sampling and inspection procedures shall be in accordance with MIL-PRF-38535, appendix A.

4.2 <u>Screening</u>. For device classes Q and V, screening shall be in accordance with MIL-PRF-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection.

#### 4.2.1 Additional criteria for device class M.

- a. Delete the sequence specified as initial (preburn-in) electrical parameters through interim (postburn-in) electrical parameters of method 5004 and substitute lines 1 through 6 of table IIA herein.

- b. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1015.

- (1) Dynamic burn-in (method 1015 of MIL-STD-883, test condition D; for circuit, see 4.2.1b herein).

- c. Interim and final electrical parameters shall be as specified in table IIA herein.

#### 4.2.2 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The burn-in test circuit shall be maintained under document revision level control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1015 of MIL-STD-883.

- b. Interim and final electrical test parameters shall be as specified in table IIA herein.

- c. Additional screening for device class V beyond the requirements of device class Q shall be as specified in MIL-PRF-38535, appendix B.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                     | 5962-90620 |

|-------------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>A | SHEET 6    |

| TABLE I. Electrical performance characteristics.      |                  |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |                     |                                 |     |       |         |  |  |

|-------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------|-----|-------|---------|--|--|

| Test                                                  | Symbol           | Conditions $-55^{\circ}C \le T_{C} \le +$                                                                                                                                                                                                                                                                                        | 125°C                                                                                                                           | Group A<br>subgroup |                                 | Li  | imits | Unit    |  |  |

|                                                       |                  | $4.5 V \le V_{CC} \le 3$<br>unless otherwise s                                                                                                                                                                                                                                                                                   | 5.5 V<br>specified                                                                                                              |                     |                                 | Min | Max   |         |  |  |

| Output high voltage                                   | V <sub>OH</sub>  | $V_{CC} = 4.5 V$<br>$V_{IN} = V_{IH}, V_{IL}$<br>$I_{OH} = -4.0 mA$                                                                                                                                                                                                                                                              |                                                                                                                                 | 1,2,3               | All                             | 2.4 |       | V       |  |  |

| Output low voltage                                    | V <sub>OL</sub>  | V <sub>CC</sub> = 4.5 V,<br>V <sub>IN</sub> = V <sub>IH</sub> , V <sub>IL</sub>                                                                                                                                                                                                                                                  |                                                                                                                                 |                     |                                 |     |       |         |  |  |

|                                                       |                  | - I.                                                                                                                                                                                                                                                                                                                             | <sub>oL</sub> = 4.0 mA                                                                                                          | 1,2,3               | All                             |     | 0.4   |         |  |  |

|                                                       |                  | I                                                                                                                                                                                                                                                                                                                                | <sub>oL</sub> = 16.0 mA <u>1</u>                                                                                                | / 1,2,3             | All                             |     | 0.5   | V       |  |  |

| Input high voltage <u>2</u> /                         | V <sub>IH</sub>  |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 | 1,2,3               | All                             | 2.2 |       | V       |  |  |

| Input low voltage 2/                                  | V <sub>IL</sub>  |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 | 1,2,3               | All                             |     | 0.8   | V       |  |  |

| Input leakage current                                 | I <sub>IX</sub>  | $V_{IN}$ = 5.5 V to GND                                                                                                                                                                                                                                                                                                          |                                                                                                                                 | 1,2,3               | All                             | -5  | 5     | μΑ      |  |  |

| Output leakage current                                | I <sub>OZ</sub>  | V <sub>CC</sub> = 5.5 V,<br>V <sub>OUT</sub> = 5.5 V to GNI                                                                                                                                                                                                                                                                      | D                                                                                                                               | 1,2,3               | All                             | -5  | 5     | μΑ      |  |  |

| Operating supply current                              | I <sub>CC1</sub> |                                                                                                                                                                                                                                                                                                                                  | $V_{CC} = 5.5 \text{ V}, \text{ I}_{OUT} = 0 \text{ mA}$<br>$\overline{CE}_{L} \text{ and } \overline{CE}_{R} = \text{V}_{IL},$ |                     |                                 |     | 120   | mA      |  |  |

|                                                       |                  |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 | 1,2,3               | 03,06,<br>09,12                 |     | 170   |         |  |  |

| Standby supply current,<br>both ports, TTL<br>inputs  | I <sub>CC2</sub> | $V_{CC} = 5.5 \text{ V}, \text{ I}_{OUT} = 0$<br>$\overline{CE}_{L} \text{ and } \overline{CE}_{R} = \text{V}_{I}$<br>$f = f_{MAX} = \frac{3}{2}$                                                                                                                                                                                |                                                                                                                                 | 1,2,3               | 01,02,04,<br>05,07,08,<br>10,11 |     | 45    | mA      |  |  |

|                                                       |                  |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |                     | 03,06,<br>09,12                 |     | 65    |         |  |  |

| Standby supply current,<br>one port, TTL<br>inputs    | I <sub>CC3</sub> | $V_{CC} = 5.5 \text{ V}, \text{ I}_{OUT} = 0$<br>$\overline{CE}_{R} \text{ or } \overline{CE}_{L} = V_{IH}, \text{ f} = f_{MAX} \qquad \underline{3}/$                                                                                                                                                                           |                                                                                                                                 | 1,2,3               | 01,02,04,<br>05,07,08,<br>10,11 |     | 90    | mA      |  |  |

|                                                       |                  | $f = f_{MAX} $ <u>3</u> /                                                                                                                                                                                                                                                                                                        |                                                                                                                                 |                     | 03,06,<br>09,12                 |     | 115   |         |  |  |

| Standby supply current,<br>both ports, CMOS<br>inputs | I <sub>CC4</sub> | $\overline{CE}_{L}$ and $\overline{CE}_{R} \ge (V$                                                                                                                                                                                                                                                                               |                                                                                                                                 |                     | All                             |     | 15    | mA      |  |  |

| Standby supply current,<br>one port, CMOS<br>inputs   | I <sub>CC5</sub> | $\begin{split} & V_{CC} = 5.5 \text{ V}, \text{ I}_{OUT} = 0 \text{ mA} \\ & \overline{CE}_{L} \text{ or } \overline{CE}_{R} \geq (V_{CC} \text{ -} 0.2 \text{ V}), \\ & \text{all other inputs} \geq (V_{CC} \text{ -} 0.2 \text{ V}), \\ & \text{or } \leq 0.2 \text{ V}, \\ & \text{f} = f_{MAX}  \underline{3}/ \end{split}$ |                                                                                                                                 | 1,2,3               | 01,02,04,<br>05,07,08,<br>10,11 |     | 85    | mA      |  |  |

|                                                       |                  |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |                     | 03,06,<br>09,12                 |     | 105   |         |  |  |

| See footnotes at end of ta                            | able.            |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |                     |                                 |     |       |         |  |  |

|                                                       |                  | RD<br>DRAWING                                                                                                                                                                                                                                                                                                                    | 5                                                                                                                               | SIZE<br>A           |                                 |     | 5962  | 2-90620 |  |  |

| DEFENSE SUPI                                          | PLY CEN          | TER COLUMBUS<br>43218-3990                                                                                                                                                                                                                                                                                                       |                                                                                                                                 |                     | REVISION LEVE<br>A              | ΞL  | SHEET | 7       |  |  |

| DSCC FORM 2234<br>APR 97                              |                  |                                                                                                                                                                                                                                                                                                                                  | I                                                                                                                               | <b>I</b>            |                                 |     |       |         |  |  |

|                                           | Т                                                                                   | ABLE I. Electrical performar                                                 | nce charac | cteristics -         | continued.                      | _   |       |         |

|-------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------|----------------------|---------------------------------|-----|-------|---------|

| Test                                      | Symbol                                                                              | Conditions<br>-55°C $\leq$ T <sub>C</sub> $\leq$ +125°C                      |            | Group A<br>subgroups | Device<br>type                  | Li  | mits  | Unit    |

|                                           |                                                                                     | $4.5 \text{ V} \le V_{CC} \le 5.5 \text{ V}$ unless otherwise specified      |            |                      |                                 | Min | Max   |         |

| Input capacitance <u>4</u> /              | C <sub>IN</sub>                                                                     | V <sub>CC</sub> = 5.0 V<br>T <sub>A</sub> = +25°C, f = 1 MHz<br>(See 4.4.1e) |            | 4                    | All                             |     | 15    | ns      |

| Output capacitance <u>4</u> /             | C <sub>OUT</sub>                                                                    | $V_{CC} = 5.0 V$<br>$T_A = +25^{\circ}C, f = 1 MHz$<br>(See 4.4.1e)          |            | 4                    | All                             |     | 10    | ns      |

| Functional tests                          |                                                                                     | See 4.4.1c                                                                   |            | 7,8A,8B              | All                             |     |       |         |

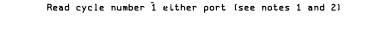

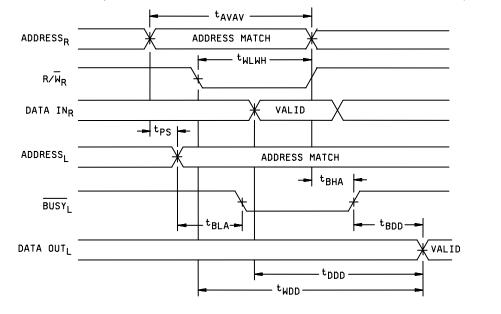

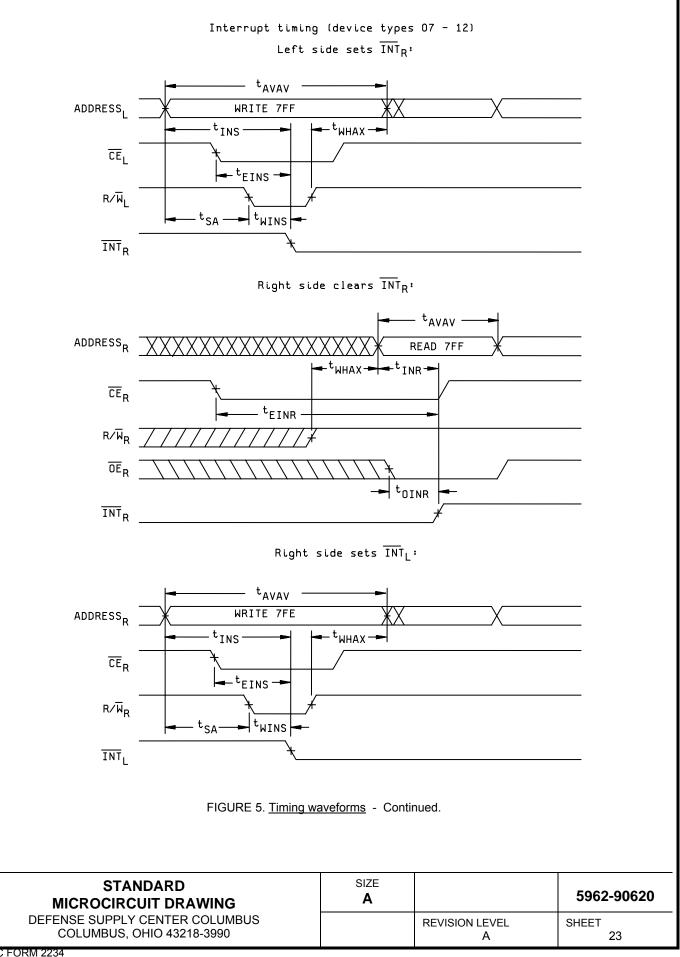

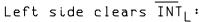

| Read cycle time                           | t <sub>AVAV</sub>                                                                   | See figures 4 and 5, read cycle timing <u>5</u> /                            |            | 9, 10, 11            | 01,04,<br>07,10                 | 55  |       | ns      |

|                                           |                                                                                     |                                                                              |            |                      | 02,05,<br>08,11                 | 45  |       | -       |

|                                           |                                                                                     |                                                                              |            |                      | 03,06,<br>09,12                 | 35  |       |         |

| Address access time                       | dress access time t <sub>AVQV</sub>                                                 |                                                                              |            | 9, 10, 11            | 01,04,<br>07,10                 |     | 55    | ns      |

|                                           |                                                                                     |                                                                              |            |                      | 02,05,<br>08,11                 |     | 45    |         |

|                                           |                                                                                     |                                                                              |            |                      | 03,06,<br>09,12                 |     | 35    |         |

| Output hold from address change <u>4/</u> | t <sub>AVQX</sub>                                                                   |                                                                              |            | 9, 10, 11            | All                             | 0   |       | ns      |

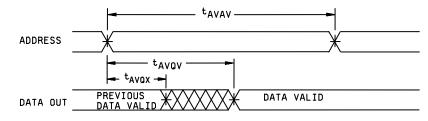

| Chip enable access time                   | t <sub>ELQV</sub>                                                                   |                                                                              |            | 9, 10, 11            | 01,04,<br>07,10                 |     | 55    |         |

|                                           |                                                                                     |                                                                              |            |                      | 02,05,<br>08,11                 |     | 45    | ns      |

|                                           |                                                                                     |                                                                              |            |                      | 03,06,<br>09,12                 |     | 35    |         |

| Output enable access time                 | t <sub>olqv</sub>                                                                   |                                                                              |            | 9, 10, 11            | 01,02,04,<br>05,07,08,<br>10,11 |     | 25    | ns      |

|                                           |                                                                                     |                                                                              |            |                      | 03,06,<br>09,12                 |     | 20    |         |

| Output enable to output active            | t <sub>olqx</sub>                                                                   | See figures 4 and 5,<br>read cycle timing <u>4</u> / <u>6/</u>               |            | 9, 10, 11            | All                             | 3   |       | ns      |

| Output enable to output inactive          | t <sub>ohqz</sub>                                                                   |                                                                              |            | 9, 10, 11            | 01,04,<br>07,10                 |     | 25    |         |

|                                           |                                                                                     |                                                                              |            |                      | 02,03,05,<br>06,08,09,<br>11,12 |     | 20    | ns      |

| Chip enable to output active              | t <sub>ELQX</sub>                                                                   |                                                                              |            | 9, 10, 11            | All                             | 5   |       | ns      |

| Chip select to output inactive            | t <sub>EHQZ</sub>                                                                   |                                                                              |            | 9, 10, 11            | 01,04,<br>07,10                 |     | 25    | ns      |

|                                           |                                                                                     |                                                                              |            |                      | 02,03,05,<br>06,08,09,<br>11,12 |     | 20    |         |

| See footnotes at end of ta                | able.                                                                               |                                                                              |            |                      |                                 |     |       | ·       |

|                                           | TANDA                                                                               |                                                                              | SIZ<br>A   |                      |                                 |     | 5064  | 2-90620 |

| DEFENSE SUPI                              | MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |                                                                              |            |                      | EVISION LEVI<br>A               | ΞL  | SHEET | 8       |

| DSCC FORM 2234                            |                                                                                     |                                                                              |            |                      |                                 |     | 1     |         |

|                                        | T                 | ABLE I. Electrical performan                                                                         | nce character | ristics - (        | continued.                      | _   |       |         |

|----------------------------------------|-------------------|------------------------------------------------------------------------------------------------------|---------------|--------------------|---------------------------------|-----|-------|---------|

| Test                                   | Symbol            | Conditions<br>-55°C $\leq$ T <sub>C</sub> $\leq$ +125°C                                              |               | roup A<br>Ibgroups | Device<br>type                  | Lir | nits  | Unit    |

|                                        |                   | $\begin{array}{c} 4.5 \ V \leq V_{CC} \leq 5.5 \ V \\ \text{unless otherwise specified} \end{array}$ |               |                    |                                 | Min | Max   |         |

| Chip enable to power<br>up <u>4</u> /  | t <sub>ELPU</sub> | See figures 4 and 5,<br>read cycle timing <u>5</u> /                                                 | 9             | ), 10, 11          | All                             | 0   |       | ns      |

| Chip enable to power down <u>4</u> /   | t <sub>EHPD</sub> |                                                                                                      | 9             | ), 10, 11          | All                             |     | 35    | ns      |

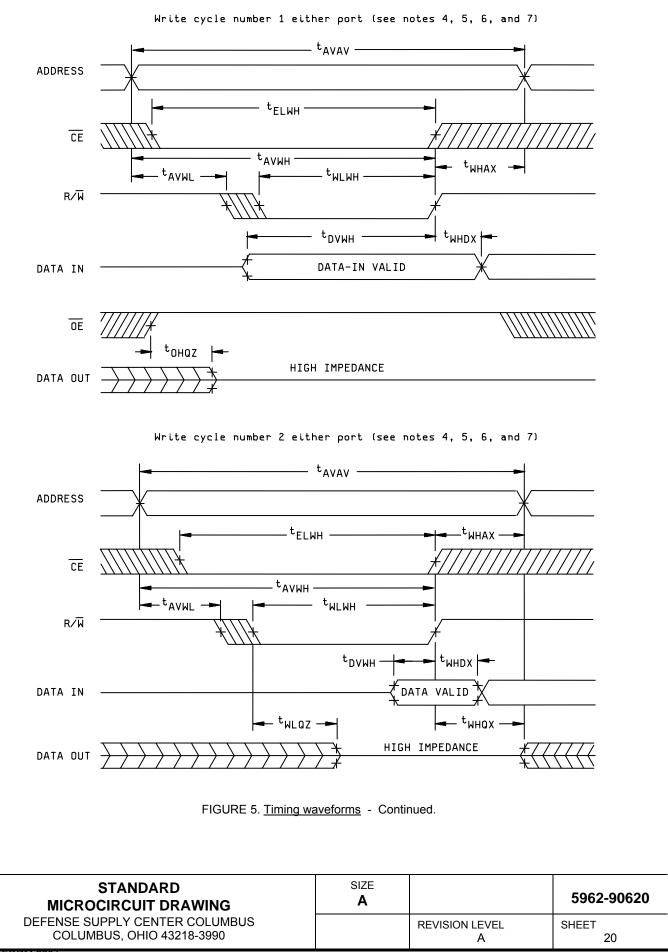

| Write cycle time                       | t <sub>AVAV</sub> | See figures 4 and 5,<br>write cycle timing <u>5</u> /                                                | 9             | 9, 10, 11          | 01,04,<br>07,10                 | 55  |       | ns      |

|                                        |                   |                                                                                                      |               |                    | 02,05,<br>08,11                 | 45  |       |         |

|                                        |                   |                                                                                                      |               |                    | 03,06,<br>09,12                 | 35  |       |         |

| Chip enable to write end               | t <sub>ELWH</sub> |                                                                                                      | 9             | 9, 10, 11          | 01,04,<br>07,10                 | 40  |       | ns      |

|                                        |                   |                                                                                                      |               |                    | 02,05,<br>08,11                 | 35  |       |         |

|                                        |                   |                                                                                                      |               |                    | 03,06,<br>09,12                 | 30  |       |         |

| Address setup to end<br>of write       | t <sub>avwh</sub> |                                                                                                      | 9             | 9, 10, 11          | 01,04,<br>07,10                 | 40  |       | ns      |

|                                        |                   |                                                                                                      |               |                    | 02,05,<br>08,11                 | 35  |       |         |

|                                        |                   |                                                                                                      |               | 10.11              | 03,06,<br>09,12                 | 30  |       |         |

| Address hold from write end            | t <sub>WHAX</sub> |                                                                                                      | 9             | ), 10, 11          | All                             | 2   |       | ns      |

| Address setup to write start           | t <sub>AVWL</sub> |                                                                                                      | 9             | ), 10, 11          | All                             | 0   |       | ns      |

| Write enable pulse<br>width            | t <sub>wLWH</sub> |                                                                                                      | 9             | 0, 10, 11          | 01,02,04,<br>05,07,08,<br>10,11 | 30  |       | ns      |

|                                        |                   |                                                                                                      |               |                    | 03,06,<br>09,12                 | 25  |       |         |

| Data setup to write end                | t <sub>DVWH</sub> |                                                                                                      | 9             | ), 10, 11          | 01,02,04,<br>05,07,08,<br>10,11 | 20  |       | ns      |

|                                        |                   |                                                                                                      |               |                    | 03,06,<br>09,12                 | 15  |       |         |

| Data hold from write<br>end            | t <sub>WHDX</sub> |                                                                                                      | 9             | ), 10, 11          | All                             | 0   |       | ns      |

| Write enable low to<br>output inactive | t <sub>wLQZ</sub> | See figures 4 and 5,<br>write cycle timing <u>4</u> / <u>6/</u>                                      | 9             | ), 10, 11          | 01,04,<br>07,10                 |     | 25    | ns      |

|                                        |                   |                                                                                                      |               |                    | 02,03,05,<br>06,08,09,<br>11,12 |     | 20    |         |

| Write enable high to output active     | t <sub>whqx</sub> |                                                                                                      | 9             | ), 10, 11          | All                             | 0   |       | ns      |

| See footnotes at end of t              | able.             |                                                                                                      |               |                    |                                 |     |       |         |

|                                        | TANDA             |                                                                                                      | SIZE          |                    |                                 |     | 506   | 2-90620 |

| DEFENSE SUP                            | PLY CEN           | DRAWING<br>TER COLUMBUS<br>43218-3990                                                                | A             | RE                 |                                 | EL  | SHEET |         |

| DSCC FORM 2234                         | 20, 0110          |                                                                                                      |               |                    | A                               |     |       | 9       |

| Test                                           | Symbol            | $-55^{\circ}C \le T_C \le +125^{\circ}C$ sul               | Group A<br>subgroups | Device<br>type  | Limits |            | Unit |

|------------------------------------------------|-------------------|------------------------------------------------------------|----------------------|-----------------|--------|------------|------|

|                                                |                   | $4.5 V \le V_{CC} \le 5.5 V$<br>unless otherwise specified |                      |                 | Min    | Мах        | -    |

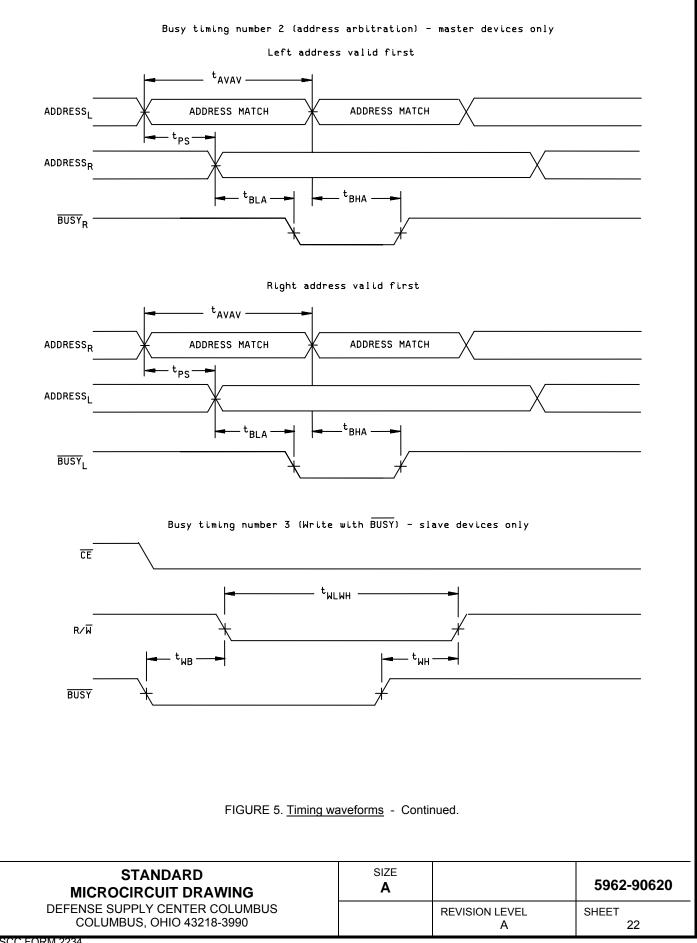

| Busy low from address                          | t <sub>BLA</sub>  | See figures 4 and 5,                                       | 9, 10, 11            | 01,07           |        | 30         | ns   |

| match                                          |                   | busy cycle timing <u>5</u> /                               |                      | 02,08           |        | 25         |      |

|                                                |                   | -                                                          |                      | 03,09           |        | 20         |      |

| Busy high from address                         | t <sub>BHA</sub>  |                                                            | 9, 10, 11            | 01,07           |        | 30         | ns   |

| mísmatch <u>7</u> /                            |                   |                                                            |                      | 02,08           |        | 25         | -    |

|                                                |                   | -                                                          |                      | 03,09           |        | 20         |      |

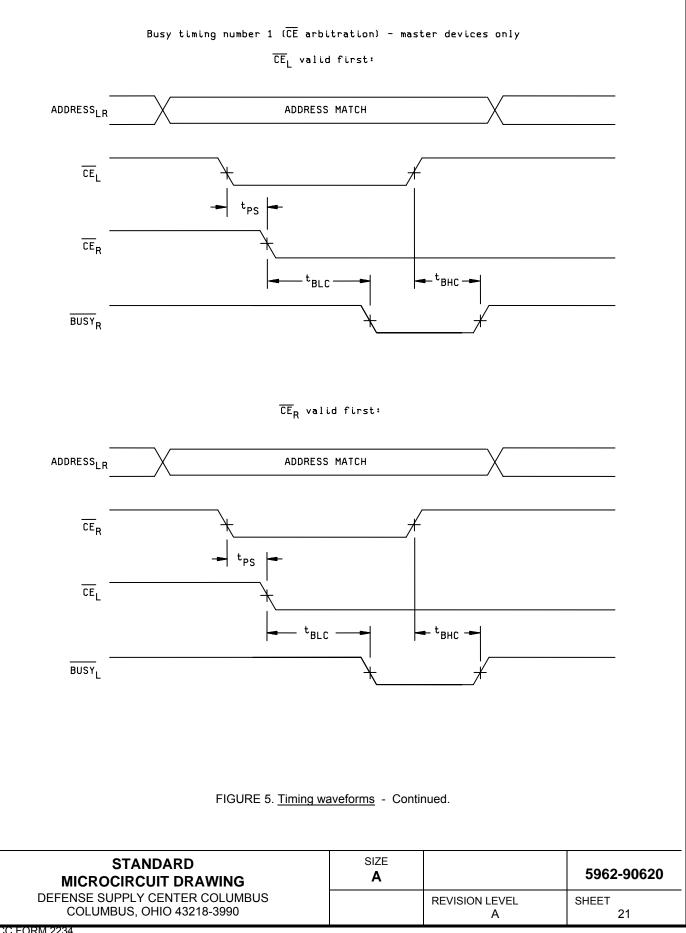

| Busy low from chip<br>enable low               | t <sub>BLC</sub>  |                                                            | 9, 10, 11            | 01,07           |        | 30         | ns   |

| enable low                                     |                   |                                                            |                      | 02,08           |        | 25         | -    |

|                                                |                   |                                                            |                      | 03,09           |        | 20         |      |

| Busy high from chip                            | t <sub>BHC</sub>  |                                                            | 9, 10, 11            | 01,07           |        | 30         | ns   |

| enable high <u>7</u> /                         |                   |                                                            |                      | 02,08           |        | 25         | _    |

|                                                |                   | -                                                          |                      | 03,09           |        | 20         |      |

| Port setup for priority                        | t <sub>PS</sub>   |                                                            | 9, 10, 11            | 01-03,<br>07-09 | 5      |            | ns   |

| Write enable low after<br>busy low             | t <sub>WB</sub>   |                                                            | 9, 10, 11            | 04-06<br>10-12  | 0      |            | ns   |

| Write enable high after<br>busy high           | t <sub>wH</sub>   |                                                            | 9, 10, 11            | 04,05<br>10,11  | 35     |            | ns   |

|                                                |                   |                                                            |                      | 06,12           | 30     |            |      |

| Busy high to valid data                        | t <sub>BDD</sub>  |                                                            | 9, 10, 11            | 01,02,<br>07,08 |        | 45         | ns   |

|                                                |                   |                                                            |                      | 03,09           |        | 35         |      |

| Write data valid to read data valid <u>4</u> / | t <sub>DDD</sub>  |                                                            | 9, 10, 11            | 01-03,<br>07-09 |        | <u>8</u> / | ns   |

| Write pulse to data<br>delay <u>4/</u>         | t <sub>WDD</sub>  |                                                            | 9, 10, 11            | 01-03,<br>07-09 |        | <u>8</u> / | ns   |

| Write enable to                                | t <sub>WINS</sub> | See figures 4 and 5,                                       | 9, 10, 11            | 07,10           |        | 45         | ns   |

| interrupt set time                             |                   | interrupt cycle timing <u>5</u> /                          |                      | 08,11           |        | 35         |      |

|                                                |                   |                                                            |                      | 09,12           |        | 25         |      |

SIZE

Α

**REVISION LEVEL**

А

5962-90620

10

SHEET

TABLE I. <u>Electrical performance characteristics</u> - continued.

**STANDARD**

MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS

COLUMBUS, OHIO 43218-3990

| Test                                           | Symbol Conditions<br>$-55^{\circ}C \le T_{C} \le +125^{\circ}C$ |                                                            | Group A<br>subgroups | Device<br>type | Limits |     | Unit |

|------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------|----------------------|----------------|--------|-----|------|

|                                                |                                                                 | $4.5 V \le V_{CC} \le 5.5 V$<br>unless otherwise specified |                      |                | Min    | Max | -    |

| Chip enable to                                 | t <sub>EINS</sub>                                               | See figures 4 and 5, sinterrupt cycle timing <u>5</u> /    | 9, 10, 11            | 07,10          |        | 45  | ns   |

| interrupt set time                             |                                                                 |                                                            |                      | 08,11          |        | 35  |      |

|                                                |                                                                 |                                                            |                      | 09,12          |        | 25  |      |

| Address to interrupt t <sub>INS</sub> 9, 10, 1 | 9, 10, 11                                                       | 07,10                                                      |                      | 45             | ns     |     |      |

|                                                |                                                                 |                                                            |                      | 08,11          |        | 35  |      |

|                                                |                                                                 |                                                            |                      | 09,12          |        | 25  |      |

| Output enable to                               | t <sub>OINR</sub>                                               |                                                            | 9, 10, 11            | 07,10          |        | 45  | ns   |

| interrupt reset time<br><u>7/</u>              |                                                                 |                                                            |                      | 08,11          |        | 35  |      |

|                                                |                                                                 |                                                            |                      | 09,12          |        | 25  |      |

| Chip enable to                                 | t <sub>EINR</sub>                                               |                                                            | 9, 10, 11            | 07,10          |        | 45  | ns   |

| interrupt reset time<br><u>7/</u>              |                                                                 |                                                            |                      | 08,11          |        | 35  |      |

|                                                |                                                                 |                                                            |                      | 09,12          |        | 25  |      |

| Address to interrupt reset time <u>7/</u>      | t <sub>INR</sub>                                                |                                                            | 9, 10, 11            | 07,10          |        | 45  | ns   |

|                                                |                                                                 |                                                            |                      | 08,11          |        | 35  |      |

|                                                |                                                                 |                                                            |                      | 09,12          |        | 25  |      |

TABLE I. Electrical performance characteristics - continued.

1/ BUSY and INT outputs only.

2/ These are absolute values with respect to device ground and all overshoots and undershoots due to system or tester noise are included.

3/ At f = f<sub>MAX</sub>, address and data inputs are cycling at the maximum frequency of  $1/t_{AVAV}$ .

4/ Tested initially and after any design or process changes that affect that parameter, and therefore shall be guaranteed to the limits specified in table I.

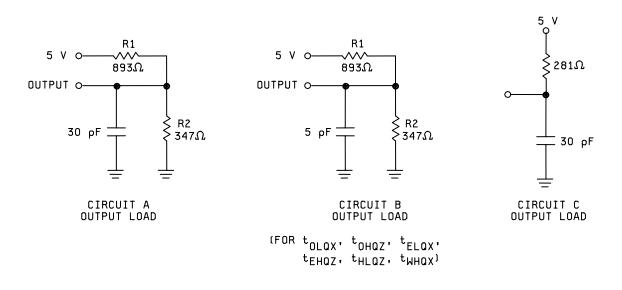

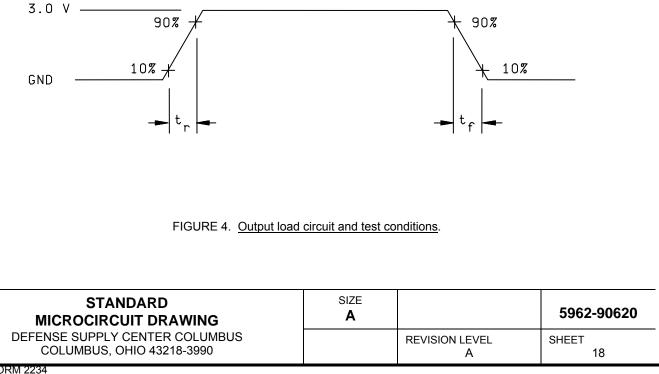

- 5/ AC tests are performed with transition times of 5 ns or less, timing reference levels of 1.5 V, input pulse levels of 0 to 3.0 V, and the output load in figure 4 (circuit A). For  $\overline{\text{BUSY}}$  and  $\overline{\text{INT}}$  loads for devices 01-03 and 07-09, see figure 4 (circuit C).

- $\underline{6}$ / Transition is measured at steady-state high level -500 mV or steady-state low level +500 mV on the output from the 1.5 V level on the input, C<sub>L</sub> = 5 pF (including scope and jig). See figure 4 (circuit B). For  $\overline{\text{BUSY}}$  and  $\overline{\text{INT}}$  loads for devices 01-03 and 07-09, see figure 4 (circuit C).

- <u>7</u>/ These parameters are measured from the input signal changing, until the output pin goes to the high-impedance state.

- 8/ A write operation on Port A, where Port A has priority, leaves the data on Port B's outputs undisturbed until one access time after one of the following:

- A. BUSY on Port B goes HIGH.

- B. Port B's address toggled.

- C.  $\overline{CE}$  for Port B is toggled.

- D.  $R/\overline{W}$  for Port B is toggled, during valid read.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                     | 5962-90620  |

|-------------------------------------------------------------|-----------|---------------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>A | SHEET<br>11 |

| SCC EODM 2224                                               |           |                     |             |

| Line<br>No. | Test<br>requirements                       | Subgroups<br>(in accordance with<br>MIL-STD-883,<br>method 5005, table I) | (in acco<br>MIL-P                 | bgroups<br>ordance with<br>RF-38535,<br>5005, table III) |

|-------------|--------------------------------------------|---------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------|

|             |                                            | Device<br>class M                                                         | Device<br>class Q                 | Device<br>class V                                        |

| 1           | Interim electrical<br>parameters (see 4.2) |                                                                           | 1,7,9                             | 1,7,9                                                    |

| 2           | Static burn-in L and II<br>(method 1015)   | Not<br>required                                                           | Not<br>required                   | Required                                                 |

| 3           | Same as line 1                             |                                                                           |                                   | 1*,7* ∆                                                  |

| 4           | Dynamic burn-in<br>(method 1015)           | Required                                                                  | Required                          | Required                                                 |

| 5           | Same as line 1                             |                                                                           |                                   | 1*,7* <b>Δ</b>                                           |

| 6           | Final electrical<br>parameters             | 1*,2,3,7*,<br>8A,8B,9,10,<br>11                                           | 1*,2,3,7*,<br>8A,8B,9,10,<br>11   | 1*,2,3,7*,<br>8A,8B,9,10,<br>11                          |

| 7           | Group A test<br>requirements               | 1,2,3,4**,7,<br>8A,8B,9,10,<br>11                                         | 1,2,3,4**,7,<br>8A,8B,9,10,<br>11 | 1,2,3,4**,7,<br>8A,8B,9,10,<br>11                        |

| 8           | Group C end-point<br>electrical parameters | 2,3,7,<br>8A,8B                                                           | 1,2,3,7,<br>8A,8B ∆               | 1,2,3,7,<br>8A,8B,9,10,11 ∆                              |

| 9           | Group D end-point<br>electrical parameters | 2,3,<br>8A,8B                                                             | 2,3,<br>8A,8B                     | 2,3,<br>8A,8B                                            |

| 10          | Group E end-point<br>electrical parameters | 1,7,9                                                                     | 1,7,9                             | 1,7,9                                                    |

TABLE IIA. Electrical test requirements. 1/2/3/4/5/6/7/

<u>1</u>/ Blank spaces indicates tests are not applicable.

2/ Any or all subgroups may be combined when using high-speed testers.

3/ Subgroups 7, 8A, and 8B functional tests shall verify the truth table.

$\underline{4}$ / \* indicates PDA applies to subgroup 1 and 7.

<u>5</u>/ \*\* see 4.4.1e.

$\underline{6}$  /  $\Delta$  indicates delta limit (see table IIB) shall be required where specified, and the delta values shall be computed with reference to the previous interim electrical parameters.

<u>7</u>/ See 4.4.1d.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-90620 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | A              | 12         |

| r                  |                   |                   | [                  |                     |                    |

|--------------------|-------------------|-------------------|--------------------|---------------------|--------------------|

| Device<br>types    | 01-06             | 07-12             | Device<br>types    | 01-06               | 07-12              |

| Case<br>outlines   | Y,<br>Z and U     | х                 | Case<br>outlines   | Y,<br>Z and U       | х                  |

| Terminal<br>number | Termina           | l symbol          | Terminal<br>number | Termina             | al symbol          |

| 1                  | ¯⊂E ∟             | ¯CE ∟             | 27                 | I/O <sub>2R</sub>   | I/O <sub>0R</sub>  |

| 2                  | R/₩ L             | R/ W L            | 28                 | I/O <sub>3R</sub>   | I/O <sub>1R</sub>  |

| 3                  | BUSY L            | BUSY L            | 29                 | I/O <sub>4R</sub>   | I/O <sub>2R</sub>  |

| 4                  | A <sub>10L</sub>  |                   | 30                 | I/O <sub>5R</sub>   | I/O <sub>3R</sub>  |

| 5                  | OE L              | A <sub>10L</sub>  | 31                 | I/O <sub>6R</sub>   | I/O <sub>4R</sub>  |

| 6                  | A <sub>0L</sub>   | OE L              | 32                 | I/O <sub>7R</sub>   | I/O <sub>5R</sub>  |

| 7                  | A <sub>1L</sub>   | A <sub>0L</sub>   | 33                 | A <sub>9R</sub>     | I/O <sub>6R</sub>  |

| 8                  | A <sub>2L</sub>   | A <sub>1L</sub>   | 34                 | A <sub>8R</sub>     | I/O <sub>7R</sub>  |

| 9                  | A <sub>3L</sub>   | A <sub>2L</sub>   | 35                 | A <sub>7R</sub>     | NC                 |

| 10                 | A <sub>4L</sub>   | A <sub>3L</sub>   | 36                 | A <sub>6R</sub>     | A <sub>9R</sub>    |

| 11                 | A <sub>5L</sub>   | A <sub>4L</sub>   | 37                 | A <sub>5R</sub>     | A <sub>8R</sub>    |

| 12                 | A <sub>6L</sub>   | A <sub>5L</sub>   | 38                 | A <sub>4R</sub>     | A <sub>7R</sub>    |

| 13                 | A <sub>7L</sub>   | A <sub>6L</sub>   | 39                 | A <sub>3R</sub>     | A <sub>6R</sub>    |

| 14                 | A <sub>8L</sub>   | A <sub>7L</sub>   | 40                 | A <sub>2R</sub>     | A <sub>5R</sub>    |

| 15                 | A <sub>9L</sub>   | A <sub>8L</sub>   | 41                 | A <sub>1R</sub>     | A <sub>4R</sub>    |

| 16                 | I/O <sub>0L</sub> | A <sub>9L</sub>   | 42                 | A <sub>0R</sub>     | A <sub>3R</sub>    |

| 17                 | I/O <sub>1L</sub> | I/O <sub>0L</sub> | 43                 | $\overline{OE}_{R}$ | A <sub>2R</sub>    |

| 18                 | I/O <sub>2L</sub> | I/O <sub>1L</sub> | 44                 | A <sub>10R</sub>    | A <sub>1R</sub>    |

| 19                 | I/O <sub>3L</sub> | I/O <sub>2L</sub> | 45                 | BUSY R              | A <sub>0R</sub>    |

| 20                 | I/O <sub>4L</sub> | I/O <sub>3L</sub> | 46                 | $R/\overline{W}_R$  | OE R               |

| 21                 | I/O <sub>5L</sub> | I/O <sub>4L</sub> | 47                 | CE R                | A <sub>10R</sub>   |

| 22                 | I/O <sub>6L</sub> | I/O <sub>5L</sub> | 48                 | V <sub>CC</sub>     | INT <sub>R</sub>   |

| 23                 | I/O <sub>7L</sub> | I/O <sub>6L</sub> | 49                 |                     | BUSY R             |

| 24                 | GND               | I/O <sub>7L</sub> | 50                 |                     | $R/\overline{W}_R$ |