|                                                                                   | REVISIONS                                                                                                 |                       |      |                                   |             |                |          |                                   |         |                                                             |        |                                   |        |                   |                 |    |                |     |    |    |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------|------|-----------------------------------|-------------|----------------|----------|-----------------------------------|---------|-------------------------------------------------------------|--------|-----------------------------------|--------|-------------------|-----------------|----|----------------|-----|----|----|

| LTR                                                                               |                                                                                                           |                       |      |                                   |             | DES            | CRIPTI   | ON                                |         |                                                             |        |                                   |        | DATE A (YR-MO-DA) |                 |    | APPROVED       |     |    |    |

| С                                                                                 | Convert to military drawing format. Add LCC package. Edito<br>Change code ident. no. from 14933 to 67268. |                       |      |                                   |             |                | Editor   | rial changes throughout. 88-01-27 |         |                                                             |        | M. A. Frye                        |        |                   |                 |    |                |     |    |    |

| D                                                                                 |                                                                                                           | ate boile<br>ce funct |      | to MIL-<br>CFS                    | PRF-38      | 8535 re        | quirem   | ents. C                           | Correct | title to a                                                  | ocurat | ely refle                         | ect    | 0                 | 5-03-23         | 3  | Thomas M. Hess |     |    | s  |

|                                                                                   |                                                                                                           |                       |      |                                   |             |                |          |                                   |         |                                                             |        |                                   |        |                   |                 |    |                |     |    |    |

| THE ORIGIN                                                                        | IAL FI                                                                                                    | RST                   | SHEE | T OF                              | THIS        | DRA            | WING     | HAS                               | BEEN    | I REP                                                       | LACE   | ED.                               | i      | t                 | ì               | i  | i              | i   | i  |    |

| REV                                                                               |                                                                                                           |                       |      |                                   |             |                |          |                                   |         |                                                             |        |                                   |        |                   |                 |    |                |     |    |    |

| SHEET                                                                             |                                                                                                           |                       |      |                                   |             |                |          |                                   |         |                                                             |        |                                   |        |                   |                 |    |                |     |    |    |

| REV                                                                               | D                                                                                                         | D                     | D    | D                                 | D           | D              | D        | D                                 | D       | D                                                           | D      | D                                 | D      |                   |                 |    |                |     |    |    |

| SHEET                                                                             | 15                                                                                                        | 16                    | 17   | 18                                | 19          | 20             | 21       | 22                                | 23      | 24                                                          | 25     | 26                                | 27     |                   |                 |    |                |     |    |    |

| REV STATUS<br>OF SHEETS                                                           |                                                                                                           |                       |      | REV                               | /           |                | D        | D                                 | D       | D                                                           | D      | D                                 | D      | D                 | D               | D  | D              | D   | D  | D  |

| OF SHEETS                                                                         |                                                                                                           |                       |      | SHE                               | ET          |                | 1        | 2                                 | 3       | 4                                                           | 5      | 6                                 | 7      | 8                 | 9               | 10 | 11             | 12  | 13 | 14 |

| PMIC N/A                                                                          |                                                                                                           |                       |      | PREI                              | PARED<br>Ja | ) BY<br>ames E | . Jamis  | on                                |         | DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |        |                                   |        |                   |                 |    |                |     |    |    |

| STAI<br>MICRC                                                                     |                                                                                                           |                       |      | CHE                               | CKED        |                | )iCenzo  | )                                 |         |                                                             |        |                                   |        |                   | , onic<br>/w.ds |    |                | 990 |    |    |

| DRA                                                                               | WIN                                                                                                       | G                     |      | APP                               | ROVED       | ) BY<br>Michae | I A. Fry | e                                 |         |                                                             |        |                                   | IT, DI |                   |                 |    |                |     | R  |    |

| THIS DRAWING IS AVAILABLE<br>FOR USE BY ALL<br>DEPARTMENTS<br>AND AGENCIES OF THE |                                                                                                           |                       |      | DRAWING APPROVAL DATE<br>83-04-07 |             |                |          |                                   |         |                                                             |        | JNTER/TIMER, PA<br>-CHANNEL, MONO |        |                   |                 |    | LICO           | N   |    |    |

| DEPARTMEN                                                                         | NT OF [                                                                                                   | DEFEN                 |      | REVI                              | ISION I     |                |          |                                   |         | SIZE CAGE CODE<br>A 67268                                   |        | 83001                             |        | 001               |                 |    |                |     |    |    |

| AM                                                                                | SC N/A                                                                                                    |                       |      |                                   |             | I              | C        |                                   |         | SHE                                                         |        | 1                                 | 0      |                   | 27              |    |                |     |    |    |

|                                                                                   |                                                                                                           |                       |      |                                   |             |                |          |                                   |         |                                                             |        |                                   |        |                   |                 |    |                |     |    |    |

1. SCOPE

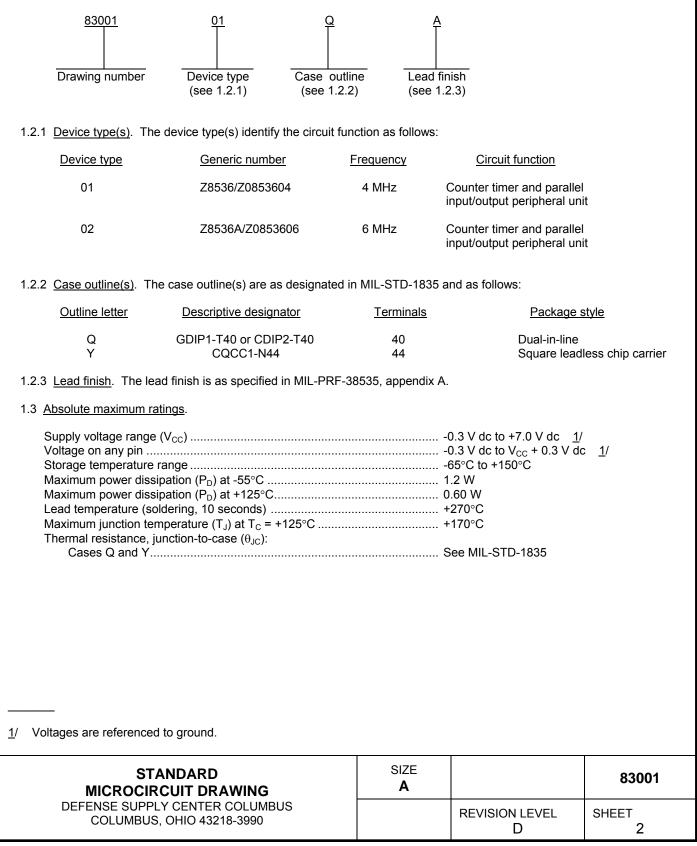

1.1 <u>Scope</u>. This drawing describes device requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A.

1.2 Part or Identifying Number (PIN). The complete PIN is as shown in the following example:

# 1.4 Recommended operating conditions.

| Supply voltage range (V <sub>CC</sub> )             |                  |

|-----------------------------------------------------|------------------|

| Minimum high level input voltage (V <sub>IH</sub> ) |                  |

| Maximum low level input voltage (VIL)               | . 0.8 V dc       |

| Frequency of operation:                             |                  |

| Device type 01                                      | . 0.5 to 4.0 MHz |

| Device type 02                                      | . 0.5 to 6.0 MHz |

| Case operating temperature range (T <sub>c</sub> )  | 55°C to +125°C   |

| Maximum clock rise time                             | . 20 ns          |

| Maximum clock fall time                             | . 20 ns          |

| <u>Timing pa</u>                       | arameter    | Reference number 1/ | <u>Minimum</u> | <u>Maximum</u> | <u>Units</u> |

|----------------------------------------|-------------|---------------------|----------------|----------------|--------------|

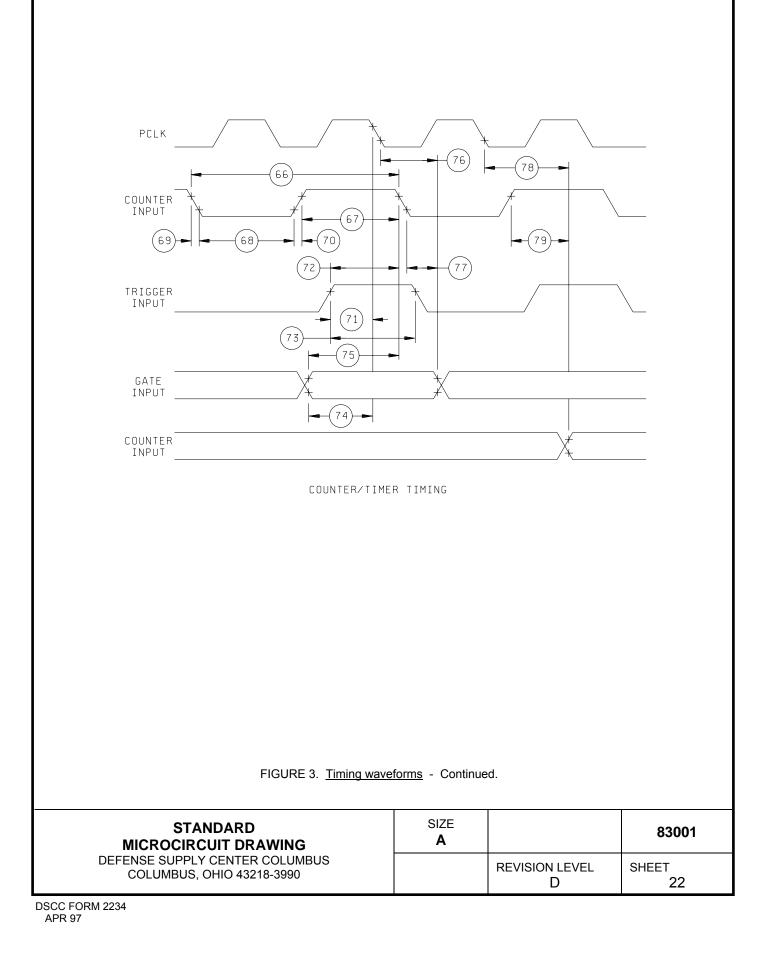

| Trigger in<br>setup time<br>(timer mo  |             | 71                  | 150            |                | ns           |

| Trigger in<br>input setu<br>(counter r |             | 72                  | 150            |                | ns           |

| Trigger in width (hig                  |             | 73                  | 200            |                | ns           |

| Gate inpu<br>setup time<br>(timer mo   |             | 74                  | 100            |                | ns           |

| Gate inpu<br>input setu<br>(counter r  |             | 75                  | 100            |                | ns           |

| Gate inpu<br>hold time<br>(timer mo    |             | 76                  | 100            |                | ns           |

| Gate inpu<br>input hold<br>(counter r  |             | 77                  | 100            |                | ns           |

| PCLK to o<br>output de<br>(timer mo    | lay         | 78                  |                | 475            | ns           |

| Counter in<br>counter o<br>(counter r  | utput delay | 79                  |                | 475            | ns           |

|                                        |             |                     |                |                |              |

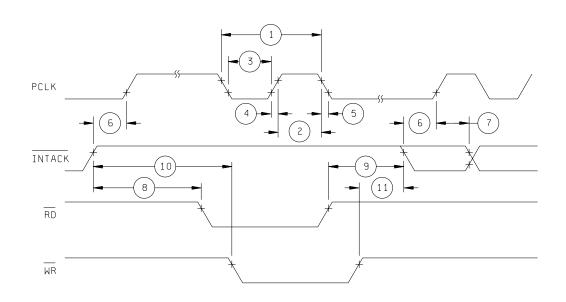

1/ The reference number refers to the identified parameter on figure 3 for device type 01 only.

2/ These parameters must be met to guarantee trigger or gate are valid for the next counter/timer cycle.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 83001 |

|----------------------------------|------------------|----------------|-------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET |

| COLUMBUS, OHIO 43218-3990        |                  | D              | 3     |

# 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

### DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

#### DEPARTMENT OF DEFENSE STANDARDS

| MIL-STD-883  | - | Test Method Standard Microcircuits.                    |

|--------------|---|--------------------------------------------------------|

| MIL-STD-1835 | - | Interface Standard Electronic Component Case Outlines. |

DEPARTMENT OF DEFENSE HANDBOOKS

| MIL-HDBK-103 | - | List of Standard Microcircuit Drawings. |

|--------------|---|-----------------------------------------|

| MIL-HDBK-780 | - | Standard Microcircuit Drawings.         |

(Copies of these documents are available online at <u>http://assist.daps.dla.mil/quicksearch/</u> or <u>http://assist.daps.dla.mil</u> or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

# 3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein. Product built to this drawing that is produced by a Qualified Manufacturer Listing (QML) certified and qualified manufacturer or a manufacturer who has been granted transitional certification to MIL-PRF-38535 may be processed as QML product in accordance with the manufacturers approved program plan and qualifying activity approval in accordance with MIL-PRF-38535. This QML flow as documented in the Quality Management (QM) plan may make modifications to the requirements herein. These modifications shall not affect form, fit, or function of the device. These modifications shall not affect the PIN as described herein. A "Q" or "QML" certification mark in accordance with MIL-PRF-38535 is required to identify when the QML flow option is used.

3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535, appendix A and herein.

3.2.1 <u>Case outlines</u>. The case outlines shall be in accordance with 1.2.2 herein.

3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

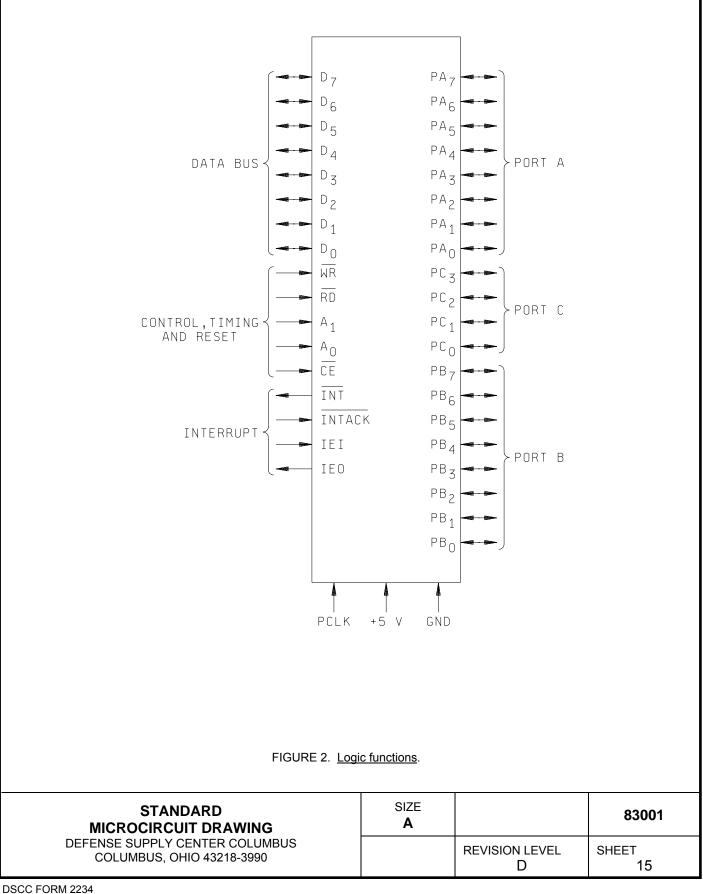

3.2.3 Logic functions. The logic functions shall be as specified on figure 2.

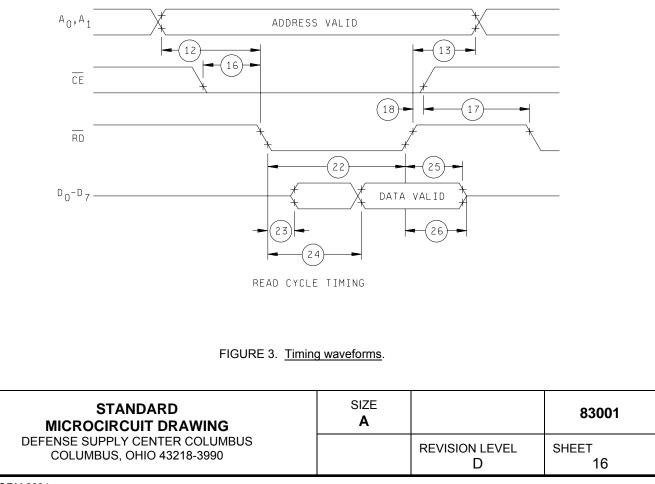

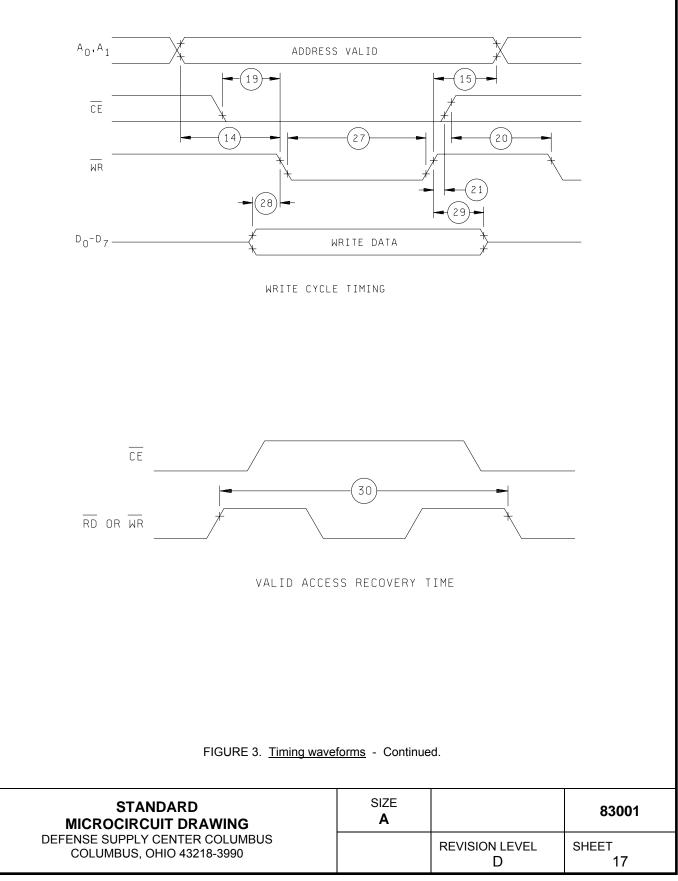

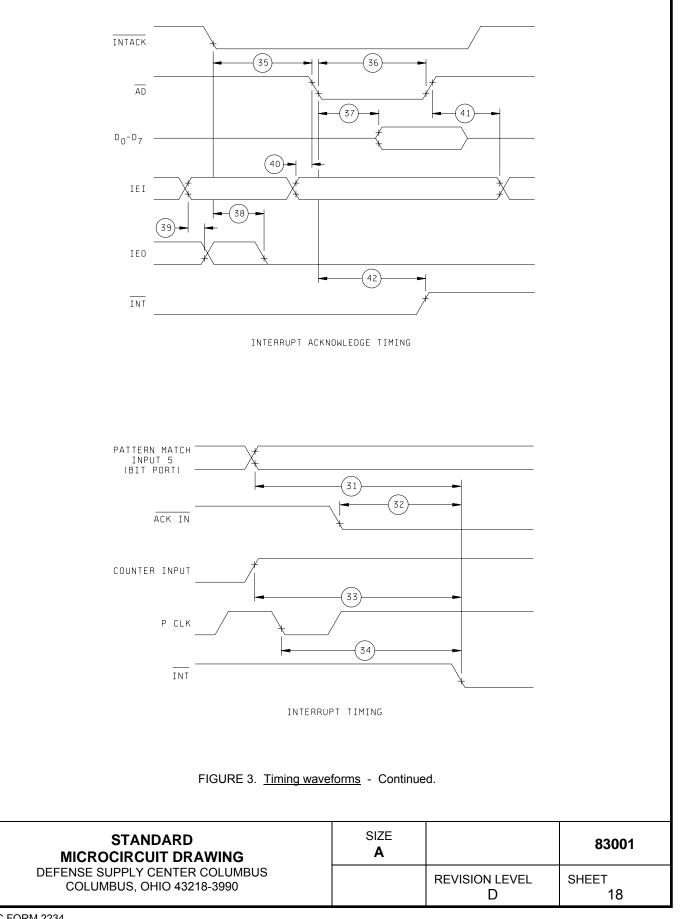

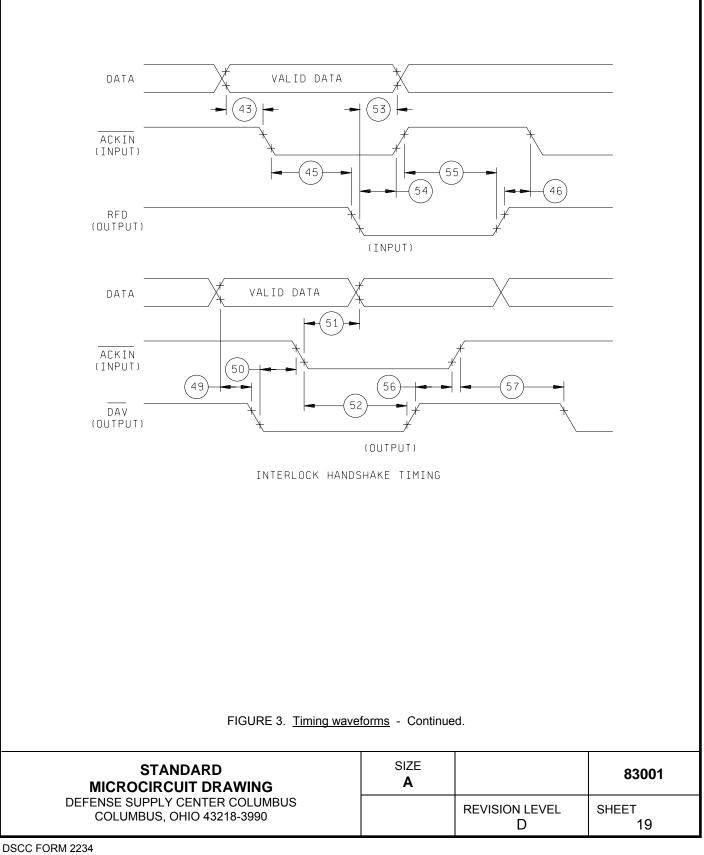

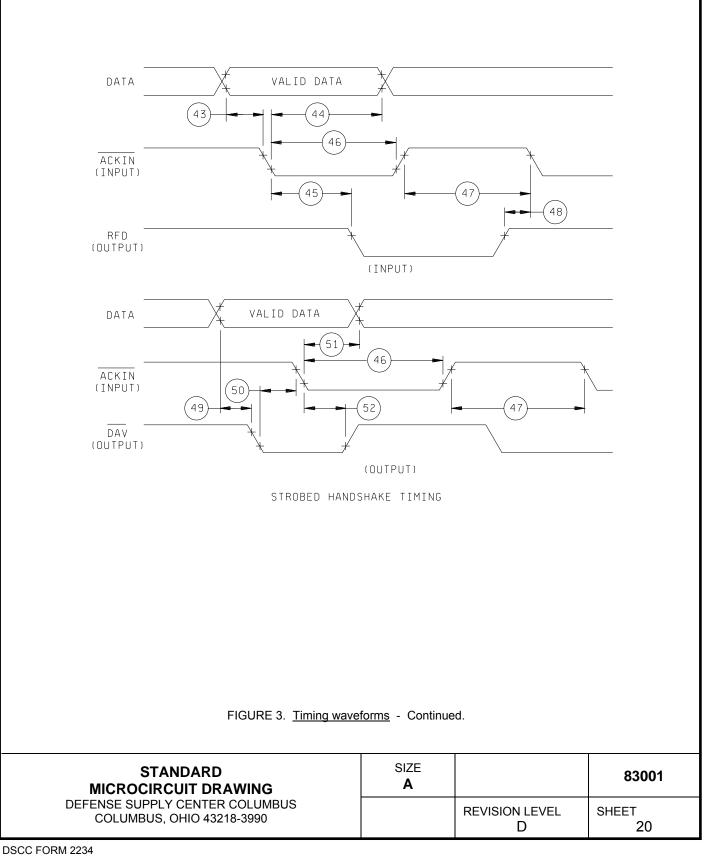

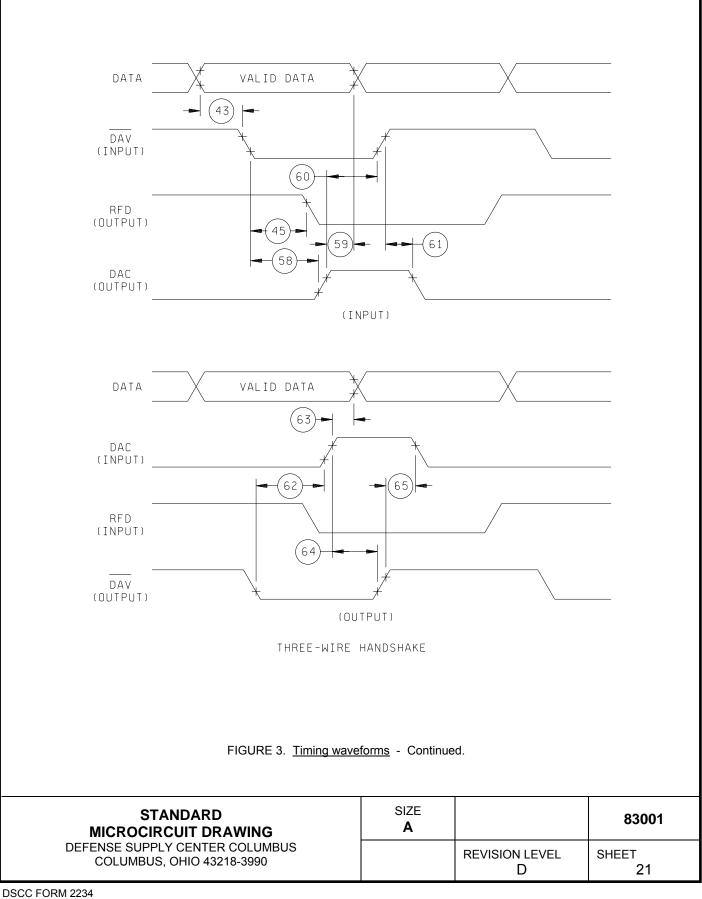

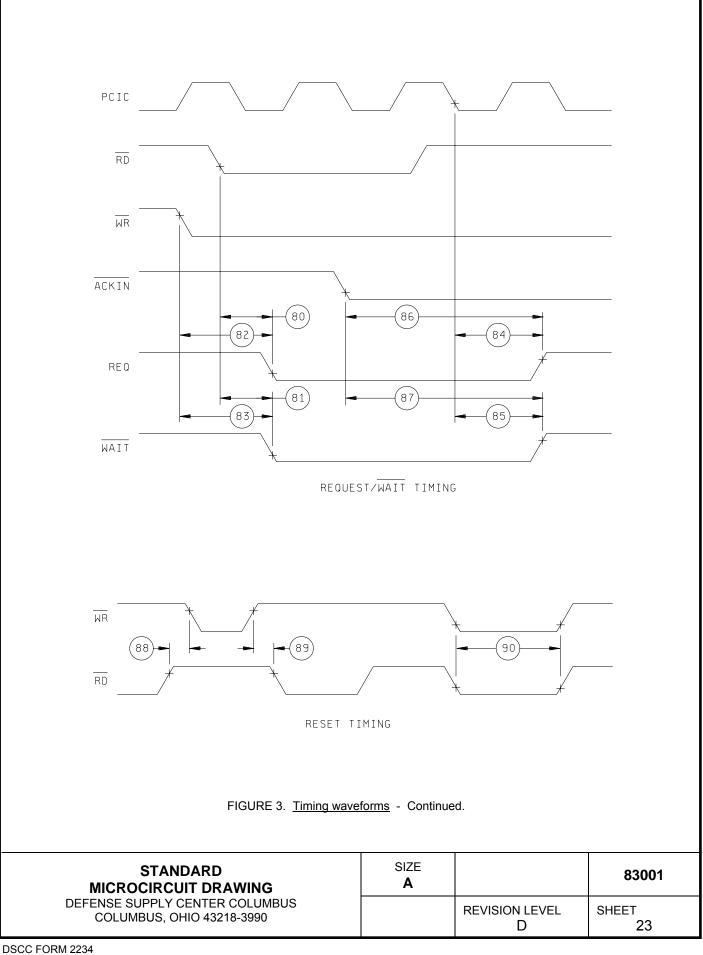

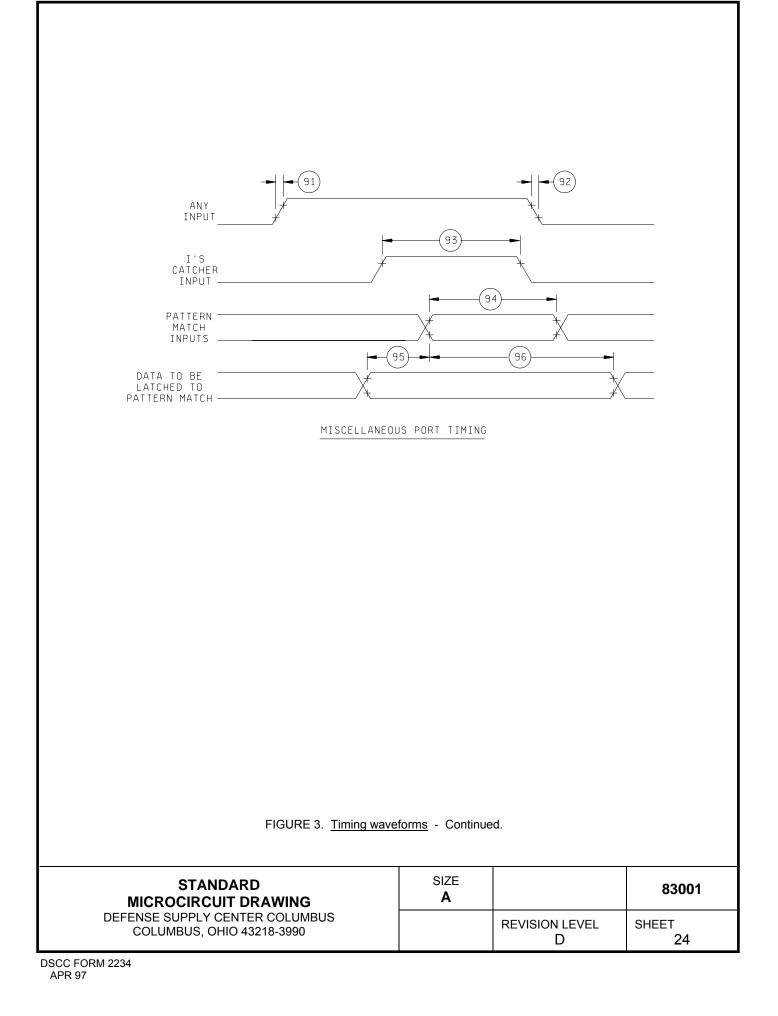

3.2.4 <u>Timing waveforms</u>. The timing waveforms shall be as specified on figure 3.

3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 83001 |

|----------------------------------|------------------|----------------|-------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET |

| COLUMBUS, OHIO 43218-3990        |                  | D              | 4     |

3.5 <u>Marking</u>. Marking shall be in accordance with MIL-PRF-38535, appendix A. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked.

3.5.1 <u>Certification/compliance mark</u>. A compliance indicator "C" shall be marked on all non-JAN devices built in compliance to MIL-PRF-38535, appendix A. The compliance indicator "C" shall be replaced with a "Q" or "QML" certification mark in accordance with MIL-PRF-38535 to identify when the QML flow option is used.

3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-PRF-38535, appendix A and the requirements herein.

3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

3.8 Notification of change. Notification of change to DSCC-VA shall be required for any change that affects this drawing.

3.9 <u>Verification and review</u>. DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 83001 |

|----------------------------------|------------------|----------------|-------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET |

| COLUMBUS, OHIO 43218-3990        |                  | D              | 5     |

| Test                                            | Symbol           | Conditions                                                                                                                                        | Device | Group A   | L          | imits                 | Unit |

|-------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|------------|-----------------------|------|

|                                                 |                  | $\begin{array}{l} 4.5 \ V \leq V_{CC} \leq 5.5 \ V, \\ -55^{\circ}C \leq T_C \leq +125^{\circ}C \\ \text{unless otherwise specified} \end{array}$ | type   | subgroups | Min        | Max                   |      |

| High level input voltage                        | V <sub>IH</sub>  |                                                                                                                                                   | All    | 1, 2, 3   | 2.2        | V <sub>CC</sub> + 0.3 | V    |

|                                                 |                  |                                                                                                                                                   |        | -         |            | <u>1</u> /            |      |

| Low level input voltage                         | V <sub>IL</sub>  |                                                                                                                                                   |        |           | -0.3       | 0.8                   |      |

| Low level output voltage                        | V <sub>OL</sub>  | I <sub>OL</sub> = 2.0 mA                                                                                                                          | _      | _         | <u>1</u> / | 0.4                   |      |

| Lon lovel output reliage                        | • OL             |                                                                                                                                                   | _      |           |            | 0.1                   |      |

| High level output voltage                       | V <sub>OH</sub>  | I <sub>OH</sub> = -250 μA                                                                                                                         |        |           | 2.4        |                       |      |

| Power supply current                            | I <sub>CC</sub>  | V <sub>CC</sub> = 5.5 V                                                                                                                           | All    | 1, 2, 3   |            | 200                   | mA   |

|                                                 |                  | Outputs open                                                                                                                                      |        |           |            |                       |      |

| Input capacitance                               | C <sub>IN</sub>  |                                                                                                                                                   | All    | 4         |            | 10                    | pF   |

|                                                 |                  |                                                                                                                                                   |        | -         |            | <u>1/</u>             | -    |

| Output capacitance                              | C <sub>OUT</sub> |                                                                                                                                                   |        |           |            | 15                    |      |

| Bidirectional capacitance                       | C <sub>I/O</sub> |                                                                                                                                                   |        | _         |            | <u>1</u> /<br>20      |      |

| Brancotional oupdoltanoo                        | 01/0             |                                                                                                                                                   |        |           |            | <u>1</u> /            |      |

| Output leakage current low, open drain outputs  | I <sub>LOL</sub> | $0.4~V \leq V_{OUT} \leq 2.4~V$                                                                                                                   | All    | 1, 2, 3   | -10        | +10                   | μA   |

| Output leakage current high, open drain outputs | I <sub>LOH</sub> |                                                                                                                                                   |        |           | -10        | +10                   |      |

| Input low current<br>(input and bidirectional)  | IL               | $0.4~V \leq V_{IN} \leq 2.4~V$                                                                                                                    |        |           | -10        | +10                   | -    |

| Input high current<br>(input and bidirectional) | IIH              |                                                                                                                                                   |        | -         | -10        | +10                   | -    |

| Maximum frequency                               | f <sub>MAX</sub> |                                                                                                                                                   | 01     | 9, 10, 11 | 4.0        |                       | MHz  |

| <u>1</u> /                                      |                  |                                                                                                                                                   | 02     |           | 6.0        |                       |      |

| Functional tests                                | I <sub>CEX</sub> | See paragraph 4.3.1c.                                                                                                                             | All    | 7, 8      |            |                       |      |

| See footnotes at end of table.                  |                  |                                                                                                                                                   |        |           |            |                       |      |

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 83001 |

|----------------------------------|------------------|----------------|-------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET |

| COLUMBUS, OHIO 43218-3990        |                  | D              | 6     |

| Test                                                                                          | Symbol                                   | Conditions                                                                                                                                        | Device | Group A   | Lir | nits | Unit |

|-----------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|-----|------|------|

|                                                                                               |                                          | $\begin{array}{l} 4.5 \ V \leq V_{CC} \leq 5.5 \ V, \\ -55^{\circ}C \leq T_C \leq +125^{\circ}C \\ \text{unless otherwise specified} \end{array}$ | type   | subgroups | Min | Max  |      |

| PCLK cycle time                                                                               | t <sub>CYC1</sub>                        | Reference number 1.                                                                                                                               | 01     | 9, 10, 11 | 250 | 4000 | ns   |

|                                                                                               |                                          | <u>2/3/4/</u>                                                                                                                                     | 02     |           | 165 | 4000 |      |

| PCLK width high                                                                               | t <sub>PWH1</sub>                        | Reference number 2.                                                                                                                               | 01     | 9, 10, 11 | 105 | 2000 | ns   |

| <u>1</u> /                                                                                    |                                          | <u>2/3/4/</u>                                                                                                                                     | 02     |           | 70  | 2000 |      |

| PCLK width low                                                                                | t <sub>PWL1</sub>                        | Reference number 3.                                                                                                                               | 01     | 9, 10, 11 | 105 | 2000 | ns   |

| <u>1</u> /                                                                                    |                                          | <u>2/3/4/</u>                                                                                                                                     | 02     |           | 70  | 2000 |      |

| PCLK rise time                                                                                | t <sub>RC1</sub>                         | Reference number 4.                                                                                                                               | 01     | 9, 10, 11 |     | 20   | ns   |

| <u>1/</u>                                                                                     |                                          | <u>2/3/4/</u>                                                                                                                                     | 02     |           |     | 10   |      |

| PCLK fall time                                                                                | t <sub>FC1</sub>                         | Reference number 5.                                                                                                                               | 01     | 9, 10, 11 |     | 20   | ns   |

| <u> <u> </u></u>                                                                              |                                          | <u>2/3/4/</u>                                                                                                                                     | 02     |           |     | 15   |      |

| INTACK to PCLK setup time $\underline{1}^{/}$                                                 | t <sub>SHL1</sub> ,<br>t <sub>SLH1</sub> | Reference number 6.<br><u>2/ 3/ 4</u> /                                                                                                           | All    | 9, 10, 11 | 100 |      | ns   |

| INTACK to PCLK hold time <u>1</u> /                                                           | t <sub>HHL1</sub> ,<br>t <sub>HLH1</sub> | Reference number 7.<br><u>2/3/4</u> /                                                                                                             | All    | 9, 10, 11 | 0   |      | ns   |

| INTACK to RD setup time<br><u>1</u> /                                                         | t <sub>SHL2</sub> ,<br>t <sub>SLH2</sub> | Reference number 8.<br><u>2</u> / <u>3</u> / <u>4</u> /                                                                                           | All    | 9, 10, 11 | 200 |      | ns   |

| INTACK to RD hold time<br><u>1</u> /                                                          | t <sub>HHL2</sub> ,<br>t <sub>HLH2</sub> | Reference number 9.<br><u>2/ 3/ 4/</u>                                                                                                            | All    | 9, 10, 11 | 0   |      | ns   |

| INTACK to WR setup time<br><u>1</u> /                                                         | t <sub>SHL3</sub> ,<br>t <sub>SLH3</sub> | Reference number 10.<br><u>2</u> / <u>3</u> / <u>4</u> /                                                                                          | All    | 9, 10, 11 | 200 |      | ns   |

| INTACK to $\overline{WR}\uparrow$ hold time $\underline{1}/$                                  | t <sub>HHL3</sub> ,<br>t <sub>HLH3</sub> | Reference number 11.<br><u>2/3/4/</u>                                                                                                             | All    | 9, 10, 11 | 0   |      | ns   |

| Address to RD↓ setup time                                                                     | t <sub>SHL4</sub> ,<br>t <sub>SLH4</sub> | Reference number 12.<br><u>2</u> / <u>3</u> / <u>4</u> /                                                                                          | All    | 9, 10, 11 | 80  |      | ns   |

| Address to $\overline{\text{RD}}_{\uparrow}$ hold time $\underline{1}/$                       | t <sub>HHL4</sub> ,<br>t <sub>HLH4</sub> | Reference number 13.<br><u>2/3/4/</u>                                                                                                             | All    | 9, 10, 11 | 0   |      | ns   |

| Address to WR↓ setup time                                                                     | t <sub>SHL5</sub> ,<br>t <sub>SLH5</sub> | Reference number 14.<br><u>2/3/4/</u>                                                                                                             | All    | 9, 10, 11 | 80  |      | ns   |

| Address to $\overline{WR}$ hold time $\underline{1}/$                                         | t <sub>HHL5</sub> ,<br>t <sub>HLH5</sub> | Reference number 15.<br><u>2/3/4/</u>                                                                                                             | All    | 9, 10, 11 | 0   |      | ns   |

| $\overline{CE} \text{ low to } \overline{RD} \downarrow \text{ setup time} \\ \underline{5}/$ | t <sub>SHL6</sub>                        | Reference number 16.<br><u>2/ 3/ 4</u> /                                                                                                          | All    | 9, 10, 11 | 0   |      | ns   |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 83001 |

|----------------------------------|------------------|----------------|-------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET |

| COLUMBUS, OHIO 43218-3990        |                  | D              | 7     |

| Test                                                              | Symbol                                     | Conditions                                                                                                | Device | Group A   | Lii  | mits                             | Uni |

|-------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------|-----------|------|----------------------------------|-----|

|                                                                   |                                            | $4.5~V \leq V_{CC} \leq 5.5~V, \\ -55^{\circ}C \leq T_C \leq +125^{\circ}C \\ unless otherwise specified$ | type   | subgroups | Min  | Max                              |     |

| $\overline{CE}$ high to $\overline{RD}$ setup time                | t <sub>SLH7</sub>                          | Reference number 17.                                                                                      | 01     | 9, 10, 11 | 100  |                                  | ns  |

| <u>1/</u> 5/                                                      |                                            | <u>2/3/4/</u>                                                                                             | 02     |           | 70   |                                  |     |

| CE to RD↑ hold time<br><u>5</u> /                                 | t <sub>HHL6</sub> ,<br>t <sub>HLH6</sub>   | Reference number 18.<br><u>2/ 3/ 4</u> /                                                                  | All    | 9, 10, 11 | 0    |                                  | ns  |

| $\overline{CE}$ low to $\overline{WR}{\downarrow}$ setup time     | t <sub>SHL8</sub>                          | Reference number 19.<br><u>2/ 3/ 4</u> /                                                                  | All    | 9, 10, 11 | 0    |                                  | ns  |

| $\overline{CE}$ high to $\overline{WR}$ $\downarrow$ setup time   | t <sub>SLH9</sub>                          | Reference number 20.                                                                                      | 01     | 9, 10, 11 | 100  |                                  | ns  |

| <u>1</u> /                                                        |                                            | <u>2/ 3/ 4/</u>                                                                                           | 02     |           | 70   |                                  |     |

| CE to WR↑ hold time                                               | t <sub>HHL7</sub> ,<br>t <sub>HLH7</sub>   | Reference number 21.<br><u>2/3/4/</u>                                                                     | All    | 9, 10, 11 | 0    |                                  | ns  |

| RD to low width                                                   | t <sub>PWL2</sub>                          | Reference number 22.                                                                                      | 01     | 9, 10, 11 | 390  |                                  | ns  |

| <u>1</u> / <u>5</u> /                                             |                                            | <u>2/3/4/</u>                                                                                             | 02     |           | 250  |                                  |     |

| RD↓ to read data active<br>delay <u>1</u> /                       | t <sub>PHL1</sub> ,<br>t <sub>PLH1</sub>   | Reference number 23.<br><u>2</u> / <u>3</u> / <u>4</u> /                                                  | All    | 9, 10, 11 | 0    |                                  | ns  |

| $\overline{RD}$ to read data valid                                | t <sub>PHL2</sub> ,                        | Reference number 24.                                                                                      | 01     | 9, 10, 11 |      | 255                              | ns  |

| delay <u>1</u> /                                                  | t <sub>PLH2</sub>                          | <u>2/3/4</u> /                                                                                            | 02     |           |      | 180                              |     |

| RD↑ to read data not valid<br>delay <u>1</u> /                    | t <sub>PHL3</sub> ,<br>t <sub>PLH3</sub>   | Reference number 25.<br><u>2</u> / <u>3</u> / <u>4</u> /                                                  | All    | 9, 10, 11 | 0    |                                  | ns  |

| RD↑ to read data float                                            | t <sub>PHZ1</sub> ,                        | Reference number 26.                                                                                      | 01     | 9, 10, 11 |      | 70                               | ns  |

| delay <u>6</u> /                                                  | t <sub>PZH1</sub>                          | <u>2/3/4/</u>                                                                                             | 02     |           |      | 45                               |     |

| WR low width                                                      | t <sub>PWL3</sub>                          | Reference number 27.                                                                                      | 01     | 9, 10, 11 | 390  |                                  | ns  |

| <u><u>1</u>/</u>                                                  |                                            | <u>2/3/4/</u>                                                                                             | 02     |           | 250  |                                  |     |

| Write data to WR↓ setup<br>time <u>1</u> /                        | t <sub>SHL10</sub> ,<br>t <sub>SLH10</sub> | Reference number 28.<br><u>2/ 3/ 4/</u>                                                                   | All    | 9, 10, 11 | 0    |                                  | ns  |

| Write data to $\overline{WR}\uparrow$ hold time $\underline{1}/$  | t <sub>HHL8</sub> ,<br>t <sub>HLH8</sub>   | Reference number 29.<br><u>2</u> / <u>3</u> / <u>4</u> /                                                  | All    | 9, 10, 11 | 0    |                                  | ns  |

| Valid access recovery time                                        | t <sub>CYC2</sub>                          | Reference number 30.                                                                                      | 01     | 9, 10, 11 | 1000 |                                  | ns  |

| <u>1</u> / <u>7</u> /                                             |                                            | <u>2/3/4</u> /                                                                                            | 02     |           | 650  |                                  |     |

| Pattern match to INT delay<br>(bit port) <u>1</u> /               | t <sub>PHL4</sub>                          | Reference number 31.<br><u>2</u> / <u>3</u> / <u>4</u> /                                                  | All    | 9, 10, 11 |      | 2*(t <sub>CYC1</sub> )<br>+ 800  | ns  |

| ACKIN to INT delay (port<br>with handshake) <u>1</u> / <u>8</u> / | t <sub>PHL5</sub>                          | Reference number 32.<br><u>2/</u> <u>3/</u> <u>4/</u>                                                     | All    | 9, 10, 11 |      | 10*(t <sub>CYC1</sub> )<br>+ 600 | ns  |

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 83001 |

|----------------------------------|------------------|----------------|-------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET |

| COLUMBUS, OHIO 43218-3990        |                  | D              | 8     |

| Test                                                    | Symbol                                     | Conditions                                                                                                | Device | Group A   | Limits                 |                                 | Uni |

|---------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------|-----------|------------------------|---------------------------------|-----|

|                                                         |                                            | $4.5~V \leq V_{CC} \leq 5.5~V, \\ -55^{\circ}C \leq T_C \leq +125^{\circ}C \\ unless otherwise specified$ | type   | subgroups | Min                    | Max                             |     |

| Counter input to INT delay<br>(counter mode) <u>1</u> / | t <sub>PHL6</sub>                          | Reference number 33.<br><u>2/ 3/ 4/</u>                                                                   | All    | 9, 10, 11 |                        | 2*(t <sub>CYC1</sub> )<br>+ 700 | ns  |

| PCLK to INT delay<br>(timer mode) <u>1</u> /            | t <sub>PHL7</sub>                          | Reference number 34.<br><u>2/</u> <u>3/</u> <u>4</u> /                                                    | All    | 9, 10, 11 |                        | 3*(t <sub>CYC1</sub> )<br>+ 700 | ns  |

| INTACK to RD↓                                           | t <sub>SHL11</sub> ,                       | Reference number 35.                                                                                      | 01     | 9, 10, 11 | 350                    |                                 | ns  |

| (acknowledge setup time)<br><u>1/_9</u> /               | t <sub>SLH11</sub>                         | <u>2/3/4/</u>                                                                                             | 02     | -         | 250                    |                                 |     |

| RD acknowledge width                                    | t <sub>PWL4</sub>                          | Reference number 36.                                                                                      | 01     | 9, 10, 11 | 350                    |                                 | ns  |

| <u>1</u> /                                              |                                            | <u>2/ 3/ 4</u> /                                                                                          | 02     | _         | 250                    |                                 |     |

| $\overline{RD}$ (acknowledge) to read                   | t <sub>PHL8</sub> ,                        | Reference number 37.                                                                                      | 01     | 9, 10, 11 |                        | 250                             | ns  |

| data valid delay <u>1</u> /                             | t <sub>PLH8</sub>                          | <u>2/3/4/</u>                                                                                             | 02     |           |                        | 180                             |     |

| INTACK↓ to IEO↓ delay                                   | t <sub>PHL9</sub>                          | Reference number 38.                                                                                      | 01     | 9, 10, 11 |                        | 350                             | ns  |

| <u>1/ 9</u> /                                           |                                            | <u>2/3/4/</u>                                                                                             | 02     |           |                        | 250                             |     |

| IEI to IEO delay                                        | t <sub>PHL10</sub>                         | Reference number 39.                                                                                      | 01     | 9, 10, 11 |                        | 150                             | ns  |

| <u><u> </u></u>                                         |                                            | <u>2/3/4/</u>                                                                                             | 02     |           |                        | 100                             |     |

| IEI to $\overline{RD}\downarrow$ (acknowledge)          | t <sub>SHL12</sub> ,                       | Reference number 40.                                                                                      | 01     | 9, 10, 11 | 100                    |                                 | ns  |

| setup time <u>1/ 9</u> /                                | t <sub>SLH12</sub>                         | <u>2/3/4/</u>                                                                                             | 02     |           | 70                     |                                 |     |

| IEI to RD↑ (acknowledge)                                | t <sub>HHL9</sub> ,                        | Reference number 41.                                                                                      | 01     | 9, 10, 11 | 100                    |                                 | ns  |

| hold time <u>1</u> /                                    | t <sub>HLH9</sub>                          | <u>2/3/4/</u>                                                                                             | 02     |           | 70                     |                                 |     |

| RD↓ (acknowledge) to<br>INT delay <u>1</u> /            | t <sub>PHL11</sub>                         | Reference number 42.<br><u>2/ 3/ 4/</u>                                                                   | All    | 9, 10, 11 |                        | 600                             | ns  |

| Data input to ACKIN↓<br>setup time <u>1</u> /           | t <sub>SHL13</sub> ,<br>t <sub>SLH13</sub> | Reference number 43.<br><u>2/ 3/ 4/</u>                                                                   | All    | 9, 10, 11 | 0                      |                                 | ns  |

| ACKIN↓ to RFD↓ delay<br><u>1</u> /                      | t <sub>PHL12</sub>                         | Reference number 45.<br><u>2/ 3/ 4/</u>                                                                   | All    | 9, 10, 11 | 0                      |                                 | ns  |

| RFD↑ to ACKIN↓ delay<br><u>1</u> /                      | t <sub>HHL10</sub>                         | Reference number 48.<br><u>2/ 3/ 4</u> /                                                                  | All    | 9, 10, 11 | 0                      |                                 | ns  |

| Data out to DAV↓ setup                                  | t <sub>PHL13</sub> ,                       | Reference number 49.                                                                                      | 01     | 9, 10, 11 | 25                     |                                 | ns  |

| time <u>1</u> / <u>10</u> /                             | t <sub>PLH13</sub>                         | <u>2/ 3/ 4/</u>                                                                                           | 02     |           | 20                     |                                 |     |

| DAV↓ to ACKIN↓ delay<br><u>1</u> /                      | t <sub>SHL14</sub>                         | Reference number 50.<br><u>2/</u> <u>3/</u> <u>4</u> /                                                    | All    | 9, 10, 11 | 0                      |                                 | ns  |

| Data out to ACKIN↓ hold                                 | t <sub>HHL11</sub> ,                       | Reference number 51.                                                                                      | All    | 9, 10, 11 | 2*(t <sub>CYC1</sub> ) |                                 | ns  |

| time <u>1</u> /                                         | t <sub>HLH11</sub>                         | <u>2/ 3/ 4</u> /                                                                                          |        |           |                        |                                 |     |

| See footnotes at end of table.                          |                                            |                                                                                                           |        |           |                        |                                 |     |

|                                                         |                                            |                                                                                                           |        |           |                        |                                 |     |

**REVISION LEVEL**

D

SHEET

9

DSCC FORM 2234 APR 97

DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43218-3990

| Test                                                                                                                                                                          | Symbol                                     | Conditions                                                                                                                                  | Device | Group A   | Lim                    | its | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|------------------------|-----|------|

|                                                                                                                                                                               |                                            | $\begin{array}{l} 4.5 \ V \leq V_{CC} \leq 5.5 \ V, \\ -55^{o}C \leq T_{C} \leq +125^{o}C \\ \text{unless otherwise specified} \end{array}$ | type   | subgroups | Min                    | Max |      |

| ACKIN↓ to DAV↑ delay<br><u>1</u> /                                                                                                                                            | t <sub>PLH14</sub>                         | Reference number 52.<br><u>2/</u> <u>3/</u> <u>4/</u>                                                                                       | All    | 9, 10, 11 | 2*(t <sub>CYC1</sub> ) |     | ns   |

| RFD↓ to ACKIN↑ delay<br>(interlocked handshake)<br><u>1</u> /                                                                                                                 | t <sub>HLH12</sub>                         | Reference number 54.<br><u>2/ 3/ 4/</u>                                                                                                     | All    | 9, 10, 11 | 0                      |     | ns   |

| $\overrightarrow{ACKIN}$ ( $\overrightarrow{DAV}$ )↑ to RFD↑<br>delay (interlocked and three<br>wire handshake) <u>1</u> /                                                    | t <sub>PLH15</sub>                         | Reference number 55.<br><u>2</u> / <u>3</u> / <u>4</u> /                                                                                    | All    | 9, 10, 11 | 0                      |     | ns   |

| $\overrightarrow{\text{DAV}}\uparrow\overrightarrow{\text{ACKIN}}\uparrow$ to $(\overrightarrow{\text{RFD}})\uparrow$<br>(interlocked and three<br>wire handshake) <u>1</u> / | t <sub>HLH13</sub>                         | Reference number 56.<br><u>2/ 3/ 4</u> /                                                                                                    | All    | 9, 10, 11 | 0                      |     | ns   |

| $\overrightarrow{ACKIN}$ ( $\overrightarrow{RFD}$ ) to $\overrightarrow{DAV}$<br>delay (interlocked and three<br>wire handshake) <u>1</u> /                                   | t <sub>PLH16</sub>                         | Reference number 57.<br><u>2/ 3/ 4/</u>                                                                                                     | All    | 9, 10, 11 | 0                      |     | ns   |

| DAV↓to DAC↑ delay (input<br>three wire handshake) <u>1</u> /                                                                                                                  | t <sub>PLH17</sub>                         | Reference number 58.<br><u>2/</u> <u>3/</u> <u>4/</u>                                                                                       | All    | 9, 10, 11 | 0                      |     | ns   |

| Data input to DAC↑ hold time (three wire handshake) <u>1</u> /                                                                                                                | t <sub>HHL14</sub> ,<br>t <sub>HLH14</sub> | Reference number 59.<br><u>2/ 3/ 4/</u>                                                                                                     | All    | 9, 10, 11 | 0                      |     | ns   |

| DAC↑ to DAV↓ delay (input three wire handshake) <u>1</u> /                                                                                                                    | t <sub>HLH15</sub>                         | Reference number 60.<br><u>2/ 3/ 4/</u>                                                                                                     | All    | 9, 10, 11 | 0                      |     | ns   |

| DAV↑ to DAC↓ delay (input<br>three wire handshake) <u>1</u> /                                                                                                                 | t <sub>PHL18</sub>                         | Reference number 61.<br><u>2/ 3/ 4/</u>                                                                                                     | All    | 9, 10, 11 | 0                      |     | ns   |

| DAV↓ to DAC↑ delay (output three wire handshake) <u>1</u> /                                                                                                                   | t <sub>SLH15</sub>                         | Reference number 62.<br><u>2/ 3/ 4/</u>                                                                                                     | All    | 9, 10, 11 | 0                      |     | ns   |

| Data output to DAC $\uparrow$ hold time (three wire handshake) $\underline{1}/$                                                                                               | t <sub>PHL19</sub> ,<br>t <sub>PLH19</sub> | Reference number 63.<br><u>2/ 3/ 4/</u>                                                                                                     | All    | 9, 10, 11 | 2*(t <sub>CYC1</sub> ) |     | ns   |

| DAC $\uparrow$ to DAV $\uparrow$ delay (output three wire handshake) <u>1</u> /                                                                                               | t <sub>PHL20</sub>                         | Reference number 64.<br><u>2/ 3/ 4/</u>                                                                                                     | All    | 9, 10, 11 | 2*(t <sub>CYC1</sub> ) |     | ns   |

| DAV↑ to DAC↓ delay (output three wire handshake) <u>1</u> /                                                                                                                   | t <sub>HHL16</sub>                         | Reference number 65.<br><u>2/ 3/ 4/</u>                                                                                                     | All    | 9, 10, 11 | 0                      |     | ns   |

| Counter input cycle time $\underline{1}/$                                                                                                                                     | t <sub>CYC3</sub>                          | Reference number 66.<br><u>2/ 3/ 4</u> /                                                                                                    | 01     | 9, 10, 11 | 500<br>330             |     | ns   |

| Counter input high width <u>1/</u>                                                                                                                                            | t <sub>PWH5</sub>                          | Reference number 67.<br><u>2/ 3/ 4/</u>                                                                                                     | 01     | 9, 10, 11 | 230<br>150             |     | ns   |

| See footnotes at end of table.                                                                                                                                                |                                            |                                                                                                                                             |        |           | I                      |     | _    |

| SIANDARD                       |  |

|--------------------------------|--|

| MICROCIRCUIT DRAWING           |  |

| DEFENSE SUPPLY CENTER COLUMBUS |  |

| COLUMBUS, OHIO 43218-3990      |  |

| COLUMBUS, OHIO 43218-3990      |  |

| SIZE<br>A |                     | 83001       |

|-----------|---------------------|-------------|

|           | REVISION LEVEL<br>D | SHEET<br>10 |

| Test                                                           | Symbol             | Conditions                                                                                                                                                                  | Device | Group A   | Li  | mits                             | Unit |

|----------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|-----|----------------------------------|------|

|                                                                | Gymbol             | $\begin{array}{l} 4.5 \text{ V} \leq V_{CC} \leq 5.5 \text{ V},\\ -55^{\circ}\text{C} \leq T_{C} \leq +125^{\circ}\text{C}\\ \text{unless otherwise specified} \end{array}$ | type   | subgroups | Min | Max                              |      |

| Counter input low width                                        | t <sub>PWL5</sub>  | Reference number 68.                                                                                                                                                        | 01     | 9, 10, 11 | 230 |                                  | ns   |

| <u>1/</u>                                                      |                    | <u>2/3/4/</u>                                                                                                                                                               | 02     |           | 150 |                                  |      |

| Counter input fall time                                        | t <sub>FC2</sub>   | Reference number 69.                                                                                                                                                        | 01     | 9, 10, 11 |     | 20                               | ns   |

| <u>1/</u>                                                      |                    | <u>2/3/4/</u>                                                                                                                                                               | 02     |           |     | 15                               |      |

| Counter input rise time                                        | t <sub>RC2</sub>   | Reference number 70.                                                                                                                                                        | 01     | 9, 10, 11 |     | 20                               | ns   |

| <u>1</u> /                                                     |                    | <u>2/3/4</u> /                                                                                                                                                              | 02     |           |     | 15                               |      |

| $\overline{RD} \downarrow$ to $REQ \downarrow$ delay           | t <sub>PHL21</sub> | Reference number 80.<br><u>2/ 3/ 4</u> /                                                                                                                                    | 01     | 9, 10, 11 |     | 500                              | ns   |

| $\overline{RD}\downarrow$ to $\overline{WAIT}\downarrow$ delay | t <sub>PHL22</sub> | Reference number 81.<br><u>2/</u> 3/4/                                                                                                                                      | 01     | 9, 10, 11 |     | 500                              | ns   |

| $\overline{WR}$ to REQ delay                                   | t <sub>PHL23</sub> | Reference number 82.<br><u>2/ 3/ 4</u> /                                                                                                                                    | 01     | 9, 10, 11 |     | 500                              | ns   |

| $\overline{WR}$ to $\overline{WAIT}$ delay                     | t <sub>PHL24</sub> | Reference number 83.<br><u>2/ 3/ 4</u> /                                                                                                                                    | 01     | 9, 10, 11 |     | 500                              | ns   |

| $PCLK{\downarrow}$ to $REQ{\uparrow}$ delay                    | t <sub>PHL25</sub> | Reference number 84.<br><u>2/</u> <u>3/</u> <u>4</u> /                                                                                                                      | 01     | 9, 10, 11 |     | 300                              | ns   |

| PCLK↓ to WAIT↑ delay                                           | t <sub>PHL26</sub> | Reference number 85.<br><u>2/</u> 3/4/                                                                                                                                      | 01     | 9, 10, 11 |     | 300                              | ns   |

| ACKIN↓ to REQ↑ delay<br><u>8/</u>                              | t <sub>PHL27</sub> | Reference number 86.<br><u>2/</u> 3/4/                                                                                                                                      | 01     | 9, 10, 11 |     | 8*(t <sub>CYC1</sub> )<br>+ 1000 | ns   |

| ACKIN↓ to WAIT↑ delay<br><u>8/</u>                             | t <sub>PHL28</sub> | Reference number 87.<br><u>2/</u> 3/4/                                                                                                                                      | 01     | 9, 10, 11 |     | 10*(t <sub>CYC1</sub> )<br>+ 600 | ns   |

| Delay from RD↑ to WR↓ for<br>no reset <u>1</u> /               | t <sub>SHL16</sub> | Reference number 88.<br><u>2/</u> 3/4/                                                                                                                                      | All    | 9, 10, 11 | 50  |                                  | ns   |

| Delay from WR↑ to RD↓ for<br>no reset <u>1</u> /               | t <sub>SHL17</sub> | Reference number 89.<br><u>2/</u> 3/4/                                                                                                                                      | All    | 9, 10, 11 | 50  |                                  | ns   |

| Width of RD and WR low to insure reset                         | t <sub>PWL6</sub>  | Reference number 90.<br><u>2/ 3/ 4</u> /                                                                                                                                    | All    | 9, 10, 11 | 250 |                                  | ns   |

| Any input rise time not otherwise specified <u>1</u> /         | t <sub>RI1</sub>   | Reference number 91.<br><u>2/</u> 3/4/                                                                                                                                      | All    | 9, 10, 11 |     | 100                              | ns   |

| Any input fall time not otherwise specified <u>1</u> /         | t <sub>FI1</sub>   | Reference number 92.<br><u>2/ 3/ 4</u> /                                                                                                                                    | All    | 9, 10, 11 |     | 100                              | ns   |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 83001 |

|----------------------------------|-----------|----------------|-------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET |

| COLUMBUS, OHIO 43218-3990        |           | D              | 11    |

|                                                                     | TABLE                                      | I. Electrical performance character                                                                                                         | <u>istics</u> - Co | ontinued. |      |      |      |

|---------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------|------|------|------|

| Test                                                                | Symbol                                     | Conditions                                                                                                                                  | Device             | Group A   | Lin  | nits | Unit |

|                                                                     |                                            | $\begin{array}{l} 4.5 \ V \leq V_{CC} \leq 5.5 \ V, \\ -55^{o}C \leq T_{C} \leq +125^{o}C \\ \text{unless otherwise specified} \end{array}$ | type               | subgroups | Min  | Max  |      |

| 1's catcher high width                                              | t <sub>PWH7</sub>                          | Reference number 93.                                                                                                                        | 01                 | 9, 10, 11 | 250  |      | ns   |

| <u>1/ 11/</u>                                                       |                                            | <u>2/ 3/ 4</u> /                                                                                                                            | 02                 |           | 170  |      |      |

| Pattern match input valid                                           | t <sub>PWL8</sub> ,                        | Reference number 94.                                                                                                                        | 01                 | 9, 10, 11 | 750  |      | ns   |

| (bit port) <u>1</u> /                                               | t <sub>PWH8</sub>                          | <u>2/3/4</u> /                                                                                                                              | 02                 |           | 500  |      |      |

| Data latched on pattern<br>match setup time (bit port)<br><u>1/</u> | t <sub>SHL18</sub> ,<br>t <sub>SLH18</sub> | Reference number 95.<br><u>2/ 3/ 4/</u>                                                                                                     | All                | 9, 10, 11 | 0    |      | ns   |

| Data latched on pattern                                             | t <sub>HHL17</sub> ,                       | Reference number 96.                                                                                                                        | 01                 | 9, 10, 11 | 1000 |      | ns   |

| match hold time (bit port)<br><u>1/</u>                             | t <sub>HLH17</sub>                         | <u>2/3/4/</u>                                                                                                                               | 02                 |           | 650  |      |      |

- 1/ Guaranteed if not tested.

- 2/ The reference number refers to the parameter being measured on figure 3.

- 3/ See figure 3.

- <u>4</u>/  $C_L = 50 \text{ pF} \pm 10\%$ .

- 5/ Parameter does not apply to Interrupt Acknowledge transactions.

- 6/ Float delay is measured to the time when the output has changed 0.5 V with minimum ac load and maximum dc load.

- $\underline{7}$ /  $t_{CYC2}$  is 1  $\mu$ s or  $t_{CYC1}$ , whichever is longer.

- <u>8</u>/ The delay is from DAV↓ for three-wire input handshake. The delay is from DAC↑ for three-wire output handshake.

- <u>9</u>/ The parameters for the devices in any particular daisy chain must meet the following constraint: The delay from INTACK↓ to RD↓ must be greater than the sum of tdIA(EIO) for the highest priority peripheral, tsIEI(RDA) for the lowest priority peripheral, and tdIEI(IEO) for each peripheral separating them in the chain.

- 10/ This time can be extended through the use of deskew timers.

- 11/ If the input is programmed inverting, a low-going pulse of the same width will be detected.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 83001 |

|----------------------------------|------------------|----------------|-------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET |

| COLUMBUS, OHIO 43218-3990        |                  | D              | 12    |

| Device<br>types:   |                  | 01 and 02          |                  |  |  |  |

|--------------------|------------------|--------------------|------------------|--|--|--|

| Case<br>outline:   | Q                |                    |                  |  |  |  |

| Terminal<br>number | Terminal<br>name | Terminal<br>number | Terminal<br>name |  |  |  |

| 1                  | D <sub>4</sub>   | 21                 | PC <sub>2</sub>  |  |  |  |

| 2                  | $D_5$            | 22                 | PC <sub>3</sub>  |  |  |  |

| 3                  | D <sub>6</sub>   | 23                 | +5 V             |  |  |  |

| 4                  | D <sub>7</sub>   | 24                 | INT              |  |  |  |

| 5                  | RD               | 25                 | INTACK           |  |  |  |

| 6                  | WR               | 26                 | PA <sub>7</sub>  |  |  |  |

| 7                  | GND              | 27                 | PA <sub>6</sub>  |  |  |  |

| 8                  | PB <sub>0</sub>  | 28                 | $PA_5$           |  |  |  |

| 9                  | PB <sub>1</sub>  | 29                 | PA <sub>4</sub>  |  |  |  |

| 10                 | PB <sub>2</sub>  | 30                 | $PA_3$           |  |  |  |

| 11                 | PB <sub>3</sub>  | 31                 | PA <sub>2</sub>  |  |  |  |

| 12                 | PB <sub>4</sub>  | 32                 | PA <sub>1</sub>  |  |  |  |

| 13                 | PB₅              | 33                 | PA <sub>0</sub>  |  |  |  |

| 14                 | $PB_6$           | 34                 | A <sub>0</sub>   |  |  |  |

| 15                 | PB <sub>7</sub>  | 35                 | A <sub>1</sub>   |  |  |  |

| 16                 | PCLK             | 36                 | CE               |  |  |  |

| 17                 | IEI              | 37                 | D <sub>0</sub>   |  |  |  |

| 18                 | IEO              | 38                 | D <sub>1</sub>   |  |  |  |

| 19                 | PC <sub>0</sub>  | 39                 | D <sub>2</sub>   |  |  |  |

| 20                 | PC <sub>1</sub>  | 40                 | D <sub>3</sub>   |  |  |  |

FIGURE 1. <u>Terminal connections</u>.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 | SIZE<br><b>A</b> |                     | 83001       |

|-------------------------------------------------------------------------------------------------|------------------|---------------------|-------------|

|                                                                                                 |                  | REVISION LEVEL<br>D | SHEET<br>13 |

| Device<br>types:   | 01 and 02        |                    |                  |

|--------------------|------------------|--------------------|------------------|

| Case<br>outline:   | Y                |                    |                  |

| Terminal<br>number | Terminal<br>name | Terminal<br>number | Terminal<br>name |

| 1                  | D <sub>4</sub>   | 23                 | PC <sub>2</sub>  |

| 2                  | D <sub>5</sub>   | 24                 | PC <sub>3</sub>  |

| 3                  | D <sub>6</sub>   | 25                 | +5 V             |

| 4                  | D <sub>7</sub>   | 26                 | INT              |

| 5                  | RD               | 27                 | INTACK           |

| 6                  | NC               | 28                 | NC               |

| 7                  | WR               | 29                 | NC               |

| 8                  | NC               | 30                 | PA <sub>7</sub>  |

| 9                  | GND              | 31                 | PA <sub>6</sub>  |

| 10                 | PB <sub>0</sub>  | 32                 | PA <sub>5</sub>  |

| 11                 | PB <sub>1</sub>  | 33                 | PA <sub>4</sub>  |

| 12                 | PB <sub>2</sub>  | 34                 | PA <sub>3</sub>  |

| 13                 | PB <sub>3</sub>  | 35                 | PA <sub>2</sub>  |

| 14                 | PB <sub>4</sub>  | 36                 | PA <sub>1</sub>  |

| 15                 | PB₅              | 37                 | PA <sub>0</sub>  |

| 16                 | PB <sub>6</sub>  | 38                 | A <sub>0</sub>   |

| 17                 | PB <sub>7</sub>  | 39                 | A <sub>1</sub>   |

| 18                 | PCLK             | 40                 | CE               |

| 19                 | IEI              | 41                 | D <sub>0</sub>   |

| 20                 | IEO              | 42                 | D <sub>1</sub>   |

| 21                 | PC <sub>0</sub>  | 43                 | D <sub>2</sub>   |

| 22                 | PC <sub>1</sub>  | 44                 | D <sub>3</sub>   |

| L                  |                  | u                  |                  |

NC = No connection

FIGURE 1. <u>Terminal connections</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 | SIZE<br><b>A</b> |                     | 83001       |

|-------------------------------------------------------------------------------------------------|------------------|---------------------|-------------|