INCH-POUND

MIL-M-38510/209H

21 April 2014

SUPERSEDING

MIL-M-38510/209G

13 September 2013

#### MILITARY SPECIFICATION

# MICROCIRCUIT, DIGITAL, 8192-BIT, SCHOTTKY, BIPOLAR, PROGRAMMABLE READ-ONLY MEMORY (PROM), MONOLITHIC SILICON

Inactive for new design after 24 July 1995

This specification is approved for use by all Departments and Agencies of the Department of Defense.

The requirements for acquiring the product herein shall consist of this specification sheet and MIL-PRF-38535.

#### 1. SCOPE

- 1.1 <u>Scope.</u> This specification covers the detail requirements for monolithic silicon, PROM microcircuits which employ thin film nichrome (NiCr) resistors, zapped vertical emitter, tungsten (W), titanium tungsten (TiW), or platinum silicide as the fusible link or programming element. Two product assurance class and a choice of case outlines and lead finishes are provided for each type and are reflected in the complete part number. For this product, the requirements of MIL-M-38510 have been superseded by MIL-PRF-38535, (see 6.4).

- 1.2 Part or Identifying Number (PIN). The PIN is in accordance with MIL-PRF-38535, and as specified herein.

- 1.2.1 <u>Device types.</u> The device types are as follows:

| Device type | <u>Circuit</u>                                                                                   | Access time (ns) |

|-------------|--------------------------------------------------------------------------------------------------|------------------|

| 01          | 2048 word / 4 bits per word PROM with uncommitted collector                                      | 125              |

| 02, 08, 10  | $2048\ word\ /\ 4$ bits per word PROM with active pullup and a third high-impedance state output | 125, 90, 55      |

| 03          | 1024 word / 8 bits per word PROM with uncommitted collector                                      | 90               |

| 04, 09      | 1024 word / 8 bits per word PROM with active pullup and a third high-impedance state output      | 90, 55           |

| 05          | 1024 word / 8 bits per word PROM with active pullup and a third high-impedance state output      | 90               |

| 06          | 1024 word / 8 bits per word PROM with uncommitted collector                                      | 90               |

| NOTE:       | Device type 07 was deleted from this document under revision D.                                  |                  |

1.2.2 <u>Device class.</u> The device class is the product assurance level as defined in MIL-PRF-38535.

Comments, suggestions, or questions on this document should be addressed to: Commander, Defense Supply Center Columbus, ATTN: DLA Land and Maritime-VAS, P. O. Box 3990, Columbus, OH 43218-3990, or emailed to memory@dla.mil. Since contact information can change, you may want to verify the currency of this address information using the ASSIST Online database at https://assist.dla.mil

AMSC N/A FSC 5962

## 1.2.3 <u>Case outlines.</u> The case outlines are as designated in MIL-STD-1835 and as follows:

| Outline letter                                                    | Descriptive designator                                                                                  | Termin                     | nals Package style                                                  |  |  |  |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------|--|--|--|

| J<br>K<br>V<br>X<br>Y                                             | GDIP1-T24 or CDIP2-T24<br>GDFP2-F24 or CDFP3-F24<br>GDIP1-T18 or CDIP2-T18<br>See figure 1<br>GDFP2-F18 | 24<br>24<br>18<br>18<br>18 | Dual-in-line<br>Flat pack<br>Dual-in-line<br>Flat pack<br>Flat pack |  |  |  |

| 1.3 Absolute maximum                                              | ratings.                                                                                                |                            |                                                                     |  |  |  |

| Input voltage range<br>Storage temperature<br>Lead temperature (s | e rangeoldering, 10 seconds)junction to case (θ <sub>J</sub> C) :                                       |                            | -1.5 V at -10 mA to +5.5 V -65°C to +150°C                          |  |  |  |

| Cases J, K, V, and Case X                                         | nd Y                                                                                                    |                            | 35°C/W maximum 1/                                                   |  |  |  |

|                                                                   |                                                                                                         |                            |                                                                     |  |  |  |

| Device types 03,                                                  | 02, 08, and 10<br>04, 05, 06, and 09                                                                    |                            | 1.1 W <u>2</u> /                                                    |  |  |  |

| Maximum junction te                                               | emperature (T <sub>J</sub> )                                                                            |                            | +175°C                                                              |  |  |  |

| 1.4 Recommended ope                                               | rating conditions.                                                                                      |                            |                                                                     |  |  |  |

| Supply voltage range                                              | 9                                                                                                       |                            | +4.5 V dc minimum to<br>+5.5 V dc maximum                           |  |  |  |

| Minimum high-level                                                | input voltage (V <sub>IH</sub> )                                                                        |                            | 2.0 V                                                               |  |  |  |

| Maximum low-level i<br>Normalized fanout (e                       | nput voltage (V <sub>IL</sub> )<br>each output) :                                                       |                            | 0.8 V                                                               |  |  |  |

| Device types 01,                                                  | 02, 08, and 10<br>04, 05, 06, and 09                                                                    |                            |                                                                     |  |  |  |

|                                                                   | perature range (T <sub>C</sub> )                                                                        |                            | <del>-</del>                                                        |  |  |  |

<sup>1/</sup> Heat sinking is recommended to reduce the junction temperature.

$<sup>\</sup>underline{2}$ / Must withstand the added  $P_D$  due to short circuit test (e.g.  $I_{OS}$ ).

<sup>3/ 16</sup> mA for circuits B, D, and F devices.

#### 2. APPLICABLE DOCUMENTS

2.1 <u>General.</u> The documents listed in this section are specified in sections 3, 4, or 5 of this specification. This section does not include documents cited in other sections of this specification or recommended for additional information or as examples. While every effort has been made to ensure the completeness of this list, document users are cautioned that they must meet all specified requirements of documents cited in sections 3, 4, or 5 of this specification, whether or not they are listed.

#### 2.2 Government documents.

2.2.1 <u>Specifications and Standards.</u> The following specifications and standards form a part of this specification to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

#### DEPARTMENT OF DEFENSE SPECIFICATIONS

MIL-PRF-38535 - Integrated Circuits (Microcircuits) Manufacturing, General Specification for.

#### DEPARTMENT OF DEFENSE STANDARDS

MIL-STD-883 - Test Method Standard for Microelectronics.

MIL-STD-1835 - Interface Standard Electronic Component Case Outline

(Copies of these documents are available online at <a href="http://quicksearch.dla.mil">http://quicksearch.dla.mil</a> or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.3 <u>Order of precedence</u>. Unless otherwise noted herein or in the contract, in the event of a conflict between the text of this document and the references cited herein (except for related specification sheets), the text of this document takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

#### 3. REQUIREMENTS

- 3.1 <u>Qualification</u>. Microcircuits furnished under this specification shall be products that are manufactured by a manufacturer authorized by the qualifying activity for listing on the applicable qualified manufacturers list before contract award (see 4.3 and 6.3).

- 3.2 <u>Item requirements</u>. The individual item requirements shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

- 3.3 <u>Design, construction, and physical dimensions.</u> The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein.

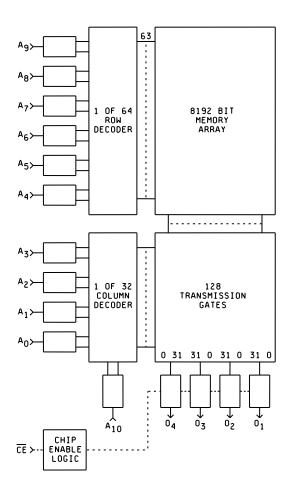

- 3.3.1 Terminal connections. The terminal connections shall be as specified on figure 2.

- 3.3.2 Truth table.

- 3.3.2.1 <u>Unprogrammed devices.</u> The truth tables for unprogrammed devices for contracts involving no altered item drawing shall be as specified on figure 3. When required in groups A, B, or C inspection (see 4.4), the devices shall be programmed by the manufacturer prior to test in a checkerboard pattern (a minimum of 50 percent of the total number of bits programmed) or to any altered item drawing pattern which includes at least 25 percent of the total number of bits programmed.

- 3.3.2.2 <u>Programmed devices.</u> The truth table for programmed devices shall be as specified by the altered item drawing.

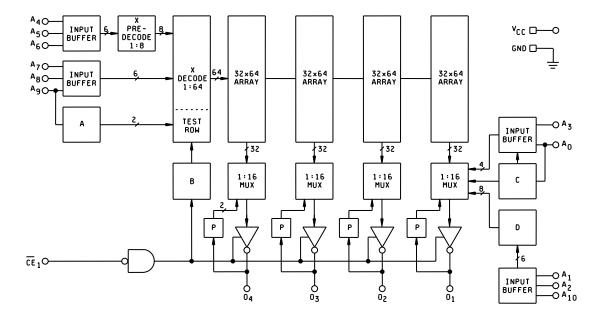

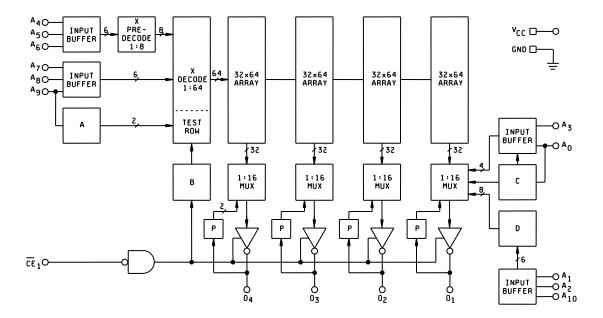

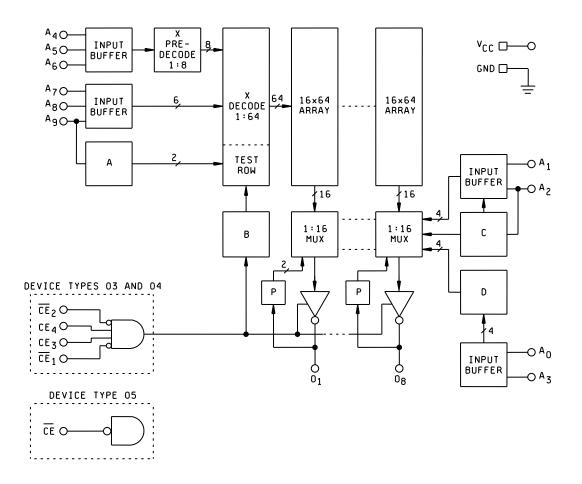

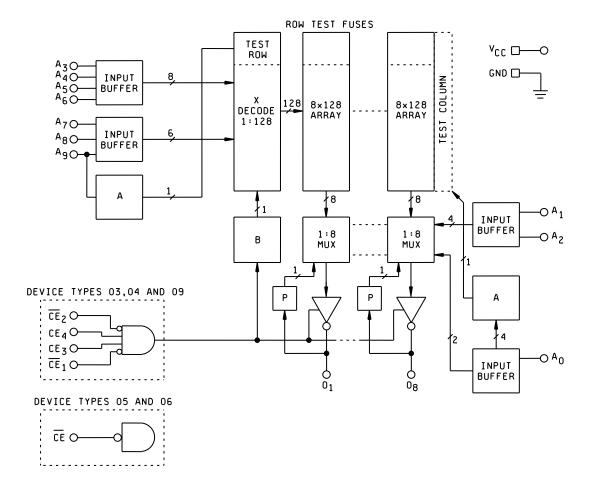

- 3.3.3 Functional block diagram. The functional block diagram shall be as specified on figure 4.

- 3.3.4 Case outlines. The case outlines shall be as specified in 1.2.3.

- 3.4 <u>Lead material and finish.</u> The lead material and finish shall be in accordance with MIL-PRF-38535 (see 6.6).

- 3.5 <u>Electrical performance characteristics</u>. The electrical performance characteristics are as specified in table I, and apply over the full recommended case operating temperature range, unless otherwise specified.

- 3.6 <u>Electrical test requirements.</u> The electrical test requirements shall be as specified in table II, and where applicable, the altered item drawing. The electrical tests for each subgroup are described in table III.

- 3.7 <u>Marking.</u> Marking shall be in accordance with MIL-PRF-38535. For programmed devices, the altered item drawing number shall be added to the marking by the programming activity.

- 3.8 <u>Processing options</u>. Since the PROM is an unprogrammed device capable of being programmed by either the manufacturer or the user to result in a wide variety of PROM configurations, two processing options are provided for selection in the contract, using an altered item drawing.

- 3.8.1 <u>Unprogrammed PROM delivered to the user</u>. All testing shall be verified through group A testing as defined in 3.3.2.1, table II, and table III. It is recommended that users perform subgroups 7 and 9 after programming to verify the specific program configuration.

- 3.8.2 <u>Manufacturer-programmed PROM delivered to the user</u>. All testing requirements and quality assurance provisions herein, including the requirements of the altered item drawing, shall be satisfied by the manufacturer prior to delivery.

- 3.9 <u>Microcircuit group assignment.</u> The devices covered by this specification shall be in microcircuit group number 14 (see Appendix A, MIL-PRF-38535.)

TABLE I. <u>Electrical performance characteristics</u>.

| Toot                                                        | Cymhal                               | Conditions 1/                                                                                                        | Device                           | Lin  | nits | Lloito |

|-------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------|------|------|--------|

| Test                                                        | Symbol                               | -55°C ≤ T <sub>C</sub> ≤ +125°C unless other wise specified                                                          | type                             | Min  | Max  | Units  |

| High-level output voltage                                   | VoH                                  | $V_{CC} = 4.5 \text{ V}, I_{OH} = -2 \text{ mA},$<br>$V_{IL} = 0.8 \text{ V}, V_{IH} = 2.0 \text{ V}$                | 02, 04, 05,<br>08, 09, 10        | 2.4  |      | V      |

| Low-level output voltage 2/                                 | V <sub>OL</sub>                      | V <sub>CC</sub> = 4.5 V, I <sub>OL</sub> = 12 mA,<br>V <sub>IL</sub> = 0.8 V, V <sub>IH</sub> = 2.0 V                | 01, 02,<br>08, 10                |      | 0.5  | V      |

|                                                             |                                      | V <sub>CC</sub> = 4.5 V, I <sub>OL</sub> = 8 mA                                                                      | 03, 04, 05,<br>06, 09            |      | 0.5  |        |

| Input clamp voltage                                         | VIC                                  | $V_{CC} = 4.5 \text{ V}, I_{IN} = -10 \text{ mA},$<br>$T_{C} = +25^{\circ}\text{C}$                                  | All                              |      | -1.5 | V      |

| Maximum collector cut-off current                           | ICEX                                 | V <sub>CC</sub> = 5.5 V, V <sub>O</sub> = 5.2 V                                                                      | 01, 03, 06                       |      | 100  | μΑ     |

| High impedance (off-state) output high current              | lohz                                 | V <sub>CC</sub> = 5.5 V, V <sub>O</sub> = 5.2 V                                                                      | 02, 04, 05,<br>08, 09, 10        |      | 100  | μΑ     |

| High impedance (off-state) output low current               | lolz                                 | V <sub>CC</sub> = 5.5 V, V <sub>O</sub> = 0.5 V                                                                      | 02, 04, 05,<br>08, 09, 10        |      | -100 | μΑ     |

| High level input current                                    | l <sub>IH1</sub>                     | V <sub>CC</sub> = 5.5 V, V <sub>IN</sub> = 5.5 V                                                                     | All                              |      | 50   | μΑ     |

|                                                             | I <sub>IH2</sub>                     | V <sub>CC</sub> = 5.5 V, V <sub>IN</sub> = 4.5 V , special programming pin                                           | 03, 04, 06,<br>09                |      | 100  |        |

| Low level input current                                     | I <sub>Ι</sub> Γ                     | V <sub>CC</sub> = 5.5 V, V <sub>IN</sub> = 0.5 V                                                                     | All                              | -1.0 | -250 | μΑ     |

| Short circuit output current                                | los                                  | $V_{CC} = 5.5 \text{ V}, V_{O} = 0.0 \text{ V},  \underline{3}/$<br>$V_{IH} = 2.0 \text{ V}, V_{IL} = 0.8 \text{ V}$ | 02, 04, 05,<br>08, 09, 10        | -15  | -100 | mA     |

| Supply current                                              | Icc                                  | V <sub>CC</sub> = 5.5 V, V <sub>IN</sub> = 0 V,<br>outputs = open                                                    | 01, 02                           |      | 170  | mA     |

|                                                             |                                      |                                                                                                                      | 03, 04, 05,<br>06, 08, 09,<br>10 |      | 185  |        |

| Propagation delay time, high to low level logic, address to | tPHL1                                | V <sub>CC</sub> = 4.5 V and 5.5 V,                                                                                   | 08                               |      | 90   | ns     |

| output                                                      | C <sub>L</sub> = 30 pF, see figure 6 |                                                                                                                      | 01, 02                           |      | 125  |        |

|                                                             |                                      |                                                                                                                      | 03, 04, 05,<br>06                |      | 90   |        |

|                                                             |                                      |                                                                                                                      | 09, 10                           |      | 55   |        |

TABLE I. <u>Electrical performance characteristics</u> – Continued.

| Test                                                              | Symbol            | Conditions $\underline{1}/$ -55°C $\leq$ T <sub>C</sub> $\leq$ +125°C unless other wise specified | Device<br>type    | Lin<br>Min | nits<br>Max | Units |

|-------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------|-------------------|------------|-------------|-------|

| Propagation delay time, low to                                    | tPLH1             | $V_{CC} = 4.5 \text{ V} \text{ and } 5.5 \text{ V},$                                              | 08                |            | 90          | ns    |

| high level logic, address to output                               |                   | C <sub>L</sub> = 30 pF, see figure 6                                                              | 01, 02            |            | 125         |       |

|                                                                   |                   |                                                                                                   | 03, 04, 05,<br>06 |            | 90          |       |

|                                                                   |                   |                                                                                                   | 09, 10            |            | 55          |       |

| Propagation delay time, high to low level logic, enable to output | t <sub>PHL2</sub> | V <sub>CC</sub> = 4.5 V and 5.5 V,<br>C <sub>L</sub> = 30 pF, see figure 6                        | 08                |            | 50          | ns    |

|                                                                   |                   |                                                                                                   | 01, 02            |            | 60          |       |

|                                                                   |                   |                                                                                                   | 03, 04, 05,<br>06 |            | 50          |       |

|                                                                   |                   |                                                                                                   | 09, 10            |            | 30          |       |

| Propagation delay time, low to high level logic, enable to output | t <sub>PLH2</sub> | V <sub>CC</sub> = 4.5 V and 5.5 V,<br>C <sub>L</sub> = 30 pF, see figure 6                        | 08                |            | 50          | ns    |

|                                                                   |                   |                                                                                                   | 01, 02            |            | 60          |       |

|                                                                   |                   |                                                                                                   | 03, 04, 05,<br>06 |            | 50          |       |

|                                                                   |                   |                                                                                                   | 09, 10            |            | 30          |       |

$<sup>\</sup>underline{1}/$  Complete terminal conditions shall be specified In table III.

<sup>2/</sup> I<sub>OL</sub> = 16 mA for circuits B, D, and F devices.

<sup>3/</sup> Not more than one output shall be grounded at one time. Output shall be at high logic level prior to test.

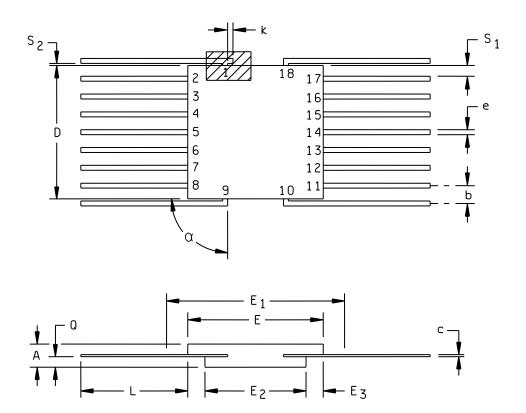

FIGURE 1. Case outline X.

| Symbol         | Inc  | hes  | Millim | neters | Notes |

|----------------|------|------|--------|--------|-------|

|                | Min  | Max  | Min    | Max    |       |

| Α              | .045 | .085 | 1.14   | 2.16   |       |

| b              | .015 | .020 | .38    | .51    | 5     |

| С              | .003 | .006 | .08    | .15    | 5     |

| D              | .340 | .380 | 8.64   | 9.65   |       |

| E              | .340 | .380 | 8.64   | 9.65   |       |

| E <sub>1</sub> |      | .400 |        | 10.16  | 3     |

| E <sub>2</sub> | .260 | .290 | 6.60   | 7.37   |       |

| E <sub>3</sub> | .025 |      | .63    |        |       |

| е              | .050 | BSC  | 1.27   | BSC    | 4, 6  |

| K              | .008 | .015 | .20    | .38    | 9     |

| L              | .250 | .330 | 6.35   | 8.38   |       |

| Q              | .010 | .040 | .25    | 1.02   | 2     |

| S <sub>1</sub> | .005 |      | .13    |        | 7, 8  |

| S <sub>2</sub> | .004 |      | .10    |        | 10    |

| α              | 30°  | 90°  | 30°    | 90°    |       |

## NOTES:

- 1. Index area; a tab (dim K) may be used to identify pin one. This tab may be located on either side as shown.

- 2. Dimension Q shall be measured at the point of exit of the lead from the body.

- 3. This dimension allows for off-center lid, meniscus and glass overrun.

- 4. The basic pin spacing is .050 (1.27 mm) between centerlines. Each pin centerline shall be located within ±.005 (0.13 mm) of its exact longitudinal position relative to pins relative to pins 1 and 18.

- 5. All leads increase limit by .003 (0.08 mm) measured at the center of the flat, when lead finish A is applied.

- 6. Sixteen spaces.

- 7. Applies to all four corners (leads number 2, 8, 11, and 17).

- Dimension S<sub>1</sub> may be .000 (0.00 mm) if leads are brazed to the metallized ceramic body (see MIL-STD-1835).

- Optional, see note 1. If a pin one identification mark is used in addition to this tab, the minimum limit of dimension K does not apply.

- 10. Applies to leads number 1, 9, 10, and 18.

FIGURE 1. Case outline X - Continued.

| Device types    | 01, 02, 08, and 10 | 03, 04, and 09  |

|-----------------|--------------------|-----------------|

| Case outlines   | V                  | J and K         |

| Terminal number | Termina            | l symbol        |

| 1               | A <sub>6</sub>     | A <sub>7</sub>  |

| 2               | A <sub>5</sub>     | A <sub>6</sub>  |

| 3               | A <sub>4</sub>     | A <sub>5</sub>  |

| 4               | A <sub>3</sub>     | A <sub>4</sub>  |

| 5               | A <sub>0</sub>     | A <sub>3</sub>  |

| 6               | A <sub>1</sub>     | A <sub>2</sub>  |

| 7               | A <sub>2</sub>     | A <sub>1</sub>  |

| 8               | A <sub>10</sub>    | A <sub>0</sub>  |

| 9               | GND                | O <sub>1</sub>  |

| 10              | CE <sub>1</sub>    | O <sub>2</sub>  |

| 11              | O <sub>4</sub>     | O <sub>3</sub>  |

| 12              | O <sub>3</sub>     | GND             |

| 13              | O <sub>2</sub>     | O <sub>4</sub>  |

| 14              | O <sub>1</sub>     | O <sub>5</sub>  |

| 15              | A9                 | O <sub>6</sub>  |

| 16              | A <sub>8</sub>     | O <sub>7</sub>  |

| 17              | A <sub>7</sub>     | O <sub>8</sub>  |

| 18              | V <sub>CC</sub>    | CE <sub>4</sub> |

| 19              |                    | CE <sub>3</sub> |

| 20              |                    | Œ <sub>2</sub>  |

| 21              |                    | CE <sub>1</sub> |

| 22              |                    | A <sub>9</sub>  |

| 23              |                    | A <sub>8</sub>  |

| 24              |                    | V <sub>CC</sub> |

FIGURE 2. Terminal connections.

| Device types    | 05 and 06      | 01, 02, and 08  | 02 and 10       |

|-----------------|----------------|-----------------|-----------------|

| Case outlines   | J and K        | Х               | Υ               |

| Terminal number |                | Terminal symbol |                 |

| 1               | A <sub>7</sub> | A <sub>6</sub>  | A <sub>6</sub>  |

| 2               | A <sub>6</sub> | A <sub>5</sub>  | A <sub>5</sub>  |

| 3               | A <sub>5</sub> | A <sub>4</sub>  | A <sub>4</sub>  |

| 4               | A <sub>4</sub> | A <sub>3</sub>  | A <sub>3</sub>  |

| 5               | A <sub>3</sub> | A <sub>0</sub>  | A <sub>0</sub>  |

| 6               | A <sub>2</sub> | A <sub>1</sub>  | A <sub>1</sub>  |

| 7               | A <sub>1</sub> | A <sub>2</sub>  | A <sub>2</sub>  |

| 8               | A <sub>0</sub> | A <sub>10</sub> | A <sub>10</sub> |

| 9               | O <sub>1</sub> | GND             | GND             |

| 10              | O <sub>2</sub> | CE <sub>1</sub> | CE <sub>1</sub> |

| 11              | O <sub>3</sub> | O <sub>4</sub>  | O <sub>4</sub>  |

| 12              | GND            | O <sub>3</sub>  | O <sub>3</sub>  |

| 13              | O <sub>4</sub> | O <sub>2</sub>  | O <sub>2</sub>  |

| 14              | O <sub>5</sub> | 01              | 01              |

| 15              | O <sub>6</sub> | A <sub>9</sub>  | A9              |

| 16              | 07             | A <sub>8</sub>  | A <sub>8</sub>  |

| 17              | O <sub>8</sub> | A <sub>7</sub>  | A <sub>7</sub>  |

| 18              | NC             | Vcc             | Vcc             |

| 19              | NC             |                 |                 |

| 20              | CE             |                 |                 |

| 21              | NC             |                 |                 |

| 22              | A <sub>9</sub> |                 |                 |

| 23              | A <sub>8</sub> |                 |                 |

| 24              | Vcc            |                 |                 |

FIGURE 2. <u>Terminal connections</u> – Continued.

Device types 01, 02, 08, and 10 ( see notes 1, 2, and 3 )

| Word   | Enable          |                 | Address |                |                |                |                |                |                |                |                |                |  |  |

|--------|-----------------|-----------------|---------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|--|

| number | CE <sub>1</sub> | A <sub>10</sub> | A9      | A <sub>8</sub> | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |  |  |

| NA     | L               | Х               | Х       | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              |  |  |

| NA     | Н               | Х               | Х       | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              |  |  |

| Word   |                | Data           |                |                |  |  |  |  |  |  |  |

|--------|----------------|----------------|----------------|----------------|--|--|--|--|--|--|--|

| number | O <sub>1</sub> | O <sub>2</sub> | O <sub>3</sub> | O <sub>4</sub> |  |  |  |  |  |  |  |

| NA     |                | See no         | te 5           |                |  |  |  |  |  |  |  |

| NA     | ОС             | ОС             | ОС             | ОС             |  |  |  |  |  |  |  |

Device types 05 and 06 (see notes 1, 2, and 3)

| Word   | Enable          |                | Address        |                |                |                |                |                |                |                |                |  |  |

|--------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|--|

| number | CE <sub>1</sub> | A <sub>9</sub> | A <sub>8</sub> | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |  |  |

| NA     | L               | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              |  |  |

| NA     | Н               | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              |  |  |

|   | Word   |                | Data       |    |    |                |    |    |    |  |  |  |  |  |  |

|---|--------|----------------|------------|----|----|----------------|----|----|----|--|--|--|--|--|--|

|   | number | O <sub>1</sub> | 02         | 03 | 04 | O <sub>5</sub> | 06 | 07 | 08 |  |  |  |  |  |  |

| Ī | NA     |                | See note 5 |    |    |                |    |    |    |  |  |  |  |  |  |

|   | NA     | ОС             | ОС         | ОС | ОС | ОС             | ОС | ОС | ОС |  |  |  |  |  |  |

FIGURE 3. Truth tables (unprogrammed).

Device types 03, 04, and 09 (see notes 1, 2, 3, and 4)

| Word   |                 | Ena             | ble             |                 |                | Address        |                |                |                |                |                |                |                |                |

|--------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| number | CE <sub>1</sub> | CE <sub>2</sub> | CE <sub>3</sub> | CE <sub>4</sub> | A <sub>9</sub> | A <sub>8</sub> | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |

| NA     | L               | L               | Н               | Н               | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              |

| NA     | L               | Н               | Н               | Н               | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              |

| NA     | Н               | L               | Н               | Н               | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              |

| NA     | Н               | Н               | L               | Н               | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              |

| NA     | Н               | Н               | L               | L               | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              |

| Word   | Data           |    |    |                |                |    |    |    |  |  |  |  |  |

|--------|----------------|----|----|----------------|----------------|----|----|----|--|--|--|--|--|

| number | O <sub>1</sub> | 02 | Ο3 | O <sub>4</sub> | O <sub>5</sub> | 06 | 07 | Ο8 |  |  |  |  |  |

| NA     |                |    |    |                |                |    |    |    |  |  |  |  |  |

| NA     | ОС             | ОС | ОС | ОС             | ОС             | ОС | ОС | ОС |  |  |  |  |  |

| NA     | ОС             | ОС | ОС | ОС             | ОС             | ОС | ОС | ОС |  |  |  |  |  |

| NA     | ОС             | ОС | ОС | ОС             | ОС             | ОС | ОС | ОС |  |  |  |  |  |

| NA     | ОС             | ОС | ОС | ОС             | ОС             | ОС | ОС | ОС |  |  |  |  |  |

- 1. NA = Not applicable.

- 2. X = Input may be high level, low level or open circuit.

- 3. OC = Open circuit (high resistance output).

- 4. Program readout can only be accomplished with both enable inputs at low level.

- 5. The outputs for an unprogrammed device shall be high for circuits A, B (device types 03 and 04), and F; and shall be low for circuits B (device types 01, 02, and 08), C, D, E, G and H.

FIGURE 3. <u>Truth tables (unprogrammed)</u> – Continued.

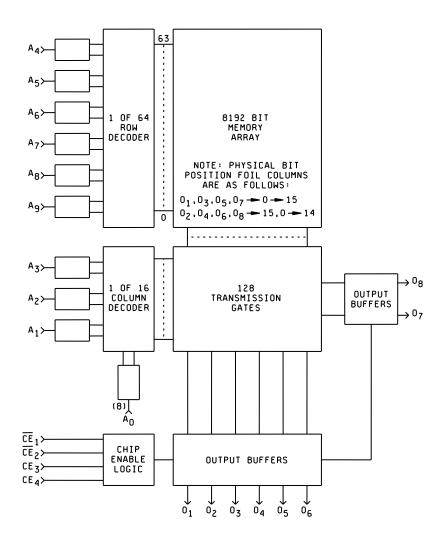

Device types 01, 02, and 08 (Circuit B)

Device types 01 and 02 (Circuit A)

Device type 02 (Circuit F)

Device types 03 and 04 (Circuit E)

FIGURE 4. Functional block diagrams.

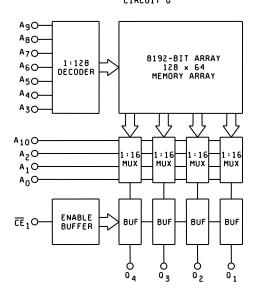

# Device types 01, 02, and 10 Circuit C

FIGURE 4. Functional block diagrams - Continued.

# Device type 02 Circuit H

FIGURE 4. Functional block diagrams - Continued.

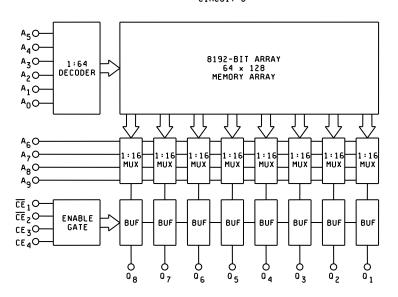

# Device types 03 and 04 Circuit A

FIGURE 4. <u>Functional block diagrams</u> – Continued.

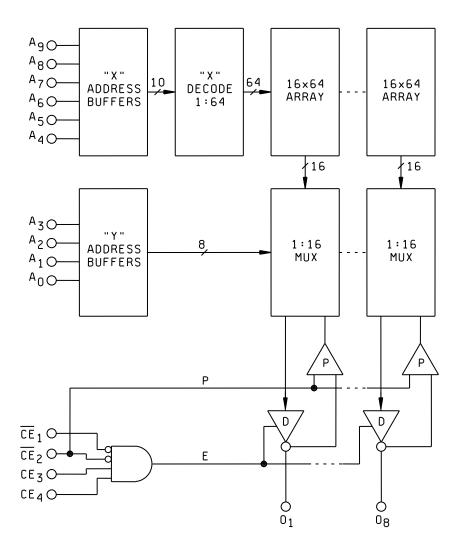

# DEVICE TYPES 01 AND 02

#### DEVICE TYPES 03 AND 04 CIRCUIT G

FIGURE 4. Functional block diagrams - Continued.

# Device type 04 Circuit F

FIGURE 4. Functional block diagrams - Continued.

## Device types 03, 04, 05, and 09 Circuit C

## Device types 04 Circuit H

FIGURE 4. Functional block diagrams - Continued.

## Device types 03, 04, 05, 06, and 09 Circuits B and D

FIGURE 4. Functional block diagrams - Continued.

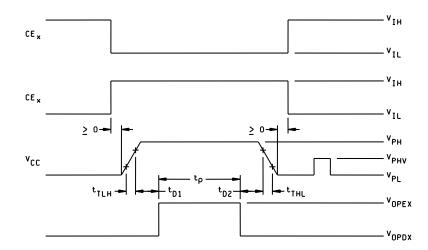

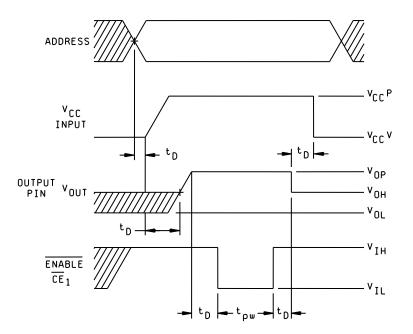

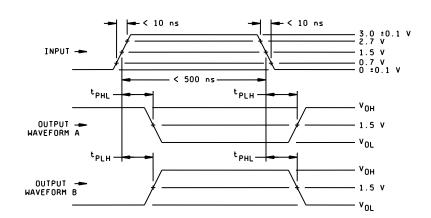

NOTE: All other waveform characteristics shall be as specified in table IVA.

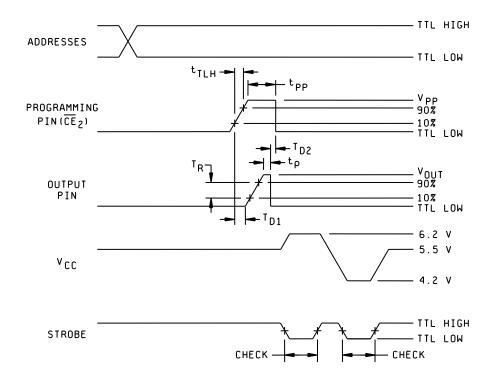

FIGURE 5A. Programming voltage waveforms during programming for circuit A.

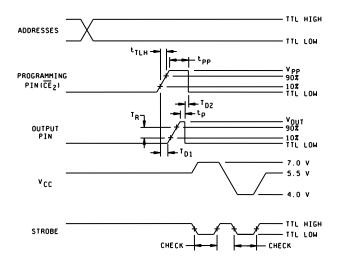

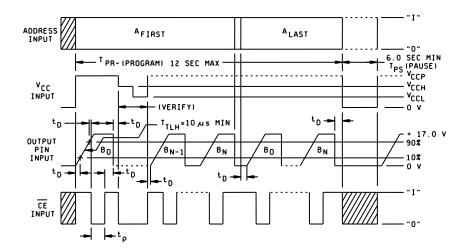

## NOTES:

- 1. Output load is 0.2 mA and 12 mA during 7.0 V and 4.0 V check, respectively.

- 2. All other waveform characteristics shall be as specified in table IVB.

(Device types 03 and 04)

FIGURE 5B. Programming voltage waveforms during programming for circuit B.

## PROGRAMMING WAVEFORMS

(Device types 01, 02, and 08)

FIGURE 5B. <u>Programming voltage waveforms during programming for circuit B</u> – Continued.

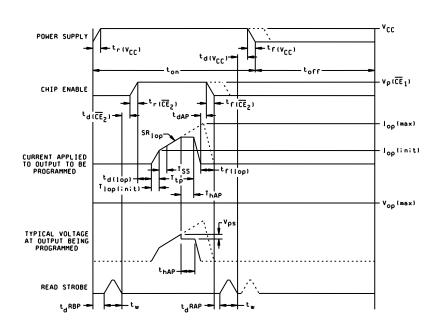

NOTE: All other waveform characteristics shall be as specified in table IVC.

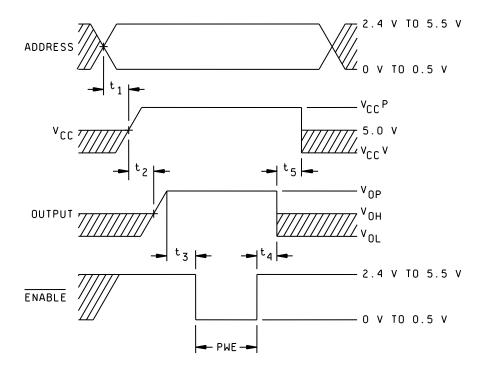

FIGURE 5C. Programming voltage waveforms during programming for circuit C and H.

NOTE: All other waveform characteristics shall be as specified in table IVD.

FIGURE 5D. Programming voltage waveforms during programming for circuit D.

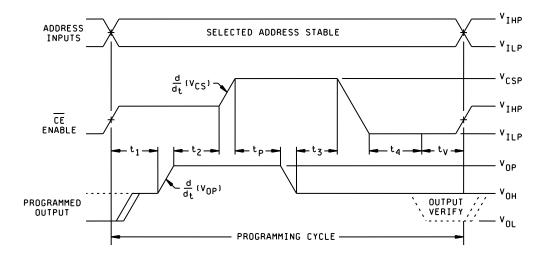

- 1. All delays between edges are specified from completion of the first edge, not midpoints.

- 2. Delays  $t_1$ ,  $t_2$ ,  $t_3$ , and  $t_4$  must be greater than 100 ns; maximum delays of 1  $\mu$ s are recommended to minimize heating during programming.

- 3. During ty the output being programmed is switched to the load R and verified.

- Outputs not being programmed are connected to V<sub>ONP</sub> through a resistor which provides output current limiting.

- 5. All other waveform characteristics shall be as specified in table IVE.

FIGURE 5E. Programming voltage waveforms during programming for circuit E.

- 1. Output load is 0.2 mA and 12 mA during 6.2 V and 4.2 V check, respectively.

- 2. All other waveform characteristics shall be as specified in table IVF.

FIGURE 5F. Programming voltage waveforms during programming for circuit F.

FIGURE 5G. Programming voltage waveforms during programming for circuit G.

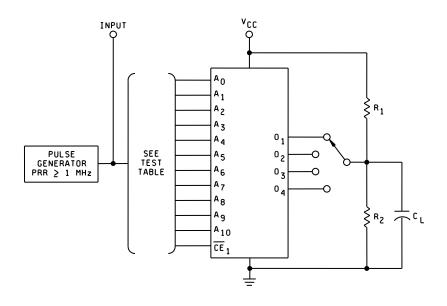

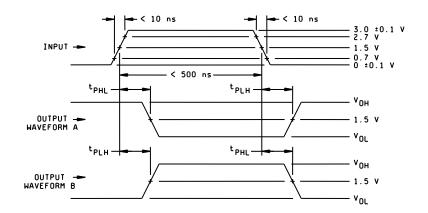

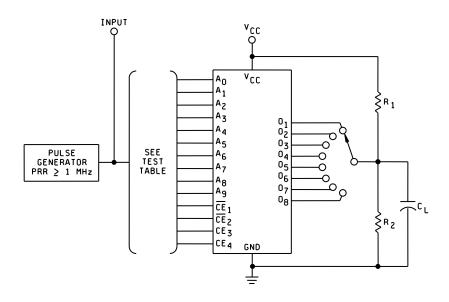

## Device types 01, 02, 08, and 10

- 1. Test table for devices programmed in accordance with an altered item drawing may be replaced by the equivalent tests which apply to the specific program configuration for the resulting read-only memory.

- 2.  $C_L$  = 30 pF minimum, including jig and probe capacitance;  $R_1$  = 330  $\Omega$  ±25% and  $R_2$  = 680  $\Omega$  ±20 %.

- 3. Outputs may be under load simultaneously.

FIGURE 6. Switching time test circuit.

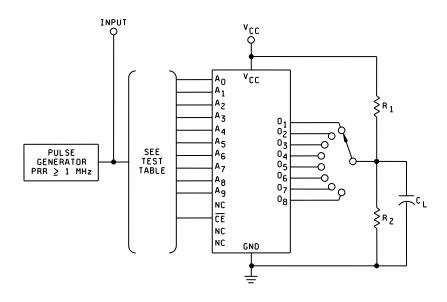

## Device types 03, 04, and 09

- 1. Test table for devices programmed in accordance with an altered item drawing may be replaced by the equivalent tests which apply to the specific program configuration for the resulting read-only memory.

- 2.  $C_L$  = 30 pF minimum, including jig and probe capacitance;  $R_1$  = 330  $\Omega$  ±25% and  $R_2$  = 680  $\Omega$  ±20 %.

- 3. Outputs may be under load simultaneously.

FIGURE 6. Switching time test circuit - Continued.

## Device types 05 and 06

- Test table for devices programmed in accordance with an altered item drawing may be replaced by the equivalent tests which apply to the specific program configuration for the resulting read-only memory.

- 2.  $C_L$  = 30 pF minimum, including jig and probe capacitance;  $R_1$  = 330  $\Omega$  ±25% and  $R_2$  = 680  $\Omega$  ±20 %.

- 3. Outputs may be under load simultaneously.

FIGURE 6. Switching time test circuit - Continued.

#### 4. VERIFICATION

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with MIL-PRF-38535 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not effect the form, fit, or function as described herein.

- 4.2 <u>Screening.</u> Screening shall be in accordance with MIL-PRF-38535 and shall be conducted on all devices prior to qualification and quality conformance inspection. The following additional criteria shall apply:

- a. The burn-in test duration, test condition, and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The burn-in test circuit shall be maintained under document control by the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015 of MIL-STD-883

- b. Interim and final electrical test parameters shall be as specified in table II, except interim electrical parameters test prior to burn-in is optional at the discretion of the manufacturer.

- c. Additional screening for space level product shall be as specified in MIL-PRF-38535, appendix B.

- d. Class B devices processed to an altered item drawing may be programmed either before or after burn-in at the manufacturer's discretion. The required electrical testing shall include, as a minimum, the final electrical tests for programmed devices as specified in table II herein. Class S devices processed by the manufacturer to an altered item drawing shall be programmed prior to burn-in.

- 4.3 <u>Qualification inspection.</u> Qualification inspection shall be in accordance with MIL-PRF-38535. Qualification data for subgroups 7 through 11 shall be by attributes only.

- 4.3.1 <u>Qualification extension</u>. When authorized by the qualifying activity, for qualification inspection, if a manufacturer qualifies faster device type which is manufactured identically (for example, same die, process, and package) to other device types on this specification, then the other device types may be qualified by conducting only group A electrical tests and any electrical specified as additional group C subgroups and submitting data in accordance with MIL-PRF-38535 (for example, groups B, C, and D tests are not required).

- 4.4 <u>Technology Conformance inspection (TCI)</u>. Technology conformance inspection shall be in accordance with MIL-PRF-38535 and as specified herein for groups A, B, C, and D inspections (see 4.4.1 through 4.4.4).

- 4.4.1 <u>Group A inspection.</u> Group A inspection shall be in accordance with table III of MIL-PRF-38535 and as follows:

- a. Electrical test requirements shall be as specified in table II herein.

- b. Subgroups 4, 5, and 6 shall be omitted.

- c. For unprogrammed devices, a sample shall be selected to satisfy programmability requirements prior to performing subgroups 9, 10, and 11. Twelve devices shall be submitted to programming (see 3.3.2.1). If more than 2 devices fail to program, the lot shall be rejected, At the manufacturer's option, the sample may be increased to 24 total devices with no more than 4 total device failures allowed.

- d. For unprogrammed devices, 10 devices from the programmability sample shall be subjected to the requirements of group A, subgroups 9, 10, and 11. If more than two total devices fail in all three subgroups, the lot shall be rejected. At the manufacturer's option, the sample may be increased to 20 total devices with no more that 4 total device failures allowable.

TABLE II. Electrical test requirements.

| MIL-PRF-38535                                                                            | '.                           | (see table III)<br><u>2</u> /, <u>3</u> / |

|------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------|

| test requirements                                                                        | Class S<br>devices           | Class B<br>devices                        |

| Interim electrical parameters                                                            | 1                            | 1                                         |

| Final electrical test parameters for unprogrammed devices                                | 1*, 2, 3, 7*,<br>8           | 1*, 2, 3,<br>7*, 8                        |

| Final electrical test parameters for programmed devices                                  | 1*, 2, 3, 7*<br>8, 9, 10, 11 | 1*, 2, 3, 7*,<br>8, 9,                    |

| Group A test requirements                                                                | 1, 2, 3, 7, 8,<br>9, 10, 11  | 1, 2, 3, 7, 8,<br>9, 10, 11               |

| Group B end-point electrical parameters subgroup 5 when using the method 5005 QCI option | 1, 2, 3, 7, 8,<br>9, 10, 11  | N/A                                       |

| Group C end-point electrical parameters                                                  | 1, 2, 3, 7, 8,<br>9, 10, 11  | 1, 2, 3, 7, 8                             |

| Group D test requirements                                                                | 1, 2, 3, 7, 8                | 1, 2, 3, 7, 8                             |

- 1/ \* indicates PDA applies to subgroups 1 and 7.

- 2/ Any or all subgroups may be combined when using high-speed testers.

- 3/ Subgroups 7 and 8 shall consist of verifying the pattern specified.

- 4.4.2 Group B inspection. Group B inspection shall be in accordance with table II MIL-PRF-38535.

- 4.4.3 <u>Group C inspection.</u> Group C inspection shall be in accordance with table IV of MIL-PRF-38535 and as follows:

- a. End-point electrical parameters shall be as specified in table II herein.

- b. The steady-state life test duration, test condition, and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The burnin test circuit shall be maintained under document control by the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005 of MIL-STD-883.

- c. For qualification inspection, at least 50 percent of the sample selected for testing in subgroup 1 shall be programmed (see 3.3.2). For quality conformance inspection, the programmability sample (see 4.4.1c) shall be included in the life tests.

- 4.4.4 <u>Group D inspection.</u> Group D inspection shall be in accordance with table V of MIL-PRF-38535. Endpoint electrical parameters shall be as specified in table II herein.

- 4.5 Methods of inspection. Methods of inspection shall be specified and as follows:

- 4.5.1 <u>Voltage and current.</u> All voltages given are referenced to the microcircuit ground terminal. Currents given are conventional and positive when flowing into the referenced terminal.

# TABLE III. Group A inspection for device type 01.

Terminal conditions (outputs not designated are open or resistive coupled to GND or voltage; inputs not designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  2.0 V, low  $\leq$  2.0 V, low  $\leq$  2.0 V, low  $\leq$  2.0 V, l

| Subgroup                       | Symbol          | MIL-<br>STD-  | Cases<br>V,X                                                         | 1              | 2              | 3              | 4              | 5              | 6              | 7              | 8               | 9                                                                          | 10                 | 11         | 12             | 13         | 14             | 15              | 16             | 17             | 18              |

|--------------------------------|-----------------|---------------|----------------------------------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|----------------------------------------------------------------------------|--------------------|------------|----------------|------------|----------------|-----------------|----------------|----------------|-----------------|

| Gubg. Gup                      | Cy              | 883<br>method | Test no.                                                             | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | A <sub>10</sub> | GND                                                                        | CE 1               | 04         | O <sub>3</sub> | 02         | O <sub>1</sub> | A <sub>9</sub>  | A <sub>8</sub> | A <sub>7</sub> | V <sub>CC</sub> |

| 1<br>T <sub>C</sub> =<br>+25°C | Vic             |               | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11                | -10mA           | GND                                                                        | -10mA              |            |                |            |                | -10mA           | -10mA          | -10mA          | 4.5V            |

|                                | V <sub>OL</sub> | 3007          | 13<br>14<br>15<br>16                                                 | 1/2/           | 1/             | 1/             | 1/             | 1/             | 1/             | 1/             | 1/              | u<br>u                                                                     | 0.5V<br>"          | <u>3</u> / | <u>3</u> /     | <u>3</u> / | 3/             | <u>1</u> /<br>" | 1/             | 1/             | ec<br>ec        |

|                                | I <sub>IL</sub> | 3009          | 17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28 | 0.5V            | 44<br>44<br>44<br>44<br>44<br>44<br>44<br>44<br>44<br>44<br>44<br>44<br>44 | 0.5V               |            |                |            |                | 0.5V            | 0.5V           | 0.5V           | 5.5V            |

|                                | Ιιн             | 3010          | 29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40 | 5.5V            |                                                                            | 5.5V               |            |                |            |                | 5.5V            | 5.5V           | 5.5V           |                 |

|                                | ICEX            | 3005          | 41<br>42<br>43<br>44<br>45                                           | GND             | «<br>«                                                                     | "<br>"<br>"<br>GND | 5.2V       | 5.2V           | 5.2V       | 5.2V           | GND             | GND            | GND            | и<br>и          |

| 2                              | Icc             |               |                                                                      | l              |                | l              | l              |                | l .            |                |                 | -1441                                                                      | GIND               |            |                |            |                | GIND            | GND            | GND            | <u> </u>        |

| 3                              |                 |               | nal conditi<br>nal conditi                                           |                |                |                |                |                |                |                |                 |                                                                            |                    |            |                |            |                |                 |                |                |                 |

| 7<br>T <sub>C</sub> =          | Func-<br>tional | 4/            | 46                                                                   | 4/             | 4/             | 4/             | 4/             | 4/             | 4/             | 4/             | 4/              | GND                                                                        | <u>4</u> /         | <u>4</u> / | <u>4</u> /     | <u>4</u> / | <u>4</u> /     | <u>4</u> /      | <u>4</u> /     | <u>4</u> /     | <u>4</u> /      |

TABLE III. Group A inspection for device type 01 – Continued.

Terminal conditions (outputs not designated are open or resistive coupled to GND or voltage; inputs not designated are high  $\geq$  2.0 V, low  $\leq$  0.8

|                           | MIL- Cases        |                            |              |                |                |                |                |                        |                |                |                 |     |            |                |                |                |            |            |                |                |                  |

|---------------------------|-------------------|----------------------------|--------------|----------------|----------------|----------------|----------------|------------------------|----------------|----------------|-----------------|-----|------------|----------------|----------------|----------------|------------|------------|----------------|----------------|------------------|

| Subgroup                  | Symbol            | STD-                       | Cases<br>V,X | 1              | 2              | 3              | 4              | 5                      | 6              | 7              | 8               | 9   | 10         | 11             | 12             | 13             | 14         | 15         | 16             | 17             | 18               |

| Subgroup                  | Symbol            | 883<br>method              | Test no.     | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>0</sub>         | A <sub>1</sub> | A <sub>2</sub> | A <sub>10</sub> | GND | CE 1       | O <sub>4</sub> | O <sub>3</sub> | O <sub>2</sub> | 01         | A9         | A <sub>8</sub> | A <sub>7</sub> | Vcc              |

| 8                         | Same te           | sts, termin                | al condition | ns, and I      | imits as f     | or subgro      | up 7, exc      | ept T <sub>C</sub> = - | +125°C a       | nd -55°C.      |                 |     |            |                |                |                |            |            |                |                | , and the second |

| 9                         | t <sub>PHL1</sub> | GALPAT                     | 47           | <u>5</u> /             | <u>5</u> /     | <u>5</u> /     | <u>5</u> /      | GND | GND        | <u>6</u> /     | <u>6</u> /     | <u>6</u> /     | <u>6</u> / | <u>5</u> / | <u>5</u> /     | <u>5</u> /     | <u>5</u> /       |

| T <sub>C</sub> =<br>+25°C | t <sub>PLH1</sub> | Fig. 6<br>GALPAT<br>Fig. 6 | 48           | <u>5</u> /             | <u>5</u> /     | <u>5</u> /     | <u>5</u> /      | и   | GND        | ш              | и              | u              | и          | <u>5</u> / | <u>5</u> /     | <u>5</u> /     | <u>5</u> /       |

|                           | t <sub>PHL2</sub> | Sequen-<br>tial<br>Fig. 6  | 49           | <u>7</u> /             | <u>7</u> /     | <u>7</u> /     | <u>7</u> /      | и   | <u>7</u> / | ш              | ш              | ш              | и          | <u>7</u> / | <u>7</u> /     | <u>7</u> /     | <u>7</u> /       |

|                           | t <sub>PLH2</sub> | Sequen-<br>tial<br>Fig. 6  | 50           | <u>Z</u> /     | <u>7</u> /     | <u>Z</u> /     | <u>7</u> /     | <u>7</u> /             | <u>7</u> /     | <u>7</u> /     | <u>7</u> /      | и   | <u>7</u> / | и              | и              | и              | ш          | <u>7</u> / | <u>7</u> /     | <u>7</u> /     | <u>Z</u> /       |

| 10                        | Same te           | sts, termin                | al condition | ns, and I      | imits as f     | or subgro      | up 9, exc      | ept T <sub>C</sub> = - | +125°C.        |                |                 |     |            |                | •              |                | •          |            |                | •              |                  |

| 11                        | Same te           | sts, termin                | al condition | ns, and I      | imits as f     | or subgro      | up 9, exc      | ept T <sub>C</sub> = - | -55°C.         |                |                 |     |            |                |                |                |            |            |                |                |                  |

TABLE III. Group A inspection for device types 02, 08, and 10.

Terminal conditions (outputs not designated are open or resistive coupled to GND or voltage; inputs not designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\geq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  2.0 V, low  $\leq$  0.8 designated are high  $\leq$  0.8 designated are

| Subgroup           | Symbol                 | MIL-<br>STD-  | Cases<br>V,X,Y                                                       | 1                      | 2              | 3                           | 4                | 5                 | 6              | 7              | 8               | 9                                                              | 10              | 11             | 12             | 13             | 14         | 15                         | 16                          | 17              | 18       |

|--------------------|------------------------|---------------|----------------------------------------------------------------------|------------------------|----------------|-----------------------------|------------------|-------------------|----------------|----------------|-----------------|----------------------------------------------------------------|-----------------|----------------|----------------|----------------|------------|----------------------------|-----------------------------|-----------------|----------|

|                    |                        | 883<br>method | Test no.                                                             | A <sub>6</sub>         | A <sub>5</sub> | A <sub>4</sub>              | А3               | A <sub>0</sub>    | A <sub>1</sub> | A <sub>2</sub> | A <sub>10</sub> | GND                                                            | CE <sub>1</sub> | O <sub>4</sub> | O <sub>3</sub> | O <sub>2</sub> | 01         | A9                         | A <sub>8</sub>              | A <sub>7</sub>  | Vcc      |

| 1<br>Tc =<br>+25°C | Vic                    |               | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12          | -10mA                  | -10mA          | -10mA                       | -10mA            | -10mA             | -10mA          | -10mA          | -10mA           | GND<br>« « « « « « « « « « « « « « « « « « «                   | -10mA           |                |                |                |            | -10mA                      | -10mA                       | -10mA           | 4.5V     |

|                    | V <sub>OL</sub>        | 3007          | 13<br>14<br>15<br>16                                                 | <u>1/2/</u><br>"       | 1/"            | <u>1</u> /<br>"             | 1/"              | <u>1/ 9/</u><br>" | 1/             | 1/"            | <u>1</u> /<br>" | и<br>и                                                         | 0.5V<br>"       | <u>3</u> /     | <u>3</u> /     | <u>3</u> /     | <u>3</u> / | <u>1</u> /<br>"            | <u>1</u> /<br>"             | <u>1</u> /<br>" | a        |

|                    | V <sub>OH</sub>        | 3006          | 17<br>18<br>19<br>20                                                 | 1/ 10/ 11/<br>"<br>12/ | 1/ 9/ 10/<br>" | <u>1</u> / <u>12</u> /<br>" | <u>21</u> /<br>" | 1/13/             | u<br>u         | "              | 1/ 10/ 12/      | "                                                              | u<br>u          | -2mA           | -2mA           | -2mA           | -2mA       | <u>1</u> / <u>9</u> /<br>" | <u>1</u> / <u>13</u> /<br>" | u<br>u          | er<br>er |

|                    | I∟                     | 3009          | 21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32 | 0.5V                   | 0.5V           | 0.5V                        | 0.5V             | 0.5V              | 0.5V           | 0.5V           | 0.5V            |                                                                | 0.5V            |                |                |                |            | 0.5V                       | 0.5V                        | 0.5V            | 5.5V     |

|                    | ΊΗ                     | 3010          | 33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43       | 5.5V                   | 5.5V           | 5.5V                        | 5.5V             | 5.5V              | 5.5V           | 5.5V           | 5.5V            | 62<br>62<br>62<br>62<br>62<br>62<br>63<br>64<br>64<br>64<br>64 | 5.5V            |                |                |                |            | 5.5V                       | 5.5V                        | 5.5V            | 5.5V     |

|                    | I <sub>OHZ</sub>       |               | 45<br>46<br>47<br>48                                                 |                        |                |                             |                  |                   |                |                |                 | u<br>u                                                         | <u>14/</u><br>" | 5.2V           | 5.2V           | 5.2V           | 5.2V       |                            |                             |                 | a        |

|                    | loLZ                   |               | 49<br>50<br>51<br>52                                                 |                        |                |                             |                  |                   |                |                |                 | "                                                              | u<br>u          | 0.5V           | 0.5V           | 0.5V           | 0.5V       |                            |                             |                 | u        |

|                    | I <sub>CC</sub><br>15/ | 3005          | 53                                                                   | GND                    | GND            | GND                         | GND              | GND               | GND            | GND            | GND             | ш                                                              | GND             |                |                |                |            | GND                        | GND                         | GND             | и        |

TABLE III. Group A inspection for device types 02, 08, and 10 – Continued.

Terminal conditions (outputs not designated are open or resistive coupled to GND or voltage; inputs not designated are high  $\geq$  2.0 V, low  $\leq$  0.8

| Subgroup                       | Symbol                                                                                                                              | MIL-<br>STD-                               | Cases<br>V,X,Y       | 1                         | 2                               | 3                        | 4                           | 5                           | 6                        | 7                        | 8                                  | 9        | 10                | 11             | 12             | 13             | 14             | 15                       | 16                          | 17                       | 18                       |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------|---------------------------|---------------------------------|--------------------------|-----------------------------|-----------------------------|--------------------------|--------------------------|------------------------------------|----------|-------------------|----------------|----------------|----------------|----------------|--------------------------|-----------------------------|--------------------------|--------------------------|

| Gubgroup                       | Cymbol                                                                                                                              | 883<br>method                              | Test no.             | A <sub>6</sub>            | A <sub>5</sub>                  | A <sub>4</sub>           | A <sub>3</sub>              | A <sub>0</sub>              | A <sub>1</sub>           | A <sub>2</sub>           | A <sub>10</sub>                    | GND      | CE <sub>1</sub>   | O <sub>4</sub> | O <sub>3</sub> | O <sub>2</sub> | O <sub>1</sub> | A <sub>9</sub>           | A <sub>8</sub>              | A <sub>7</sub>           | Vcc                      |

| 1<br>T <sub>C</sub> =<br>+25°C | los                                                                                                                                 | 3011                                       | 54<br>55<br>56<br>57 | 1/ 10/<br>11/<br>"<br>12/ | <u>1/ 9/</u><br><u>10/</u><br>" | <u>1</u> /<br>"<br>12/   | <u>1</u> / <u>21</u> /<br>" | <u>1</u> / <u>13</u> /<br>" | <u>1</u> /<br>"          | <u>1</u> /<br>"          | 1/ <u>10</u> /<br>"<br><u>12</u> / | GND<br>" | 0.5V<br>"         | GND            | GND            | GND            | GND            | <u>1/9</u> /<br>"        | <u>1</u> / <u>13</u> /<br>" | <u>1</u> /<br>"          | 5.5V<br>"                |

| 2                              | Same te                                                                                                                             | sts, termin                                | al condition         | ons, and I                | imits as fo                     | or subgro                | up 1, exc                   | ept T <sub>C</sub> = +      | ⊦125°C aı                | nd V <sub>IC</sub> tes   | ts are om                          | itted.   |                   |                |                |                |                |                          |                             |                          |                          |

| 3                              | Same tests, terminal conditions, and limits as for subgroup 1, except T <sub>C</sub> = -55°C and V <sub>IC</sub> tests are omitted. |                                            |                      |                           |                                 |                          |                             |                             |                          |                          |                                    |          |                   |                |                |                |                |                          |                             |                          |                          |

| 7<br>T <sub>C</sub> =<br>+25°C | Func-<br>tional<br>tests                                                                                                            | <u>4</u> /                                 | 58                   | <u>4</u> /                | <u>4</u> /                      | <u>4</u> /               | <u>4</u> /                  | <u>4</u> /                  | <u>4</u> /               | <u>4</u> /               | <u>4</u> /                         | GND      | <u>4</u> /        | <u>4</u> /     | <u>4</u> /     | <u>4</u> /     | <u>4</u> /     | <u>4</u> /               | <u>4</u> /                  | <u>4</u> /               | <u>4</u> /               |

| 8                              | Same te                                                                                                                             | sts, termin                                | al condition         | ons, and I                | imits as fo                     | or subgro                | up 7, exc                   | ept TC = -                  | +125°C a                 | ind TC =                 | -55°C.                             |          |                   |                |                |                |                |                          |                             |                          |                          |

| 9                              | t <sub>PHL1</sub>                                                                                                                   | GALPAT                                     | 59                   | <u>5</u> /                | <u>5</u> /                      | <u>5</u> /               | <u>5</u> /                  | <u>5</u> /                  | <u>5</u> /               | <u>5</u> /               | <u>5</u> /                         | GND      | GND               | <u>6</u> /     | <u>6</u> /     | <u>6</u> /     | <u>6</u> /     | <u>5</u> /               | <u>5</u> /                  | <u>5</u> /               | <u>5</u> /               |

|                                |                                                                                                                                     | Eig 6                                      | 00                   | _                         |                                 |                          |                             |                             |                          |                          |                                    |          |                   |                |                |                |                | _                        | _                           |                          | _                        |

| T <sub>C</sub> =<br>+25°C      | t <sub>PLH1</sub>                                                                                                                   | Fig. 6<br>GALPAT                           | 60                   | <u>5</u> /                | <u>5</u> /                      | <u>5</u> /               | <u>5</u> /                  | <u>5</u> /                  | <u>5</u> /               | <u>5</u> /               | <u>5</u> /                         | u        | GND               | ш              | и              | и              | и              | <u>5</u> /               | <u>5</u> /                  | <u>5</u> /               | <u>5</u> /               |

|                                | t <sub>PLH1</sub>                                                                                                                   | GALPAT<br>Fig. 6<br>Sequen-<br>tial        |                      | <u>5</u> /<br><u>7</u> /  | <u>5</u> /<br><u>7</u> /        | <u>5</u> /<br><u>7</u> / | <u>5</u> /<br><u>7</u> /    | <u>5</u> /<br><u>7</u> /    | <u>5</u> /<br><u>7</u> / | <u>5</u> /<br><u>7</u> / | <u>5</u> /<br><u>7</u> /           | ш        | GND<br><u>7</u> / | ш              | ш              | ш              | ii<br>ii       |                          |                             | <u>5</u> /<br><u>7</u> / | _                        |

|                                |                                                                                                                                     | GALPAT<br>Fig. 6<br>Sequen-                | 60                   |                           |                                 | _                        |                             | _                           | _                        |                          | _                                  |          | -                 |                | =              | u              | u              | <u>5</u> /               | <u>5</u> /                  |                          | <u>5</u> /               |

| +25°C                          | t <sub>PHL2</sub>                                                                                                                   | GALPAT Fig. 6 Sequential Fig. 6 Sequential | 60<br>61<br>62       | <u>Z</u> /                | <u>Z</u> /                      | <u>Z</u> /               | <u>Z</u> /                  | <u>Z</u> /                  | <u>Z</u> /               | <u>Z</u> /               | <u>7</u> /                         | u        | <u>7</u> /        | ш              | u              | ee             | а              | <u>5</u> /<br><u>7</u> / | <u>5</u> /<br><u>7</u> /    | <u>7</u> /               | <u>5</u> /<br><u>7</u> / |

## TABLE III. Group A inspection for device type 03.

Terminal conditions (outputs not designated are open or resistive coupled to GND or voltage; inputs not designated are high  $\geq$  2.0 V, low  $\leq$  0.8

|                                |                                 | MIL-<br>STD-  | Cases<br>J,K                                                                     | 1                | 2                 | 3              | 4              | 5                      | 6              | 7              | 8              | 9    | 10   | 11             | 12                                         | 13   | 14             | 15             | 16  | 17             | 18              | 19              | 20        | 21        | 22             | 23                | П |

|--------------------------------|---------------------------------|---------------|----------------------------------------------------------------------------------|------------------|-------------------|----------------|----------------|------------------------|----------------|----------------|----------------|------|------|----------------|--------------------------------------------|------|----------------|----------------|-----|----------------|-----------------|-----------------|-----------|-----------|----------------|-------------------|---|