# INCH POUND

MIL-M-38510/502A <u>21 November 2005</u> SUPERSEDING MIL-M-38510/502 (USAF) 16 June 1981

#### MILITARY SPECIFICATION

#### MICROCIRCUITS, DIGITAL, BIPOLAR FIELD PROGRAMMABLE LOGIC ARRAY (FPLA) 16 x 48 x 8, MONOLITHIC SILICON

#### Inactive for new design after 28 July 1995.

This specification is approved for use by all Departments and Agencies of the Department of Defense.

The requirements for acquiring the product herein shall consist of this specification sheet and MIL-PRF 38535.

1. SCOPE

1.1 <u>Scope.</u> This specification covers the detail requirements for monolithic silicon, bipolar, field programmable logic array (FPLA) microcircuits which employ thin film nichrome resistors (NICr) as the fusible link or programming element. Three product assurance classes and a choice of case outline / lead material and finish are provided for each type and are reflected in the complete part number. For this product, the requirements of MIL-M-38510 have been superseded by MIL-PRF-38535, (see 6.4).

1.2 Part or Identifying Number (PIN). The PIN is in accordance with MIL-PRF-38535, and as specified herein.

1.2.1 <u>Device type.</u> The device types are as follows:

| Device type | Circuit                                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------------------|

| 01<br>02    | 16 x 48 x 8 logic array with uncommitted collector<br>16 x 48 x 8 logic array with active pull-up and a third |

|             | high-impedance state output.                                                                                  |

1.2.2 <u>Device class</u>. The device class is the product assurance level as defined in MIL-PRF-38535.

1.2.3 Case outline. The case outline is as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | Terminals | Package style        |

|----------------|------------------------|-----------|----------------------|

| х              | GDIP1-T28, CDIP2-T28   | 28        | Dual in line package |

Comments, suggestions, or questions on this document should be addressed to: Commander, Defense Supply Center Columbus, ATTN: DSCC-VAS, P. O. Box 3990, Columbus, OH 43218-3990, or emailed to <a href="mailto:memory@dscc.dla.mil">memory@dscc.dla.mil</a>. Since contact information can change, you may want to verify the currency of this address information using the ASSIST Online database at <a href="http://assist.daps.dla.mil">http://assist.daps.dla.mil</a>.

FSC 5962

#### 1.3 Absolute maximum ratings.

| Supply voltage range                                            | 0.5 V dc to 7.0 V dc              |

|-----------------------------------------------------------------|-----------------------------------|

| Input voltage range                                             | . 0.5 V dc at -10. mA to 5.5 V dc |

| Storage temperature range                                       | -65°C to +150°C                   |

| Lead temperature (soldering, 10 seconds)                        | +260°C                            |

| Thermal resistance, junction-to-case $(\theta_{JC})$ <u>1</u> / | . 27 °C / W                       |

| Output voltage applied                                          | 0.4 V dc to +5.5 V dc             |

| Output sink current                                             | . 9.6 mA                          |

| Maximum power dissipation, (P <sub>D</sub> ) <u>2</u> /         | . 2.0 W                           |

| Maximum junction temperature (T <sub>J</sub> )                  | . +175°C                          |

#### 1.4 Recommended operating conditions.

| Supply voltage                                     | 4.5 V dc minimum to 5.5 V dc maximum |

|----------------------------------------------------|--------------------------------------|

| Minimum high level input voltage                   |                                      |

| Maximum low level input voltage                    | 0.8 V dc                             |

| Case operating temperature range (T <sub>C</sub> ) |                                      |

#### 2.0 APPLICABLE DOCUMENTS

2.1 General. The documents listed in this section are specified in sections 3, 4, or 5 of this specification. This section does not include documents cited in other sections of this specification or recommended for additional information or as examples. While every effort has been made to ensure the completeness of this list, document users are cautioned that they must meet all specified requirements of documents cited in sections 3, 4, or 5 of this specification, whether or not they are listed.

#### 2.2 Government documents.

2.2.1 Specifications and standards. The following specifications and standards form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

#### **DEPARTMENT OF DEFENSE SPECIFICATIONS**

MIL-PRF-38535 - Integrated Circuits (Microcircuits) Manufacturing, General Specification for.

#### DEPARTMENT OF DEFENSE STANDARDS

| MIL-STD-883  | - | Test Method Standard for Microelectronics.            |

|--------------|---|-------------------------------------------------------|

| MIL-STD-1835 | - | Interface Standard Electronic Component Case Outlines |

(Copies of these documents are available online at http://assist.daps.dla.mil/quicksearch/ or http://assist.daps.dla.mil or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.3 Order of precedence. In the event of a conflict between the text of this specification and the references cited herein, the text of this document takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

- <u>1/</u> Heat sinking is recommended to reduce the junction temperature.

- 2/ Must withstand the added P<sub>D</sub> due to short circuit condition (e.g., I<sub>OS</sub>) test.

#### 3. REQUIREMENTS

3.1 <u>Qualification</u>. Microcircuits furnished under this specification shall be products that are manufactured by a manufacturer authorized by the qualifying activity for listing on the applicable qualified manufacturers list before contract award (see 4.2 and 6.3). When manufacturer programmed devices are delivered to the user, an altered item drawing shall be prepared by the procuring activity to specify the required program configuration.

3.2 <u>Item requirements</u>. The individual item requirements shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

3.3 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein.

3.3.1 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

3.3.2 Truth tables.

3.3.2.1 <u>Unprogrammed devices</u>. The truth tables for unprogrammed devices for contracts involving no altered item drawing shall be as specified on figure 2. When required in groups A, B, or C (see 4.4), the devices shall be programmed by the manufacturer prior to test as per table A-I (a minimum of 50% of the total number of gates programmed) or to any altered item drawing pattern which includes at least 25 percent of the total number of gates programmed.

3.3.2.2 <u>Programmed devices</u>. The truth table for programmed devices shall be as specified by the altered item drawing.

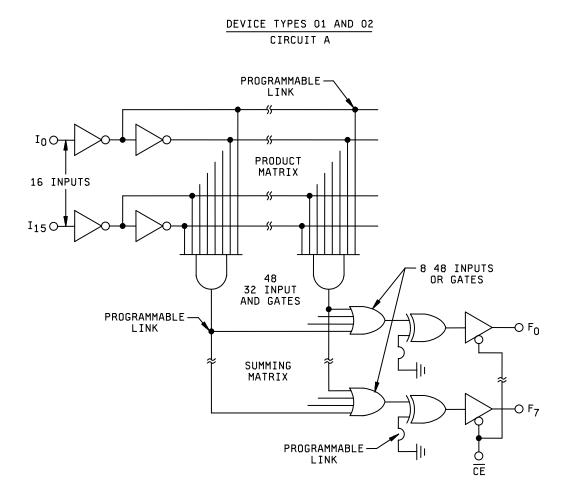

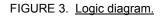

3.3.3 Logic diagrams. The logic diagram shall be as specified on figure 3.

3.3.4 <u>Case outlines</u>. Case outlines shall be in accordance with MIL-STD-1835 and 1.2.3 herein.

3.4 Lead material and finish. The lead material and finish shall be in accordance with MIL-PRF-38535 (see 6.6).

3.5 <u>Electrical performance characteristics</u>. Unless otherwise specified, the electrical performance characteristics are as specified in table I, and apply over the full recommended case operating temperature range.

3.6 <u>Electrical test requirements</u>. Electrical test requirements shall be as specified in table III and (where applicable), the altered item drawing for the applicable device type and device class. The subgroups of table III which constitute the minimum electrical test requirements for screening, qualifications, and quality conformance, by device class, are specified in table II.

3.7 <u>Marking</u>. Marking shall be in accordance with MIL-PRF-38535. For programmed devices, the altered item drawing number shall be added to the marking by the programming activity.

3.8 <u>Processing options</u>. Since the FPLA is an unprogrammed device capable of being programmed by either the manufacturer or the user to result in a wide variety of configurations, two processing options are provided for selection in the contract, using an altered item drawing.

3.8.1 <u>Unprogrammed FPLA delivered to the user</u>. All testing shall be verified through group A testing as defined in 3.3.2.1, tables II and III. It is recommended that users perform subgroups 7 and 9 after programming to verify the specific program configuration.

3.8.2 <u>Manufacturer programmed FPLA delivered to the user</u>. All testing requirements and quality assurance provisions herein, including the requirements of the altered item drawing, shall be satisfied by the manufacturer prior to delivery.

3.9 <u>Microcircuit group assignment.</u> The devices covered by this specification shall be in microcircuit group number 14 (see MIL-PRF-38535, appendix A).

| Test                                                                   | Symbol                                  | Test conditions 1/                                              | Device | Lir | nits | Unit |

|------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------|--------|-----|------|------|

|                                                                        |                                         | _                                                               | types  | Min | Max  |      |

| High-level output voltage                                              | V <sub>OH</sub>                         | V <sub>CC</sub> = 4.5 V;<br>I <sub>OH</sub> = -2 mA             | 02     | 2.4 |      | V    |

| Low-level output voltage                                               | V <sub>OL</sub>                         | V <sub>CC</sub> = 5.5 V;<br>I <sub>OL</sub> = 9.6 mA            | 01,02  |     | 0.5  | V    |

| Input clamp voltage                                                    | V <sub>IC</sub>                         | V <sub>CC</sub> = 4.5 V;<br>I <sub>IN</sub> = -18 mA            | 01,02  |     | -1.2 | V    |

| Maximum collector cut-off<br>current                                   | I <sub>CEX</sub>                        | V <sub>CC</sub> = 5.5 V;<br>V <sub>O</sub> = 5.5 V              | 01     |     | 100  | μΑ   |

| High-impedance (off-state) output high current                         | I <sub>OHZ</sub>                        | V <sub>CC</sub> = 5.5 V;<br>V <sub>O</sub> = 5.5 V              | 02     |     | 100  | μΑ   |

| High-impedance (off-state) output low current                          | I <sub>OLZ</sub>                        | V <sub>CC</sub> = 5.5 V;<br>V <sub>O</sub> = 0.45 V             | 02     |     | -60  | μΑ   |

| High-level input current                                               | I <sub>IH</sub>                         | V <sub>CC</sub> = 5.5 V;<br>V <sub>IN</sub> = 5.5 V             | 01,02  |     | 50   | μΑ   |

| Low-level input current                                                | IIL                                     | V <sub>CC</sub> = 5.5 V;<br>V <sub>IN</sub> = 0.45 V            | 01,02  | -1  | -250 | μΑ   |

| Short circuit output<br>current                                        | I <sub>OS</sub> <u>2</u> /              | V <sub>CC</sub> = 5.5 V;<br>V <sub>OUT</sub> = GND              | 02     | -10 | -85  | mA   |

| Supply current                                                         | I <sub>CC</sub>                         | $V_{CC} = 5.5 V;$<br>$V_{IN} = 0;$<br>outputs = open            | 01,02  |     | 180  | mA   |

| Propagation delay time<br>high-to-low level logic,<br>input to output  | t <sub>PHL1</sub><br>(t <sub>IA</sub> ) | V <sub>CC</sub> = 4.5 V<br>and 5.5 V;<br>C <sub>L</sub> = 30 pF | 01,02  |     | 80   | ns   |

| Propagation delay time<br>low-to-high level logic,<br>input to output  | t <sub>PLH1</sub><br>(t <sub>IA</sub> ) | (See figure 4)                                                  | 01,02  |     | 80   | ns   |

| Propagation delay time<br>high-to-low level logic,<br>enable to output | t <sub>PHL2</sub><br>(t <sub>EC</sub> ) |                                                                 | 01,02  |     | 50   | ns   |

| Propagation delay time<br>low-to-high level logic,<br>enable to output | t <sub>PLH2</sub><br>(t <sub>CO</sub> ) | ]                                                               | 01,02  |     | 50   | ns   |

# TABLE I. Electrical performance characteristics.

1/ Complete terminal conditions shall be specified in table III.

2/ Not more than one output shall be grounded at one time. Output shall be at high logic level prior to test.

| IADLE II. <u>EI</u>                                                            | <u>ectrical test requirements.</u> |                                  |

|--------------------------------------------------------------------------------|------------------------------------|----------------------------------|

| MIL-PRF-38535 test                                                             | Subgroups (per ta                  | able III) <u>2</u> /, <u>3</u> / |

| requirements                                                                   | Class S                            | Class B                          |

|                                                                                | devices                            | devices                          |

| Interim electrical parameters<br>(pre burn-in)                                 | 1                                  | 1                                |

| Final electrical test parameters<br>for unprogrammed<br>devices                | 1*, 2, 3, 7*, 8                    | 1*, 2, 3, 7*, 8                  |

| Final electrical test parameters<br>for programmed<br>devices                  | 1*, 2, 3, 7*, 8, 9, 10, 11         | 1*, 2, 3, 7*, 8, 9               |

| Group A test requirements                                                      | 1, 2, 3, 7, 8, 9, 10, 11           | 1, 2, 3, 7, 8, 9, 10, 11         |

| Group B electrical test parameters<br>When using the method 5005 QCI<br>option | 1, 2, 3, 7, 8, 9, 10, 11           | N/A                              |

| Group C end-point electrical<br>parameters                                     | 1, 2, 3, 7, 8, 9, 10, 11           | 1, 2, 3, 7, 8                    |

| Group D end-point electrical<br>parameters                                     | 1, 2, 3, 7, 8                      | 1, 2, 3, 7, 8                    |

| TABLE II. Electrical test requirements | TABLE II. | Electrical test | requirements. |

|----------------------------------------|-----------|-----------------|---------------|

|----------------------------------------|-----------|-----------------|---------------|

<u>1</u>/ (\*) indicates PDA applies to subgroups 1 and 7.

<u>2</u>/ Any or all subgroups may be combined when using high-speed testers.

<u>3</u>/ Subgroup 7 and 8 shall consist of verifying the pattern specified.

| Pin Number                 | Device Type                                                                                              |

|----------------------------|----------------------------------------------------------------------------------------------------------|

| Case X                     | 01 and 02                                                                                                |

|                            | FE                                                                                                       |

| 1<br>2<br>3<br>4<br>5<br>6 | I <sub>7</sub>                                                                                           |

| 3                          | I <sub>6</sub>                                                                                           |

| 4                          | I <sub>5</sub>                                                                                           |

| 5                          | <b>I</b> 4                                                                                               |

| 6                          | I <sub>3</sub>                                                                                           |

| 7                          | I <sub>2</sub>                                                                                           |

| 8                          | I <sub>1</sub>                                                                                           |

| 9                          | I <sub>0</sub>                                                                                           |

| 10                         | F <sub>7</sub>                                                                                           |

| 11                         | F <sub>6</sub>                                                                                           |

| 12                         | $F_5$                                                                                                    |

| 13                         | F <sub>4</sub>                                                                                           |

| 13<br>14                   | $     F_{7} \\     F_{6} \\     F_{5} \\     F_{4} \\     GND \\     F_{3} \\     F_{2} \\     F_{1}   $ |

| 15                         | F <sub>3</sub>                                                                                           |

| 16                         | F <sub>2</sub>                                                                                           |

| 17                         | F <sub>1</sub>                                                                                           |

| 18                         | F <sub>1</sub><br>F <sub>0</sub>                                                                         |

| 19                         | CE                                                                                                       |

| 20                         | I <sub>15</sub>                                                                                          |

| 21                         | I <sub>14</sub>                                                                                          |

| 22                         | I <sub>13</sub>                                                                                          |

| 22<br>23<br>24             | I <sub>12</sub>                                                                                          |

| 24                         | I <sub>11</sub>                                                                                          |

| 25                         | I <sub>10</sub>                                                                                          |

| 26                         | <b>I</b> 9                                                                                               |

| 27                         | I <sub>8</sub>                                                                                           |

| 28                         | V <sub>CC</sub>                                                                                          |

FIGURE 1. Terminal connections.

| Circuit |    |                 | Address                |                 |                 |          |                 |                |                |       |       |       |       |                |       |       | Jutou          | t lovo         | .1             |                |                |                |                |

|---------|----|-----------------|------------------------|-----------------|-----------------|----------|-----------------|----------------|----------------|-------|-------|-------|-------|----------------|-------|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Circuit | CE |                 | Address                |                 |                 |          |                 |                |                |       |       |       |       |                | _     | _     | (              | Dutpu          | lieve          |                |                |                |                |

| Туре    | 0L | I <sub>15</sub> | <b>I</b> <sub>14</sub> | I <sub>13</sub> | I <sub>12</sub> | $I_{11}$ | I <sub>10</sub> | l <sub>9</sub> | 1 <sub>8</sub> | $I_7$ | $I_6$ | $I_5$ | $I_4$ | I <sub>3</sub> | $I_2$ | $I_1$ | I <sub>0</sub> | F <sub>7</sub> | F <sub>6</sub> | F <sub>5</sub> | F <sub>4</sub> | F <sub>3</sub> | F <sub>2</sub> |

| Α       | L  | Х               | Х                      | Х               | Х               | Х        | Х               | Х              | Х              | Х     | Х     | Х     | Х     | Х              | Х     | Х     | Х              | L              | L              | L              | L              | L              | L              |

| В       | L  | Х               | Х                      | Х               | Х               | Х        | Х               | Х              | Х              | Х     | Х     | Х     | Х     | Х              | Х     | Х     | Х              | Н              | Н              | Н              | Н              | Н              | Н              |

| A, B    | Н  | Х               | Х                      | Х               | Х               | Х        | Х               | Х              | Х              | Х     | Х     | Х     | Х     | Х              | Х     | Х     | Х              | 1/             | 1/             | 1/             | 1/             | 1/             | 1/             |

| А, В    | н  | Х               | Х                      | Х               | Х               | х        | х               | х              | х              | х     | Х     | Х     | х     | х              | х     | Х     | Х              | Hi             | Hi             | Hi             | Hi             | Hi             | Hi             |

|         |    |                 |                        |                 |                 |          |                 |                |                |       |       |       |       |                |       |       |                | Ζ.             | Ζ.             | Ζ.             | Z              | Z              | Z              |

NOTES:

Output disabled.

X = Input may be high, low level, open circuit or as defined in Appendix A.

L = Low

H = High

Hi Z = High impedance.

FIGURE 2. <u>Truth table (unprogrammed).</u>

7

DEVICE TYPES 01 AND 02 CIRCUIT B

FIGURE 3. Logic diagram. - Continued.

NOTES:

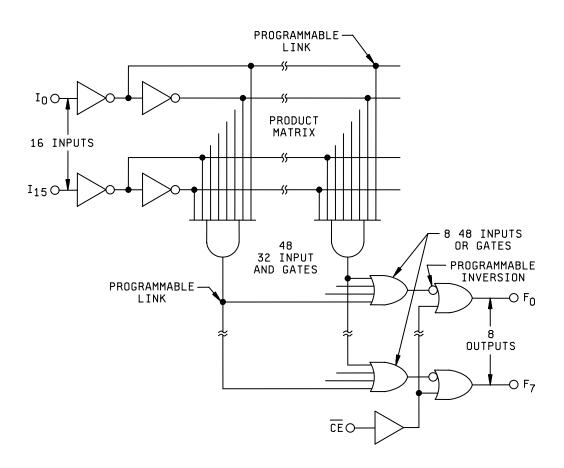

- 1. Test table for devices programmed in accordance with an altered item drawing may be replaced by the equivalent tests which apply to the specific program configuration for the resulting FPLA.

- 2. C<sub>L</sub> = 30 pF minimum, including jig and probe capacitance; R1 = 300  $\Omega$  ± 25% and R2 = 600  $\Omega$  ±20%.

- 3. Outputs may be under load simultaneously.

FIGURE 4. Switching time test circuit.

#### 4. VERIFICATION

4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with MIL-PRF-38535 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not effect the form, fit, or function as described herein.

4.2 <u>Qualification inspection</u>. Qualification inspection shall be in accordance with MIL-PRF-38535. Qualification data for subgroups 7, 8, 9, 10, and 11 shall be attributes only.

4.3 <u>Screening</u>. Screening shall be in accordance with MIL-PRF-38535, and shall be conducted prior to qualification, and conformance inspection. The following additional criteria shall apply:

- a. The burn-in test duration, test condition, and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The burn-in test circuit shall be maintained under document control by the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015 of MIL-STD-883.

- b. Interim and final electrical test parameters shall be as specified in table II, except interim electrical parameters test prior to burn-in is optional at the discretion of the manufacturer.

- c. Additional screening for space level product shall be as specified in MIL-PRF-38535.

- d. All devices processed by the manufacturer to an altered item drawing shall be programmed prior to burn in.

4.4 <u>Technology Conformance Inspection (TCI)</u>. Technology conformance inspection shall be in accordance with MIL-PRF-38535 and herein for groups A, B, C, and D inspections (see 4.4.1 through 4.4.4).

4.4.1 <u>Group A inspection</u>. Group A inspection shall be in accordance with table III of MIL-PRF-38535 and as follows:

- a. Tests shall be as specified in table II.

- b. Subgroups 4, 5, and 6 of table III of MIL-PRF-38535 shall be omitted.

- c. For unprogrammed devices, a sample shall be selected to satisfy programmability requirements prior to performing subgroups 9, 10, and 11. Twelve (12) devices shall be submitted to programming (see 3.3.2.1). If more than two devices fail to program, the lot shall be rejected. At the manufacturers option, the sample may be increased to 24 total devices with no more than 4 total device failures allowable.

- d. For unprogrammed devices, ten devices from the programmability sample shall be submitted to the requirements of group A, subgroups 9, 10, and 11. If more than two total devices fail in all three subgroups, the lot shall be rejected. At the manufacturers option, the sample may be increased to 20 total devices with no more than four total device failures allowable.

- 4.4.2 Group B inspection. Group B inspection shall be in accordance with table II of MIL-PRF-38535.

- a. Water drop test. This test shall be added to group B for class S devices. The devices selected for subgroup 2 (b) testing shall be a sealed, electrically good unprogrammed device which has passed the applicable screening and group A electrical test requirements. The device shall be carefully delidded and functionally verified to contain no programmed bits. Power shall be applied (or continually cycled through its test sequence), for the duration of the test. A drop of deionized water (resistivity of 5 megohms minimum at the point of use and at 25°C) shall be placed on the memory element containing nichrome film resistors so as to completely cover a minimum of 25 percent of the memory bits without touching any bonding pads, wires, or exposed metallization. Examination the water drop at 20 X magnification during placement with a micropipette is sufficient to determine coverage. The water drop shall be allowed to remain with the device under power for a minimum of 3 minutes duration. The power shall be removed, the device dried, and the device functionally verified to contain no programmed bit. Failure of any functional test which results from an open thin nichrome resistor (other than test equipment induced) shall fail the lot.

b. Electrical parameters shall be as specified in table II herein.

4.4.3 <u>Group C inspection</u>. Group C inspection shall be in accordance with table IV of MIL-PRF-38535 and as follows:

- a. End-point electrical parameters shall be as specified in table II herein.

- b. The steady-state life test duration, test condition, and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The burn-in test circuit shall be maintained under document control by the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005 of MIL-STD-883.

- c. For qualification, at least 50 percent of the sample selected for life testing shall be programmed (see 3.3.2). For quality conformance inspection, the programmability sample (see 4.4.1c) shall be included in the life test.

- 4.4.4 <u>Group D inspection</u>. Group D inspection shall be in accordance with table V of MIL-PRF-38535; end point electrical parameters shall be as specified in table II herein.

- 4.5 <u>Methods of inspection</u>. Methods of inspection shall be as specified in the appropriate tables and as follows:

4.5.1 <u>Voltage and current</u>. All voltages given are referenced to the microcircuit ground terminal. Currents given are conventional and positive when flowing into the referenced terminal.

- 4.6 <u>Programming procedure for circuit A</u>. The programming specifications in table IV and the following procedures shall be used for programming the device.

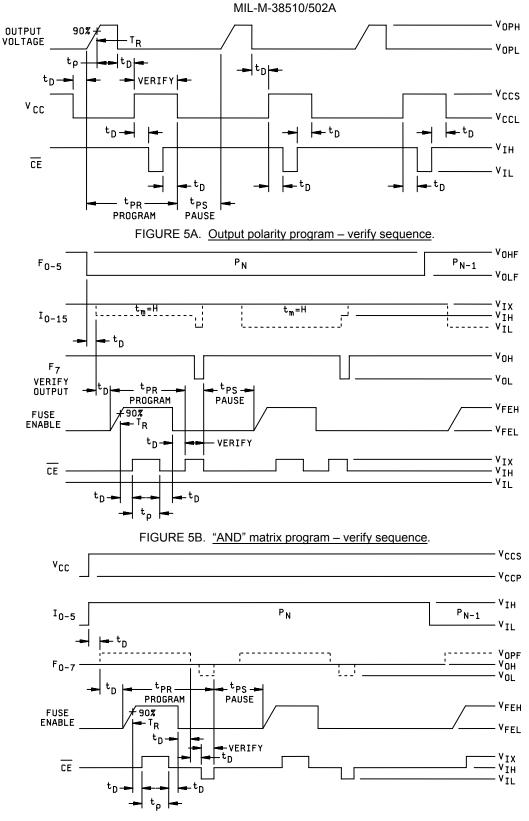

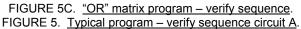

- 4.6.1 Output polarity.

- 4.6.1.1 <u>Program active low (F<sub>P</sub> function)</u>. Program output polarity before programming "AND" matrix and "OR" matrix. Program 1 output at a time. (S) links of unused outputs are not required to be fused.

- a. Set GND (pin 14), and FE (pin 1) to 0 V.

- b. Set  $V_{CC}$  (pin 28) to  $V_{CCL}$ .

- c. Set  $\overline{CE}$  (pin 19), and I<sub>0</sub> through I<sub>15</sub> to V<sub>IH</sub>.

- d. Apply  $V_{OPH}$  to the appropriate output, and remove after a period  $t_p$ .

- e. Repeat step D to program other outputs.

#### 4.6.1.2 Verify output polarity.

- a. Set GND (pin 14) to 0 V, and  $V_{CC}$  (pin 28) to  $V_{CCS}$ .

- b. Enable the chip by setting  $\overline{CE}$  (pin 19) to V<sub>IL</sub>.

- c. Address a non-existent P-term by applying  $V_{IH}$  to all inputs  $I_0$  through  $I_{15}$ .

- d. Verify output polarity by sensing the logic state of outputs F<sub>0</sub> through F<sub>7</sub>. All outputs at a high logic level are programmed active low (F<sub>P</sub> function), while all outputs at a low logic level are programmed active high (F<sub>P</sub> function).

- e. Return  $V_{CC}$  to  $V_{CCP}$  or  $V_{CCL}$ .

f. For class S and B devices, if any output polarity does not verify as programmed, it shall be considered a programming reject. For class C devices, if any output does not verify as programmed, repeat 4.6.1.1 one time only. Outputs which fail to program the second time shall be considered programming rejects.

#### 4.6.2 <u>"AND" Matrix</u>.

- 4.6.2.1 <u>Programming input variable</u>. Program one input at a time and one P-term at a time. All input variable links of unused P-terms are not required to be fused. However, unused input variables must be programmed as Don't Care for all programmed P-terms.

- a. Set GND (pin 14) to 0 V, and  $V_{CC}$  (pin 28) to  $V_{CCP}$ .

- b. Disable all device outputs by setting  $\overline{CE}$  (pin 19) to V<sub>IH</sub>.

- c. Disable all input variables by applying  $V_{IX}$  to inputs  $I_0$  through  $I_{15}$ .

- d. Address the P-term to be programmed (No. 0 through 47) by forcing the corresponding binary code on outputs  $F_0$  through  $F_5$  with  $F_0$  as LSE. Use standard TTL logic levels  $V_{OHF}$  and  $V_{OLF}$ .

- e. If the P-term contains neither  $I_0$  or  $\overline{I}_0$  (input is a Don't care), fuse both  $I_0$  and  $\overline{I}_0$  links by executing both steps f and g, before continuing with step k.

- f. If the P-term contains  $I_0$ , set to fuse the  $\overline{I}_0$  link by lowering the input voltage at  $I_0$  from  $V_{IX}$  to  $V_{IL}$ . Execute steps h, i, and j.

- g. If the P-term contains  $\overline{I}_{0}$ , set to fuse the I<sub>0</sub> link by lowering the input voltage at I<sub>0</sub> from V<sub>IX</sub> to V<sub>IL</sub>. Execute steps h, i, and j.

- h. After t<sub>D</sub> delay, raise FE (pin 1) from V<sub>FEL</sub> to V<sub>FEH</sub>.

- i. After t<sub>D</sub> delay, pulse the  $\overline{CE}$  input from V<sub>IH</sub> to V<sub>IX</sub> for a period of t<sub>P</sub>.

- j. After t<sub>D</sub> delay, return FE input to V<sub>FEL</sub>.

- k. Disable programmed input by returning I<sub>0</sub> to V<sub>IX</sub>.

- I. Repeat steps e through k for all other input variables.

- m. Repeat steps d through e for all other P-terms.

- n. Remove V<sub>IX</sub> from all input variables.

#### 4.6.2.2 Verify input variable.

- a. Set GND (pin 14) to 0 V,  $V_{CC}$  (pin28) to  $V_{CCP}$ , and FE (pin 1) to  $V_{FEL}$ .

- b. Enable  $F_7$  output by setting CE to  $V_{IX}$ .

- c. Disable all input variables by applying  $V_{IX}$  to inputs  $I_0$  through  $I_{15}$ .

- d. Address the P-term to be verified (No. 0 through 47) by forcing the corresponding binary code on outputs  $F_0$  through  $F_5$ .

- e. Interrogate input variable I<sub>0</sub> as follows:

- 1. Lower the input voltage to  $I_0$  from  $V_{IX}$  to  $V_{IH}$ , and sense the logic state of output  $F_7$ .

- 2. Lower the input voltage to  $I_0$  from  $V_{IH}$  to  $V_{IL}$ , and sense the logic state of output  $F_7$ .

f. The state of I<sub>0</sub> contained in the P-term is determined in accordance with the following truth table:

| I <sub>0</sub> | F <sub>7</sub> | Input variable state contained in P-term <u>1/</u> |

|----------------|----------------|----------------------------------------------------|

| 0              | 1              | Ī                                                  |

| 1              | 0              | - 0                                                |

| 0              | 0              | lo                                                 |

| 1              | 1              | 10                                                 |

| 0              | 1              | Don't Care                                         |

| 1              | 1              | Dent Gale                                          |

| 0              | 0              | $(I_0), (\overline{I}_0)$                          |

| 1              | 0              |                                                    |

Two tests are required to uniquely determine the state of the input variable contained in the P-term.

- g. Disable verified input by returning to  $I_0$  to  $V_{IX}$ .

- h. Repeat steps e and g for all other input variables.

- i. Repeat steps d through h for all other P-terms.

- j. Remove V<sub>IX</sub> from all input variables.

- k. For class S and B devices, if any gate does not verify as programmed, it shall be considered a programming reject.

#### 4.6.3 <u>"OR" (Sum) Matrix</u>.

- 4.6.3.1 <u>Program product term</u>. Program one output at a time for a P-term at the time. All P<sub>n</sub> links in the "OR" matrix corresponding to unused outputs and unused P-terms are not required to be fused.

- a. Set GND (pin 14) to 0 V, and  $V_{CC}$  (pin 28) to  $V_{CCS}$ .

- b. Disable the chip by setting  $\overline{CE}$  (pin 19) to V<sub>IH</sub>.

- c. Set inputs  $I_6$  through  $I_{15}$  to  $V_{IH}$  or  $V_{IL}$ .

- d. Address the P-term to be programmed (No. 0 through 47) by applying the corresponding binary code to input variables  $I_0$  through  $I_{5}$ , with  $I_0$  as LSB.

- e. If the P-term is contained in output functions F<sub>0</sub> (F<sub>0</sub> = 1 or F<sub>0</sub> = 0), go to step g, (fusing cycle not required).

- f. If the P-term is not contained in output function  $F_0$  ( $F_0 = 0$  or  $F_0 = 1$ ), set to fuse the  $P_n$  link by forcing output  $F_0$  to  $V_{OPF}$ .

- g. After  $t_D$  delay, raise FE (pin 1) from  $V_{FEL}$  to  $V_{FEH}$ .

- h. After  $t_D$  delay, pulse the CE input from  $V_{IH}$  to  $V_{IX}$  for a period  $t_P$ .

- i. After t<sub>D</sub> delay, return FE input to V<sub>FEL</sub>.

- j. After  $t_D$  delay, remove  $V_{OPF}$  from output  $F_0$ .

- k. Repeat steps e through j for all other output functions.

- I. Repeat steps d through k for all other P-terms.

- m. Remove  $V_{CCS}$  from  $V_{CC}$ .

# 4.6.3.2 Verify product term.

- a. Set GND (pin 14) to 0 V, and  $V_{CC}$  (pin 28) to  $V_{CCS}$ .

- b. Enable the chip by setting  $\overline{CE}$  (pin 19) to V<sub>IL</sub>.

- c. Set inputs  $I_0$  through  $I_{15}$  to  $V_{IH}$  and  $V_{IL}$ .

- d. Address the P-term to be verified (No. 0 through 47) by applying the corresponding binary code to input variables  $I_0$  through  $I_5$ .

- e. To determine the status of the  $P_n$  link in the "OR" matrix for each output function  $F_P$  or  $F_P$  sense, the state of outputs  $F_0$  through  $F_7$ . The status of the link is given by the following truth table:

| ſ | Out               | Output             |             |  |  |  |  |  |

|---|-------------------|--------------------|-------------|--|--|--|--|--|

|   | Active high       | Active low         | P-term link |  |  |  |  |  |

|   | (F <sub>P</sub> ) | (F <sub>P</sub> °) |             |  |  |  |  |  |

|   | 0                 | 1                  | Fused       |  |  |  |  |  |

|   | 1                 | 0                  | Present     |  |  |  |  |  |

- f. Repeat steps d and e for all other P-terms.

- g. Remove  $V_{CCS}$  from  $V_{CC}$ .

- h. For class S and B devices, if any bit does not verify as programmed it shall be considered a programming reject.

- 4.7 <u>Programming procedure for circuit B</u>. The programmed specifications on table V and the following procedures shall be used for programming the device.

- 4.7.1 Program "PRODUCT (AND)" matrix.

- 4.7.1.1 All 48 AND gates of the product matrix are fuse linked to both the true and false lines of every input buffer in the initial unprogrammed state. The initial logic expression for the 48 unprogrammed AND gates is I<sub>0</sub> ° I<sub>1</sub> ° I<sub>1</sub> ° I<sub>1</sub> ° I<sub>15</sub> ° I<sub>15</sub> (where I<sub>n</sub> or I<sub>n</sub> is defined to be an input term). Programming the fuse located by the selection of an input line, 'i<sub>n</sub>" and the mth AND gate replaces the input term I<sub>n</sub> with "1" in the logic expression for the mth AND gate.

- a. Connect pin 28 ( $V_{CC}$ ) to 5.0 V.

- b. Connect pin 14 (GND) to ground.

- c. Connect pin 19 ( $\overline{CE}$ ) to a TTL HIGH level.

- d. Apply TTL levels to pins 10 through 13, 15, and 16 (F<sub>7</sub> through F<sub>2</sub>) to address an on chip one of forty eight decoder to select the AND gate to be programmed (F<sub>7</sub> = LSB and F<sub>2</sub> = MSB).

- e. Apply 12.0 V to all input pins ( $I_0$  through  $I_{15}$ ).

- f. Apply the proper TTL level to an Ix input pin as follows (program one input at a time):

- 1. If the product term to be programmed contains the input term lx (where x = 0 through 15), lower the lx pin to a TTL HIGH level.

- 2. If the product term to be programmed contains the input term Ix, lower the  $\overline{I} x$  to a TTL LOW level.

- 3. If the product term does not contain the input terms  $\overline{1}$  x or lx (i.e., lx is a DON'T CARE input), perform steps f1, g, f2, and g.

- g. Apply a 15 V programming pulse to pin 1 (FE) according to the programming specification table.

- h. Repeat steps e through g for each input of the selected product term.

- i. Repeat steps d through h for all other product terms to be programmed.

- j. Program one input at a time.

- k. All unused inputs of programmed product terms must be programmed as DON'T CARES.

- I. Inputs of unused product lines are not required to be programmed.

- m. Pin 18 ( $F_0$ ) is in the read mode (open collector). Care must be taken so that this pin is either left open, grounded, or loaded such that the current flowing into the pin does not exceed 16 mA.

#### 4.7.1.2 Verify "PRODUCT (AND)" matrix.

- a. Connect pin 28 (V<sub>CC</sub>) to 5.0 V.

- b. Connect pin 14 (GND) to ground.

- c. Connect pin 19 ( $\overline{CE}$ ) to a TTL HIGH level.

- d. Apply TTL levels to pins 10 through 13, 15, and 16 (F<sub>7</sub> through F<sub>2</sub>) to address an on chip one of fortyeight decoder to select the AND gate to be verified (F<sub>7</sub> = LSB and F<sub>2</sub> = MSB).

- e. Apply 10.8 V to all input pins ( $I_0$  through  $I_{15}$ ).

- f. Test the state of the Ix input as follows:

- 1. Lower the Ix pin to a TTL HIGH level and sense the voltage on pin 18 (F<sub>0</sub>).

- 2. Lower the Ix pin to a TTL LOW and sense the voltage on pin 18 (F<sub>0</sub>).

- g. The state of the lx input is determined as follows:

|                                | lx =<br>TTL HIGH | lx =<br>TTL LOW | Condition of<br>Ix for selected<br>product term. |

|--------------------------------|------------------|-----------------|--------------------------------------------------|

|                                | Н                | Н               | Don't Care                                       |

| Level at output F <sub>0</sub> | Н                | L               | Ix IN P-term                                     |

|                                | L                | Н               | Ix IN P-term                                     |

|                                | L                | L               | unprogrammed                                     |

NOTES:

- 1.  $F_0$  in this mode functions as an open collector output,  $H = \ge 2.0 \text{ V}, L \le 0.8 \text{ V}.$

- 2. The table above is valid regardless of the polarity (active HIGH or active LOW) of F<sub>0</sub>.

- 3. Pin 1 (FE) should be either floating or grounded.

#### 4.7.2 Program summing matrix.

- 4.7.2.1 All 8 OR gates of the summing matrix are fuse linked to the outputs of the AND gates in the initial unprogrammed state. The initial logic expressions (sum of products) of the eight unprogrammed OR gates is P0 + P1 + P2 + ° ° ° + P47 where Pm is the product term programmed into the mth AND gate. Programming the fuse located by the selection of the mth AND gate and the nth summing line replaces the product term Pm with '0' in the logic expression of the nth OR gate. The nth summing line is selected by the selection of the nth OR gate.

- a. Connect pin 28 (V<sub>CC</sub>) to 5.0 V.

- b. Connect pin 14 (GND) to ground.

- c. Connect pin 19 ( $\overline{CE}$ ) to a TTL HIGH level.

- d. Apply TTL levels to pins 4 through 9 ( $I_5$  through  $I_0$ ) to address an on chip one of forty-eight decoder to select the AND gate to be programmed ( $I_0$  = LSB and  $I_5$  = MSB).

- e. Apply a TTL HIGH level to pins 20 and 21 (I<sub>15</sub> and I<sub>14</sub>).

- f. Connect the remaining input pins to 12.0 V.

- g. Apply an 18 V programming pulse (see programming specification table) at the pin of the output to be programmed. Other output pins should be either left open or tied to a TTL HIGH level.

- h. Progran one output pin at a time.

- i. All unused product lines are not required to be programmed.

#### 4.7.2.2 Verify summing matrix.

- a. Connect pin 28 ( $V_{CC}$ ) to 5.0 V.

- b. Connect pin 14 (GND) to ground.

- c. Connect pin 19 ( $\overline{CE}$ ) to a TTL LOW level.

- d. Apply TTL levels to pins 4 through 9 ( $I_5$  through  $I_0$ ) to address an on chip one of forty eight decoder to select the AND gate to be verified ( $I_0$  = LSB and  $I_5$  = MSB).

- e. Apply a TTL HIGH level to pins 20 and 22 ( $I_{15}$  and  $I_{13}$ ).

- f. Connect the remaining input pins to 12.0 V.

- g. Sense the voltage on the output pin to be verified. The programming of the selected product line to the output line can be determined as follows:

| Output<br>Reads | Fuse<br>Link     |

|-----------------|------------------|

| Reads           | LINK             |

| L               | Blown (inactive) |

| Н               | Unblown (active) |

- h. Repeat steps d through g with  $V_{CC}$  at 4.4 V (LOW  $V_{CC}$  read).

- i. The condition of the fuse link can be determined from the table above regardless of the polarity (active HIGH or active LOW) of the output buffer being verified.

#### 4.7.3 Program output polarity.

- 4.7.3.1 The initial unprogrammed state of all eight output buffers is active LOW or inverting. To program an output buffer into the active HIGH or non-inverting state, proceed as follows:

- a. Connect pin 28 (V<sub>CC</sub>) to 5.0 V.

- b. Connect pin 14 (GND) to ground.

- c. Connect pin 19 ( $\overline{CE}$ ) to a TTL HIGH level.

- d. Apply a TTL HIGH level to pins 4 through 9 ( $I_5$  through  $I_0$ ).

- e. Apply a TTL HIGH level to pin 20 (I<sub>15</sub>).

- f. Connect the remaining input pins to 12.0 V.

- g. Apply an 18 V programming pulse (see programming specifications table) to the pin of the output to be programmed. Other output pins should be either left open or tied to a TTL HIGH level.

- h. Program one output at a time.

#### 4.7.3.2 Verify output polarity.

- a. Connect pin 28 (V<sub>CC</sub>) to 5.0 V.

- b. Connect pin 14 (GND) to ground.

- c. Connect pin 19 ( $\overline{CE}$ ) to a TTL LOW level.

- d. Apply a TTL HIGH level to pins 4 through 9 ( $I_5$  through  $I_0$ ).

- e. Apply a TTL HIGH level to pins 21 and 22 (I<sub>14</sub> and I<sub>13</sub>).

- f. Connect the remaining input pins to 12.0 V.

- g. Sense the voltage on the pin of the output buffer to be verified. The condition of the output can be determined as follows:

| Output reads | Output state |

|--------------|--------------|

| Н            | Active LOW   |

| L            | Active HIGH  |

- h. Repeat with  $V_{CC}$  at 4.4 V (LOW  $V_{CC}$  read).

- 4.7.4 <u>Summary of pin voltage circuit B</u>. In addition to verifying the Product (AND) Matrix, Summing Matrix, and Output Polarity separately after programming, a complete logic verification (normal read) with V<sub>CC</sub> at 5.0 V is recommended after a device has been fully programmed. Table VI summarizes the full programming and verifying procedures.

| Subgroup                  | Symbol          | MIL-<br>STD-                                                                                   | Case<br>X                                                                                          | 1  | 2                     | 3                        | 4                         | 5                         | 6                              | 7                 | 8                             | 9                        | 10     | 11     | 12     | 13     | 14                                                                                                 | 15     | 16     | 17     | 18     | 19    | 20                        | 21                        | 22                | 23                        | 24                        | 25                |

|---------------------------|-----------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----|-----------------------|--------------------------|---------------------------|---------------------------|--------------------------------|-------------------|-------------------------------|--------------------------|--------|--------|--------|--------|----------------------------------------------------------------------------------------------------|--------|--------|--------|--------|-------|---------------------------|---------------------------|-------------------|---------------------------|---------------------------|-------------------|

|                           |                 | 883<br>method                                                                                  | Test                                                                                               | FE | 17                    | 16                       | 15                        | 14                        | 13                             | 12                | 11                            | 10                       | F7     | F6     | F5     | F4     | GND                                                                                                | F3     | F2     | F1     | F0     | CE    | l15                       | 114                       | 113               | 112                       | 111                       | 110               |

| 1<br>T <sub>C</sub> =25°C | V <sub>IC</sub> |                                                                                                | no.<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17   |    | -18mA                 | -18mA                    | -18mA                     | -18mA                     | -18mA                          | -18mA             | -18mA                         | -18mA                    |        |        |        |        | GND<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 |        |        |        |        | -18mA | -18mA                     | -18mA                     | -18mA             | -18mA                     | -18mA                     | -18mA             |

|                           | V <sub>OL</sub> | 3007<br>"<br>"<br>"                                                                            | 18<br>19<br>20<br>21<br>22<br>23<br>24<br>25                                                       |    | <u>4/</u><br>""<br>"" | <u>4/</u><br>«<br>«<br>« | <u>4</u> /<br>«<br>«<br>« | <u>4</u> /<br>«<br>«<br>« | <u>4</u> /<br>«<br>«<br>«<br>« | 4/<br>«<br>«<br>« | <u>4/</u><br>«<br>«<br>«<br>« | <u>4/</u><br>«<br>«<br>« | -9.6mA | -9.6mA | -9.6mA | -9.6mA |                                                                                                    | -9.6mA | -9.6mA | -9.6mA | -9.6mA |       | <u>4</u> /<br>«<br>«<br>« | <u>4</u> /<br>«<br>«<br>« | 4/<br>«<br>«<br>« | <u>4</u> /<br>«<br>«<br>« | <u>4</u> /<br>«<br>«<br>« | 4/<br>«<br>«<br>« |

|                           | I <sub>IL</sub> | 3009<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>« | 26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42 |    | 0.45V                 | 0.45V                    | 0.45V                     | 0.45V                     | 0.45V                          | 0.451/            | 0.45V                         | 0.45V                    |        |        |        |        |                                                                                                    |        |        |        |        | 0.45V | 0.45V                     | 0 451/                    | 0.451/            | 0 451/                    | 0.45V                     | 0.45∨             |

|                           | I <sub>IH</sub> | 3010<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>« | 43<br>44<br>45<br>46<br>47<br>48<br>49<br>50<br>51<br>52<br>53<br>54<br>55<br>56<br>57<br>58<br>59 |    | 5.5V                  | 5.5V                     | 5.5V                      | 5.5V                      | 5.5V                           | 5.5V              | 5.5V                          | 5.5V                     |        |        |        |        |                                                                                                    |        |        |        |        | 5.5V  | 5.5V                      | 5.5V                      | 5.5V              | 5.5V                      | 5.5V                      | 5.5V              |

TABLE III. Group A inspection for device type 01.

See footnotes at end of table.

19

TABLE III. Group A inspection for device type 01 – Continued.

| Subgroup                  | Symbol                  | MIL-<br>STD-   | Case<br>X                                    | 1      | 2          | 3          | 4          | 5          | 6                    | 7            | 8          | 9          | 10         | 11         | 12         | 13         | 14            | 15         | 16         | 17         | 18         | 19                  | 20         | 21         | 22         | 23         | 24         | 25         |

|---------------------------|-------------------------|----------------|----------------------------------------------|--------|------------|------------|------------|------------|----------------------|--------------|------------|------------|------------|------------|------------|------------|---------------|------------|------------|------------|------------|---------------------|------------|------------|------------|------------|------------|------------|

|                           |                         | 883<br>method  | Test                                         | FE     | 17         | 16         | 15         | 14         | 13                   | 12           | 11         | 10         | F7         | F6         | F5         | F4         | GND           | F3         | F2         | F1         | F0         | CE                  | l15        | 114        | 113        | 112        | 111        | l10        |

| 1<br>T <sub>c</sub> =25°C | I <sub>CEX</sub>        |                | 60<br>61<br>62<br>63<br>64<br>65<br>66<br>67 |        |            |            |            |            |                      |              |            |            | 5.5V       | 5.5V       | 5.5V       | 5.5V       | GND<br>"<br>" | 5.5V       | 5.5V       | 5.5V       | 5.5V       | 4.5V<br>«<br>«<br>« |            |            |            |            |            |            |

|                           | I <sub>cc</sub>         | 3005           | 68                                           |        |            |            |            |            | GND                  |              |            | GND        |            |            |            |            | 44            |            |            |            |            | GND                 | GND        | GND        | GND        | GND        | GND        | GND        |

| 2                         | Same te                 | ests and       | termin                                       | al cor | nditions   | as in s    | ubgrou     | p 1, exc   | ept T <sub>c</sub> = | = 125°C      |            |            |            |            |            |            |               |            |            |            |            |                     |            |            |            |            |            |            |

| 3                         | Same te                 | ests and       | termin                                       | al cor | nditions   | as in s    | ubgrou     | р 1, ехс   | ept T <sub>c</sub> = | = -55°C.     |            |            |            |            |            |            |               |            |            |            |            |                     |            |            |            |            |            |            |

| 7<br>T <sub>C</sub> =25°C | Func-<br>tional<br>test |                | 69                                           |        | <u>1</u> / | <u>1</u> / | <u>1</u> / | <u>1</u> / | <u>1/</u>            | <u>1</u> /   | <u>1</u> / | <u>1</u> / | <u>1</u> / | <u>1</u> / | <u>1</u> / | <u>1</u> / | GND           | <u>1</u> / | <u>1</u> / | <u>1</u> / | <u>1/</u>  | GND                 | <u>1</u> / |

| 8                         | Same te                 | ests and       | termin                                       | al cor | nditions   | as in s    | ubgrou     | p 7, exc   | ept T <sub>c</sub> = | = -55°C.     |            |            |            |            |            |            |               |            |            |            |            |                     |            |            |            |            |            |            |

| 9<br>T <sub>c</sub> =25°C | t <sub>PHL1</sub>       | 3003<br>Fig. 4 | 70                                           |        | <u>2</u> /           | <u>2</u> /   | <u>2</u> / | <u>2</u> / | <u>3</u> / | <u>3</u> / | <u>3</u> / | <u>3</u> / | GND           | <u>3</u> / | <u>3</u> / | <u>3</u> / | <u>3</u> / | GND                 | <u>2</u> / |

| -                         | t <sub>PLH1</sub>       |                | 71                                           |        | "          | "          | и          | и          | 4                    |              |            | 8          | u          | н          | и          | u          | "             | u          | u          | -          | 8          | 66                  |            | 66         | 8          | 4          | 8          | -          |

|                           | t <sub>PHL2</sub>       |                | 72                                           |        | "          |            | н          | к          |                      | ш            | 8          |            | u          | ĸ          | "          | a          | "             | "          | u          |            |            |                     | ш          | 8          |            | 8          |            |            |

|                           | t <sub>PLH2</sub>       |                | 73                                           |        | "          | "          | "          | "          |                      |              |            |            | u          | "          | "          | u          | "             | "          | u          |            |            | -                   |            | **         |            | 66         |            | "          |

| 10                        | Same te                 | ests, terr     | minal co                                     | onditi | ons and    | d limits   | as subg    | roup 9,    | except               | $T_{c} = 12$ | 25°C.      |            |            |            |            |            |               |            |            |            |            |                     |            |            |            |            |            |            |

|                           |                         |                |                                              |        |            |            |            |            |                      |              |            |            |            |            |            |            |               |            |            |            |            |                     |            |            |            |            |            |            |

|                           | Same te                 | ests, terr     | ninal co                                     | onditi | ons and    | l limits   | as subg    | roup 9,    | except               | $T_{c} = -5$ | 5°C.       |            |            |            |            |            |               |            |            |            |            |                     |            |            |            |            |            |            |

20

- 1/ The functional tests shall verify that no fuses are blown for unprogrammed devices or that the altered item drawing pattern exists for programmed devices (see table II). The functional tests shall be accomplished as defined in Appendix A for unprogrammed devices.

- $\underline{2}$ / (Programmed device) The test will check all inputs, gates, and outputs that have been programmed. Propagation test for t<sub>PHL1</sub>, t<sub>PLH1</sub>, t<sub>PLH2</sub> is also measured. This test shall be performed with V<sub>CC</sub> = 4.5 V, and V<sub>CC</sub> = 5.5 V.

- $\underline{3}$ / The outputs are loaded per figure 4.

- 4/ For programmed devices, select an appropriate set of inputs to acquire the desired output state.

| Subgroup                  | Symbol          | MIL-<br>STD-                                                                                   | Case<br>X                                                                                          | 1  | 2                         | 3                        | 4                        | 5                              | 6                                  | 7                          | 8                               | 9                        | 10    | 11    | 12    | 13    | 14                                                                                                 | 15    | 16    | 17    | 18    | 19    | 20                         | 21                               | 22                               | 23                               | 24                               | 25                         |

|---------------------------|-----------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----|---------------------------|--------------------------|--------------------------|--------------------------------|------------------------------------|----------------------------|---------------------------------|--------------------------|-------|-------|-------|-------|----------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|----------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------|

|                           |                 | 883<br>method                                                                                  | Test<br>no.                                                                                        | FE | 17                        | 16                       | 15                       | 14                             | 13                                 | 12                         | 11                              | 10                       | F7    | F6    | F5    | F4    | GND                                                                                                | F3    | F2    | F1    | F0    | CE    | 115                        | 114                              | 113                              | 112                              | 111                              | 110                        |

| 1<br>T <sub>c</sub> =25°C | V <sub>iC</sub> |                                                                                                | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17          |    | -18mA                     | -18mA                    | -18mA                    | -18mA                          | -18mA                              | -18mA                      | -18mA                           | -18mA                    |       |       |       |       | GND<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>« |       |       |       |       | -18mA | -18mA                      | -18mA                            | -18mA                            | -18mA                            | -18mA                            | -18mA                      |

|                           | V <sub>OL</sub> | 3007<br>"<br>"<br>"                                                                            | 18<br>19<br>20<br>21<br>22<br>23<br>24<br>25                                                       |    | <u>4</u> /<br>"<br>"<br>" | <u>4/</u><br>«<br>«<br>« | <u>4/</u><br>«<br>«<br>« | <u>4</u> /<br>«<br>«<br>«<br>« | <u>4/</u><br>8<br>8<br>8<br>8<br>8 | <u>4/</u><br>«<br>«<br>«   | 4/<br>                          | <u>4/</u><br>«<br>«<br>« | 9.6mA | 9.6mA | 9.6mA | 9.6mA | ee<br>ee<br>ee<br>ee<br>ee                                                                         | 9.6mA | 9.6mA | 9.6mA | 9.6mA |       | <u>4</u> /<br>«<br>«<br>«  | <u>4</u> /<br>«<br>«<br>«        | <u>4</u> /<br>«<br>«<br>«        | <u>4</u> /<br>«<br>«<br>«        | <u>4</u> /<br>«<br>«<br>«        | <u>4</u> /<br>«<br>«<br>«  |

|                           | V <sub>OH</sub> | 3006<br>"<br>"<br>"                                                                            | 26<br>27<br>28<br>29<br>30<br>31<br>32<br>33                                                       |    |                           | и<br>и<br>и<br>и<br>и    | и<br>и<br>и<br>и<br>и    | и<br>и<br>и<br>и<br>и          | 8<br>8<br>8<br>8<br>8<br>8         | 8<br>8<br>8<br>8<br>8<br>8 | 8<br>8<br>8<br>8<br>8<br>8<br>8 |                          | -2mA  | -2mA  | -2mA  | -2mA  | 44<br>44<br>44<br>44<br>44                                                                         | -2mA  | -2mA  | -2mA  | -2mA  |       | 66<br>66<br>66<br>66<br>66 | 64<br>64<br>64<br>64<br>64<br>64 | 64<br>64<br>64<br>64<br>64<br>64 | 64<br>64<br>64<br>64<br>64<br>64 | 64<br>64<br>64<br>64<br>64<br>64 | ee<br>ee<br>ee<br>ee<br>ee |

|                           | I <sub>IL</sub> | 3009<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>« | 34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50 |    | 0.45V                     | 0.45V                    | 0.45V                    | 0.45V                          | 0.45V                              | 0.45V                      | 0.45V                           | 0.45V                    |       |       |       |       |                                                                                                    |       |       |       |       | 0.45V | 0.45V                      | 0.45V                            | 0.45V                            | 0.45V                            | 0.45V                            | 0.45V                      |

TABLE III. Group A inspection for device type 02.

See footnotes at end of table.

| Subgroup                  | Symbol                                 | MIL-                                                                                 | Case                                                                                                                              | 1                                                                                           | 2                                | 3                                                        | 4                         | 5                         | 6                                                                                           | 7                         | 8                        | 9                        | 10             | 11              | 12              | 13              | 14                                                                                                 | 15             | 16              | 17              | 18              | 19                 | 20                                                                                          | 21                                                                         | 22                       | 23                         | 24                                                                         | 25                       | 26                                                                              | 27                                                                                          |

|---------------------------|----------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------|---------------------------|---------------------------|---------------------------------------------------------------------------------------------|---------------------------|--------------------------|--------------------------|----------------|-----------------|-----------------|-----------------|----------------------------------------------------------------------------------------------------|----------------|-----------------|-----------------|-----------------|--------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------|----------------------------|----------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|                           |                                        | STD-<br>883                                                                          | X<br>Test                                                                                                                         | FF                                                                                          | 17                               | 16                                                       | 15                        | 14                        | 13                                                                                          | 12                        | l1                       | 10                       | F7             | F6              | F5              | F4              | GND                                                                                                | F3             | F2              | F1              | F0              | CE                 | I15                                                                                         | 114                                                                        | 113                      | 112                        | 111                                                                        | l10                      | 19                                                                              | 18                                                                                          |

|                           |                                        | method                                                                               | no.                                                                                                                               |                                                                                             |                                  | 10                                                       | 20                        | 14                        | 2                                                                                           | 14                        |                          |                          |                | 10              | 10              | 14              |                                                                                                    | 10             | 12              |                 | 10              | 0L                 | 110                                                                                         |                                                                            | 110                      | 112                        |                                                                            | 110                      | 10                                                                              |                                                                                             |

| 1<br>T <sub>c</sub> =25°C | Iμ                                     | 3010<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>« | $\begin{array}{c} 51 \\ 52 \\ 53 \\ 55 \\ 55 \\ 57 \\ 58 \\ 90 \\ 61 \\ 62 \\ 64 \\ 56 \\ 67 \\ 67 \\ 67 \\ 67 \\ 67 \\ 67 \\ 67$ |                                                                                             | 5.5V                             | 5.5V                                                     | 5.5V                      | 5.5V                      | 5.5V                                                                                        | 5.5V                      | 5.5V                     | 5.5V                     |                |                 |                 |                 | GND<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>«<br>« |                |                 |                 |                 | 5.5V               | 5.5V                                                                                        | 5.5V                                                                       | 5.5V                     | 5.5V                       | 5.5V                                                                       | 5.5V                     | 5.5V                                                                            | 5.5                                                                                         |

|                           | I <sub>OZH</sub>                       |                                                                                      | 68<br>69<br>70<br>71<br>72<br>73<br>74<br>75                                                                                      | <u>4/</u><br>«<br>«<br>«<br>«                                                               | <u>4</u> /<br>«<br>«<br>«        | 4/<br>«<br>«<br>«                                        | <u>4</u> /<br>«<br>«<br>« | <u>4</u> /<br>«<br>«<br>« | 4/<br>«<br>«<br>«                                                                           | <u>4</u> /<br>«<br>«<br>« | <u>4/</u><br>«<br>«<br>« | <u>4/</u><br>«<br>«<br>« | 5.51/          | 5.5V            | 5.5V            | 5.5V            | и<br>и<br>и<br>и<br>и                                                                              | 5.5V           | 5.5V            | 5.5V            | 5.5V            | GND<br>"<br>"<br>" | 4/<br>«<br>«<br>«                                                                           | <u>4</u> /<br>«<br>«<br>«                                                  | <u>4/</u><br>"<br>"<br>" | <u>4</u> /<br>«<br>«<br>«  | <u>4</u> /<br>«<br>«<br>«                                                  | <u>4/</u><br>«<br>«<br>« | <u>4/</u><br>«<br>«<br>«                                                        | 4<br>                                                                                       |

|                           | I <sub>OLZ</sub>                       |                                                                                      | 75                                                                                                                                | "                                                                                           |                                  |                                                          |                           | "                         |                                                                                             | "                         | "                        |                          | 5.5V           |                 |                 |                 | "                                                                                                  |                |                 |                 | 0.45V           | "                  |                                                                                             | u                                                                          | "                        |                            | u                                                                          | "                        |                                                                                 | "                                                                                           |