# QP82S100 - PLS100

October 9, 2007

# QP82S100 – PLS100 Field Programmable Logic Array (16 x 48 x 8)

## **General Description**

The QP82S100 – PLS100 PLA is a tri-state output bi-polar programmable logic array with field programmable metal fuse technology (NiChrome). The device utilizes the standard AND/OR/NOT (invert) architecture to directly implement custom sum of product logic equations.

Each Device consists of 16 dedicated inputs and 8 dedicated outputs. Each output is capable of being actively controlled by any or all of the 48 product terms. The True, Complement, or Don't Care condition of each of the 16 inputs can be ANDed together to comprise one P-Term. All 48 P-Terms can be selectively Ored to each output.

The device is fully TTL compatible, and chip enable control for expansion of input variables and output inhibit. The device features Tri-State outputs for ease of expansion terms and application in bus-organized systems.

The QP82S100 - PLS100 features:

- Field-Programmable (Ni-Cr link)

- Output Functions: 8

- I/O propagation delay: 50ns

- Input loading: -100uA

- Tri-State Output

#### Applications:

- CRT Display Systems

- Code Conversion

- Peripheral Controllers

- Function Generators

- Look-up and Decision Tables

- Microprogramming

- Address Mapping

- Input Variables: 16

- Product Terms: 48

- Power Dissipation: 600mW (typ.)

- Chip Enable Input

- Output Disable Function: High-Z

- Character Generators

- Data Security Encoders

- Fault Detectors

- Frequency Synthesizers

- 16-bit to 8-bit Bus Interface

- Random Logic Replacement

The device/family is constructed using Bipolar/NiChrome processing. Programming supported by Data I/O under QP Semi/Qualified Parts Lab 82S100

QP Semiconductor products are not authorized for use in any space applications. The inclusion of QP Semiconductor products in space applications implies that the space application manufacturer assumes all risk of such use and in doing so indemnifies QP Semiconductor against all charges.

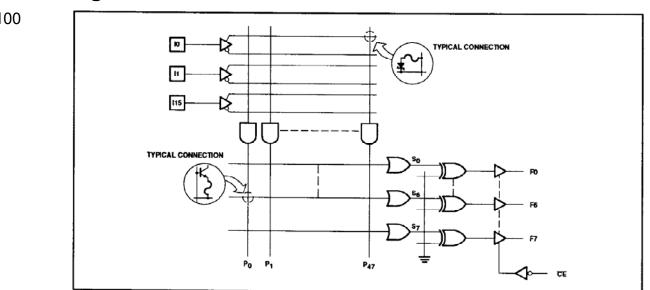

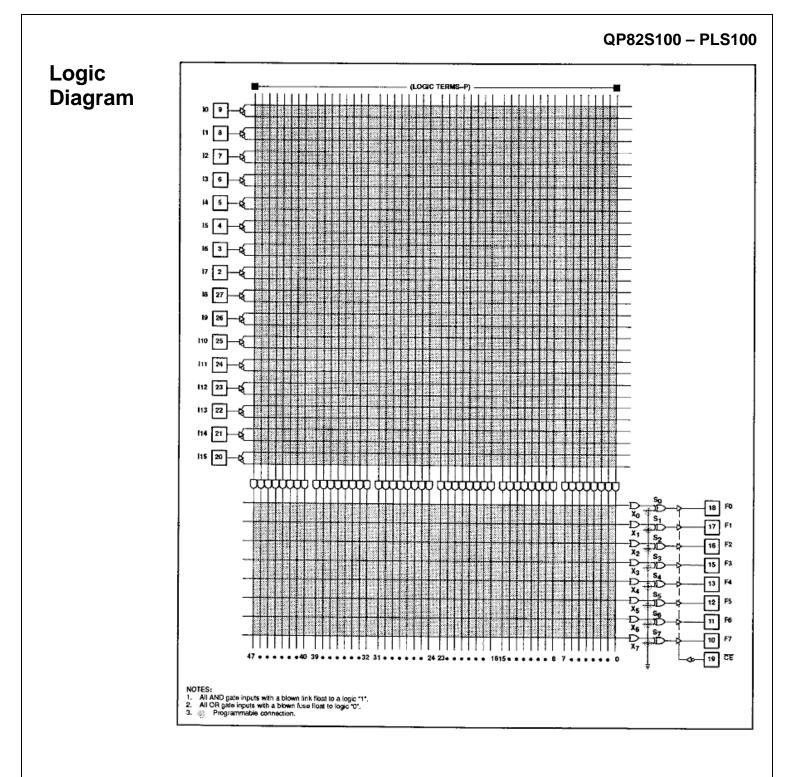

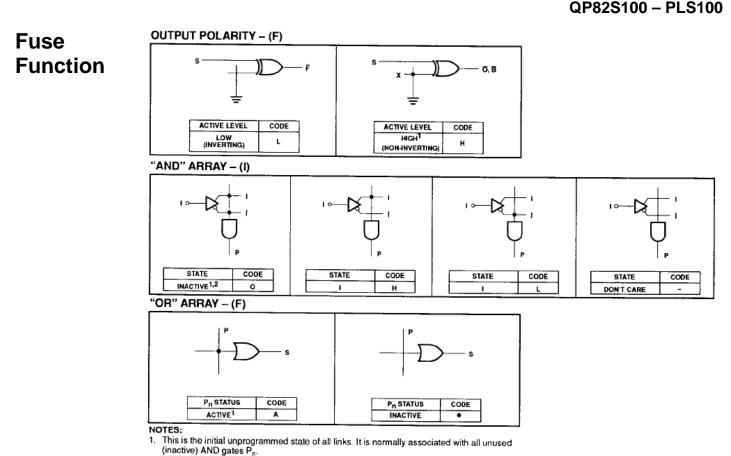

# **Functional Diagram**

QP82S100 PLS100

Any gate P<sub>n</sub> will be unconditionally inhibited if any one of its (I) link pairs is left intact.

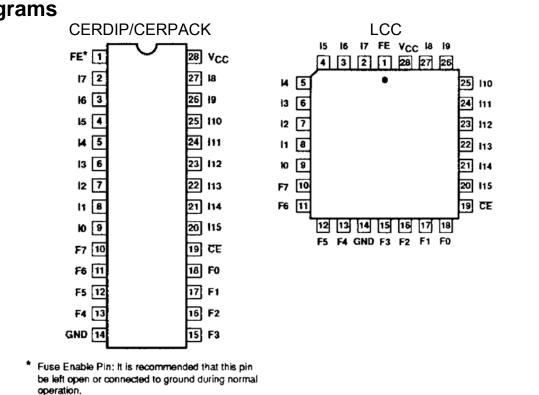

### **Connection Diagrams**

QP82S100 - PLS100

#### QP82S100 - PLS100

#### Absolute Maximum Ratings

Stresses above the AMR may cause permanent damage; extended operation at AMR may degrade performance and affect reliability

| Condition                                |              | Units    | Notes |

|------------------------------------------|--------------|----------|-------|

|                                          |              |          |       |

| Power Supply and Input Voltage           | -0.5 to +7.0 | Volts DC |       |

| Output Current                           | +100         | mA       |       |

| Input Clamp Current                      | -30 to +30   | mA       |       |

| No Terminal may exceed VCC               | >0.5         | Volts    | /1    |

| Storage Temperature Range                | -65 to +150  | °C       |       |

| Lead Temperature (soldering, 10 seconds) | +300         | °C       |       |

| Junction Temperature (T <sub>J</sub> )   | +150         | °C       |       |

|                                          |              |          |       |

| Condition                               |                 | Units    | Notes |

|-----------------------------------------|-----------------|----------|-------|

|                                         |                 |          |       |

| Supply Voltage Range (V <sub>CC</sub> ) | 4.5 to 5.5      | Volts DC |       |

| Input or Output Voltage Range           | 0.0 to $V_{CC}$ | Volts DC | /1    |

| Minimum High-Level Input Voltage (VIH)  | 2.0             | Volts DC |       |

| Maximum Low-Level Input Voltage (VIL)   | 0.8             | Volts DC |       |

| Case Operating Range $(T_c)$            | -55C to +125    | °C       | /2    |

/2 - Maximum PD, Maximum T<sub>1</sub> Are Not to Be Exceeded

**TABLE I – ELECTRICAL PERFORMANCE CHARACTERISTICS** Conditions Symbol Test Min Max Unit -55°C ≤TA≤+125°C **Unless Otherwise Specified** V Input High Voltage Vін  $V_{CC} = 5.5V$ 2.0 Input Low Voltage VII  $V_{CC} = 4.5V$ V 0.8 V<sub>CC</sub>=5.5V, V<sub>IN</sub>=5.5V Input High Current 50 uΑ  $I_{\rm H}$ V<sub>CC</sub>=5.5V, V<sub>IN</sub>=0.45V Input Low Current III --1.0 -250 uΑ Vic  $V_{CC} = 4.5V, I_{IN} = -18mA$ 1.2 V Input Clamp **Output High Voltage** VOH  $V_{CC} = 4.5V, I_{OH} = -2mA$ 2.4 V **Output Low Voltage**  $V_{CC} = 5.5V, I_{OH} = 9.6mA$ V Vol 0.5 Tri-State Output Current  $V_{CC} = 5.5V, V_{OUT} =$ **I**OZL -60.0 uA 0.45V, CE<sub>BAR</sub>=High  $V_{CC} = 5.5 V_{,V_{OUT}} =$ (High Impedance State) +100.0I<sub>OZH</sub> uA 5.5V, CE<sub>BAR</sub>=High Short Circuit Current  $V_{CC} = 5.5 V, V_{OUT} = 0 V,$ -15 -85 mΑ los CE<sub>BAR</sub>=Low Duration not to exceed 1 second, one output at a time Power Supply Current 180 Icc  $V_{CC} = 5.5V$ mΑ

#### QP82S100 - PLS100

| TABLE I – ELECTRICAL PERFORMANCE CHARACTERISTICS |                 |                                                              |     |     |      |

|--------------------------------------------------|-----------------|--------------------------------------------------------------|-----|-----|------|

| Test                                             | Symbol          | Conditions<br>-55°C ≤TA≤+125°C<br>Unless Otherwise Specified | Min | Max | Unit |

| Input to Output Propagation<br>Delay             | t <sub>PD</sub> | V <sub>CC</sub> = 4.5 - 5.5V                                 |     | 80  | ns   |

| Chip Enable Delay<br>ENABLE to OUTPUT            | $t_{CE}$        | V <sub>CC</sub> = 4.5 - 5.5V                                 |     | 50  | ns   |

| Chip Disable Delay<br>ENABLE to OUTPUT           | t <sub>CD</sub> | V <sub>CC</sub> = 4.5 - 5.5V                                 |     | 50  | ns   |

#### **Ordering Information**

| Part Number      | Package (Mil-Std-1835)         | Generic         |

|------------------|--------------------------------|-----------------|

| QP82S100/B3A-MIL | CQCC1-N28 (LCC)                | 82S100 – PLS100 |

| QP82S100/BXA-MIL | GDIP1-T28 CDIP2-T28 (DIP)      | 82S100 – PLS100 |

| QP82S100/BYA-MIL | GDFP2-F28 CDFP3-F28 (FLATPACK) | 82S100 – PLS100 |

QP Semiconductor supports Source Control Drawing (SCD), and custom package development for this product family.

#### Notes:

Package outline information and specifications are defined by Mil-Std-1835 package dimension requirements.

"-MIL" products manufactured by QP Semiconductor are compliant to the assembly, burn-in, test and quality conformance requirements of Test Methods 5004 & 5005 of Mil-Std-883 for Class B devices. This datasheet defines the electrical test requirements for the device(s).

The listed drawings, Mil-PRF-38535, Mil-Std-883 and Mil-Std-1835 are available online at http://www.dscc.dla.mil/

Additional information is available at our website <u>http://www.qpsemi.com</u>

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for FPGA - Field Programmable Gate Array category:

Click to view products by E2v manufacturer:

Other Similar products are found below :

5AGXBA5D4F27I5N 5AGXMA3D4F27I3N 5CEFA7F27C6N 5CGTFD7D5F27I7N EP1C4F400C7N EP1S25F672I7 EP1SGX25DF672I6N EP2C50F672C8N EP2S30F672C5 EP2S60F672C5N EP4CGX110DF27C8N EP4CGX150DF27I7N EP4CGX50DF27I7N EP4CGX75DF27I7N LAMX0640C-3FTN256E LFE2-12E-6QN208I LFE2-20E-6FN484I LFE2-68E-6FN256I LFEC1E-3QN208C LFXP6C-3QN208CACD PLUS16L87N PLUS16R67N PLUS20L87N PLUS20R87N LCMX02280C-4FTN324I LFXP15-C-4F388C LFXP2-8E-6FT256I 5AGTMC3D3F27I3N 5AGXBA5D6F27C6N 5AGXMA5D6F27C6N 5CGXBC4C6F27C7N EP2C70F672C8N EP2S15F672C3N EP4CGX110DF27I7N QP82S100/BXA LCMX0640C-3FT256CAHW LFE2-6E-5TN144I LFSC3GA40E-7FFA1020C LFXP2-8E-6M132IAEJ LFE2M50SE-6F484I9A LFE3-70EA-8F672C LFSC3GA25E-7FFA1020C LFSC3GA40E-5FFA1020C LFSC3GA40E-6FFA1020I LFSCM3GA40EP1-5FFA1020C LFSCM3GA40EP1-6FFA1020C LFXP10C-5F388CA1370 LFXP2-5E-5M132I LFXP2-8E-6M132CAEJ 5962-9154507MXA