Rev. 1 Issued: 21-Oct-13

# Datasheet EC19D01 (Preliminary)

## **Revision History**

| Rev | Date        | Comments                 |

|-----|-------------|--------------------------|

| 1   | 21-Oct-2013 | Initial document release |

|     |             |                          |

|     |             |                          |

|     |             |                          |

## **Disclaimer and copyright notice**

Information in this document, including URL references, is subject to change without notice.

THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

All liability, including liability for infringement of any proprietary rights, relating to use of information in this document is disclaimed.

No licenses express or implied, by estoppels or otherwise, to any intellectual property rights are granted herein.

- WiSmart<sup>™</sup> is a trademark owned by eConais inc

- WiCReal<sup>™</sup> is a trademark owned by eConais inc

- Wi-Fi<sup>™</sup> is a trademark owned by Wi-Fi Alliance, U.S.A.

- Exynos, Exynos4210, FlexOneNAND, and OneNAND are trademarks of Samsung Electronics.

- ARM, Jazelle, TrustZone, and Thumb are registered trademarks of ARM Limited. Cortex, ETM, ETB, Coresight, ISA, and Neon are trademarks of ARM Limited.

- Java is a trademark of Sun Microsystems, Inc.

- SD is a registered trademark of Toshiba Corporation.

- MMC and eMMC are trademarks of MultiMediaCard Association.

- JTAG is a registered trademark of JTAG Technologies, Inc.

- Synopsys is a registered trademark of Synopsys, Inc.

- I2S is a trademark of Phillips Electronics.

- I2C is a trademark of Phillips Semiconductor Corp.

- MIPI and Slimbus are registered trademarks of the Mobile Industry Processor Interface (MIPI) Alliance

All other trade names, trademarks and registered trademarks are property of their respective owners

Copyright ©2013 eConais

## **Table of Contents**

| Revi | isior | History1                                           |

|------|-------|----------------------------------------------------|

| Disc | laim  | er and copyright notice2                           |

| Tab  | le of | Contents3                                          |

| 1    | Мо    | dule Handling Guide5                               |

| 2    | List  | of Acronyms                                        |

| 3    | Dev   | vice details, block diagram and schematics7        |

| 4    | Eleo  | ctrical Data10                                     |

| 4.   | .1    | Absolute Maximum Ratings10                         |

| 4.   | .2    | Recommended Operating Conditions                   |

| 4.   | .3    | Current Consumption                                |

| 4.   | .4    | RF Performance                                     |

| 4.   | .5    | Channel Frequencies                                |

| 4.   | .6    | Receiver Performance                               |

| 4.   | .7    | Receiver sensitivity12                             |

| 4.   | .8    | Transmitter Performance                            |

| 4.   | .9    | Output Power vs. Supply Voltage13                  |

| 4.   | .10   | Output Power vs. Temperature14                     |

| 5    | I/0   | Characteristics                                    |

| 5.   | .1    | SDIO timing characteristics15                      |

| 5.   | .2    | SPI timing characteristics                         |

| 5.   | .3    | Digital I/O pad17                                  |

| 5.   | .4    | Protection digital pins                            |

| 5.   | .5    | Shutdown                                           |

| 6    | PIN   | Configuration19                                    |

| 6.   | .1    | Device Pin Out                                     |

| 6.   | .2    | Pin assignment21                                   |

| 6.   | .3    | Pin Functions and Configurations21                 |

| 7    | Me    | chanical dimensions, footprint24                   |

| 8    | Lay   | out considerations25                               |

| 8.   | .1    | DC-DC converter25                                  |

| REV  | .1, 2 | 21-Oct-13 ©eConais, Proprietary and Confidential 3 |

| 9 Reference Design                                   |

|------------------------------------------------------|

| 10 Reflow profile27                                  |

| 11 Device Operation Description                      |

| 11.1 WLAN Radio28                                    |

| 11.1.1 WLAN RF Receiver28                            |

| 11.1.2 RF Transmitter                                |

| 11.2 WLAN Baseband and MAC                           |

| 11.2.1 Operational Modes                             |

| 11.3 Power ON Sequence with external 1.5 Volt Supply |

| 11.3.1 Shutdown Sequence                             |

| 11.3.2 Interfaces                                    |

| 11.3.3 Memory                                        |

| 11.3.4 Bluetooth Coexistence                         |

| 11.4 Audio Subsystem                                 |

| 11.4.1 I2S/PCM                                       |

| 11.4.2 Class D                                       |

| 11.5 Power Management                                |

| 11.5.1 IO Supply                                     |

| 11.5.2 Ground                                        |

| 11.6 Clock Management                                |

| 11.6.1 High Frequency Clock, HFC                     |

| 11.6.2 External reference requirements               |

| 11.6.3 Low Frequency Clock, LFC35                    |

| 11.7 WLAN Firmware                                   |

| 11.7.1 Features                                      |

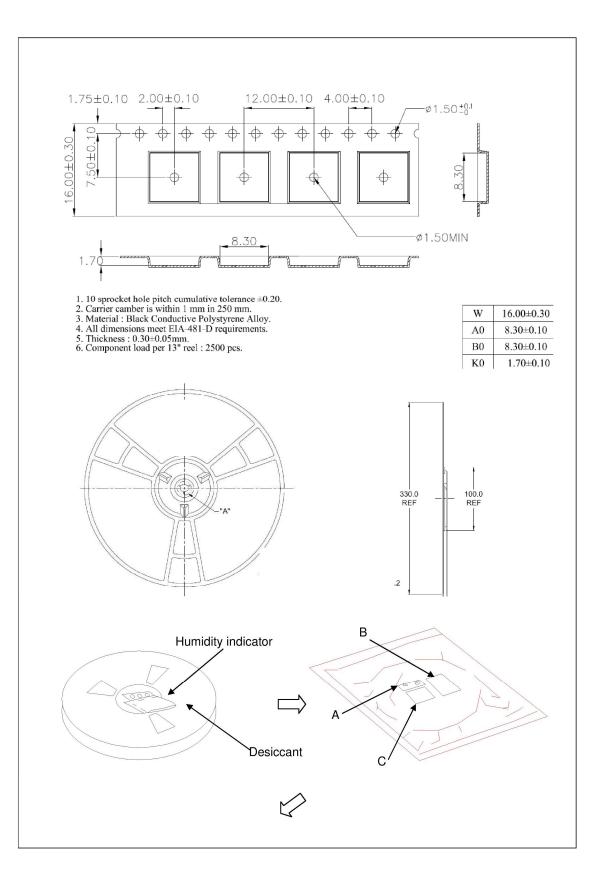

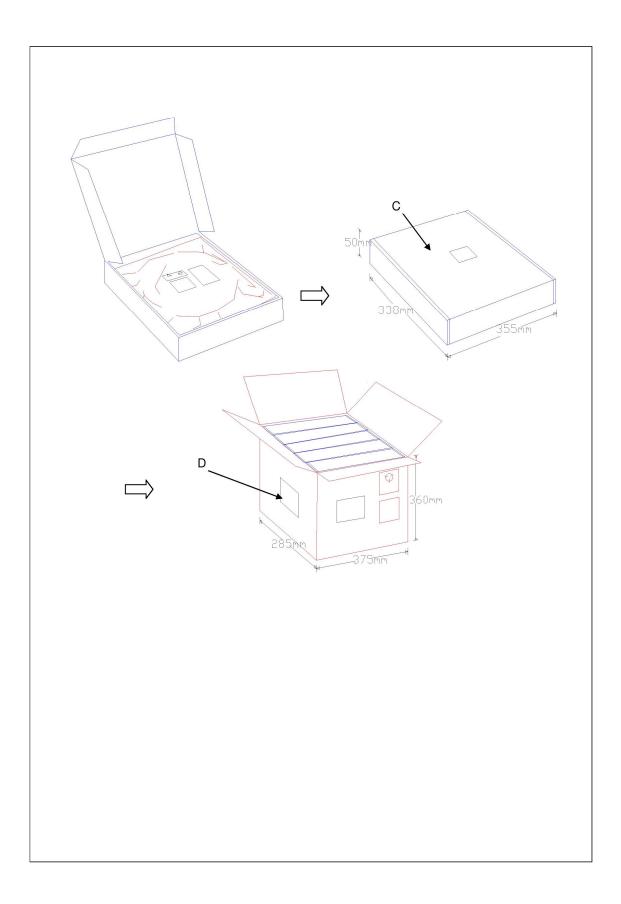

| 12 Pick and Place and Packing information            |

| 13 Contact Information41                             |

## 1 Module Handling Guide

#### Precaution against Electrostatic Discharge

When using semiconductor devices, ensure that the environment is protected against static electricity:

- 1. Wear antistatic clothes and use earth band.

- 2. All objects that are in direct contact with devices must be made up of materials that do not produce static electricity.

- 3. Ensure that the equipment and work table are earthed.

- 4. Use ionizer to remove electron charge.

#### Contamination

Do not use semiconductor products in an environment exposed to dust or dirt adhesion.

#### **Temperature/Humidity**

Semiconductor devices are sensitive to:

- Environment

- Temperature

- Humidity

High temperature or humidity deteriorates the characteristics of semiconductor devices. Therefore, do not store or use semiconductor devices in such conditions.

#### Mechanical Shock

Do not to apply excessive mechanical shock or force on semiconductor devices.

#### Chemical

Do not expose semiconductor devices to chemicals because exposure to chemicals leads to reactions that deteriorate the characteristics of the devices.

#### Light Protection

In non- Epoxy Molding Compound (EMC) package, do not expose semiconductor IC to bright light. Exposure to bright light causes malfunctioning of the devices. However, a few special products that utilize light or with security functions are exempted from this guide.

#### Radioactive, Cosmic and X-ray

Radioactive substances, cosmic ray, or X-ray may influence semiconductor devices. These substances or rays may cause a soft error during a device operation. Therefore, ensure to shield the semiconductor devices under environment that may be exposed to radioactive substances, cosmic ray, or X-ray.

#### EMS (Electromagnetic Susceptibility)

Strong electromagnetic wave or magnetic field may affect the characteristic of semiconductor devices during the operation under insufficient PCB circuit design for Electromagnetic Susceptibility (EMS).

## 2 List of Acronyms

| Acronym                                                                                 | Description                                                   |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------|

| <b>802.11</b> ™                                                                         | WLAN specification defined by a working group within the IEEE |

| АР                                                                                      | WLAN Access Point                                             |

| BOM                                                                                     | Bill of Material                                              |

| BPSK                                                                                    | Binary Phase Shift Keying                                     |

| BT                                                                                      | Bluetooth                                                     |

| ССК                                                                                     | Complementary Code Keying                                     |

| СОВ                                                                                     | Chip on Board                                                 |

| DPSK                                                                                    | Differential Phase Shift Keying                               |

| DQPSK                                                                                   | Differential Quadrature Phase Shift Keying                    |

| DTIM1                                                                                   | Delivery Traffic Indication Message – 100ms beacon interval   |

| DTIM3                                                                                   | Delivery Traffic Indication Message – 300ms beacon interval   |

| FW                                                                                      | Firmware                                                      |

| HFC                                                                                     | WLAN, High Frequency Clock, 26 or 40 MHz                      |

| I/O                                                                                     | Input/Output                                                  |

| IC                                                                                      | Integrated Circuit                                            |

| LDO                                                                                     | Low-dropout regulator                                         |

| LFC                                                                                     | Low Frequency Clock, 32.768 kHz Real Time Clock               |

| LNA                                                                                     | Low Noise Amplifier                                           |

| MIB                                                                                     | Management Information Base                                   |

| MIMO                                                                                    | Multiple-In, Multiple-Out                                     |

| OFDM                                                                                    | Orthogonal Frequency Division Multiplexing                    |

| PA                                                                                      | Power Amplifier                                               |

| PLL                                                                                     | Phase Locked Loop                                             |

| POR                                                                                     | Power On Reset                                                |

| QAM                                                                                     | Quadrature Amplitude Modulation                               |

| QPSK                                                                                    | Quadrature phase-shift keying                                 |

| RAM                                                                                     | Random Access Memory                                          |

| RF                                                                                      | Radio Frequency                                               |

| <b>RoHS</b> The Restriction of Hazardous Substances in Electrical and Electronic Equipm |                                                               |

|                                                                                         | Directive (2002/95/EC)                                        |

| ROM                                                                                     | Read Only Memory                                              |

| STBC                                                                                    | Space-Time Block Coding                                       |

| UART                                                                                    | Universal Asynchronous Receiver Transmitter                   |

| VCO                                                                                     | Voltage Controlled Oscillator                                 |

## 3 Device details, block diagram and schematics

#### **General Description**

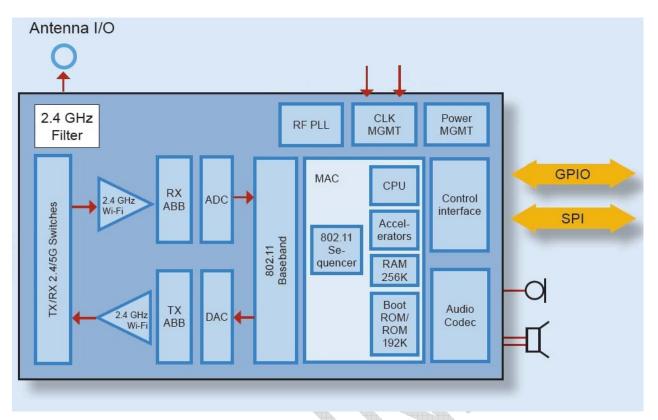

EC19D01 is an 802.11bgn WLAN module including RF frontend circuitry, baseband, MAC, Clock Management and Power Management for direct battery operation. It also incorporates the balun and low pass filter and a 40MHz crystal. EC19D01 supports Bluetooth coexistence with the major Bluetooth chips available on the market.

EC19D01 is designed for direct PCB attach without under-fill and a low BOM cost for the total solution.

#### **Key Features**

- Compliant with 802.11b/g/n

- Supports direct attach to Li-Ion battery. Supports VBAT 2.7-4.5V with on-module power management.

- Class D stereo headphone drivers

- Digital Microphone input

- I2S and PCM external codec interface

- On-module IP stack and web server

- WiFi Direct Group Owner (GO and Client)

- Support for 802.11n up to MCS7, SGI 0.4us, STBC (Rx), L-SIG TXOP Protection, PSMP.

- BT ePTA/PTA Co-existence support.

- 802.1x, 802.11i, WEP, WPA, WPA2 (PSK/Enterprise, EAP), WPS security support, WAPI HW accelerator support.

- 802.11e including WMM/WMM-PS QoS support.

- 802.11d/h support

- Support of SDIO 2.0 (52 MHz) host interface.

- TX output power pre-calibrated in production.

- High integration level

- External clock reference 26, 38.4, 40, 52 MHz support (tolerance +/- 20 ppm).

- Integrated TX/RX switches

- Fully integrated power management (DCDC).

- Support external Power Management.

- Integrated PA and LNA.

Device details, block diagram and schematics WiSmart™ EC19D0x Datasheet eC@∩OIS

#### Figure 1: EC19D0x Block diagram

## Device details, block diagram and schematics

## WiSmart

©eConais, Proprietary and Confidential

## 4 Electrical Data

#### 4.1 Absolute Maximum Ratings

The absolute maximum ratings specify the values beyond which the device may be damaged permanently. Exposure to absolute maximum ratings conditions for extended periods of time may affect reliability. Each condition is applied with all other values kept within the recommended operating condition.

|                  |                                                                |                   | VIIIA                       |      |

|------------------|----------------------------------------------------------------|-------------------|-----------------------------|------|

| Symbol           | Parameter                                                      | Min.              | Max.                        | Unit |

| VBAT             | Direct battery connect Supply voltage                          | 0                 | 4.8 <sup>1</sup>            | V    |

| VDD_DCDC         | Digital Supply voltage                                         | -0.3              |                             | V    |

| VDD_IO, VDD_SDIO | Supply voltage I/O                                             | -0.3              | 3.6                         | V    |

| Vin              | Input voltage on any digital pin                               | -0.3              | VDD_IO+0.3,<br>VDD_SDIO+0.3 | V    |

| Vssdiff          | Maximum voltage difference between different types of Vss pins | $\langle \rangle$ |                             | V    |

| Tstg             | Storage temperature                                            | -65               | 125                         | °C   |

|                  |                                                                |                   |                             |      |

Table 1:Absolute maximum ratings

<sup>1</sup>: 5.5V acceptable for duration less than 2 ms

<sup>2</sup>: No Pb (Solder 40sec); Refer to the IPC/JEDEC J-STD-020C, July 2004.

#### 4.2 Recommended Operating Conditions

The recommended operating conditions specify the values in which region the device is operational meeting specification

| Symbol           | Parameter                                                                                                                                                                    | Min. | Тур. | Max. | Unit |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Tamb             | Operating ambient temperature                                                                                                                                                | -30  |      | 70   | °C   |

| VBAT             | Direct battery connect Supply voltage.<br>- All specs guaranteed.<br>- All specs guaranteed with output power<br>back-off<br>- Device functional with reduced<br>performance | 2.7  | 3.6  | 4.5  | V    |

| VDD_DCDC,        | Supply voltage                                                                                                                                                               |      | 1.5  |      | V    |

| VDD_IO, VDD_SDIO | I/O supply voltage                                                                                                                                                           | 1.62 |      | 3.6  | V    |

Table 2:Recommended operating condition

#### 4.3 Current Consumption

VBAT current consumption. RF power, Pout, is referenced to IC interface.

Conditions: VBAT= 3.6 V, Tamb = 25°C, internal DCDC for 1.5 Volt

| Mode                 | Condition                                | Min | Тур  | Max | Unit |

|----------------------|------------------------------------------|-----|------|-----|------|

| Transmit 802.11b     | CCK 11Mbps, Pout=21 dBm                  |     | 220  |     | mA   |

| Transmit 802.11g     | OFDM 54 Mbps, Pout=18 dBm                |     | 215  |     | mA   |

| Transmit 802.11n     | OFDM 72.2 Mbps, Pout=17 dBm (2.4<br>GHz) |     | 185  |     | mA   |

| Receive 802.11b      | Normal mode – Max sensitivity            |     | 40   |     | mA   |

| Receive<br>802.11g/n | Normal mode – Max sensitivity            |     | 42   |     | mA   |

| P0 (Sleep Mode)      |                                          |     | 39   |     | μA   |

| Power Save<br>DTIM1  | Beacon interval 100ms                    |     | 0.8  |     | mA   |

| Power Save<br>DTIM3  | Beacon interval 300ms                    |     | 0.11 |     | mA   |

| Shutdown             |                                          |     | 10   |     | μA   |

Table 3: Typical power consumption values in different modes

#### 4.4 RF Performance

All data is referenced to the IC interface.

#### 4.5 Channel Frequencies

Supported 2.4 GHz channels and frequencies according to IEEE802.11 b/g/n standard.

| Channel no. | Frequency MHz | Note | Channel no. | Frequency MHz | Note |

|-------------|---------------|------|-------------|---------------|------|

| 1           | 2412          |      | 8           | 2447          |      |

| 2           | 2417          |      | 9           | 2452          |      |

| 3           | 2422          |      | 10          | 2457          |      |

| 4           | 2427          |      | 11          | 2462          |      |

| 5           | 2432          |      | 12          | 2467          |      |

| 6           | 2437          |      | 13          | 2472          |      |

| 7           | 2442          |      | 14          | 2484          |      |

Table 4: Channel and frequency table

## 4.6 Receiver Performance

Conditions: VBAT = 3.6 V. Tamb = 25°C.

| Mode                | Condition                                       | Min | Тур | Max | Unit |

|---------------------|-------------------------------------------------|-----|-----|-----|------|

| Input level         | All data rates, CCK FER < 8%, OFDM<br>PER < 10% |     |     | -20 | dBm  |

|                     | 11 Mbit/s, Pwanted = - 70 dBm                   | 35  |     |     | dB   |

| Adjacent<br>channel | 6 Mbit/s, Pwanted = - 79 dBm                    | 16  |     |     | dB   |

| rejection           | 54 Mbit/s, Pwanted = - 62 dBm                   | -1  | X   |     | dB   |

|                     | 72.2 Mbit/s, Pwanted = - 64 dBm                 | -2  |     |     | dB   |

## Table 5: Receiver performance

## 4.7 Receiver sensitivity

Conditions: VBAT = 3.6 V, Tamb = 25°C.

| Band   | Standard                 | Rate | Rate      |                  | Conditions                     |     | odule Po<br>ecificati |     | Units |

|--------|--------------------------|------|-----------|------------------|--------------------------------|-----|-----------------------|-----|-------|

|        |                          | Mbps |           |                  |                                | Min | Тур                   | Max |       |

|        |                          | 1    |           | DSSS             |                                |     | -99,5                 |     | dBm   |

|        |                          | 2    |           | DSSS             |                                |     | -97,0                 |     | dBm   |

|        |                          | 5,5  |           | ССК              |                                |     | -94,5                 |     | dBm   |

|        | 4                        | 11   |           | ССК              | @ FER<8%, 1024                 |     | -91,0                 |     | dBm   |

|        | 8/                       | 6    | BP        | SK 1/2           | bytes<br>Full Operating        |     | -95,0                 |     | dBm   |

|        | 802.11b/g                | 9    | BP        | SK 3/4           | Full Operating<br>Temperature; |     | -93,5                 |     | dBm   |

|        | 02.1                     | 12   | QF        | PSK 1/2          | Full Battery Voltage           |     | -92,0                 |     | dBm   |

|        | 80                       | 18   | QF        | PSK 3/4          | Range;                         |     | -90,0                 |     | dBm   |

| Ŷ      |                          | 24   | 16QAM 1/2 |                  | Load Z : 50 Ohms;              |     | -87,5                 |     | dBm   |

| 2.4GHz |                          | 36   | 16C       | AM 3/4           |                                |     | -84,0                 |     | dBm   |

|        |                          | 48   | 64C       | AM 2/3           |                                |     | -79,5                 |     | dBm   |

|        |                          | 54   | 64C       | AM 3/4           |                                |     | -78,0                 |     | dBm   |

|        |                          | 7,2  | MCS0      | BPSK 1/2         | @ PER<10%, 4096                |     | -93,5                 |     | dBm   |

|        | 20<br>1)                 | 14,4 | MCS1      | QPSK 1/2         | bytes                          |     | -90,5                 |     | dBm   |

|        | 11n (OFDM,<br>MHz, Nss = | 21,7 | MCS2      | QPSK 3/4         | Full Operating                 |     | -88,5                 |     | dBm   |

|        | .1n (OFDM,<br>MHz, Nss = | 28,9 | MCS3      | 16QAM 1/2        | Temperature;                   |     | -85,5                 |     | dBm   |

|        | n (C<br>Hz,              | 43,3 | MCS4      | 16QAM 3/4        | Full Battery Voltage           |     | -82,0                 |     | dBm   |

|        | $\Xi$                    | 57,8 | MCS5      | 64QAM 2/3        | Range;                         |     | -78,0                 |     | dBm   |

|        |                          | 65   | MCS6      | 64QAM 3/4        | Load Z : 50 Ohms;              |     | -76,5                 |     | dBm   |

| R      | EV.1, 29-Sep             | -13  | ©eCc      | onais, Proprieta | ry and Confidential            |     |                       | -   | L2    |

## WiSmart<sup>™</sup> EC19D0x Datasheet eC@∩QIS

|  |                     | 72,2      | MCS7     | 64QAM 5/6       |                                                                           | -74,5 | dBm   |     |

|--|---------------------|-----------|----------|-----------------|---------------------------------------------------------------------------|-------|-------|-----|

|  |                     | 15        | MCS0     | BPSK 1/2        |                                                                           | -90,5 | dBm   |     |

|  | MHz,                | 월 30 MCS1 | QPSK 1/2 | @ PER<10%, 4096 | -87,5                                                                     | dBm   |       |     |

|  |                     | 45        | MCS2     | QPSK 3/4        | bytes<br>Full Operating<br>Temperature;<br>Full Battery Voltage<br>Range; | ,     | -85,5 | dBm |

|  |                     | 60        | MCS3     | 16QAM 1/2       |                                                                           | -82,5 | dBm   |     |

|  | FDN<br>Nss          | 90        | MCS4     | 16QAM 3/4       |                                                                           | -79,0 | dBm   |     |

|  | 11n (OFDM,<br>Nss = | 120       | MCS5     | 64QAM 2/3       |                                                                           | -75,0 | dBm   |     |

|  |                     | 135       | MCS6     | 64QAM 3/4       | Load Z : 50 Ohms;                                                         | -73,5 | dBm   |     |

|  | -                   | 150       | MCS7     | 64QAM 5/6       |                                                                           | -71,5 | dBm   |     |

**Table 6:**2.4 GHz Sensitivity (minimum input level)

#### 4.8 Transmitter Performance

Conditions: VBAT = 3.6 V. Tamb = 25°C.

Fulfilled spectrum mask according to the IEEE 802.11b/g/n specification, calibrated.

| Band  | Std   | BW | MCS        | Conditions                                                                                                 | Output Power (2.4 GHz)<br>Mosule Port Specification |     |     |       | EVM   |       |

|-------|-------|----|------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|-------|-------|-------|

| Dallu |       |    |            |                                                                                                            | Min                                                 | Тур | Max | Units | Max   | Units |

|       |       |    | DSSS/CCK   |                                                                                                            |                                                     | 21  |     | dBm   | 15.0  | %     |

|       |       |    | BPSK 1/2   |                                                                                                            |                                                     | 21  |     | dBm   | 13,00 | %     |

|       | 11b/g |    | BPSK 3/4   | Requirements<br>at T=25<br>degrees and<br>VBAT >= 3.3V;<br>Load Z: 50<br>Ohms;<br>Meeting<br>spectral mask |                                                     | 21  |     | dBm   | 13,00 | %     |

|       |       | 20 | QPSK 1/2   |                                                                                                            |                                                     | 21  |     | dBm   | 13,00 | %     |

|       |       |    | QPSK 3/4 🥄 |                                                                                                            |                                                     | 21  |     | dBm   | 13,00 | %     |

| GHz   |       |    | 16QAM 1/2  |                                                                                                            |                                                     | 20  |     | dBm   | 9,00  | %     |

| 2.4 G |       |    | 16QAM 3/4  |                                                                                                            |                                                     | 19  |     | dBm   | 7,00  | %     |

| 5.    |       |    | 64QAM 2/3  |                                                                                                            |                                                     | 18  |     | dBm   | 5.6   | %     |

|       |       |    | 64QAM 3/4  |                                                                                                            |                                                     | 18  |     | dBm   | 5.6   | %     |

|       | 11n   | 20 | MCS7       | and regulatory requirements                                                                                |                                                     | 17  |     | dBm   | 4.0   | %     |

Table 7: Coding Rate dependent Output power vs. EVM for 2.4 GHz

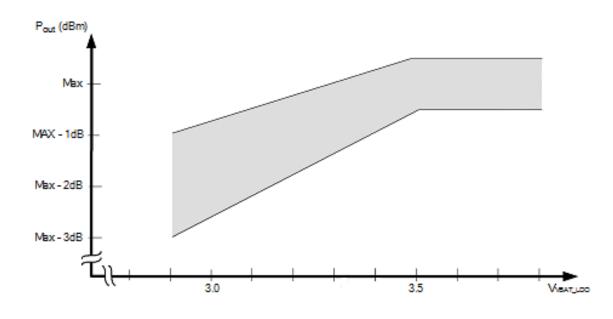

## 4.9 Output Power vs. Supply Voltage

The figure below shows the allowed output power variations dependent of the VBAT\_LDO supply voltage. This is controlled by FW and MIB settings.

Figure 2: Output Power vs. Supply Voltage

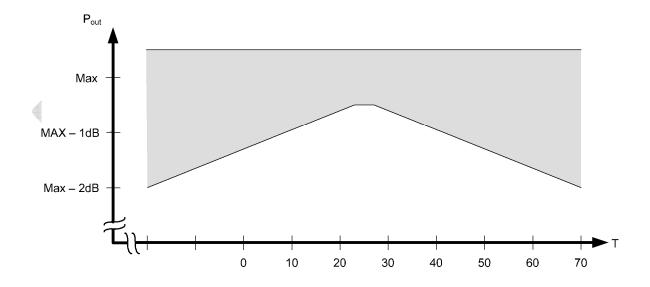

#### 4.10 Output Power vs. Temperature

The figure below shows the allowed variation of the output power versus temperature. The output power is controlled by FW in order to maximize the performance of the circuit without jeopardizing quality and function. Tested with the radio mounted on a PCB with the thermal resistance Tj-pin=40 deg/W.

Figure 3: Output Power vs. Temperature

## 5 I/O Characteristics

#### 5.1 SDIO timing characteristics

The SDIO/SPI-interface can run in three different modes, SDIO 1-bit mode, SDIO 4-bit mode or in SDIO/SPI 1-bit mode. Timing can be set for Default speed mode or High speed mode.

SDIO 1-bit Default speed mode is selected at Power On Reset. The host can change mode by sending the corresponding command over the SDIO-interface.

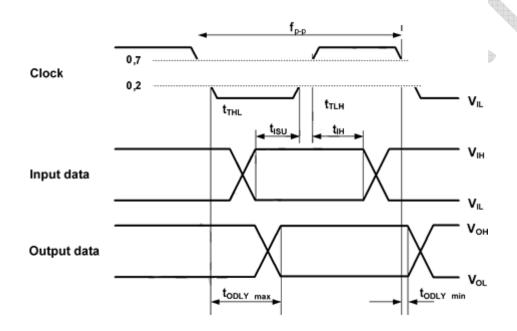

The Default mode is showed in Figure 1) and Table 8). For the high speed mode see Figure 2) and Table 9). Condition: VDDIO\_SDIO= 1.7 - 3.6 V, Tamb=  $-20 - +70^{\circ}\text{C}$

Figure 4: SDIO/SPI timing diagram (default mode)

| Parameter         | Symbol               | Min | Max | Unit | Comment |

|-------------------|----------------------|-----|-----|------|---------|

| Input set-up time | t <sub>ISU</sub>     | 5   |     | ns   |         |

| Input hold time   | t <sub>iH</sub>      | 5   |     | ns   |         |

| Clock fall time   | t <sub>THL</sub>     |     | 10  | ns   |         |

| Clock rise time   | t <sub>TLH</sub>     |     | 10  | ns   |         |

| Output delay time | t <sub>odly</sub>    | 0   | 14  | ns   |         |

| Clock Frequency   | f <sub>sdio_cl</sub> |     | 25  | MHz  |         |

**Table 8:** SDIO timing parameter values (default mode)

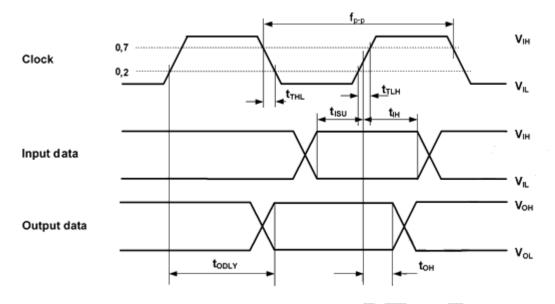

Figure 5: SDIO timing diagram (high speed mode)

| Parameter         | Symbol               | Min | Max | Unit | Comment |

|-------------------|----------------------|-----|-----|------|---------|

| Input set-up time | t <sub>ISU</sub>     | 6   |     | ns   |         |

| Input hold time   | t <sub>iH</sub>      | 2   |     | ns   |         |

| Clock fall time   | t <sub>тнL</sub>     |     | 3   | ns   |         |

| Clock rise time   | t <sub>TLH</sub>     |     | 3   | ns   |         |

| Output delay time | t <sub>ODLY</sub>    | 2.5 | 14  | ns   |         |

| Output hold time  | t <sub>он</sub>      | 2.5 |     | ns   |         |

| Clock Frequency   | f <sub>sdio_cl</sub> |     | 52  | MHz  |         |

Table 9: SDIO timing diagram (high speed mode)

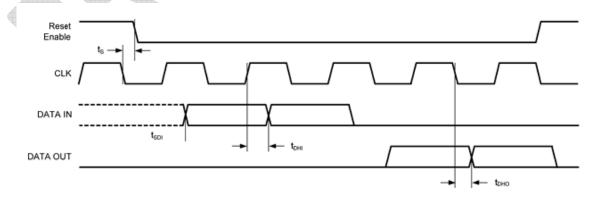

#### 5.2 SPI timing characteristics

The SPI interface is intended to be used for application specific purposes, like communicating with an external memory, display or codec. Note that this interface cannot be used as a host interface. The timing characteristics are shown in Figure 6 and Table 10.

Figure 6: SPI timing diagram

| Parameter           | Symbol           | Min | Max | Unit | Comment |

|---------------------|------------------|-----|-----|------|---------|

| SPI Clock Frequency | f <sub>SPI</sub> |     | 10  | MHz  |         |

| Enable delay time   | ts               |     | 15  | ns   |         |

| Input setup time    | t <sub>sDI</sub> | 11  |     | ns   |         |

| Input hold time     | t <sub>DHI</sub> | 0   |     | ns   |         |

| Output delay time   | t <sub>DHO</sub> |     | 15  | ns   |         |

Table 10: SPI timing parameter values

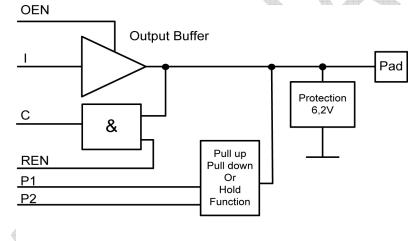

## 5.3 Digital I/O pad

The digital I/O pads are of type none inverting three-state driver/receiver. The I/O pin functional schematic is shown in Figure 7. It includes an LVCMOS/LVTTL compatible input buffer and an output buffer with enable/disable control inputs. It also includes a programmable Pull up, Pull down and Hold-function. When the I/O is neither driven by the internal nor by an external circuitry, the hold function holds the latest state of the I/O. This is the case for example when Shutdown is activated, then the Hold function is set and the Output Enable-signal is set low

Figure 7: Functional schematic of the I/O pad

The hold-function resists a change of state on the pad. Therefore, an external driver that feeds the pad must overpower the hold function. The needed drive strength is low, typically less than 1 uA. The hold function resists a change of state on the pad only at the first part of the transition. In the last part, it assists the change of the state.

In addition to the above Digital I/O-pads there are five Output Only pads, SW1, SW2, SW3, LNA\_GAIN1 and LNA\_GAIN2. These I/O-cells consists of a non-inverting driver. They are connected to the VDD\_IO-domain. During SHUTDOWN SW1 is set high and SW2 is set low.

| Parameter                  | Symbol          | Min                  | Тур | Max                  | Unit | Comment                    |

|----------------------------|-----------------|----------------------|-----|----------------------|------|----------------------------|

| Input low voltage          | VIL             | -0.3                 |     | 0.3* V <sub>IO</sub> | V    |                            |

| Input high voltage         | V <sub>IH</sub> | 0.7* V <sub>IO</sub> |     | V <sub>IO</sub> +0.3 | V    |                            |

| Input leakage current      | ١ <sub>١L</sub> |                      |     | 50                   | nA   | IO in High Z state         |

| Output sink current,       |                 | 4                    | 7   |                      | mA   | V <sub>IO</sub> =1.8 Volt, |

| V <sub>OL</sub> = 0.4 Volt | I <sub>OL</sub> | 5                    | 8   |                      | mA   | V <sub>IO</sub> =3.3 Volt  |

| Output drive current,                       | I                 | 4    | 6   |     | mA | V <sub>IO</sub> =1.8 Volt, |

|---------------------------------------------|-------------------|------|-----|-----|----|----------------------------|

| V <sub>OH</sub> = V <sub>IO</sub> -0.4 Volt | I <sub>ОН</sub>   | 5    | 7   |     | mA | V <sub>IO</sub> =3.3 Volt  |

| Weak Pull Down current                      | I                 | 15   | 37  | 97  |    | V <sub>IO</sub> =1.8 Volt  |

| Weak Pull Down current                      | I <sub>PD</sub>   | 17   | 43  | 162 | uA | V <sub>IO</sub> =3.3 Volt  |

| Week Bull Lin current                       | 1                 | 17   | 30  | 54  |    | V <sub>IO</sub> =1.8 Volt  |

| Weak Pull Up current                        | I <sub>PU</sub>   | 39   | 65  | 105 | uA | V <sub>IO</sub> =3.3 Volt  |

| VDD_IO, VDD_SDIO                            | V <sub>IO</sub>   | 1.62 |     | 3.6 | V  |                            |

| Input pin capacitance                       | C <sub>IP</sub>   | 0    | 5.5 |     | рF |                            |

| Output sink current,<br>Output Only pads,   | I <sub>OLOO</sub> |      | TBD |     | mA | V <sub>IO</sub> =1.8 Volt  |

| $V_{OL} = 0.4$ Volt                         | 10100             |      | 3   |     | mA | V <sub>IO</sub> =3.3 Volt  |

| Output drive current,<br>Output Only pads,  | I <sub>оноо</sub> |      | TBD |     | mA | V <sub>IO</sub> =1.8 Volt, |

| $V_{OH} = V_{IO} - 0.4$ Volt                | UHUU              |      | 3   |     | mA | V <sub>IO</sub> =3.3 Volt  |

#### 5.4 Protection digital pins

All digital pins are protected against over-voltage with a "snap-back" circuit connected between the pad and GND. The "snap-back" voltage is 6.2 V and the holding voltage is 6 V. This provides a satisfying protection against over voltages and ESD.

Also there is a diode included to protect against reversed voltages.

#### 5.5 Shutdown

The Shutdown input uses an analog pad type A1 with a high impedance resistor in series with a diode to GND. Set the pin low or open to put NRX901 in shutdown mode.

Pull the pin high to initialize EC19D01. If a pull up resistor is used, connect it to VBAT, recommended value is 1Mohm.

REV.1, 29-Sep-13

## 6 PIN Configuration

## 6.1 Device Pin Out

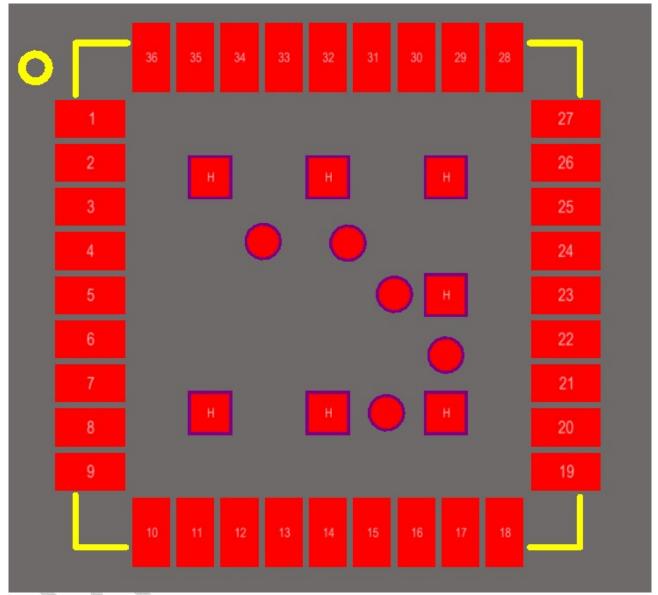

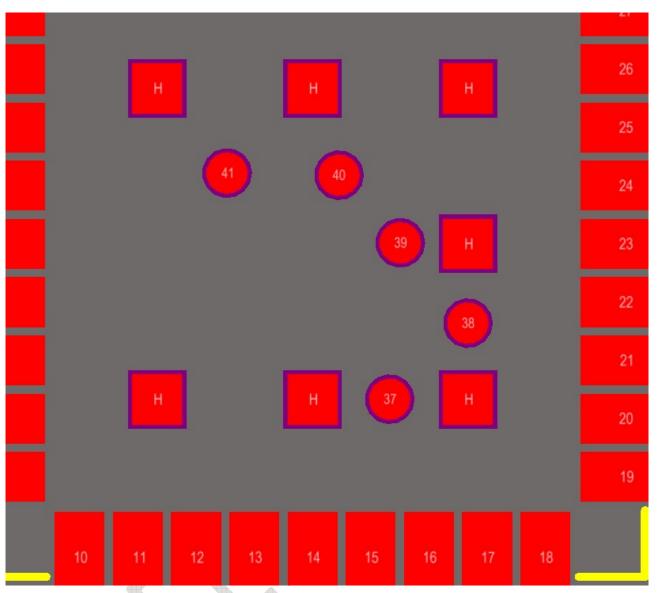

Figure 8: EC19D01 package perimeter pin-out (top view)

## WiSmart<sup>™</sup> EC19D0x Datasheet eC@∩OIS

Figure 9: EC19D01 package central area pin out (top view)

#### 6.2 Pin assignment

| Assignment | Pin #                                                                                                                                       | Assignment                                                                                                                                                                                                                                                                                                  | Pin #                                                                                                                                                                                          | Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO0      | 16                                                                                                                                          | SDIO_CLK                                                                                                                                                                                                                                                                                                    | 31                                                                                                                                                                                             | SPI_EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GPIO1      | 17                                                                                                                                          | SDIO_DAT1                                                                                                                                                                                                                                                                                                   | 32                                                                                                                                                                                             | SPI_CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GPIO2      | 18                                                                                                                                          | SDIO_DAT0                                                                                                                                                                                                                                                                                                   | 33                                                                                                                                                                                             | SPI_DIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GPIO3      | 19                                                                                                                                          | SDIO_DAT3                                                                                                                                                                                                                                                                                                   | 34                                                                                                                                                                                             | SPI_DOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VDD_LDO    | 20                                                                                                                                          | SDIO_DAT2                                                                                                                                                                                                                                                                                                   | 35                                                                                                                                                                                             | WLAN_EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND        | 21                                                                                                                                          | SDIO_CMD                                                                                                                                                                                                                                                                                                    | 36                                                                                                                                                                                             | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GPIO4      | 22                                                                                                                                          | GND                                                                                                                                                                                                                                                                                                         | 37                                                                                                                                                                                             | HFC_EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GPIO5      | 23                                                                                                                                          | CLK_IN                                                                                                                                                                                                                                                                                                      | 38                                                                                                                                                                                             | ICE_TCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VBAT       | 24                                                                                                                                          | GND                                                                                                                                                                                                                                                                                                         | 39                                                                                                                                                                                             | ICE_TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND        | 25                                                                                                                                          | GND                                                                                                                                                                                                                                                                                                         | 40                                                                                                                                                                                             | ICE_TDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VDD_DCDC   | 26                                                                                                                                          | ANTENNA                                                                                                                                                                                                                                                                                                     | 41                                                                                                                                                                                             | ICE_TMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DCDC_OUT   | 27                                                                                                                                          | GND                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDD_IO     | 28                                                                                                                                          | GND                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDD_SDIO   | 29                                                                                                                                          | GPIO6                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| GND        | 30                                                                                                                                          | GND                                                                                                                                                                                                                                                                                                         | Н                                                                                                                                                                                              | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | GPIO0<br>GPIO1<br>GPIO2<br>GPIO3<br>VDD_LDO<br>GND<br>GPIO4<br>GPIO5<br>VBAT<br>GND<br>VDD_DCDC<br>DCDC_OUT<br>VDD_IO<br>VDD_IO<br>VDD_SDIO | GPIO0       16         GPIO1       17         GPIO2       18         GPIO3       19         VDD_LDO       20         GND       21         GPIO4       22         GPIO5       23         VBAT       24         GND_DCDC       26         DCDC_OUT       27         VDD_IO       28         VDD_SDIO       29 | GPIO016SDIO_CLKGPIO117SDIO_DAT1GPIO218SDIO_DAT0GPIO319SDIO_DAT3VDD_LDO20SDIO_DAT2GND21SDIO_CMDGPIO422GNDGPIO523CLK_INVBAT24GNDGND25GNDVDD_DCDC26ANTENNADCDC_OUT27GNDVDD_IO28GNDVDD_SDIO29GPIO6 | GPIO0         16         SDIO_CLK         31           GPIO1         17         SDIO_DAT1         32           GPIO2         18         SDIO_DAT0         33           GPIO3         19         SDIO_DAT3         34           VDD_LDO         20         SDIO_DAT2         35           GND         21         SDIO_CMD         36           GPIO4         22         GND         37           GPIO5         23         CLK_IN         38           VBAT         24         GND         39           GND         25         GND         40           VDD_DCDC         26         ANTENNA         41           DCDC_OUT         27         GND         50           VDD_IO         28         GND         50           VDD_SDIO         29         GPIO6         50 |

Table 11: Pin assignment list

## 6.3 Pin Functions and Configurations

| Pin Name | Pin | Description                                                                                       |     | Pin<br>state<br>in<br>Shutdo<br>wn | Power Domain |  |  |  |  |  |

|----------|-----|---------------------------------------------------------------------------------------------------|-----|------------------------------------|--------------|--|--|--|--|--|

| Power    |     |                                                                                                   |     |                                    |              |  |  |  |  |  |

| VBAT     | 9   | Main supply (battery) for DC/DC converter                                                         | S   | ON                                 | VBAT         |  |  |  |  |  |

| VDD_IO   | 13  | I/O supply voltage for GPIO1-GPIO6.                                                               | S   | ON                                 | VDD_IO       |  |  |  |  |  |

| VDD_SDIO | 14  | I/O supply voltage for SDIO, ICE and SPI-<br>buses                                                | S   | ON                                 | VDD_SDIO     |  |  |  |  |  |

| DCDC_OUT | 12  | DC/DC converter pulsing output.                                                                   | S   | OFF                                | VBAT         |  |  |  |  |  |

| VDD_DCDC | 11  | DC/DC Voltage Sense. Connect to filtered side of inductor or to external VDD if DCDC is not used. | S   | OFF                                | VDD_DCDC     |  |  |  |  |  |

| VDD_LDO  | 5   | 1.8 – 3.6 Volt LDO Output. For use as I/O-<br>voltage.                                            | S   | OFF                                | VBAT         |  |  |  |  |  |

|          |     | Ground                                                                                            |     |                                    |              |  |  |  |  |  |

|          | 6   |                                                                                                   | GND | GND                                |              |  |  |  |  |  |

|          | 10  |                                                                                                   | GND | GND                                |              |  |  |  |  |  |

|          | 15  |                                                                                                   | GND | GND                                |              |  |  |  |  |  |

|          | 22  |                                                                                                   | GND | GND                                |              |  |  |  |  |  |

|          | 24  |                                                                                                   | GND | GND                                |              |  |  |  |  |  |

|          | 25  |                                                                                                   | GND | GND                                |              |  |  |  |  |  |

|          | 27  |                                                                                                   | GND | GND                                |              |  |  |  |  |  |

|          | 28  |                                                                                                   | GND | GND                                |              |  |  |  |  |  |

REV.1, 29-Sep-13

|           | 30 |                                                  | GND  | GND      |          |

|-----------|----|--------------------------------------------------|------|----------|----------|

|           | 36 |                                                  | GND  | GND      |          |

|           |    | SDIO/Host Interface                              | GITE | CITE     |          |

| SDIO CLK  | 16 | SDIO Clock, SDIO/SPI CLK                         | I/O  | Hold     | VDD_SDIO |

| SDIO DATO | 18 | SDIO Data 0, SDIO/SPI MISO, UART RxD             | I/O  | Hold     | VDD SDIO |

| SDIO DAT1 | 17 | SDIO Data 1, SDIO/SPI IRQ, UART CTS              | I/O  | Hold     | VDD SDIO |

| SDIO_DAT2 | 20 | SDIO Data 2, SDIO/SPI N/A, UART RTS              | I/O  | Hold     | VDD_SDIO |

| SDIO_DAT3 | 19 | SDIO Data 3, SDIO/SPI CS, UART TxD               | I/O  | Hold     | VDD_SDIO |

| SDIO_CMD  | 21 | SDIO Command, SDIO/SPI MOSI                      | I/O  | Hold 🥼   | VDD_SDIO |

|           |    | SPI Interface                                    |      |          |          |

| SPI_EN    | 31 | SPI Enable output. Active low                    | I/O  | Hold     | VDD_SDIO |

| SPI_DIN   | 33 | SPI Data input pin                               | I/O  | Hold     | VDD_SDIO |

| SPI_DOUT  | 34 | SPI Data output pin                              | I/O  | Hold     | VDD_SDIO |

| SPI_CLK   | 32 | SPI_Clock output                                 | I/O  | Hold     | VDD_SDIO |

|           |    | General Interfaces                               |      |          |          |

| HFC_EN    | 37 | External clock request                           | I/O  | Low      | VDD_SDIO |

| GPIO0     | 1  | Host Wakeup or General purpose I/O               | 1/0  | Hold     | VDD_SDIO |

| WLAN_EN   | 35 | Shutdown input, Active low                       | А    | LOW      | VBAT     |

|           |    | Debug/Test Interface                             |      |          |          |

| ICE_TDO   | 39 | ICE Test Data Output                             | 1/0  | Hold     | VDD_SDIO |

| ICE_TDI   | 40 | ICE Test Data Input                              | I/O  | Hold     | VDD_SDIO |

| ICE_TCK   | 38 | ICE Test CLK                                     | I/O  | Hold     | VDD_SDIO |

| ICE_TMS   | 41 | ICE Test Mode Select                             | I/O  | Hold     | VDD_SDIO |

|           |    | General Purpose I/O                              |      |          |          |

|           |    | General purpose I/O 1                            |      |          |          |

| GPIO1     | 2  | Class D Head Phone Driver Left P                 | I/O  | Hold     | VDD_IO   |

| 01101     | 2  | AUD_CLK Audio I2S and PCM clock                  | 170  |          | 100_10   |

|           |    | General purpose I/O 2                            |      |          |          |

|           |    | Class D Head Phone Driver Left N                 | 1-   |          |          |

| GPIO2     | 3  | AUD_LR/SYNC Audio I2S LR or PCM                  | I/O  | Hold     | VDD_IO   |

|           |    | Sync .                                           |      |          |          |

| 60102     |    | General purpose I/O 3                            | 1/0  | 11 - Lal |          |

| GPIO3     | 4  | Class D Head Phone Driver Right P                | I/O  | Hold     | VDD_IO   |

|           |    | AUD_DOUT Audio Data Out<br>General purpose I/O 4 |      |          |          |

| GPIO4     | 7  | Class D Head Phone Driver Right N                | I/O  | Hold     | VDD_IO   |

| 0104      |    | AUD DIN Audio Data In                            | 1/0  | noiu     | VDD_10   |

|           |    | General purpose I/O 5                            |      |          |          |

| GPIO5     | 8  | Digital Microphone Clock Output                  | I/O  | Hold     | VDD_IO   |

|           |    | General purpose I/O 6                            |      |          |          |

| GPIO6     | 29 | Digital Microphone PDM Data Input                | I/O  | Hold     | VDD_IO   |

|           |    | Clock                                            |      |          |          |

| CLK_IN    | 23 | External Clock input                             | А    |          | VBAT     |

| CLK_IN    | 23 | External Clock Input                             | A    |          | VRAI     |

**Table 12:** Pin functions and configurations for EC19D01

Pad types Legend:

| Α    | Analog                                      |

|------|---------------------------------------------|

| GND  | Ground                                      |

| I .  | Input                                       |

| 0    | Output                                      |

| RF   | Radio Frequency driver, receiver            |

| S    | Supply Voltage                              |

| Hold | Week keeper state, keeps the previous state |

|      |                                             |

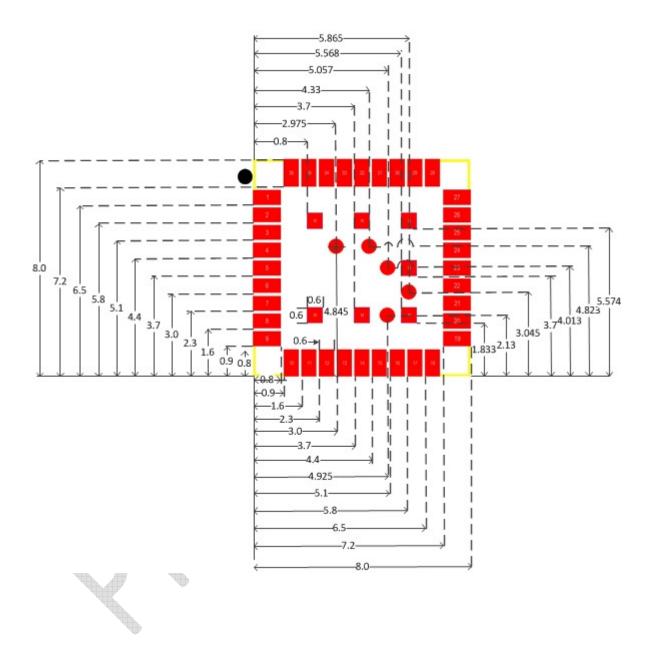

## 7 Mechanical dimensions, footprint

## 8 Layout considerations

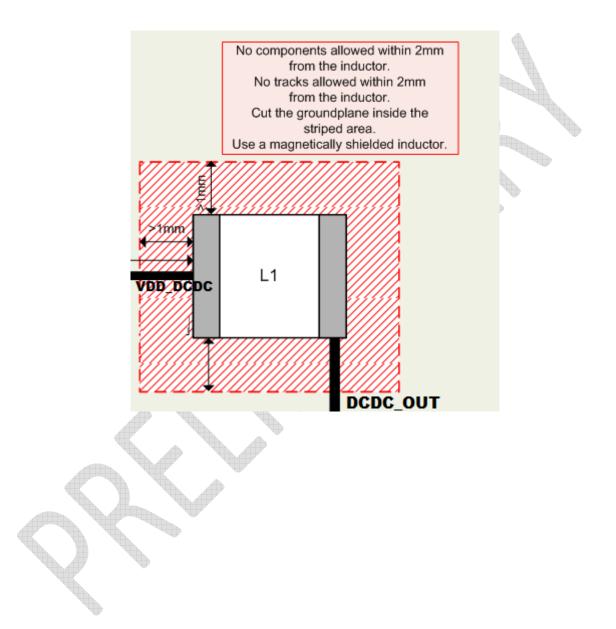

#### 8.1 DC-DC converter

For the inductor connected to the VDD\_DCDC and DCDC\_OUT (pins 11 & 12 respectively) please follow the reference design below:

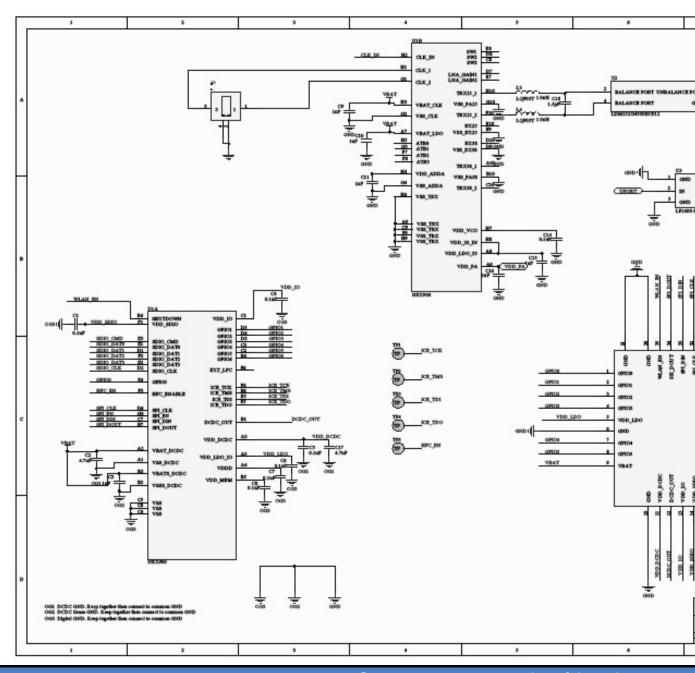

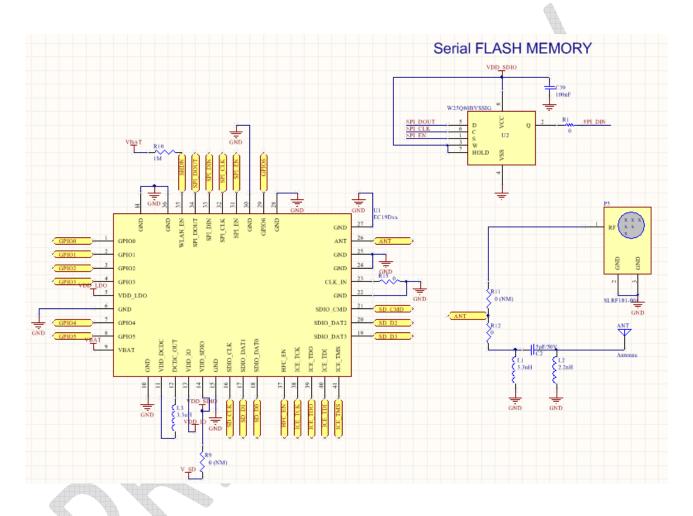

## 9 Reference Design

The EC19D01 should have some external components in order to function properly:

- Inductor for DC-DC functionality

- Serial Flash

- Antenna / Matching circuit

Inductor's characteristics: 3.3uH 20% LQM2HP (Murata LQM2HPN3R3MG0) Recommended Flash Chips for storing patch and application code:

| Vendor                | Product            | Size              |  |

|-----------------------|--------------------|-------------------|--|

| STMicroelectronics    | STM25P40           | 4 Mbit            |  |

| Numonyx               | M25P80<br>M25P16   | 8 Mbit<br>16 Mbit |  |

| Atmel                 | AT45DB011B         | 1 Mbit            |  |

| Eon Silicon Solutions | EN25Q40<br>EN25Q80 | 4 Mbit<br>8 Mbit  |  |

| Winbond               | W25Q80             | 8 Mbit            |  |

REV.1, 29-Sep-13

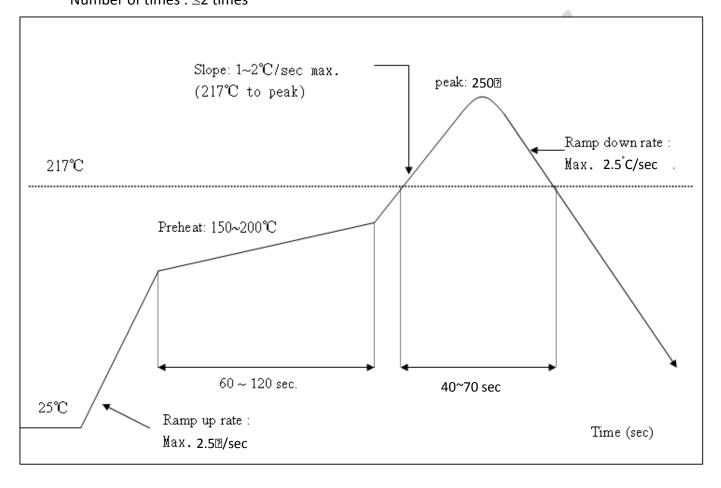

## **10** Reflow profile

Refer to IPC/JEDEC standard. Peak Temperature : <250°C Number of times : ≤2 times

REV.1, 29-Sep-13

## **11 Device Operation Description**

#### 11.1 WLAN Radio

EC19D01 contains a WLAN Radio. It is a fully integrated RF transceiver with a Zero-IF architecture, operating in the 2.4-2.5 GHz ISM band. The design uses differential RF-input/output to optimize the RF performance. A Transmit/Receive switch is integrated on module preventing signal leakage into the receiver path during RF transmit time.

#### 11.1.1 WLAN RF Receiver

The receive section is designed to work well in a radio noisy environment such as a cellular phone. The RF signal is received and amplified by the on module WLAN LNA.

In addition a separate Receive input is available to enable the use of an external RF front end.

#### 11.1.2 RF Transmitter

The EC19D01 WLAN Radio provides an on module high efficient RF Power amplifier to minimize overall solution cost. Output Power can be trimmed to meet IEEE standard requirements. Trim values can be stored in an on module fuse memory which will be available throughout the application life time.

The ISM band radio also includes a low output power mode, in the 0 dBm range, for lower power consumption in close range etc.

#### 11.2 WLAN Baseband and MAC

#### **11.2.1 Operational Modes**

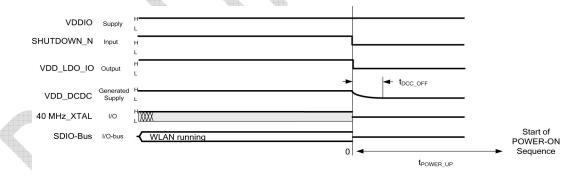

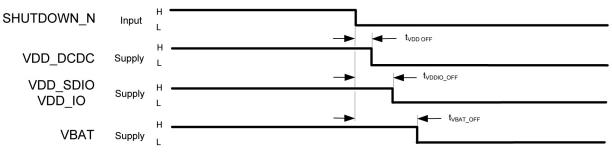

#### 11.2.1.1 ShutDown

EC19D01 can use two shutdown modes HW SHUTDOWN and Soft SHUTDOWN.

#### 11.2.1.1.1 HW Shutdown

SHUTDOWN\_N shall be set high during normal operation. Pulling the SHUTDOWN\_N pin low sets EC19D01 in HW Shutdown mode. This turns OFF most parts of the circuit and minimizes current consumption. All I/O interface pins keep their states with the I/O hold function when in Shutdown mode. In shutdown, keep the VBAT\_DCDC, VBATS\_DCDC, VBAT\_LDO and VBAT\_CLK supplies ON (the battery). EC19D01 will automatically turn OFF all generated power supplies, incl VDD\_DCDC.

If the internal DCDC-converter for 1.5 Volt is not used, the externally supplied 1.5 Volt should be turned OFF while in HW Shutdown mode.

To end HW Shutdown mode set SHUTDOWN\_N pin high and reload FW and MIB.

#### 11.2.1.1.2 Soft Shutdown

Soft Shutdown is a FW function that stops all functions and sets HW in a deep sleep state. All I/Opins are set to predefined states, FW defaults, or according to a Soft Shutdown MIB-setting. During Soft Shutdown keep all power supplies ON and pin SHUTDOWN\_N high.

To end Soft Shutdown mode toggle the SHUTDOWN\_N pin low-high and reload FW and MIB.

#### 11.2.1.2 Power Save

Power save is an energy saving mode where EC19D01 is only listening at regular intervals for the beacons transmitted from an access point and is set in sleep mode in between. During sleep mode, FW patches are kept in RAM with all not needed functions turned off. Since the receive time is very short compared to the listening interval the average current consumption is reduced significantly.

The timing of the listening interval is based on the LFC (32 kHz) clock. The LFC is implemented internally but can also be fed externally.

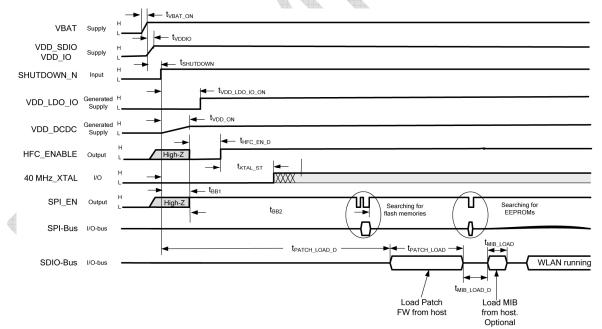

#### 11.2.1.3 Power ON Sequence internal DCDC

Figure below shows a typical Power ON sequence used for the EC1901 module. VDD, 1.5 V is supplied from the internal DCDC converter and a 40MHz crystal is used. The FW patches and the MIB data are loaded from an external flash memory connected to the SPI interface. See timing diagram Figure 6) and Table 16).

VBAT should not be applied with a faster rise time than according to table below.

VDDIO should be turned ON after VBAT or at the same time as VBAT if rise time of VDDIO is the same or slower than VBAT rise time.

Figure 10: Timing diagram Power ON sequence

| Parameter                | Symbol                     | Min | Тур  | Max | Unit | Comment              |

|--------------------------|----------------------------|-----|------|-----|------|----------------------|