The EPC9004 development board showcases the EPC1012 eGaN FET. Although the electrical performance surpasses that for traditional Si devices, their relatively smaller size does magnify the thermal management requirements. The EPC9004 is intended for bench evaluation with low ambient temperature and convection cooling. The addition of heat-sinking and forced air cooling can significantly increase the current rating of these devices, but care must be taken to not exceed the absolute maximum die temperature of 125°C.

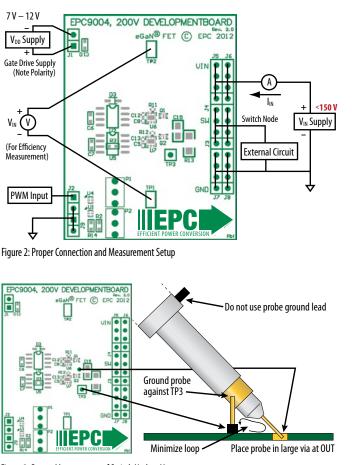

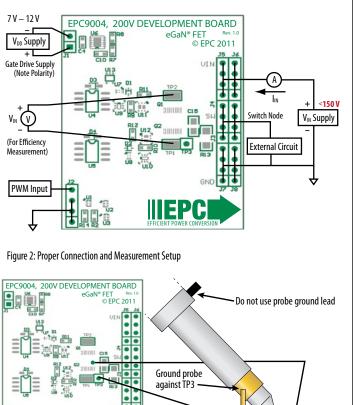

NOTE. When measuring the high frequency content switch node (OUT), care must be taken to avoid long ground leads. Measure the switch node (OUT) by placing the oscilloscope probe tip through the large via on the switch node (designed for this purpose) and grounding the probe directly across the GND terminals provided. See Figure 3 for proper scope probe technique.

9. For shutdown, please follow steps in reverse.

THERMAL CONSIDERATIONS

- 8. Once operational, adjust the bus voltage and load PWM control within the operating range and observe the output switching behavior, efficiency and other parameters.

- 7. Turn on the controller / PWM input source and probe switching node to see switching operation.

- 6. Turn on the bus voltage to the required value (do not exceed the absolute maximum voltage of 200 V on  $V_{out}$ ).

- 5. Turn on the gate drive supply make sure the supply is between 7 V and 12 V range.

- 4. With power off, connect the input PWM control signal to PWM (J2, Pin-1) and ground return to any of the remaining J2 pins.

- 3. With power off, connect the gate drive input to +VDD (J1, Pin-1) and ground return to -VDD (J1, Pin-2).

- 2. With power off, connect the switch node of the half bridge OUT (J3, J4) to your circuit as required.

- 1. With power off, connect the input power supply bus to +VIN (J5, J6) and ground / return to -VIN (J7, J8).

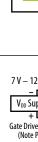

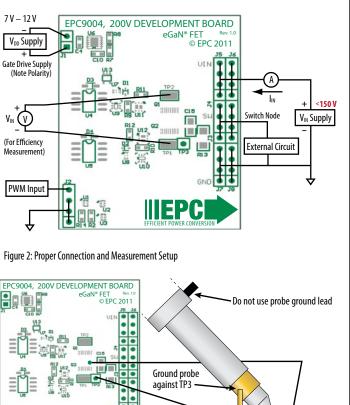

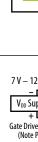

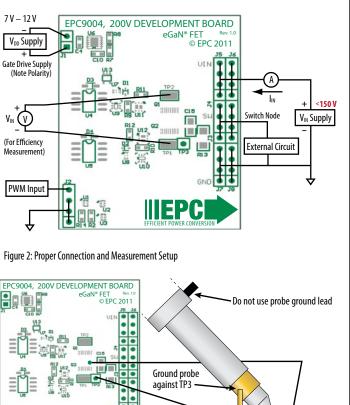

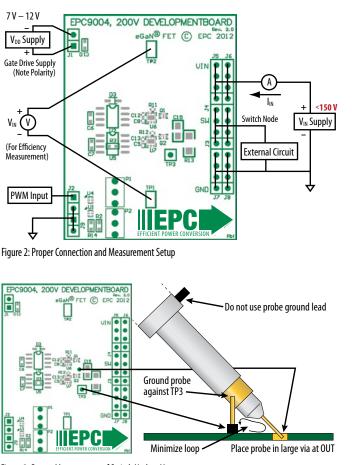

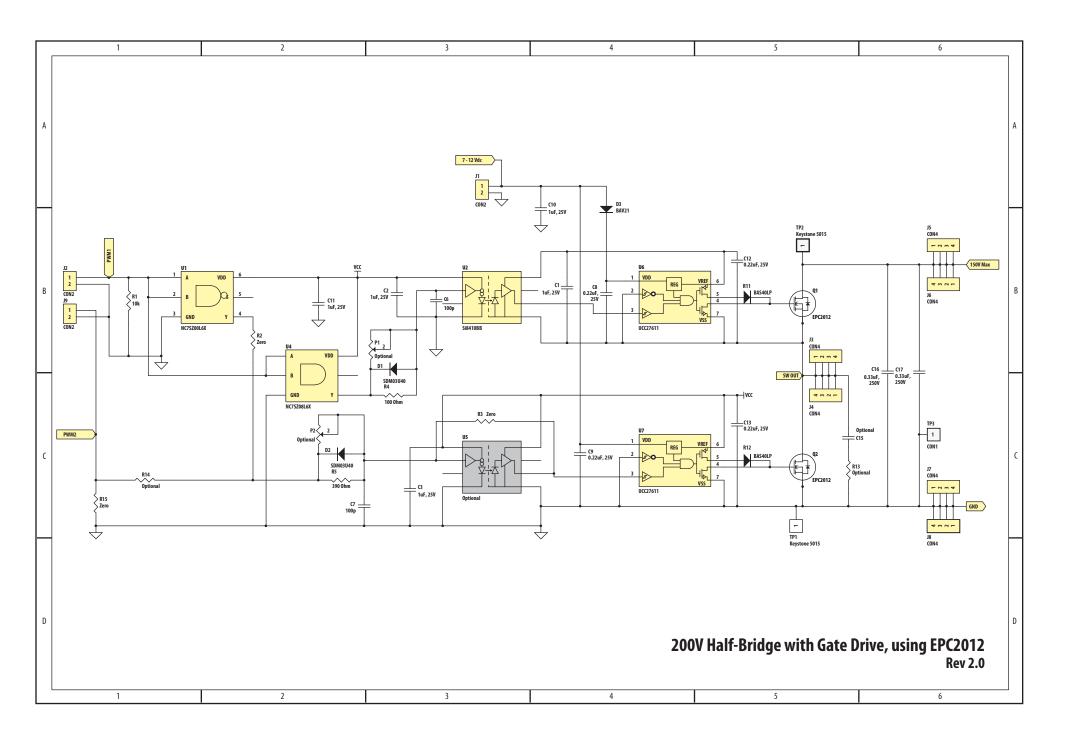

Development board EPC9004 is easy to set up to evaluate the performance of the EPC1012 eGaN FET. Refer to Figure 2 for proper connect and measurement setup and follow the procedure below:

## **Quick Start Procedure**

<u>moɔ.oɔ-ɔqə.www</u>

.l siven in Higure 1. ficiency calculation. A complete block diagram of the circuit is probe points to facilitate simple waveform measurement and eflayout for optimal switching performance. There are also various by basic components and contains all critical components and Texas Instruments UCC2701 gate drivers as well as supply and

should be read in conjunction with this quick start guide. teacheet available from EPC at www.epc-co.com. The datasheet For more information on the EPC2012 eGaNFET please refer to the

easily connected into any existing converter. cluding all the critical components on a single board that can be to simplify the evaluation process of the EPC2012 eGaN FET by ineffect transistor (FET). The purpose of this development board is blaft (<sup>©</sup>Maturing the EPC2012 enhancement mode (eGaW<sup>®</sup>) field age, 2 A maximum output current, half bridge with onboard gate The EPC9004 development board is a 200 V maximum device volt-

two EPC2012 eGaN FET in a half bridge configuration using two The EPC9004 development board is 2.1 x "2 si breod thempedoleveb 4009D43 eff.

| 108WJS           | A PARAMARAN                            | SNOILIANOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | NIW  | XAM | STINU |

|------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|

| ۸ <sup>DD</sup>  | Gate Drive Input Supply Range          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | L    | ۲۱  | ٨     |

| ۸ <sup>NI</sup>  | Politage Range Manuel Volitage Range   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 051 | ٨     |

| $\Lambda_{out}$  | Switch Node Output Voltage             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 500 | ٨     |

| I <sub>out</sub> | Switch Node Output Current             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 5*  | A     |

| Λ                | blodrovdT operilov tuggi pipe LMWG     | ,4giH' tuqn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.5  | 9   | ٨     |

| ۸ <sup>bMW</sup> | PWM Logic Input Voltage Threshold      | ,moŋ, Indul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0    | 5.1 | ٨     |

|                  | dtbiW əslu9 tuqnl ətət2 'dpiH' muminiM | ror > 9mit llst bns عان MW9V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 001  |     | su    |

|                  | dtbiW seluf tuqn1 stat2 'woJ' muminiM  | 2001 sind the subsection of the second s | #005 |     | su    |

# Dependent on time needed to 'refresh' high side bootstrap supply voltage. usus nun semie con lausnes i funisitare es sociane se usus sus

### DESCRIPTION

# Quick Start Guide Development Board EPC9004

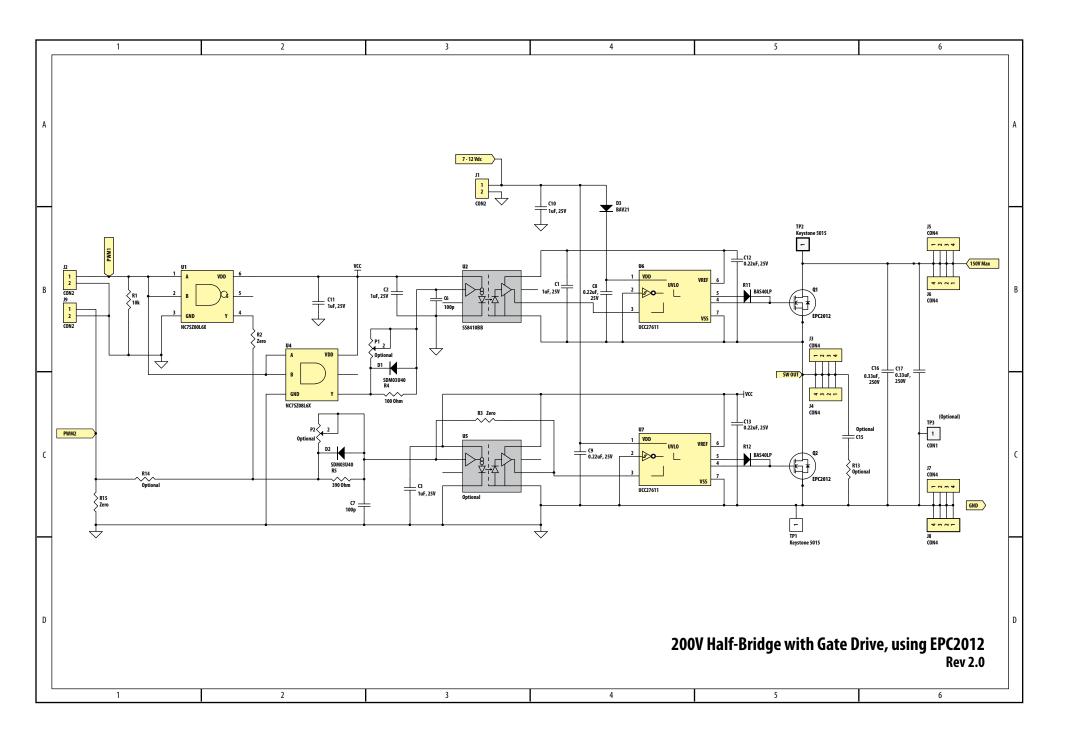

200 V Half-Bridge with Gate Drive, Using EPC2012

Half-Bridge with Bypass

**EFFICIENT POWER CONVERSION**

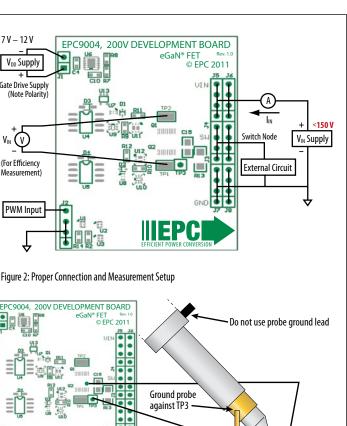

Figure 4: Waveforms for VIN = 150 V to 5 V/2 A (100kHz) Buck converter

CH1: VPWM Input voltage – CH2: (IOUT) Switch node current – CH4: (VOUT) Switch node voltage

PWM Enable Level Shift. Input Dead-time Adjust л ᅶ and Gate Drive

Gate Drive

Regulator

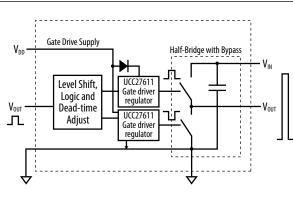

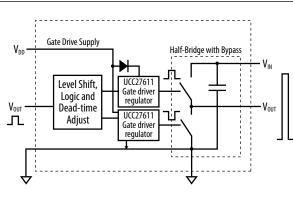

Figure 1: Block Diagram of EPC9004 Development Board

Gate Driv

Minimize loop

באר נפגפנאפג תופ נוסער פר שעא תושפי אורעסתר עסתכפי רס כעשעקפ צפוס כונכתונגא פעם צאפכועכפרוסעצי otration board Notificatio

moɔ.yəメipib.www EPC Products are distributed exclusively through Digi-Key.

moɔ.oɔ-ɔqø@pnɛsī.nandəis f258.8049.228+ :9lidoM *<b>FisA, <i>s***<b>SS** pnszi neddetż

renee.yawger@epc-co.com 8789.913.809.1+ :91idoM 2072.274.809.1+:9)ЩО WW Marketing Renee Yawger

<u>moɔ.oɔ-ɔq</u>ə.www

:su foefno)

Place probe in large via at OUT

moɔ.oɔ-ɔdə@pnənɔ.rəiəq 007.000.850.988+ :9lidoM FAE Support, Asia Peter Cheng

moo.oo-oq@nien.ysend 4242.978.934.1+:9lidoM 0fffce: +1.972.805.8585 **Froqqu2 3A7 Isdol Bhasy Vair**

Figure 3: Proper Measurement of Switch Node – OUT

The EPC9004 development board showcases the EPC1012 eGaN FET. Although the electrical performance surpasses that for traditional Si devices, their relatively smaller size does magnify the thermal management requirements. The EPC9004 is intended for bench evaluation with low ambient temperature and convection cooling. The addition of heat-sinking and forced air cooling can significantly increase the current rating of these devices, but care must be taken to not exceed the absolute maximum die temperature of 125°C.

NOTE. When measuring the high frequency content switch node (OUT), care must be taken to avoid long ground leads. Measure the switch node (OUT) by placing the oscilloscope probe tip through the large via on the switch node (designed for this purpose) and grounding the probe directly across the GND terminals provided. See Figure 3 for proper scope probe technique.

9. For shutdown, please follow steps in reverse.

THERMAL CONSIDERATIONS

- 8. Once operational, adjust the bus voltage and load PWM control within the operating range and observe the output switching behavior, efficiency and other parameters.

- 7. Turn on the controller / PWM input source and probe switching node to see switching operation.

- 6. Turn on the bus voltage to the required value (do not exceed the absolute maximum voltage of 200 V on  $V_{out}$ ).

- 5. Turn on the gate drive supply make sure the supply is between 7 V and 12 V range.

- 4. With power off, connect the input PWM control signal to PWM (J2, Pin-1) and ground return to any of the remaining J2 pins.

- 3. With power off, connect the gate drive input to +VDD (J1, Pin-1) and ground return to -VDD (J1, Pin-2).

- 2. With power off, connect the switch node of the half bridge OUT (J3, J4) to your circuit as required.

- 1. With power off, connect the input power supply bus to +VIN (J5, J6) and ground / return to -VIN (J7, J8).

Development board EPC9004 is easy to set up to evaluate the performance of the EPC1012 eGaN FET. Refer to Figure 2 for proper connect and measurement setup and follow the procedure below:

## **Quick Start Procedure**

<u>moɔ.oɔ-ɔqə.www</u>

.l siven in Higure 1. ficiency calculation. A complete block diagram of the circuit is probe points to facilitate simple waveform measurement and eflayout for optimal switching performance. There are also various by basic components and contains all critical components and Texas Instruments UCC2701 gate drivers as well as supply and

should be read in conjunction with this quick start guide. teacheet available from EPC at www.epc-co.com. The datasheet For more information on the EPC2012 eGaNFET please refer to the

easily connected into any existing converter. cluding all the critical components on a single board that can be to simplify the evaluation process of the EPC2012 eGaN FET by ineffect transistor (FET). The purpose of this development board is blaft (<sup>©</sup>Maturing the EPC2012 enhancement mode (eGaW<sup>®</sup>) field age, 2 A maximum output current, half bridge with onboard gate The EPC9004 development board is a 200 V maximum device volt-

two EPC2012 eGaN FET in a half bridge configuration using two The EPC9004 development board is 2.1 x "2 si breod thempedoleveb 4009D43 eff.

| 108WJS           | A PARAMATANA A PARAMANANA A PARAM | SNOILIANOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | NIW  | XAM | STINU |

|------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|

| ۸ <sup>DD</sup>  | Gate Drive Input Supply Range                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | L    | ۲۱  | ٨     |

| ۸ <sup>NI</sup>  | Politage Range Manuel Volitage Range                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 051 | ٨     |

| $\Lambda_{out}$  | Switch Node Output Voltage                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 500 | ٨     |

| I <sub>out</sub> | Switch Node Output Current                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 5*  | A     |

| Λ                | blodrovdT operilov tuggi pipo LMWG                                                                              | ,4giH' tuqn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.5  | 9   | ٨     |

| ۸ <sup>bMW</sup> | PWM Logic Input Voltage Threshold                                                                               | ,moŋ, Indul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0    | 5.1 | ٨     |

|                  | dtbiW əslu9 tuqnl ətət2 'dpiH' muminiM                                                                          | ror > 9mit llst bns عان MW9V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 001  |     | su    |

|                  | dtbiW seluf tuqn1 stat2 'woJ' muminiM                                                                           | 2001 sind the subsection of the second s | #005 |     | su    |

# Dependent on time needed to 'refresh' high side bootstrap supply voltage. usus nun sémice en l'ausphau éurissies es sasteres agus usus

### DESCRIPTION

# Quick Start Guide Development Board EPC9004

200 V Half-Bridge with Gate Drive, Using EPC2012

Half-Bridge with Bypass

**EFFICIENT POWER CONVERSION**

Figure 4: Waveforms for VIN = 150 V to 5 V/2 A (100kHz) Buck converter

CH1: VPWM Input voltage – CH2: (IOUT) Switch node current – CH4: (VOUT) Switch node voltage

PWM Enable Level Shift. Input Dead-time Adjust л ᅶ and Gate Drive

Gate Drive

Regulator

Figure 1: Block Diagram of EPC9004 Development Board

Gate Driv

Minimize loop

באר נפגפנאפג תופ נוסער פר שעא תושפי אורעסתר עסתכפי רס כעשעקפ צפוס כונכתונגא פעם צאפכועכפרוסעצי otration board Notificatio

moɔ.yəメipib.www EPC Products are distributed exclusively through Digi-Key.

moɔ.oɔ-ɔqø@pnɛsī.nandəis f258.8049.228+ :9lidoM *<b>FisA, <i>s***<b>SS** pnszi neddetż

renee.yawger@epc-co.com 8789.913.809.1+ :91idoM 2072.274.809.1+:9)ЩО WW Marketing Renee Yawger

<u>moɔ.oɔ-ɔq</u>ə.www

:su foefno)

Place probe in large via at OUT

moɔ.oɔ-ɔdə@pnənɔ.rəiəq 007.000.850.988+ :9lidoM FAE Support, Asia Peter Cheng

moo.oo-oq@nien.ysend 4242.978.934.1+:9lidoM 0fffce: +1.972.805.8585 **Froqqu2 3A7 Isdol Bhasy Vair**

Figure 3: Proper Measurement of Switch Node – OUT

The EPC9004 development board showcases the EPC2012 eGaN FET. Although the electrical performance surpasses that for traditional Si devices, their relatively smaller size does magnify the thermal management requirements. The EPC9004 is intended for bench evaluation with low ambient temperature and convection cooling. The addition of heat-sinking and forced air cooling can significantly increase the current rating of these devices, but care must be taken to not exceed the absolute maximum die temperature of 125°C.

NOTE. When measuring the high frequency content switch node (OUT), care must be taken to avoid long ground leads. Measure the switch node (OUT) by placing the oscilloscope probe tip through the large via on the switch node (designed for this purpose) and grounding the probe directly across the GND terminals provided. See Figure 3 for proper scope probe technique.

9. For shutdown, please follow steps in reverse.

THERMAL CONSIDERATIONS

- 8. Once operational, adjust the bus voltage and load PWM control within the operating range and observe the output switching behavior, efficiency and other parameters.

- 7. Turn on the controller / PWM input source and probe switching node to see switching operation.

- 6. Turn on the bus voltage to the required value (do not exceed the absolute maximum voltage of 200 V on  $V_{out}$ ).

- 5. Turn on the gate drive supply make sure the supply is between 7 V and 12 V range.

- 4. With power off, connect the input PWM control signal to PWM (J2, Pin-1) and ground return to any of the remaining J2 pins.

- 3. With power off, connect the gate drive input to  $+V_{DD}$  (J1, Pin-1) and ground return to  $-V_{DD}$  (J1, Pin-2).

- 2. With power off, connect the switch node of the half bridge  $V_{OUT}$  (J3, J4) to your circuit as required.

- 1. With power off, connect the input power supply bus to  $+V_{IN}$  (J5, J6) and ground / return to  $-V_{IN}$  (J7, J8).

Development board EPC9004 is easy to set up to evaluate the performance of the EPC2012 eGaN FET. Refer to Figure 2 for proper connect and measurement setup and follow the procedure below:

## **Quick Start Procedure**

<u>moɔ.oɔ-ɔqə.www</u>

.l siven in Higure 1. ficiency calculation. A complete block diagram of the circuit is probe points to facilitate simple waveform measurement and eflayout for optimal switching performance. There are also various by basic components and contains all critical components and Texas Instruments UCC2701 gate drivers as well as supply and

should be read in conjunction with this quick start guide. teacheet available from EPC at www.epc-co.com. The datasheet For more information on the EPC2012 eGaNFET please refer to the

easily connected into any existing converter. cluding all the critical components on a single board that can be to simplify the evaluation process of the EPC2012 eGaN FET by ineffect transistor (FET). The purpose of this development board is blaft (<sup>©</sup>Maturing the EPC2012 enhancement mode (eGaW<sup>®</sup>) field age, 2 A maximum output current, half bridge with onboard gate -Ihe EPC9004 development board is a 200 V maximum device volt-

two EPC2012 eGaN FET in a half bridge configuration using two The EPC9004 development board is 2.1 x "2 si breod thempedoleveb 4009D43 eff.

|                                        | dtbiW selu9 tuqnl stat2 'woJ' muminiM | 2001 > sn01 ≤ sin MW9V son01 > sin MW9V | #00S |     | su    |

|----------------------------------------|---------------------------------------|-----------------------------------------|------|-----|-------|

|                                        | dtbiW əslu9 tuqn ətst2 'dpiH' muminiM | nt son0٢ > عmit llst bus esin MWqV      | 001  |     | su    |

| WMd a                                  |                                       | ,moŋ, ֈnduj                             | 0    | ۶·۱ | ٨     |

| ۸ <sup>۵۸۸</sup>                       | PWM Logic Input Voltage Threshold     | յեր (H) մեր                             | 5.5  | 9   | ٨     |

| Ι                                      | Switch Node Output Current            |                                         |      | 5*  | А     |

| $\Lambda_{out}$                        | Switch Node Output Voltage            |                                         |      | 200 | ٨     |

| ۸ <sup>۱</sup>                         | əpneA əpetloV tuqnl suð               |                                         |      | 051 | ٨     |

| Λ <sup>DD</sup>                        | Gate Drive Input Supply Range         |                                         | L    | ۲۱  | ٨     |

| <b>IOBMYS</b>                          | ЯЭТЭМАЯАЧ                             | CONDITIONO                              | NIW  | XAM | STINU |

| ()°2.5 = AT) yremmu2 sonemrot i PaldeT |                                       |                                         |      |     |       |

# Dependent on time needed to 'refresh' high side bootstrap supply voltage. nun afinia engliauanha u fuunauus an malans agunu

### DESCRIPTION

# Quick Start Guide Development Board EPC9004

200 V Half-Bridge with Gate Drive, Using EPC2012

**EFFICIENT POWER CONVERSION**

Figure 4: Waveforms for  $V_{IN} = 150 \text{ V}$  to 5 V/2 A (100kHz) Buck converter

CH1: VPWM Input voltage – CH2: (Iour) Switch node current – CH4: (Vour) Switch node voltage

Figure 1: Block Diagram of EPC9004 Development Board

באר נפגפנאפג תופ נוסער פר שעא תושפי אורעסתר עסתכפי רס כעשעקפ צפוס כונכתונגא פעם צאפכועכפרוסעצי otteofitoN bysed nottents

moɔ.yəメipib.www EPC Products are distributed exclusively through Digi-Key.

moɔ.oɔ-ɔqø@pnɛsī.nandəis f258.8049.228+ :9lidoM *<b>FisA, <i>s***<b>SS** pnszi neddetč

renee.yawger@epc-co.com 8789.913.809.1+ :91idoM 2072.274.809.1+:9) то WW Marketing Renee Yawger

<u>moɔ.oɔ-ɔq</u>ə.www

:su foefno)

moɔ.oɔ-ɔdə@pnənɔ.rəiəq 007.000.850.988+ :9lidoM FAE Support, Asia Peter Cheng

moo.oo-oq\_@nien.ysend 4242.978.934.1+:9lidoM 0fffce: +1.972.805.8585 **Froqqu2 3A7 Isdol Bhasy Vair**

Figure 3: Proper Measurement of Switch Node  $- V_{OUT}$

The EPC9004 development board showcases the EPC2012 eGaN FET. Although the electrical performance surpasses that for traditional Si devices, their relatively smaller size does magnify the thermal management requirements. The EPC9004 is intended for bench evaluation with low ambient temperature and convection cooling. The addition of heat-sinking and forced air cooling can significantly increase the current rating of these devices, but care must be taken to not exceed the absolute maximum die temperature of 125°C.

NOTE. When measuring the high frequency content switch node (OUT), care must be taken to avoid long ground leads. Measure the switch node (OUT) by placing the oscilloscope probe tip through the large via on the switch node (designed for this purpose) and grounding the probe directly across the GND terminals provided. See Figure 3 for proper scope probe technique.

9. For shutdown, please follow steps in reverse.

THERMAL CONSIDERATIONS

- 8. Once operational, adjust the bus voltage and load PWM control within the operating range and observe the output switching behavior, efficiency and other parameters.

- 7. Turn on the controller / PWM input source and probe switching node to see switching operation.

- 6. Turn on the bus voltage to the required value (do not exceed the absolute maximum voltage of 200 V on  $V_{out}$ ).

- 5. Turn on the gate drive supply make sure the supply is between 7 V and 12 V range.

- 4. With power off, connect the input PWM control signal to PWM (J2, Pin-1) and ground return to any of the remaining J2 pins.

- 3. With power off, connect the gate drive input to  $+V_{DD}$  (J1, Pin-1) and ground return to  $-V_{DD}$  (J1, Pin-2).

- 2. With power off, connect the switch node of the half bridge  $V_{OUT}$  (J3, J4) to your circuit as required.

- 1. With power off, connect the input power supply bus to  $+V_{IN}$  (J5, J6) and ground / return to  $-V_{IN}$  (J7, J8).

Development board EPC9004 is easy to set up to evaluate the performance of the EPC2012 eGaN FET. Refer to Figure 2 for proper connect and measurement setup and follow the procedure below:

## **Quick Start Procedure**

<u>moɔ.oɔ-ɔqə.www</u>

.l siven in Higure 1. ficiency calculation. A complete block diagram of the circuit is probe points to facilitate simple waveform measurement and eflayout for optimal switching performance. There are also various by basic components and contains all critical components and Texas Instruments UCC2701 gate drivers as well as supply and

should be read in conjunction with this quick start guide. teacheet available from EPC at www.epc-co.com. The datasheet For more information on the EPC2012 eGaNFET please refer to the

easily connected into any existing converter. cluding all the critical components on a single board that can be to simplify the evaluation process of the EPC2012 eGaN FET by ineffect transistor (FET). The purpose of this development board is blaft (<sup>©</sup>Maturing the EPC2012 enhancement mode (eGaW<sup>®</sup>) field age, 2 A maximum output current, half bridge with onboard gate -Ihe EPC9004 development board is a 200 V maximum device volt-

two EPC2012 eGaN FET in a half bridge configuration using two The EPC9004 development board is 2.1 x "2 si breod thempedoleveb 4009D43 eff.

|                                        | dtbiW selu9 tuqnl stat2 'woJ' muminiM | 2001 > sn01 ≤ sin MW9V son01 > sin MW9V | #00S |     | su    |

|----------------------------------------|---------------------------------------|-----------------------------------------|------|-----|-------|

|                                        | dtbiW əslu9 tuqn ətst2 'dpiH' muminiM | nt son0٢ > عmit llst bus esin MWqV      | 001  |     | su    |

| WMd a                                  |                                       | ,moŋ, ֈnduj                             | 0    | ۶·۱ | ٨     |

| ۸ <sup>۵۸۸</sup>                       | PWM Logic Input Voltage Threshold     | յեր (H) մեր                             | 5.5  | 9   | ٨     |

| Ι                                      | Switch Node Output Current            |                                         |      | 5*  | А     |

| $\Lambda_{out}$                        | Switch Node Output Voltage            |                                         |      | 200 | ٨     |

| ۸ <sup>۱</sup>                         | əpneA əpetloV tuqni suð               |                                         |      | 051 | ٨     |

| Λ <sup>DD</sup>                        | Gate Drive Input Supply Range         |                                         | L    | ۲۱  | ٨     |

| <b>IOBMYS</b>                          | ЯЭТЭМАЯАЧ                             | CONDITIONO                              | NIW  | XAM | STINU |

| ()°2.5 = AT) yremmu2 sonemrot i PaldeT |                                       |                                         |      |     |       |

# Dependent on time needed to 'refresh' high side bootstrap supply voltage. nun afinia engliauanha u fuunauus an malans agunu

### DESCRIPTION

# Quick Start Guide Development Board EPC9004

200 V Half-Bridge with Gate Drive, Using EPC2012

**EFFICIENT POWER CONVERSION**

Figure 4: Waveforms for  $V_{IN} = 150 \text{ V}$  to 5 V/2 A (100kHz) Buck converter

CH1: VPWM Input voltage – CH2: (Iour) Switch node current – CH4: (Vour) Switch node voltage

Figure 1: Block Diagram of EPC9004 Development Board

באר נפגפנאפג תופ נוסער פר שעא תושפי אורעסתר עסתכפי רס כעשעקפ צפוס כונכתונגא פעם צאפכועכפרוסעצי otteofitoN bysed nottents

moɔ.yəメipib.www EPC Products are distributed exclusively through Digi-Key.

moɔ.oɔ-ɔqø@pnɛsī.nandəis f258.8049.228+ :9lidoM *<b>FisA, <i>s***<b>SS** pnszi neddetč

renee.yawger@epc-co.com 8789.913.809.1+ :91idoM 2072.274.809.1+:9) то WW Marketing Renee Yawger

<u>moɔ.oɔ-ɔq</u>ə.www

:su foefno)

moɔ.oɔ-ɔdə@pnənɔ.rəiəq 007.000.850.988+ :9lidoM FAE Support, Asia Peter Cheng

moo.oo-oq\_@nien.ysend 4242.978.934.1+:9lidoM 0fffce: +1.972.805.8585 **Froqqu2 3A7 Isdol Bhasy Vair**

Figure 3: Proper Measurement of Switch Node  $- V_{OUT}$

| 16 | 2 | TP1, TP2 | Test Point             | Keystone Elect, 5015           |

|----|---|----------|------------------------|--------------------------------|

| 17 | 1 | ТРЗ      | Connector              | 1/40th of Tyco, 4-103185-0     |

| 18 | 1 | U1       | I.C., Logic            | Fairchild, NC7SZ00L6X          |

| 19 | 1 | U2       | I.C., Isolator         | Silicon Laboratories, Si8410BB |

| 20 | 1 | U4       | I.C., Logic            | Fairchild, NC7SZ08L6X          |

| 21 | 2 | U6, U7   | I.C., Gate driver      | Texas Instruments, UCC27611    |

| 22 | 0 | C1, C15  | Optional capacitor     |                                |

| 23 | 0 | P1, P2   | Optional Potentiometer |                                |

| 24 | 0 | R13, R14 | Optional resistor      |                                |

| 25 | 0 | U5       | Optional I.C.          |                                |

| 16 | 2 | TP1, TP2 | Test Point             | Keystone Elect, 5015           |

|----|---|----------|------------------------|--------------------------------|

| 17 | 1 | ТРЗ      | Connector              | 1/40th of Tyco, 4-103185-0     |

| 18 | 1 | U1       | I.C., Logic            | Fairchild, NC7SZ00L6X          |

| 19 | 1 | U2       | I.C., Isolator         | Silicon Laboratories, Si8410BB |

| 20 | 1 | U4       | I.C., Logic            | Fairchild, NC7SZ08L6X          |

| 21 | 2 | U6, U7   | I.C., Gate driver      | Texas Instruments, UCC27611    |

| 22 | 0 | C1, C15  | Optional capacitor     |                                |

| 23 | 0 | P1, P2   | Optional Potentiometer |                                |

| 24 | 0 | R13, R14 | Optional resistor      |                                |

| 25 | 0 | U5       | Optional I.C.          |                                |

The EPC9004 development board showcases the EPC1012 eGaN FET. Although the electrical performance surpasses that for traditional Si devices, their relatively smaller size does magnify the thermal management requirements. The EPC9004 is intended for bench evaluation with low ambient temperature and convection cooling. The addition of heat-sinking and forced air cooling can significantly increase the current rating of these devices, but care must be taken to not exceed the absolute maximum die temperature of 125°C.

NOTE. When measuring the high frequency content switch node (OUT), care must be taken to avoid long ground leads. Measure the switch node (OUT) by placing the oscilloscope probe tip through the large via on the switch node (designed for this purpose) and grounding the probe directly across the GND terminals provided. See Figure 3 for proper scope probe technique.

9. For shutdown, please follow steps in reverse.

THERMAL CONSIDERATIONS

- 8. Once operational, adjust the bus voltage and load PWM control within the operating range and observe the output switching behavior, efficiency and other parameters.

- 7. Turn on the controller / PWM input source and probe switching node to see switching operation.

- 6. Turn on the bus voltage to the required value (do not exceed the absolute maximum voltage of 200 V on  $V_{out}$ ).

- 5. Turn on the gate drive supply make sure the supply is between 7 V and 12 V range.

- 4. With power off, connect the input PWM control signal to PWM (J2, Pin-1) and ground return to any of the remaining J2 pins.

- 3. With power off, connect the gate drive input to +VDD (J1, Pin-1) and ground return to -VDD (J1, Pin-2).

- 2. With power off, connect the switch node of the half bridge OUT (J3, J4) to your circuit as required.

- 1. With power off, connect the input power supply bus to +VIN (J5, J6) and ground / return to -VIN (J7, J8).

Development board EPC9004 is easy to set up to evaluate the performance of the EPC1012 eGaN FET. Refer to Figure 2 for proper connect and measurement setup and follow the procedure below:

## **Quick Start Procedure**

<u>moɔ.oɔ-ɔqə.www</u>

.l siven in Higure 1. ficiency calculation. A complete block diagram of the circuit is probe points to facilitate simple waveform measurement and eflayout for optimal switching performance. There are also various by basic components and contains all critical components and Texas Instruments UCC2701 gate drivers as well as supply and

should be read in conjunction with this quick start guide. teacheet available from EPC at www.epc-co.com. The datasheet For more information on the EPC2012 eGaNFET please refer to the

easily connected into any existing converter. cluding all the critical components on a single board that can be to simplify the evaluation process of the EPC2012 eGaN FET by ineffect transistor (FET). The purpose of this development board is blaft (<sup>©</sup>Maturing the EPC2012 enhancement mode (eGaW<sup>®</sup>) field age, 2 A maximum output current, half bridge with onboard gate The EPC9004 development board is a 200 V maximum device volt-

two EPC2012 eGaN FET in a half bridge configuration using two The EPC9004 development board is 2.1 x "2 si breod thempedoleveb 4009D43 eff.

| ()°2.5 = AT) y sommer of the second |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |                 |

|------------------------------------------------------------------------------------------------------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------|

| STINU                                                                                                            | XAM | NIW  | CONDITIONO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | AATAMAAAA                              | 27MBOL          |

| ٨                                                                                                                | ۲L  | Ĺ    | Gate Drive Input Supply Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        | Δα              |

| ٨                                                                                                                | 051 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | / <sub>№</sub> Bus Input Voltage Range |                 |

| ٨                                                                                                                | 500 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Switch Node Output Voltage             | $\Lambda_{out}$ |

| A                                                                                                                | 5*  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Switch Node Output Current             | Ιουτ            |

| ٨                                                                                                                | 9   | 3.5  | ,40iH, 1ndul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | blodserdT enertov tugal sing LMW9      |                 |

| ٨                                                                                                                | S.I | 0    | ,moŋ, induj                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PWM Logic Input Voltage Threshold      |                 |

| su                                                                                                               |     | 001  | 2001 > 2001 solution and soluti | dtbiW əslu9 tuqnl ətət2 'dpiH' muminiM |                 |

| su                                                                                                               |     | #00S | 2001 > amit llat bna aria MW9V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | dtbiW                                  |                 |

# Dependent on time needed to 'refresh' high side bootstrap supply voltage. ובער אונע אב אמאלבבר נה אאונבעשל עבלמבעבלי אמא אסונמלב מעמ נעבעשמי

### DESCRIPTION

# Quick Start Guide Development Board EPC9004

200 V Half-Bridge with Gate Drive, Using EPC2012

**EFFICIENT POWER CONVERSION**

Gate Driv Gate Drive Half-Bridge with Bypass pply Regulator PWM Enable Level Shift. Input Dead-time Adjust л Ţ and Gate Drive

Figure 1: Block Diagram of EPC9004 Development Board

CH1: VPWM Input voltage – CH2: (IOUT) Switch node current – CH4: (VOUT) Switch node voltage

Figure 4: Waveforms for VIN = 150 V to 5 V/2 A (100kHz) Buck converter

50.0V/ 35 218.0g 100.0g/ Stop F

Minimize loop

באר נפגפנאפג תופ נוסער פר שעא תושפי אורעסתר עסתכפי רס כעשעקפ צפוס כונכתונגא פעם צאפכועכפרוסעצי פעובה מעמבו פעל אפרבער עולער אין אייני ottestition breed notificatio

moɔ.yəメipib.www EPC Products are distributed exclusively through Digi-Key.

moɔ.oɔ-ɔqø@pnɛsī.nandəis f258.8049.228+ :9lidoM *<b>FisA, <i>s***<b>SS** pnszi neddetż

renee.yawger@epc-co.com 8789.913.809.1+ :91idoM 2072.274.809.1+:9) то WW Marketing Renee Yawger

<u>moɔ.oɔ-ɔqə.www</u>

:su foefno)

Place probe in large via at OUT

moɔ.oɔ-ɔdə@pnənɔ.rəiəq 007.000.850.988+ :9lidoM FAE Support, Asia Peter Cheng

moo.oo-oq\_@nien.ysend 4242.978.934.1+:9lidoM 0fffce: +1.972.805.8585 **Froqqu2 3A7 Isdol Bhasy Vair**

Figure 3: Proper Measurement of Switch Node – OUT

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Management IC Development Tools category:

Click to view products by EPCOS manufacturer:

Other Similar products are found below :

EVAL6482H-DISC EVAL-AD5522EBUZ EVAL-ADM1060EBZ EVAL-ADM1073MEBZ EVAL-ADM1166TQEBZ EVAL-ADM1168LQEBZ EVAL-ADM1171EBZ EVAL-ADM1276EBZ EVB-EN5319QI EVB-EN5365QI EVB-EN6347QI EVB-EP5348UI MIC23158YML EV MIC23451-AAAYFL EV MIC5281YMME EV 124352-HMC860LP3E ADM00513 ADM8611-EVALZ ADM8612-EVALZ ADM8613-EVALZ ADM8615-EVALZ ADP1046ADC1-EVALZ ADP1055-EVALZ ADP122-3.3-EVALZ ADP130-0.8-EVALZ ADP130-1.2-EVALZ ADP130-1.5-EVALZ ADP1046ADC1-EVALZ ADP160UJZ-REDYKIT ADP166UJ-EVALZ ADP1712-3.3-EVALZ ADP1714-3.3-EVALZ ADP130-1.5-EVALZ ADP1716-2.5-EVALZ ADP160UJZ-REDYKIT ADP166UJ-EVALZ ADP1712-3.3-EVALZ ADP1714-3.3-EVALZ ADP1715-3.3-EVALZ ADP1716-2.5-EVALZ ADP1740-1.5-EVALZ ADP1752-1.5-EVALZ ADP1754-1.5-EVALZ ADP1828LC-EVALZ ADP1870-0.3-EVALZ ADP1871-0.6-EVALZ ADP1873-0.6-EVALZ ADP1874-0.3-EVALZ ADP1876-EVALZ ADP1879-1.0-EVALZ ADP1882-1.0-EVALZ ADP1883-0.6-EVALZ ADP197CB-EVALZ ADP199CB-EVALZ ADP2102-1.25-EVALZ ADP2102-1.2-EVALZ