# **Application manual**

# **Real Time Clock Module**

# **RX8130CE**

ETM50E-07

| Product name | Product number  |

|--------------|-----------------|

| RX8130CE     | X1B000311000100 |

## NOTICE : PLEASE READ CAREFULLY BELOW BEFORE THE USE OF THIS DOCUMENT

- 1. The content of this document is subject to change without notice. Before purchasing or using Epson products, please contact with sales representative of Seiko Epson Corporation ("Epson") for the latest information and be always sure to check the latest information published on Epson's official web sites and resources.

- 2. This document may not be copied, reproduced, or used for any other purposes, in whole or in part, without Epson's prior consent.

- 3. Information provided in this document including, but not limited to application circuits, programs and usage, is for reference purpose only. Epson makes no guarantees against any infringements or damages to any third parties' intellectual property rights or any other rights resulting from the information. This document does not grant you any licenses, any intellectual property rights or any other rights with respect to Epson products owned by Epson or any third parties.

- 4. Using Epson products, you shall be responsible for safe design in your products; that is, your hardware, software, and/or systems shall be designed enough to prevent any critical harm or damages to life, health or property, even if any malfunction or failure might be caused by Epson products. In designing your products with Epson products, please be sure to check and comply with the latest information regarding Epson products (including, but not limited to this document, specifications, data sheets, manuals, and Epson's web site). Using technical contents such as product data, graphic and chart, and technical information, including programs, algorithms and application circuit examples under this document, you shall evaluate your products thoroughly both in stand-alone basis and within your overall systems. You shall be solely responsible for deciding whether to adopt/use Epson products with your products.

- 5. Epson has prepared this document carefully to be accurate and dependable, but Epson does not guarantee that the information is always accurate and complete. Epson assumes no responsibility for any damages you incurred due to any misinformation in this document.

- 6. No dismantling, analysis, reverse engineering, modification, alteration, adaptation, reproduction, etc., of Epson products is allowed.

- 7. Epson products have been designed, developed and manufactured to be used in general electronic applications and specifically designated applications ("Anticipated Purpose"). Epson products are NOT intended for any use beyond the Anticipated Purpose that requires particular quality or extremely high reliability in order to refrain from causing any malfunction or failure leading to critical harm to life and health, serious property damage, or severe impact on society, including, but not limited to listed below ("Specific Purpose"). Therefore, you are strongly advised to use Epson products only for the Anticipated Purpose. Should you desire to purchase and use Epson products for Specific Purpose, Epson makes no warranty and disclaims with respect to Epson products, whether express or implied, including without limitation any implied warranty of merchantability or fitness for any Specific Purpose. Please be sure to contact our sales representative in advance, if you desire Epson products for Specific Purpose: Space equipment (artificial satellites, rockets, etc.) / Transportation vehicles and their control equipment (automobiles, aircraft, trains, ships, etc.) / Medical equipment / Relay equipment to be placed on sea floor / Power station control equipment / Disaster or crime prevention equipment / Traffic control equipment / Financial equipment Other applications requiring similar levels of reliability as the above

- 8. Epson products listed in this document and our associated technologies shall not be used in any equipment or systems that laws and regulations in Japan or any other countries prohibit to manufacture, use or sell. Furthermore, Epson products and our associated technologies shall not be used for the purposes of military weapons development (e.g. mass destruction weapons), military use, or any other military applications. If exporting Epson products or our associated technologies, please be sure to comply with the Foreign Exchange and Foreign Trade Control Act in Japan, Export Administration Regulations in the U.S.A (EAR) and other export-related laws and regulations in Japan and any other countries and to follow their required procedures.

- 9. Epson assumes no responsibility for any damages (whether direct or indirect) caused by or in relation with your non-compliance with the terms and conditions in this document or for any damages (whether direct or indirect) incurred by any third party that you give, transfer or assign Epson products.

- 10. For more details or other concerns about this document, please contact our sales representative.

- 11. Company names and product names listed in this document are trademarks or registered trademarks of their respective companies.

©Seiko Epson Corporation 2021, All rights reserved.

# ETM50E Revision History

|          | E Revision |          |                                                                                |

|----------|------------|----------|--------------------------------------------------------------------------------|

| Rev. No. | Date       | Page     | Description                                                                    |

| 01       |            |          |                                                                                |

| 02       | 2015/10/05 |          | Release                                                                        |

| 03       | 2016/5/10  | 1        | Corrected a the block diagram.                                                 |

|          |            | 4        | Add description to [3.2. Pin Functions].                                       |

|          |            | 9        | Corrected a [10.1. Characteristic for the fluctuation of the power supply ]    |

|          |            | 13       | Corrected a [7) Clock output function]                                         |

|          |            | 27       | Corrected a [14.7.2. Related register of Battery backup switchover function]   |

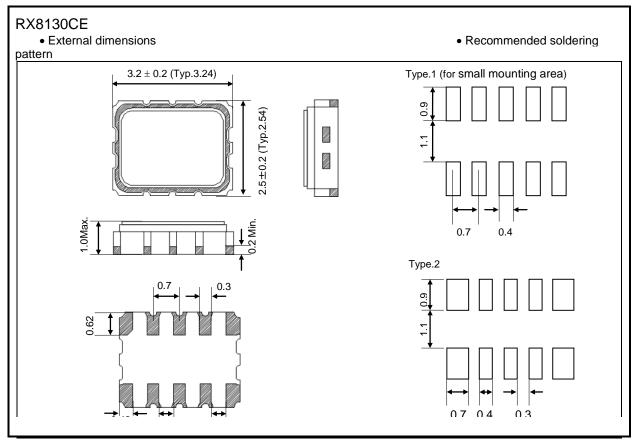

| 04       | 2016/9/20  | 3        | Updated the Recommended soldering pattern. Optimization of the text.           |

| 05       | 2016/1/23  | 2        | Added terminal processing when output terminal is not used.                    |

|          |            | 3        | Added typical value of external dimensions.                                    |

|          |            | 3        | Added recommended soldering pattern.                                           |

|          |            | 6        | Corrected Max. value of High- Level input voltage.                             |

|          |            | 8        | Corrected reset delay time (at recovery form backup).                          |

|          |            | 9        | Corrected access wait time.                                                    |

|          |            | 20       | Changed 7) TSTP bit related table.                                             |

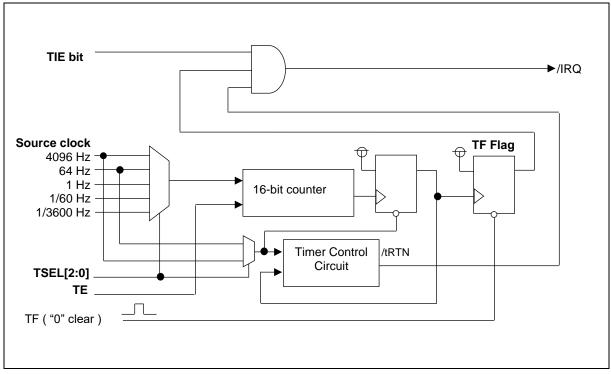

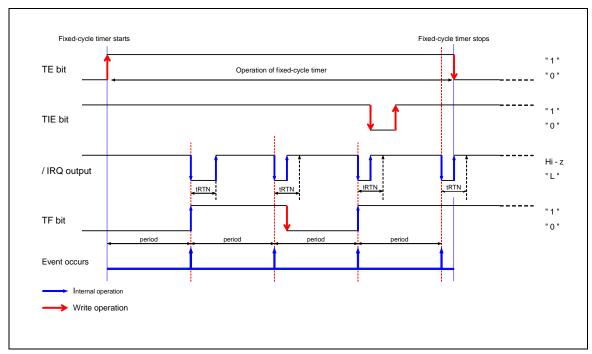

|          |            | 21       | Added timer circuit block diagram                                              |

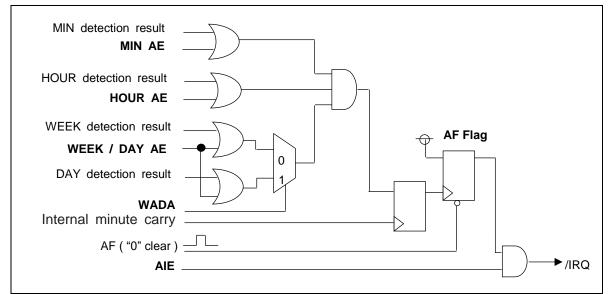

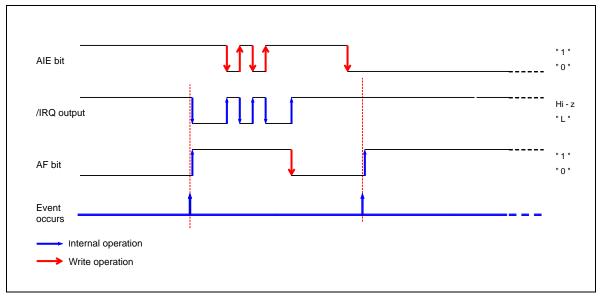

|          |            | 25       | Added alarm circuit block diagram                                              |

|          |            | 27       | Added time update circuit block diagram                                        |

|          |            | 30       | Corrected table operation stages of voltage detection.                         |

|          |            |          | 36 Added comment to wait time.                                                 |

|          |            | 36       | Added comment to wait time.                                                    |

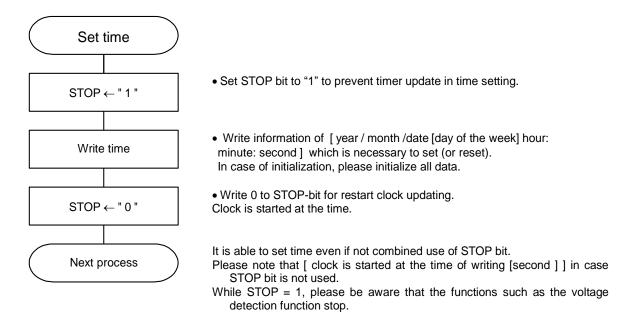

|          |            | 37       | Added comments related to STOP bit in 3)The setting of the clock and calendar. |

| 06       | 2019/7/31  | 42       | Added address circulation table of auto increment function.                    |

|          |            |          | -06 31 Jul 2019 5 Added Figure 4-4. Circuit EX4.                               |

|          |            | 5        | Added Figure 4-4. Circuit EX4.                                                 |

|          |            | 9        | Added Figure 9-1,9-2,9-3 Re-chargeable battery current                         |

|          |            | 17       | Corrected Table 13-1. Register table (expression Z)                            |

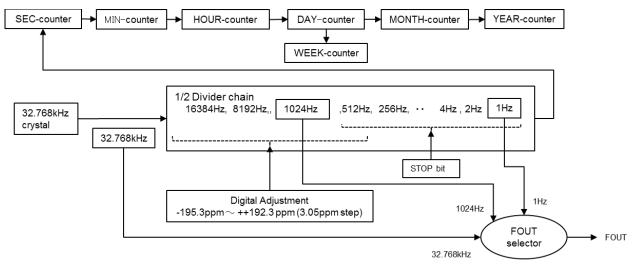

|          |            | 20       | Added Figure 14-1. Basic (32kHz oscillation, counter, FOUT) Function           |

|          |            | 32 to 41 | Fully revised (battery Backup switching)                                       |

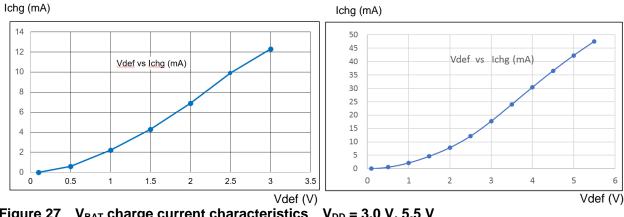

|          |            | 40       | Reference characteristics of the charge current in VBAT.                       |

|          |            | 53       | Added Figure 14-33. Typical MCU connection                                     |

|          |            | 53       | Added Figure 14-34 32kHz oscillator connection                                 |

|          |            | 54       | Added Tables                                                                   |

|          |            | 55       | Added Figures                                                                  |

| 07 | 2021/7/5 | All    | Table number. serialization                                                                                                                                                                                                                                                                                                                                                                    |

|----|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |          | All    | Figure number. serialization                                                                                                                                                                                                                                                                                                                                                                   |

|    |          | All    |                                                                                                                                                                                                                                                                                                                                                                                                |

|    |          | All    | The link to index was added to the all footer.                                                                                                                                                                                                                                                                                                                                                 |

|    |          | 7      | Power supply connection, "VD" symbol was deleted. Ex: VD3.0 to 3.0 V                                                                                                                                                                                                                                                                                                                           |

|    |          | 9      | Recommended Operation Condition                                                                                                                                                                                                                                                                                                                                                                |

|    |          |        | As for interface voltage Min,. Both spec mentioned, INIEN=0 and INIEN=1.                                                                                                                                                                                                                                                                                                                       |

|    |          |        | Optimized this chapter structure                                                                                                                                                                                                                                                                                                                                                               |

|    |          | 14     | 10. Interface timing when power is turned ON / OFF                                                                                                                                                                                                                                                                                                                                             |

|    |          | 16     | <ol> <li>The Power-On Chart was separated into two cases with and without battery.</li> <li>Correction of errors of tF condition.<br/>Error: tF = -V<sub>DET</sub>1 from "V<sub>DD</sub> OFF".<br/>Correct: tF = V<sub>CLK</sub> from "V<sub>DD</sub> OFF".</li> <li>Addition that describes the risk of not satisfying tR / tF</li> <li>Description of <u>Table11</u> was updated.</li> </ol> |

|    |          | 21     | 13.2.2. Register initial value                                                                                                                                                                                                                                                                                                                                                                 |

|    |          |        | Added description, that value are same in after software-Reset.                                                                                                                                                                                                                                                                                                                                |

|    |          | 39     | 1) Graph is added for the charge current to Battery.                                                                                                                                                                                                                                                                                                                                           |

|    |          |        | Figure27 V <sub>BAT</sub> charge current characteristics $V_{DD} = 3.0 \text{ V}, 5.5 \text{ V}$                                                                                                                                                                                                                                                                                               |

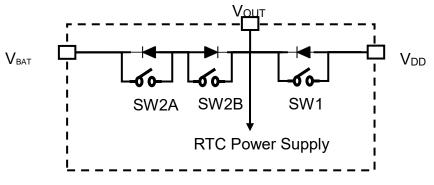

|    |          |        | 2) <u>Charging circuit diagram is added for reference.</u>                                                                                                                                                                                                                                                                                                                                     |

|    |          |        | Figure 28 Re-chargeable battery connection                                                                                                                                                                                                                                                                                                                                                     |

|    |          | 40     | Renewed the description of <u>INIEN-bit.</u>                                                                                                                                                                                                                                                                                                                                                   |

|    |          | 46     |                                                                                                                                                                                                                                                                                                                                                                                                |

|    |          | 48, 49 | Updated note of <u>STOP-bit.</u>                                                                                                                                                                                                                                                                                                                                                               |

|    |          |        | Charge enabled timing was fine corrected in Timing Chart.                                                                                                                                                                                                                                                                                                                                      |

|    |          | 54     | Figure 37 and Figure 38                                                                                                                                                                                                                                                                                                                                                                        |

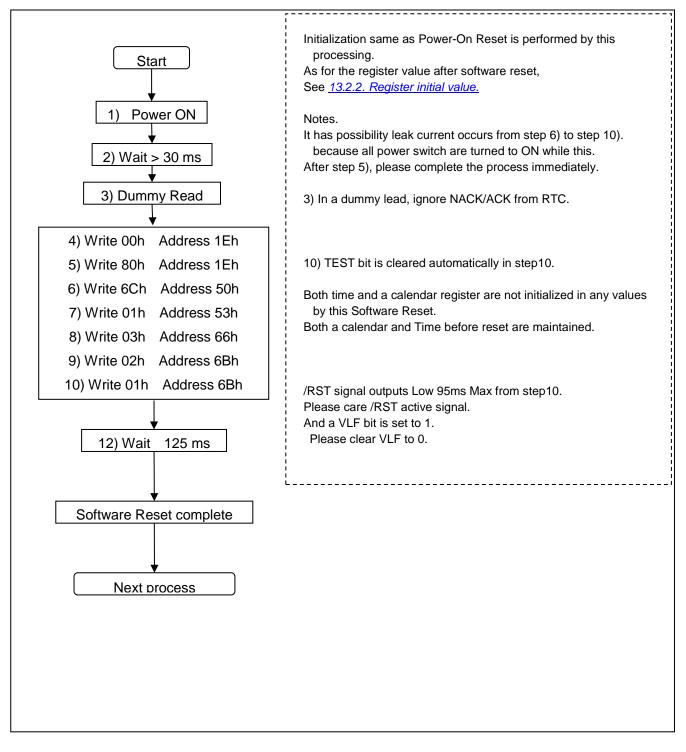

|    |          | _      | Software-Reset-Flow was added. <u>Software-Reset.</u>                                                                                                                                                                                                                                                                                                                                          |

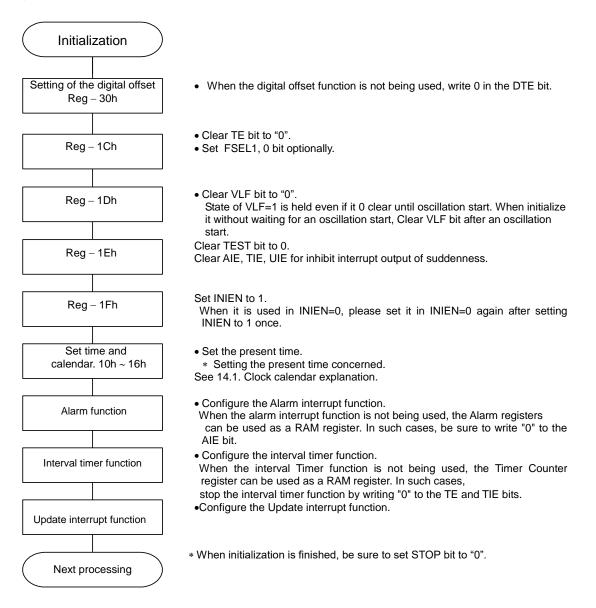

|    |          | 55     | INIEN bit processing was added to <i><u>Flow-chart of initializing.</u></i>                                                                                                                                                                                                                                                                                                                    |

|    |          | 64     | Pin connection was added for use as <u>32.768 kHz-Oscillator.</u>                                                                                                                                                                                                                                                                                                                              |

# Table of contents

| ETM50E Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table of contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                                                                                                                                                                                                                                                                                                                                                              |

| 1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                                                                                                                                                                                                                                                                                                                                              |

| 2. Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                                                                                                                                                                                                                                                                                                              |

| 3. Terminal description<br>3.1. Terminal connections<br>3.2. Pin Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                                                                                                                                                                                                                                                                                                                                                                              |

| 4. Examples of external connection<br>4.1. Examples of power supply connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                |

| 5. External Dimensions / Marking Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9                                                                                                                                                                                                                                                                                                                                                                              |

| 6. Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                             |

| 7. Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10                                                                                                                                                                                                                                                                                                                                                                             |

| 8. Frequency Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10                                                                                                                                                                                                                                                                                                                                                                             |

| 9. Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                                                                                                                                                                                                                                                                                                                                                                             |

| <ul> <li>10. Interface timing when power is turned ON / OFF</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15<br>15<br>16                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47                                                                                                                                                                                                                                                                                                                                                                             |

| 11. Reference Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1/                                                                                                                                                                                                                                                                                                                                                                             |

| 11. Reference Information     12. Application Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18<br>19<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br> |

| <ul> <li>12. Application Notes</li> <li>13. Overview of Functions and Registers</li> <li>13.1. Overview of Functions</li> <li>13.2. Register Table</li> <li>13.2.1. Register Table</li> <li>13.2.2. Register initial value and Read/Write operation Table</li> <li>13.3. Description of registers</li> <li>13.3.1. Clock and calendar registers (0h ~ 16h)</li> <li>13.3.2. RAM registers (20h ~ 23h)</li> <li>13.3.3. Alarm registers (17h ~ 19h)</li> <li>13.3.4. Timer setting and Timer counter register for wakeup timer (1Ah ~ 1Eh)</li> <li>13.3.5. Function-related register 1 (1Ch ~ 1Eh)</li> <li>13.3.6. Function-related register 2 (1Fh)</li> </ul> | 18<br>19<br>                                                                                                                                                                                                                                                                                                                                                                   |

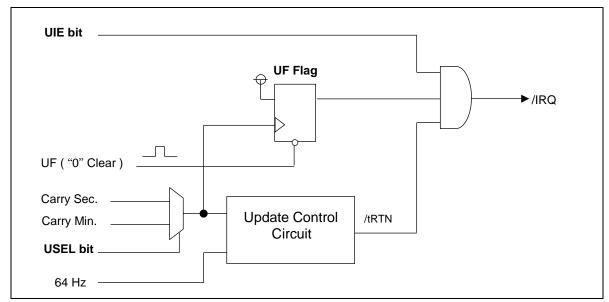

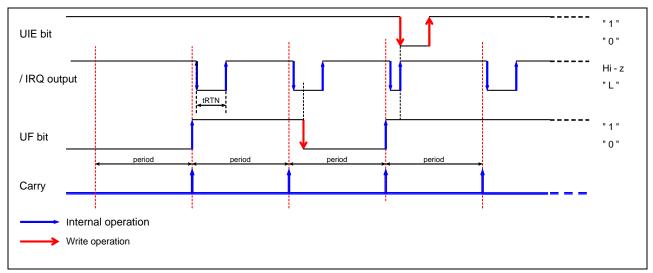

| 14.4.2. Time update interrupt function diagram                                                                  |    |

|-----------------------------------------------------------------------------------------------------------------|----|

| 14.5. Oscillation stop detection function                                                                       |    |

| 14.5.1. Related registers for Oscillation stop and Voltage low detect function                                  |    |

| 14.6.1. FOUT control register.                                                                                  |    |

| 14.6.2. FOUT function Table.                                                                                    |    |

|                                                                                                                 |    |

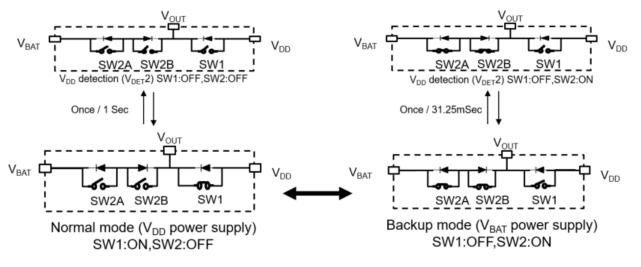

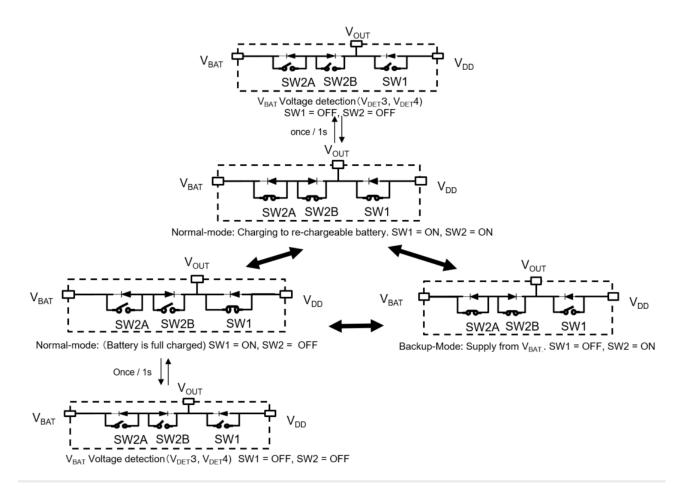

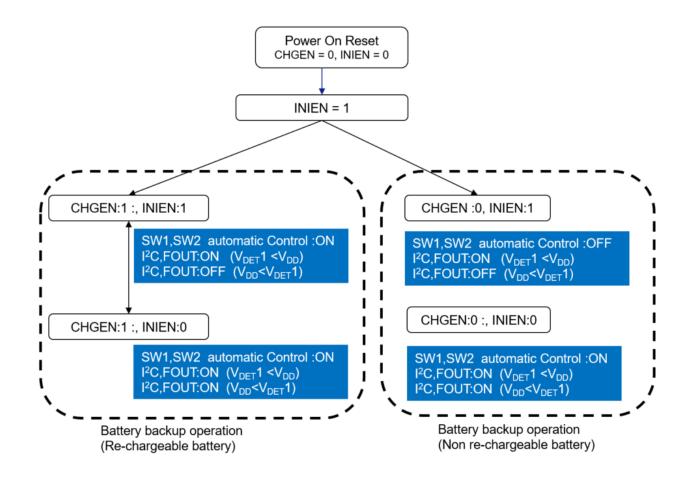

| 15 Battery backup switchover function                                                                           |    |

| 15.1. Description of Battery backup switchover function<br>15.2 Reference characteristics of switching elements |    |

| 15.3 Reference characteristics of the charge current                                                            |    |

| 15.4 Re-Chargeable battery Voltage Current features                                                             |    |

| 15.5. Related register of Battery backup switchover function                                                    | 40 |

| 15.6 Detection voltage setting                                                                                  |    |

| 15.7. Power supply control                                                                                      |    |

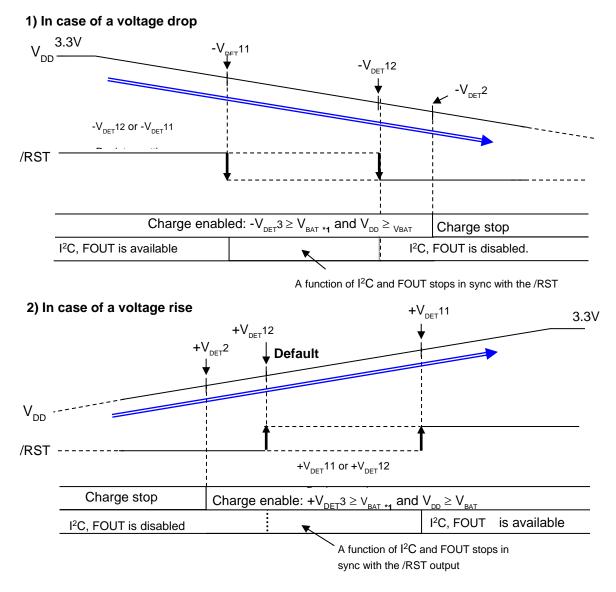

| 15.8 Main power supply $(V_{DD})$ voltage and operation state (INIEN bit = 1)                                   |    |

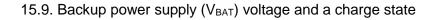

| 15.9. Backup power supply ( $V_{BAT}$ ) voltage and a charge state                                              | 49 |

| 16. Reset output function                                                                                       | 50 |

| 17. Digital offset function                                                                                     | 51 |

| 17.1.Digital offset register                                                                                    |    |

| 17.2. Effect of the digital offset function to other functions                                                  |    |

|                                                                                                                 |    |

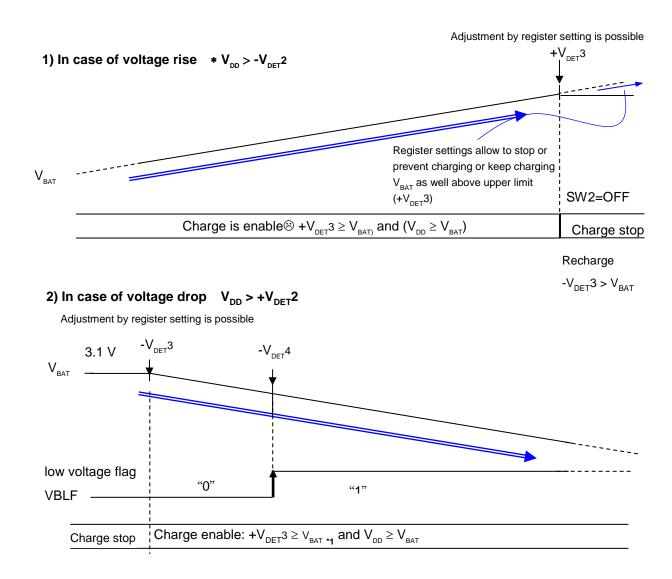

| 18. Flow-chart                                                                                                  |    |

| 18.1 Initializing example<br>18.2 Software Reset                                                                |    |

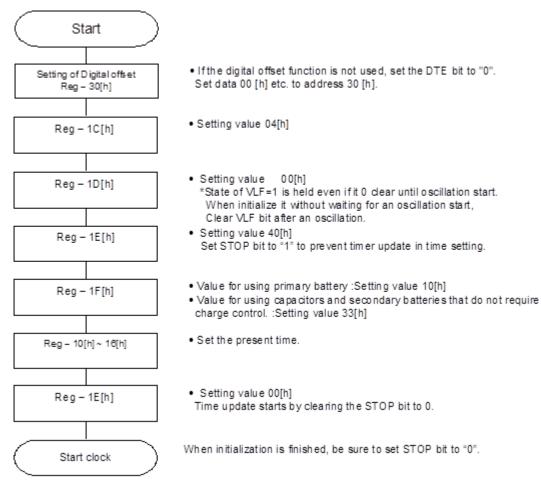

| 18.3 Example of Initialization routine                                                                          | -  |

| 18.4 Example of Initialization routine (only clock usage)                                                       |    |

| 18.5 The setting of the clock and calendar                                                                      |    |

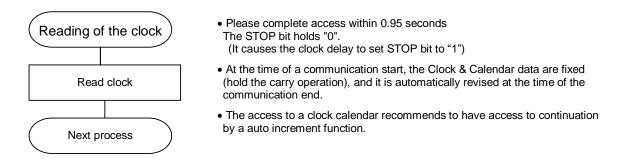

| 18.6 The reading of the clock and calendar                                                                      | 57 |

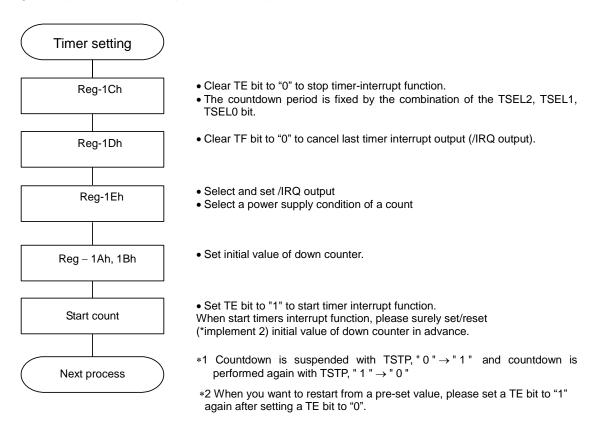

| 18.7 Setting example of the wakeup timer interrupt function                                                     |    |

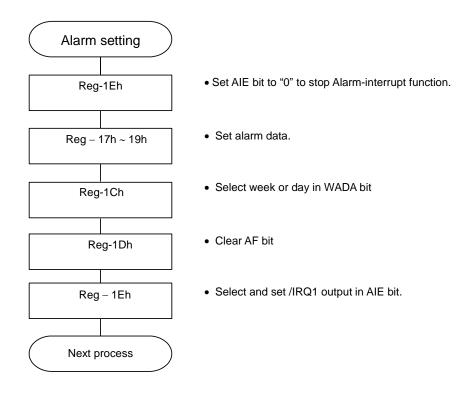

| 18.8 Setting example of the Alarm interrupt function                                                            | 58 |

| 19 Serial communication                                                                                         |    |

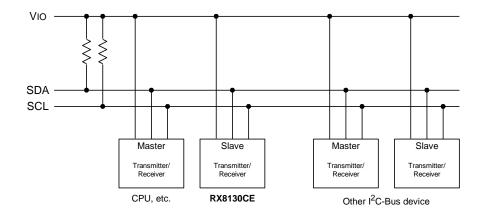

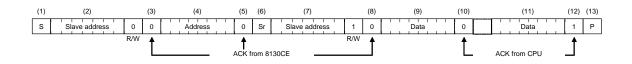

| 19.1 Overview of I <sup>2</sup> C-Bus Interface                                                                 |    |

| 19.2 Data transfers                                                                                             |    |

| 19.3 Starting and stopping I <sup>2</sup> C-Bus communications                                                  |    |

| 19.4 Slave address                                                                                              |    |

| 19.5 System configuration                                                                                       |    |

| 19.6 I <sup>2</sup> C-Bus protocol                                                                              | 01 |

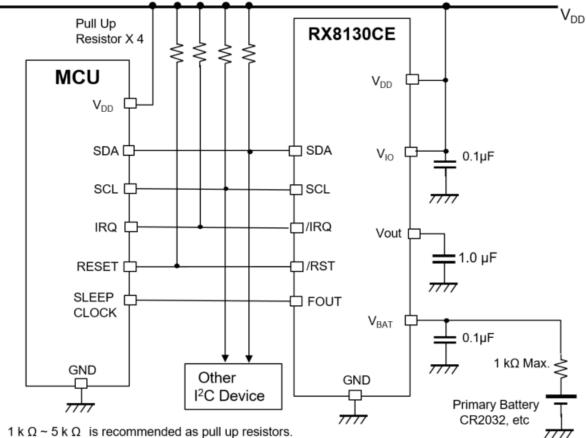

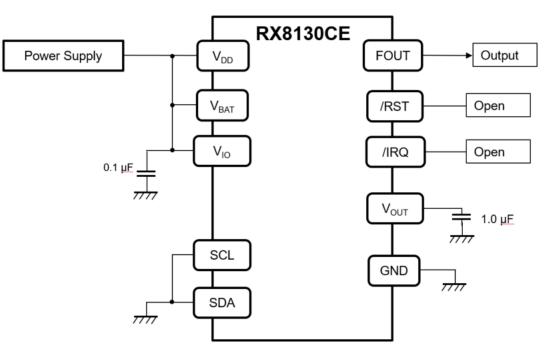

| 20 Circuit Diagram connection                                                                                   | 63 |

| 20.1 Typical MCU connection                                                                                     | 63 |

| 20.2 32.768 kHz oscillator application connection                                                               | 64 |

| 21. Tables                                                                                                      | 65 |

| 22. Figures                                                                                                     | 66 |

| Contacts                                                                                                        | 68 |

|                                                                                                                 |    |

# Build-in backup battery charge control function SERIAL-INTERFACE REAL TIME CLOCK MODULE

# **RX8130 CE**

- Built in frequency adjusted 32.768 kHz crystal unit.

- Interface type

- : I<sup>2</sup>C-Bus interface (up to 400 kHz) : 1.6 V to 5.5 V

- Wide operating voltage range : 1.1 V to 5.5 V

- Wide timekeeper voltage range

- : Switchover by main power supply monitor.

- Auto power switching function

- Backup battery charge control function : For rechargeable lithium batteries.

- : A leak current from a backup power supply pin. 5nA Max.

- Low leak current • Reset function Low voltage detection

- : At low supply voltage, external reset signal is generated.

- : Supply voltage and backup voltage detection

- Time correction

- : Digital offset function

- The various function including full calendar, alarm, timer, etc.

# 1. Overview

RX8130CE is a real-time clock module of the I<sup>2</sup>C serial interface system, 32.768 kHz crystal and oscillator is built-in it. The real-time clock function incorporates not only a calendar and clock counter for the year, month, day, day of the week, hour, minute, and second, but also a time alarm, wakeup timer, and time update interruption, among other features. By the backup battery charge control function and the interface power supply input pin, RX8130CE can support various power supply circuitries.

All these many functions are implemented in a thin, compact ceramic package, which makes it suitable for various kinds of small electronic devices, low power IoT devices etc.

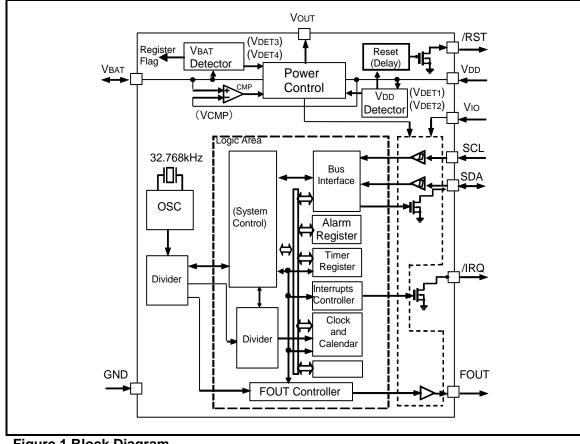

# 2. Block Diagram

Figure 1 Block Diagram

# 3. Terminal description

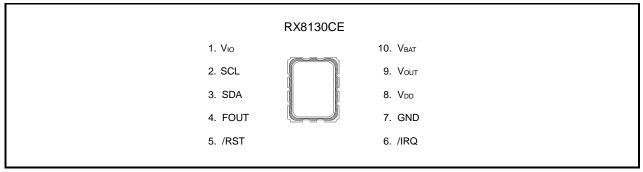

# 3.1. Terminal connections

# Figure 2 Package

# 3.2. Pin Functions

#### **Table 1 Pin Description**

| Signal<br>name | I/O            | Function                                                                                                                                                                                                                          |

|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL            | Input          | Serial clock input pin.                                                                                                                                                                                                           |

| SDA            | Bi-directional | Data input and output pin.                                                                                                                                                                                                        |

| FOUT           | Output         | Frequency output pin with output control function. (CMOS)<br>Output frequency can be selected as 32.768k Hz, 1024 Hz, 1 Hz.                                                                                                       |

| / RST          | Output         | Even in the backup mode, this pin can operate. In case of $V_{DD}$ voltage drop detection, a reset signal is outputted. (N-ch open drain)<br>In case of $V_{DD}$ voltage rise detection, it releases the reset signal after 60ms. |

| / IRQ          | Output         | Interrupt output by Alarm and Timer events.(N-ch open drain)<br>This pin can output even a backup mode.                                                                                                                           |

| Vdd            | _              | This is a power-supply pin for the internal logic.                                                                                                                                                                                |

| Vlo            | _              | This is an interface power supply pin.<br>Connect the same power supply as the MCU.                                                                                                                                               |

| Vout           | _              | Internal voltage output pin.<br>Connect smoothing capacitor of 1.0uF                                                                                                                                                              |

| VBAT           | _              | This is a power supply pin for backup battery.<br>This is a pin to connect a large-capacity capacitor, a secondary battery, and a primary<br>battery.<br>In a backup mode, the voltage is supplied inside by this pin.            |

| GND            | -              | Connected to a ground.                                                                                                                                                                                                            |

Note: Connect a bypass capacitor rated at least 0.1µF between power supply pins and GND pin.

Note: Input pins are able to input up to 5.5V regardless of  $V_{10}$  applied voltage.

Note: Open drain pins are able to Pull-up to 5.5V regardless of  $V_{10}$  applied voltage.

Note: Use the FOUT, /RST, /IRQ terminals as Open when not in use. Don't connected to GND or  $V_{DD}$

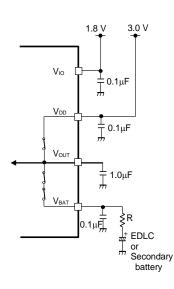

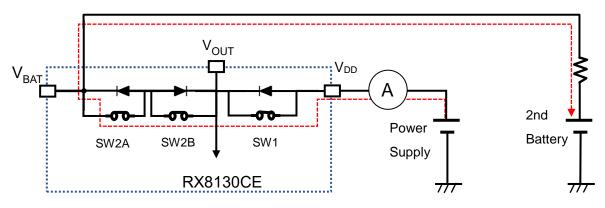

- 4. Examples of external connection

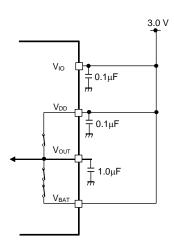

- 4.1. Examples of power supply connection

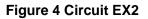

- (1) Case of different I/F voltage and charge voltage

Figure 3 Circuit EX1

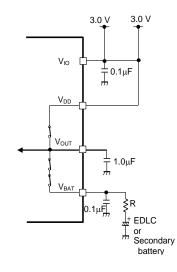

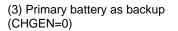

(2) Same I/F voltage and charge voltage (CHGEN=1, INIEN=1)

(4) Case of  $V_{\text{DD}}$  supply only.

Figure 6 Circuit EX4

ETM50E-07

# 5. External Dimensions / Marking Layout

# 5.1. External Dimensions

Figure 7 External Dimension and Soldering pattern

# 5.2. Marking Layout

Figure 8 Marking Layout

# 6. Absolute Maximum Ratings

| Item                        | Symbol Condition |                                           | Rating         | Unit |

|-----------------------------|------------------|-------------------------------------------|----------------|------|

| Supply voltage              | Vdd              | -                                         | -0.3 ~ +6.5    | V    |

| Internal voltage            | Vouт             | -                                         | -0.3 ~ +6.5    | V    |

| Backup supply voltage       | Vbat             | -                                         | -0.3 ~ +6.5    | V    |

| Interface<br>supply voltage | Vio              | _                                         | -0.3 ~ +6.5    | V    |

| Input voltage 1             | VIN1             | SCL, SDA                                  | -0.3 ~ +6.5    | V    |

| Output voltage 1            | Vout1            | /RST, /IRQ, SDA                           | -0.3 ~ +6.5    | V    |

| Output voltage 2            | Vout2            | FOUT                                      | -0.3 ~ Vio+0.3 | V    |

|                             |                  | When stored separately, without packaging | -55 ~ +125     | °C   |

# Table 2 Absolute Maximum Rating

# 7. Recommended Operating Conditions

# **Table 3 Recommended Operation Condition**

| Unless otherwise specified, GND = 0 V , Ta = $-40$ °C to $+85$ |        |                                           |                     |      |      |      |  |

|----------------------------------------------------------------|--------|-------------------------------------------|---------------------|------|------|------|--|

| ltem                                                           | Symbol | Condition                                 | Min.                | Тур. | Max. | Unit |  |

| Operating supply voltage                                       | Vdd    | Normal operation mode ( $V_{DD}$ )        | 1.25                | 3.0  | 5.5  | V    |  |

| Interface supply voltage                                       | Vio    | INIEN = 0                                 | 1.6                 | 3.0  | 5.5  | V    |  |

|                                                                |        | INIEN = 1                                 | -V <sub>DET</sub> 1 | 3.0  | 5.5  | V    |  |

| Clock supply voltage                                           | Vclk   | Backup operation mode (V <sub>OUT</sub> ) | 1.1                 | 3.0  | 5.5  | V    |  |

| Operating temperature                                          | T use  | No condensation                           | -40                 | +25  | +85  | °C   |  |

Minimum clock supply voltage of  $V_{CLK}$  is available after initializing in  $V_{DD}$ > $V_{DET}$ 11.

# 8. Frequency Characteristics

# **Table 4 Frequency Characteristics**

|                                       |        |                                                                                    |             | , 0.12 0. | ,        |                              |

|---------------------------------------|--------|------------------------------------------------------------------------------------|-------------|-----------|----------|------------------------------|

| Item                                  | Symbol | Condition                                                                          | Min.        | Тур.      | Max.     | Unit                         |

| Output frequency                      | fo     |                                                                                    |             | 32.768    | ( Тур. ) | kHz                          |

| Frequency stability                   | Δf/f   | Ta = +25 °C<br>V <sub>DD</sub> = 3.0 V                                             | 5 ± 23 (*1) |           |          | × 10 <sup>-6</sup>           |

| Frequency/voltage characteristics     | f / V  | Ta = +25 °C<br>V <sub>DD</sub> = 1.1 V ~ 5.5 V                                     | -2          |           | +2       | imes 10 <sup>-6</sup> / V    |

| Frequency/temperature characteristics | Тор    | Ta = -20 °C ~ +70 °C<br>V <sub>DD</sub> = 3.0 V ; +25 °C reference                 | -120        |           | +10      | × 10 <sup>-6</sup>           |

| Oscillation start time                | t_Sta  | $V_{DD} = 2.75 \text{ V} \sim 5.5 \text{ V}$<br>Internal Crystal oscillation start |             | 0.19      | 1.0      | S                            |

| Aging                                 | fa     | Ta = +25 °C , VBAT = 3.0 V ;<br>first year                                         | -5          |           | +5       | × 10 <sup>-6</sup><br>∕ year |

$^{\ast 1\,)}$  The monthly error is equal to  $\pm 60$  s Max. ( excluding offset )

RX8130CE

Unless otherwise specified, GND = 0 V , Ta = –40  $^\circ\text{C}$  to +85  $^\circ\text{C}$

# 9. Electrical Characteristics

# 9.1. DC characteristics

# Table 5 DC characteristics (1)

Unless otherwise specified, GND = 0 V ,  $V_{BAT} = V_{DD} = 1.1 V \sim 5.5 V$ ,  $V_{IO} = 1.6 V \sim 5.5 V$  Ta = -40 °C to +85 °C to

| Item                                                                     | Symbol  | Condition                                                                                                                                                                                                                                                                                                                                                                                                             | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Current consumption<br>in normal operation<br>mode without FOUT<br>(1)   | ldd     | $\begin{array}{l} \text{SCL} = \text{SDA} = \text{"H"} \ , \\ \text{F}_{\text{OUT}} = \text{OFF}, \ /\text{IRQ} = \text{OFF}, \\ \text{V}_{\text{DD}} = \text{V}_{\text{IO}} = 3.0 \ \text{V}, \ -40 \ \text{°C} \sim +85 \ \text{°C} \\ \text{CHGEN} = 0b \ \text{or} \ \text{V}_{\text{BAT}} \geqq \ \text{V}_{\text{DET}} 3 \end{array}$                                                                           |      | 1500 | 1600 | nA   |

| Current consumption<br>in normal operation<br>with FOUT (2)              | Із2к    | $\begin{array}{l} {\rm SCL} = {\rm SDA} = {\rm "H"} \;, \\ {\rm FOUT} = 32.768 \; {\rm kHz} \;, \; /{\rm IRQ} = {\rm OFF} \;, \\ {\rm V}_{\rm DD} {=} {\rm V}_{\rm IO} = 3.0 \; {\rm V} \;, \; -40 \; {\rm ^{\circ}C} \; {\rm ^{\circ} +85 \; ^{\circ}C} \\ {\rm FOUT} \; {\rm pin} \; \; {\rm CL} = 15 \; {\rm pF} \\ {\rm CHGEN} = 0b \; {\rm or} \; {\rm V}_{\rm BAT} \; \geqq \; {\rm V}_{\rm DET} 3 \end{array}$ |      | 3.5  | 4.0  | μA   |

| Current consumption in backup mode(3)                                    | Іват    | $\begin{array}{l} SCL = SDA = "L" \; , \\ VBAT = 3.0 \; V \; , V_{DD} {=} V_{IO} {=} \; 0.0 \; V, \\ 40 \; ^{\circ}C \; {\sim} \; {+}85 \; ^{\circ}C \end{array}$                                                                                                                                                                                                                                                     |      | 300  | 500  | nA   |

| Detector Threshold<br>Voltage1<br>(rising edge of VDD)                   | +Vdet11 | 2.75 V setting Reset-releases                                                                                                                                                                                                                                                                                                                                                                                         | 2.72 | 2.80 | 2.88 | V    |

| Detector Threshold<br>Voltage1<br>(falling edge of<br>VDD)               | -Vdet11 | 2.75 V setting、Reset output                                                                                                                                                                                                                                                                                                                                                                                           | 2.67 | 2.75 | 2.83 | V    |

| Detector Threshold<br>Voltage2<br>(rising edge of VDD )                  | +Vdet12 | 2.7 V setting Reset-releases                                                                                                                                                                                                                                                                                                                                                                                          | 2.67 | 2.75 | 2.83 | V    |

| Detector Threshold<br>Voltage2<br>(falling edge of<br>VDD)               | -Vdet12 | 2.7 V setting , Reset output                                                                                                                                                                                                                                                                                                                                                                                          | 2.62 | 2.70 | 2.78 | V    |

| Detector Threshold<br>Voltage3<br>(rising edge of VDD)                   | +Vdet2  | Switching voltage from VBAT to VDD                                                                                                                                                                                                                                                                                                                                                                                    | 1.25 | 1.35 | 1.45 | V    |

| Detector Threshold<br>Voltage3<br>(falling edge of<br>VDD)               | -Vdet2  | Switching voltage from VDD to VBAT                                                                                                                                                                                                                                                                                                                                                                                    | 1.20 | 1.30 | 1.40 | V    |

| Detector Threshold<br>Voltage1<br>(rising edge of VBAT)                  | +Vdet31 | Charge stop voltage (full charge)<br>BFVSEL=00b                                                                                                                                                                                                                                                                                                                                                                       | 2.94 | 3.02 | 3.10 | V    |

| Detector Threshold<br>Voltage1<br>(falling edge of<br>VBAT)              | -Vdet31 | Recharge voltage.<br>BFVSEL=00b                                                                                                                                                                                                                                                                                                                                                                                       | 2.89 | 2.97 | 3.05 | V    |

| Detector Threshold<br>Voltage2<br>(rising edge of VBAT)                  | +Vdet30 | Charge stop voltage (full charge)<br>BFVSEL=10b                                                                                                                                                                                                                                                                                                                                                                       | 2.84 | 2.92 | 3.00 | V    |

| Detector Threshold<br>Voltage2<br>(falling edge of<br>VBAT)              | -Vdet30 | Recharge voltage.<br>BFVSEL=10b                                                                                                                                                                                                                                                                                                                                                                                       | 2.79 | 2.87 | 2.95 | V    |

| Detector Threshold<br>Voltage3<br>(rising edge of VBAT)                  | +Vdet32 | Charge stop voltage (full charge)<br>BFVSEL=01b                                                                                                                                                                                                                                                                                                                                                                       | 3.00 | 3.08 | 3.16 | V    |

| Detector Threshold<br>Voltage3<br>(falling edge of<br>V <sub>BAT</sub> ) | -Vdet32 | Recharge voltage.<br>BFVSEL=01b                                                                                                                                                                                                                                                                                                                                                                                       | 2.95 | 3.03 | 3.11 | V    |

| VBAT end voltage                                                         | -Vdet4  | Low V <sub>BAT</sub> detection<br>Register flag VBLF = 1b                                                                                                                                                                                                                                                                                                                                                             | 2.32 | 2.40 | 2.48 | V    |

| VDD-VOUT<br>off-leak current                                             | Isw1    | Vout=3.0 V、Vdd=0.0 V                                                                                                                                                                                                                                                                                                                                                                                                  |      |      | 5.0  | nA   |

| VBAT-VOUT<br>off-leak current                                            | lsw2    | Vbat=3.0 V 、Vout=0.0 V                                                                                                                                                                                                                                                                                                                                                                                                |      |      | 5.0  | nA   |

RX8130CE

ETM50E-07

| Unless otherwise specified GND = 0 V V <sub>BAT</sub> = V <sub>DD</sub> = $1.1V \sim 5.5V$ V <sub>IO</sub> = $1.6V \sim 5.5V$ Ta = $-40 \circ$ C to $+85 \circ$ C |        |              |                                    |                  |           |                  |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|------------------------------------|------------------|-----------|------------------|------|

| Item                                                                                                                                                              | Symbol |              | Condition                          | Min.             | Тур.      | Max.             | Unit |

| Vout output voltage                                                                                                                                               | Vvout1 | VDD = 3.0 V  | IOUT = 1 mA                        |                  | VDD-0.06  |                  | V    |

| Vout output voltage 2                                                                                                                                             | Vvout2 | VBAT = 3.0 V | IOUT = 0.1 mA                      |                  | VBAT-0.02 |                  | V    |

| High-level<br>input voltage                                                                                                                                       | VIH1   | SCL, SDA     |                                    | $0.8 \times Vio$ |           | 5.5              | V    |

| Low-level<br>input voltage                                                                                                                                        | VIL    | SCL, SDA     |                                    | GND – 0.3        |           | $0.2 \times Vio$ | V    |

| High-level<br>output voltage                                                                                                                                      | Vон    | FOUT         | Іон = -1 mA                        | V10-0.5          |           | Vio              | V    |

| Low-level                                                                                                                                                         | Vol1   | FOUT         | IOL = 1 mA                         | GND              |           | GND+0.5          | V    |

| output voltage                                                                                                                                                    | Vol2   | /RST,/IRQ    | Vio = 5 V, IoL = 1 mA              | GND              |           | GND+0.2<br>5     | V    |

|                                                                                                                                                                   | Vol3   |              | VIO = 3 V, IOL = 1 mA              | GND              |           | GND+0.4          | V    |

|                                                                                                                                                                   | Vol4   | SDA          | $V_{IO} \ge 2 V$ , $I_{OL} = 3 mA$ | GND              |           | GND+0.4          | V    |

# Table 6 DC characteristics(2)

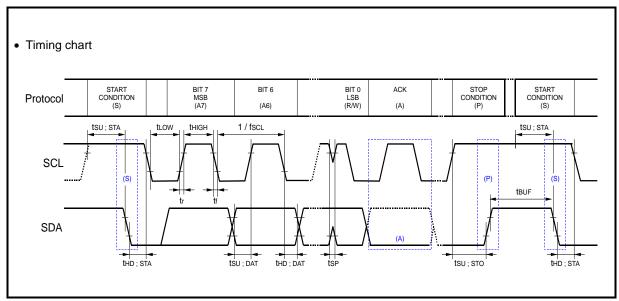

# 9.2. AC characteristics

# Table 7 AC characteristics

| Item                                                        | Symbol  | Standard-Mode<br>(fscL=100 kHz) |      | Fast-Mode<br>(fscL=400 kHz) |      | Unit |  |

|-------------------------------------------------------------|---------|---------------------------------|------|-----------------------------|------|------|--|

|                                                             | -,      | Min.                            | Max. | Min.                        | Max. |      |  |

| SCL clock frequency                                         | fscl    |                                 | 100  |                             | 400  | kHz  |  |

| Start condition setup time                                  | tsu;sta | 4.7                             |      | 0.6                         |      | μS   |  |

| Start condition hold time                                   | thd;sta | 4.0                             |      | 0.6                         |      | μs   |  |

| Data setup time                                             | tsu;dat | 250                             |      | 100                         |      | ns   |  |

| Data hold time                                              | thd;dat | 0                               |      | 0                           |      | ns   |  |

| Stop condition setup time                                   | tsu;sto | 4.0                             |      | 0.6                         |      | μs   |  |

| Bus idle time between<br>start condition and stop condition | tBUF    | 4.7                             |      | 1.3                         |      | μS   |  |

| Time when SCL = "L"                                         | tLOW    | 4.7                             |      | 1.3                         |      | μS   |  |

| Time when SCL = "H"                                         | thigh   | 4.0                             |      | 0.6                         |      | μS   |  |

| Rise time for SCL and SDA                                   | tr      |                                 | 1.0  |                             | 0.3  | μs   |  |

| Fall time for SCL and SDA                                   | tf      |                                 | 0.3  |                             | 0.3  | μS   |  |

| Allowable spike time on bus                                 | tSP     |                                 | 50   |                             | 50   | ns   |  |

. . .

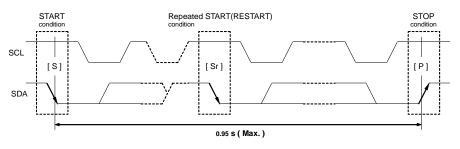

# Figure 9 I<sup>2</sup>C-Bus Interface Timing Chart

Warning: When accessing this device, all communication from transmitting the start condition to transmitting the stop condition after access should be completed within 0.95 seconds.

If such communication requires 0.95 seconds or longer, the I<sup>2</sup>C-Bus interface is reset by the internal bus timeout function.

When bus-time-out occur, SDA turns to Hi-Z input mode.

Note: During access to the time registers, the time counting is on hold. This means that up to 1 second can be "lost" in case of unsuccessful communication as mentioned above.

Please make sure to send  $I^2C$  start condition before actual transmission of the RTCs slave address as otherwise the slave address appears to be shifted by 1 bit.

# Table 8 AC characteristics (FOUT)

$\times$ Unless otherwise specified GND = 0 V , VIO = 1.6 V ~ 5.5 V , Ta= –40 °C ~ +85 °C

| Item          | Symbol | Condition     | Min. | Тур. | Max. | Unit |

|---------------|--------|---------------|------|------|------|------|

| FOUT symmetry | SYM    | 50% Vio Level | 40   |      | 60   | %    |

RX8130CE

ETM50E-07

# 9.2.3. AC characteristics(3)

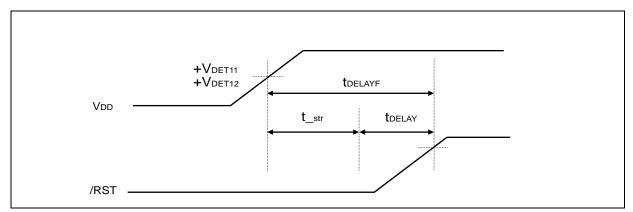

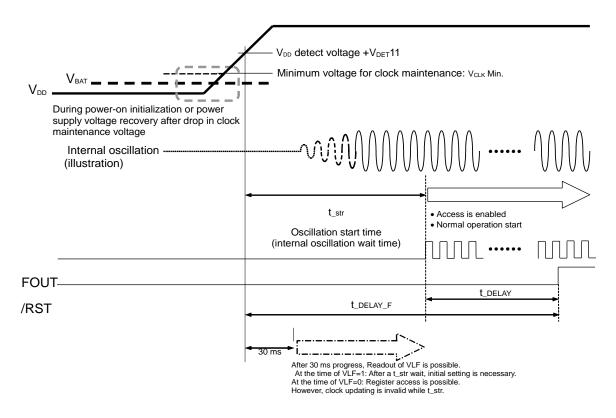

# Table 9 AC Characteristics (Reset)

| Item                                   | symbol         | Min. | Тур.                    | Max. | unit |

|----------------------------------------|----------------|------|-------------------------|------|------|

| Reset internal delay time              | <b>t</b> DELAY |      | 60                      |      | ms   |

| Reset delay time<br>(Initial power ON) | tdelay_f       |      | 250<br>(t_str + tdelay) |      | ms   |

\* t\_str is oscillation startup time. See "Table4".

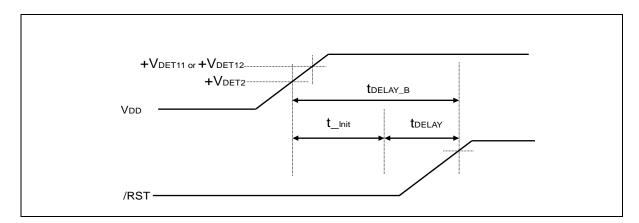

# Figure 10 Reset signal timing chart (Power Initial Supply)

# Table 10 Reset timing

| Item                                                          | symbol   | Min. | Тур. | Max. | unit |

|---------------------------------------------------------------|----------|------|------|------|------|

| Voltage detection time to reset release.                      | t_int    |      |      | 35   | ms   |

| Reset delay time<br>(Recovery from Backup)<br>t_int + t_DELAY | tdelay_b | 60   |      | 95   | ms   |

t\_int is an intermittence drive timing of a VDET2 detect circuit. Maximum value is 35 ms.

# Figure 11 Reset signal timing chart (Backup resume)

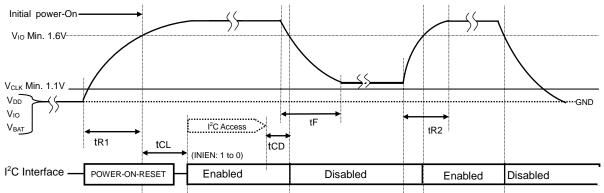

# 10. Interface timing when power is turned ON / OFF

10.1. Restrictions of I<sup>2</sup>C-Bus interface in the initial power on.

The operation of the RTC register is linked to the oscillation clock of the built-in crystal unit.  $\Box$

Therefore, it will not operate normally when the oscillation is stopped.

It is recommended that the initialization at the time of initial power-on is performed after the oscillation start time t\_str characteristic.

#### Figure 12 Power supply initial sequence

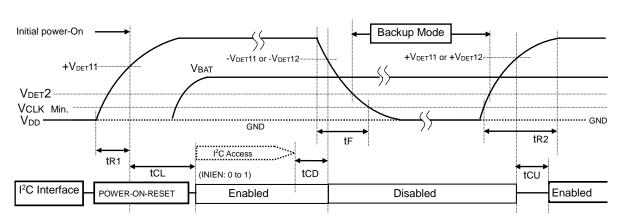

10.2. Precautions for power ON / OFF

1: To ensure that the power-on reset works at the initial power-on keep  $V_{DD}=V_{BAT}=GND$  for 10 seconds or more before  $V_{DD} = ON$ .

2: Initial power-on tR1 is a necessary condition for enabling power-on reset.

If this condition is not satisfied, power-on reset may not work. As a result, the time accuracy and current consumption may not meet the specifications. Please reset by software. See <u>18.2 Software Reset</u>.

3: When fluctuation of V<sub>DD</sub> is out of specifications, tF or tR2, it may be occur the followings, a momentary stop of crystal oscillation, a set of VLF by V<sub>OUT</sub> voltage drop lower than V<sub>CLK</sub> and so on.

4: The timing at which the I<sup>2</sup>C-Bus interface is enabled differs in when the initial power of  $V_{DD}$  is turned on and when  $V_{DD}$  is turned on from backup mode.

See the tCL and tCU specifications in the chart below.

5: These specifications don't mean a noise characteristic of a power supply of RTC.

Do not use amplitude signal output from a signal generator etc, as a power source.

# Figure 13 Power-On sequence1

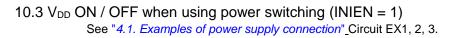

10.4 V<sub>DD</sub> ON / OFF when power switching is not used (INIEN = 0) See "4.1. Examples of power supply connection"\_Circuit EX4.

# Figure 14 Power-On sequence2

| Table 11 | Power | supply | characteristics |

|----------|-------|--------|-----------------|

|----------|-------|--------|-----------------|

| Item                   | Symbol | Condition                                                                           | Min. | Тур. | Max. | Unit   |

|------------------------|--------|-------------------------------------------------------------------------------------|------|------|------|--------|

| Power supply rise time | tr1    | From GND to VDD = +VDET11                                                           | 0.1  | -    | 10   | ms / V |

| Access wait time       | tc∟    | VDD = +VDET11 to Access start                                                       |      | -    | -30  | ms     |

| Access suspended time  | tcp    | The time from the end of I <sup>2</sup> C access to the disable of I <sup>2</sup> C | 0    | -    | -    | ms     |

| Power supply fall time | tF     | From VDD to VDD = VCLK                                                              | 1    | -    | -    | ms / V |

| Power supply rise time | tR2    | Time to restore VDD to operating voltage                                            | 1    | -    | -    | ms / V |

| Access wait time       | tCU    | VDD=+VDET1x to Access start                                                         |      | -    | 35   | ms     |

tR1, tR2, and tF specify that there is no voltage fluctuation faster / slower than the Min / Max specifications within the specified section. The risk when specifications were not satisfied, refer to the following.

| Item | Risk of fast fluctuations                                                        | Risk of slow fluctuations |  |  |  |

|------|----------------------------------------------------------------------------------|---------------------------|--|--|--|

| tR1  | Power-On-Reset d                                                                 | doesn't occur.            |  |  |  |

| tR2  | The FOUT waveform disappears momentarily, and clock time is momentarily delayed. | None                      |  |  |  |

| tF   | A data of RTC loss. A set of VLF.                                                |                           |  |  |  |

$V_{DD}$  and  $V_{BAT}$  in Figures 13 and 14 are the voltages of  $V_{DD}$  and  $V_{BAT}$  pins of RX8130CE.

Regarding access to the clock register after the initial power-on,

, See "10.1 restrictions of I2C interface in the initial power on". The clock from FOUT is outputted after tCU.

When status of  $V_{DD} = V_{BAT} = GND$  doesn't keep more than 10seconds before initial power-on, the Power-On-Reset may not work even if the tR / tF specifications are satisfied.

# 11. Reference Information

# 11.1. Reference Data

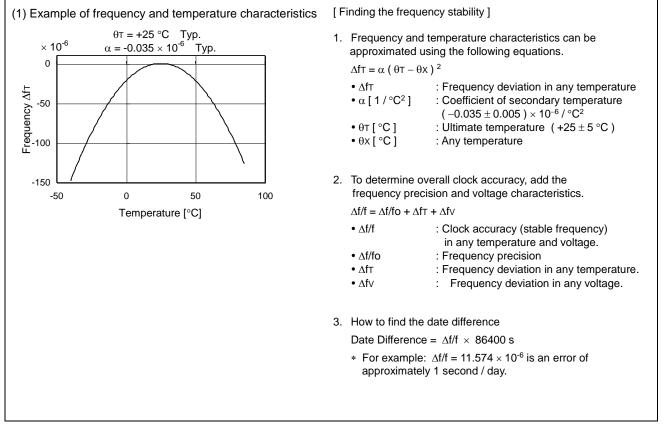

Figure 15 Frequency temperature characteristics

# 12. Application Notes

#### 1) Notes on handling

This module uses a C-MOS IC to realize low power consumption. Carefully note the following cautions when handling.

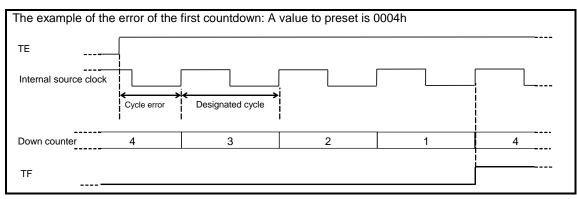

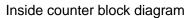

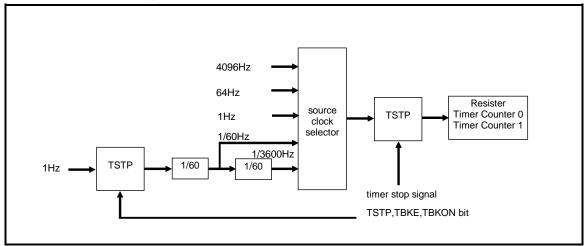

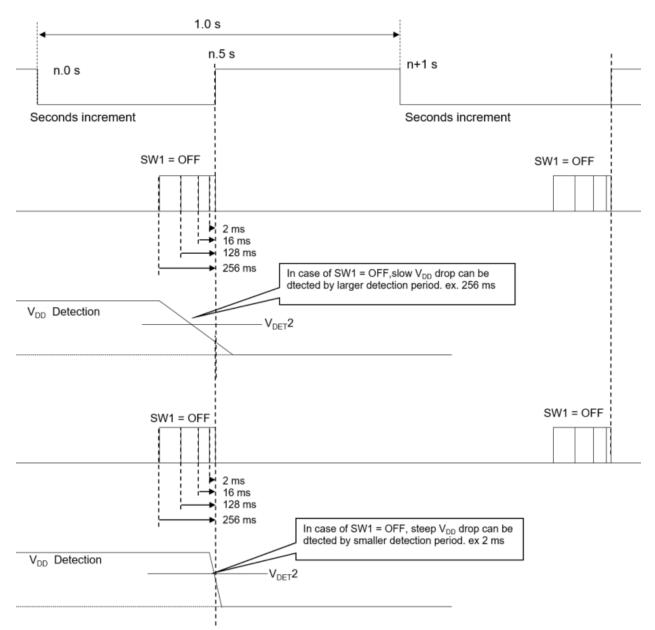

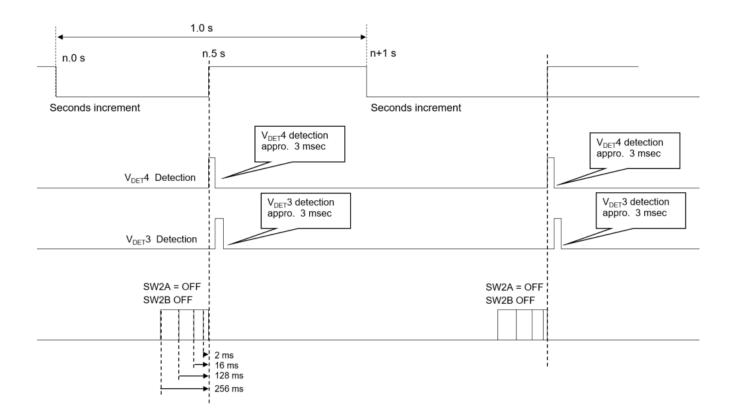

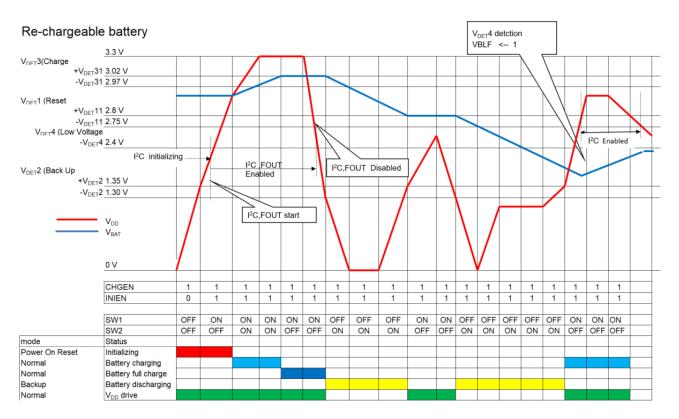

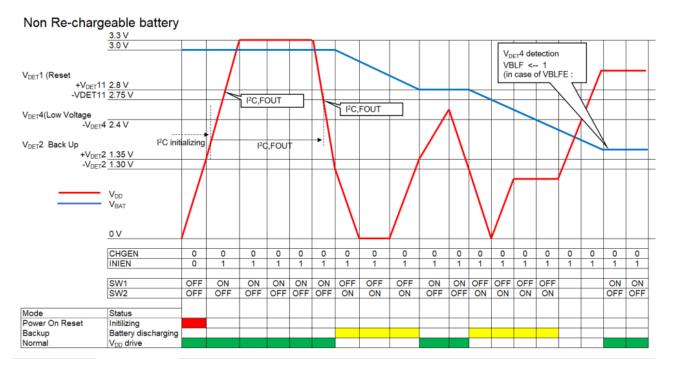

(1) Static electricity