### General Description

The EA8961 is a 100V, 1A, COT mode buck converter. Built-in high/low side Power-MOSFETs has high efficiency at light load and heavy load. COT mode operation provides very fast transient response. The EA8961 output voltage accuracy is ±2% over the full temperature range. The EA8961 has complete protection functions, including peak current limit, OTP and UVLO protection.

The EA8961 operation mode can be set by using FPWM pin. The device can works in CCM mode over full output loading current range or works in DCM mode at light loading current. The EA8961 can be designed as a buck-boost architecture to generate a negative voltage output. At this time, the reference voltage of the device is not GND but the negative voltage output, so the nternal use input range is VIN+|VOUT|.

### **Features**

- 5V to 100V Input Voltage Range

- Built-in High/Low Side Power MOSFETs

- 1A Continuous Load Current

- ±2% Output Voltage Accuracy

- COT Mode Operation & Fast Transient Response

- Programmable Light Load operation (CCM or DCM)

- Nearly Constant Switching Frequency (Maximum 1MHz)

- Programmable Soft-Start Function

- Peak Current Limit

- Input UVLO Protection

- **Auto Recovery OTP Protection**

### **Applications**

- IGBT Gate Driver Power Supply

- Industrial Programmable Logic Controller

- Telecom DC/DC Power Supply

- Power Line Communication

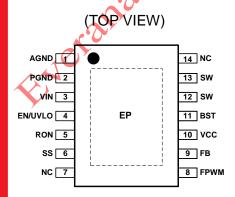

## Pin Configurations

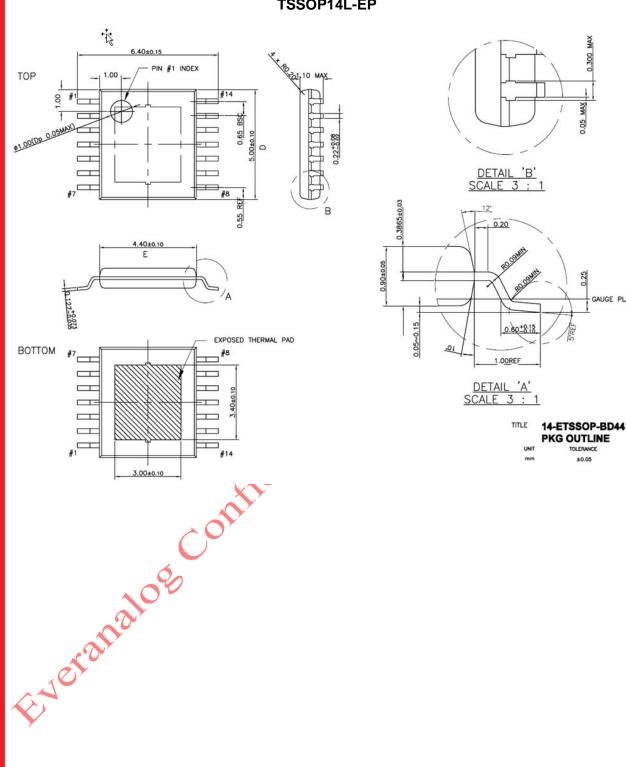

TSSOP14L-EP

Datasheet

### Pin Description

| Pin Name | Function Description                                                                             | Pin No. |

|----------|--------------------------------------------------------------------------------------------------|---------|

| AGND     | Analog ground.                                                                                   | 1       |

| PGND     | Power ground.                                                                                    | 2       |

| VIN      | Power input.                                                                                     | 3       |

| EN/UVLO  | The device turns on/turns off control input and UVLO Comparator input.                           | 41      |

| RON      | On time setting pin. Connect this pin to VIN pin via a resistor to set the on time.              | 5       |

| SS       | Soft-Start time setting pin.                                                                     | 6       |

| NC       | Not Connect.                                                                                     | 7, 14   |

| FPWM     | Mode selecting pin. Connect this pin to AGND for DCM mode. Connect this pin to VCC for CCM mode. | 8       |

| FB       | Feedback voltage input.                                                                          | 9       |

| VCC      | Internal circuit power supply.                                                                   | 10      |

| BST      | The power input of the internal high side N-MOSFET gate driver.                                  | 11      |

| SW       | Switching output.                                                                                | 12, 13  |

| EP       | Exposed Pad. Connect to AGND for dissipate heat.                                                 |         |

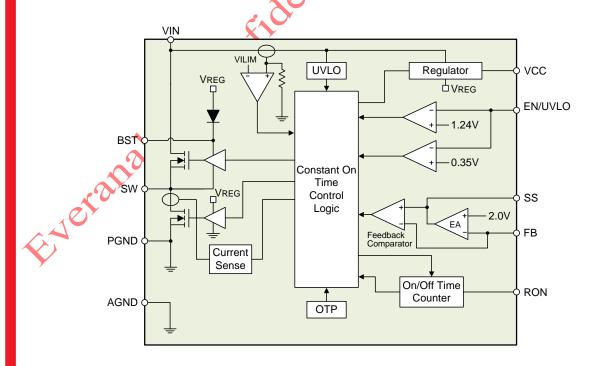

## Function Block Diagram

Figure 1. EA8961 internal function block diagram

## 100V, 1A, COT Mode Buck Converter

### **Absolute Maximum Ratings**

| Parameter                                             | Value           |

|-------------------------------------------------------|-----------------|

| Input Voltage (V <sub>IN</sub> )                      | -0.3V to +100V  |

| EN/UVLO Pin Input Voltage (V <sub>EN</sub> )          | -0.3V to +100V  |

| RON Pin Voltage (V <sub>RON</sub> )                   | -0.3V to +100V  |

| BST Pin Voltage (V <sub>BST</sub> )                   | -0.3V to +107V  |

| VCC Pin Voltage (V <sub>CC</sub> )                    | -0.3V to +7V    |

| FPWM Pin Voltage (V <sub>FPWM</sub> )                 | -0.3V to +7V    |

| SS Pin Voltage (V <sub>SS</sub> )                     | 0.3V to +7V     |

| FB Pin Voltage (V <sub>FB</sub> )                     | -0.3V to +7V    |

| SW Pin Voltage (V <sub>SW</sub> )                     | -1.5V to +100V  |

| BST Pin to SW Pin Voltage                             | -0.3V to +7V    |

| BST Pin to VCC Pin Voltage                            | 100V            |

| SW Pin to AGND Pin Voltage (20ns)                     | -3V             |

| Ambient Temperature operating Range (T <sub>A</sub> ) | -40°C to +85°C  |

| Maximum Junction Temperature (T <sub>Jmax</sub> )     | +150°C          |

| Lead Temperature (Soldering, 10 sec)                  | +260°C          |

| Storage Temperature Range (T <sub>s</sub> )           | -65°C to +150°C |

Note (1):Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

Exposure to "Absolute Maximum Ratings" conditions for extended periods may affect device reliability and lifetime.

## Package Thermal Characteristics

| Parameter                                                                  | Value    |

|----------------------------------------------------------------------------|----------|

| TSSOP14L-EP Thermal Resistance (θ <sub>JC</sub> )                          | 23.7°C/W |

| TSSOP14L-ER Thermal Resistance (θ <sub>JA</sub> )                          | 39.5°C/W |

| TSSOP14L-EP Power Dissipation at T <sub>A</sub> =25°C (P <sub>Dmax</sub> ) | 3.2W     |

Note (1):  $P_{Dmax}$  is calculated according to the formula:  $P_{DMAX}=(T_{JMAX}-T_A)/\theta_{JA}$ .

Datasheet

### Electrical Characteristics

$V_{IN}$ =48V,  $T_A$ =25°C, unless otherwise noted

| Parameter                                         | Symbol                 | Test Conditions                                               | Min | Тур  | Max | Unit |

|---------------------------------------------------|------------------------|---------------------------------------------------------------|-----|------|-----|------|

| Input Current                                     |                        |                                                               |     |      |     |      |

| Shutdown Supply Current                           | I <sub>SD</sub>        | V <sub>EN</sub> = 0V                                          |     | 35   | 60  | uA   |

| Quiescent Current                                 | IQ                     | $V_{FB} = 3V$ , $I_{LOAD} = 0A$                               |     | 1.3  | 2   | mA   |

| VCC Power Supply                                  |                        |                                                               |     |      | Â   | Ç,   |

| VCC Voltage                                       | $V_{CC}$               | $I_{CC} = 20mA$                                               | 4.5 | 5.0  | 5.5 | V    |

| VCC Current                                       | $I_{CC}$               |                                                               |     |      | 30  | mA   |

| UVLO Threshold                                    | $V_{\text{UVLO}}$      | V <sub>CC</sub> Rising                                        |     | 3.85 |     | V    |

| UVLO Hysteresis                                   | $V_{\text{UV-HYS}}$    |                                                               | Á   | 200  |     | mV   |

| VIN-VCC Dropout Voltage                           |                        | $V_{IN} = 5V$ , $I_{CC} = 20$ mA                              | xex | 600  |     | mV   |

| Power MOSFET                                      |                        |                                                               |     |      |     |      |

| High Side MOSFET<br>On-Resistance                 | R <sub>DS(ON)-HM</sub> | I <sub>SW</sub> = 0.5A                                        |     | 300  |     | mΩ   |

| Low Side MOSFET<br>On-Resistance                  | R <sub>DS(ON)-LM</sub> | I <sub>SW</sub> = 0.5A                                        |     | 150  |     | mΩ   |

| BST Pin UVLO Threshold                            |                        |                                                               |     | 2.9  |     | V    |

| BST Pin UVLO Hysteresis                           | . 3                    | <b>3</b> *                                                    |     | 200  |     | mV   |

| Current Limit                                     | <b>(1)</b>             |                                                               |     |      |     |      |

| High Side MOSFET<br>Current Limit                 | LIM-HM                 |                                                               |     | 1.61 |     | Α    |

| Low Side MOSFET<br>Souring Current Limit          | I <sub>SOURCE-LM</sub> |                                                               | 1.3 | 1.6  | 1.9 | А    |

| Low Side MOSFET Sinking Current Limit             | I <sub>SINK-LM</sub>   |                                                               |     | 3    |     | Α    |

| High Side MOSFET<br>Current Limit Respose<br>Time | t <sub>LIM-HM</sub>    | I <sub>LIM-HM</sub> threshold<br>detect to MOSFET<br>turn off |     | 100  |     | ns   |

| <b>\( \)</b>                                      | t <sub>OFF</sub>       | FB = 0V, V <sub>IN</sub> = 72V                                |     | 16.5 |     | μs   |

| High Side MOSFET Current Limit Turn off Time      | t <sub>OFF1</sub>      | FB = 0.1V, V <sub>IN</sub> = 72V                              |     | 13   |     | μs   |

|                                                   | t <sub>OFF2</sub>      | FB = 1V, V <sub>IN</sub> = 72V                                |     | 2.7  |     | μs   |

| FPWM Pin                                          |                        |                                                               |     |      |     |      |

| FPWM Pin Input High<br>Voltage                    | $V_{FPWM-H}$           |                                                               | 3   |      |     | V    |

## 100V, 1A, COT Mode Buck Converter

| $V_{FPWM-L}$          |                                                                                                                              |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                               | 1                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>ZX</sub>       | FPWM = 0V                                                                                                                    |                                                                                                                                                                                                                            | 22.5                                                                                                                                                                                                                                                          |                                                       | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                       |                                                                                                                              |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                               |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $V_{REF}$             |                                                                                                                              | 1.96                                                                                                                                                                                                                       | 2                                                                                                                                                                                                                                                             | 2.04                                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| I <sub>FB</sub>       |                                                                                                                              |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                               | 100                                                   | nA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                       |                                                                                                                              |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                               |                                                       | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I <sub>SS</sub>       | SS = 0.5V                                                                                                                    |                                                                                                                                                                                                                            | 10                                                                                                                                                                                                                                                            | Ô                                                     | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                       |                                                                                                                              |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                               | .0                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $V_{EN-TH}$           | EN/UVLO Rising                                                                                                               | 1.2                                                                                                                                                                                                                        | 1.24                                                                                                                                                                                                                                                          | 1.27                                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $V_{EN-SD}$           | EN/UVLO Falling                                                                                                              | 0.29                                                                                                                                                                                                                       | 0.35                                                                                                                                                                                                                                                          |                                                       | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $V_{\text{EN-SD-TH}}$ | •_/                                                                                                                          | O. C.                                                                                                                                                                                                                      | 50                                                                                                                                                                                                                                                            |                                                       | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I <sub>EN</sub>       | EN/UVLO = 1.4V                                                                                                               | 15                                                                                                                                                                                                                         | 20                                                                                                                                                                                                                                                            | 25                                                    | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                       |                                                                                                                              |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                               |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| T <sub>OTP</sub>      | XIA!                                                                                                                         |                                                                                                                                                                                                                            | 175                                                                                                                                                                                                                                                           |                                                       | °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| T <sub>HYS</sub>      |                                                                                                                              |                                                                                                                                                                                                                            | 20                                                                                                                                                                                                                                                            |                                                       | °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                       | V <sub>REF</sub> I <sub>FB</sub> I <sub>SS</sub> V <sub>EN-TH</sub> V <sub>EN-SD</sub> V <sub>EN-SD-TH</sub> I <sub>EN</sub> | $I_{ZX} \qquad \text{FPWM} = 0V$ $V_{REF}$ $I_{FB}$ $I_{SS} \qquad SS = 0.5V$ $V_{EN-TH} \qquad EN/UVLO \text{ Rising}$ $V_{EN-SD} \qquad EN/UVLO \text{ Falling}$ $V_{EN-SD-TH}$ $I_{EN} \qquad EN/UVLO = 1.4V$ $T_{OTP}$ | $I_{ZX} \qquad \text{FPWM} = 0V$ $V_{REF} \qquad 1.96$ $I_{FB}$ $I_{SS} \qquad SS = 0.5V$ $V_{EN-TH} \qquad EN/UVLO \text{ Rising} \qquad 1.2$ $V_{EN-SD} \qquad EN/UVLO \text{ Falling} \qquad 0.29$ $V_{EN-SD-TH}$ $I_{EN} \qquad EN/UVLO = 1.4V \qquad 15$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | I <sub>ZX</sub> FPWM = 0V         22.5           V <sub>REF</sub> 1.96         2         2.04           I <sub>FB</sub> 100           V <sub>SS</sub> SS = 0.5V         10         10           V <sub>EN-TH</sub> EN/UVLO Rising         1.2         1.24         1.27           V <sub>EN-SD</sub> EN/UVLO Falling         0.29         0.35           V <sub>EN-SD-TH</sub> 50         50           I <sub>EN</sub> EN/UVLO = 1.4V         15         20         25           T <sub>OTP</sub> 175 |

Note (1): MOSFET on-resistance specifications are guaranteed by correlation to wafer level measurements.

## Ordering Information

| Part Number | Package Type | Packing Information |

|-------------|--------------|---------------------|

| EA8961SCR   | TSSOP14L-EP  | Tape & Reel         |

Note (1): SC: Package type code.

(2):"R": Tape & Reel.

<sup>(2):</sup> Thermal shutdown specifications are guaranteed by correlation to the design and characteristics analysis.

Datasheet

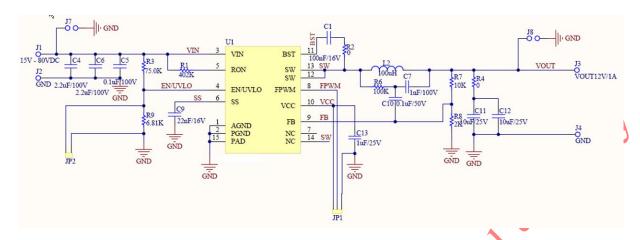

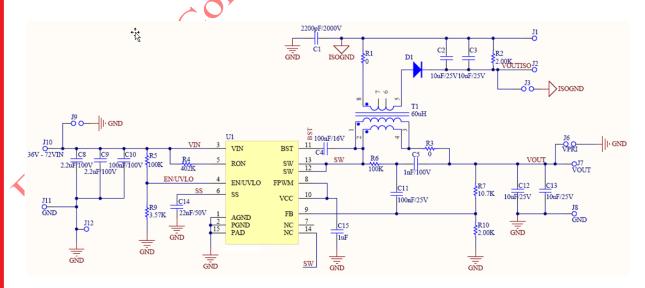

### Application Circuit Diagram

Figure 2. Typical buck converter application circuit

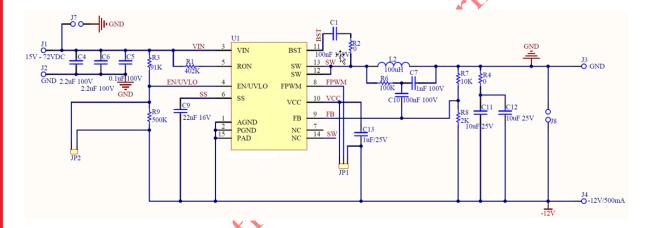

Figure 3. Negative output voltage application circuit

Figure 4. 12V,10W isolated DC/DC application circuit

### 100V, 1A, COT Mode Buck Converter

Datasheet

### 100V, 1A, COT Mode Buck Converter

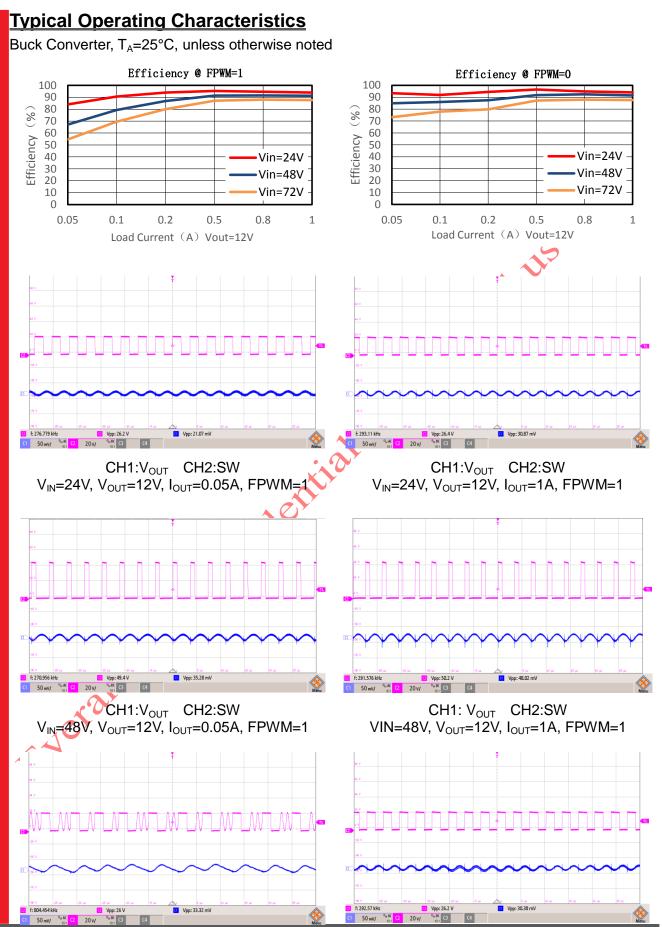

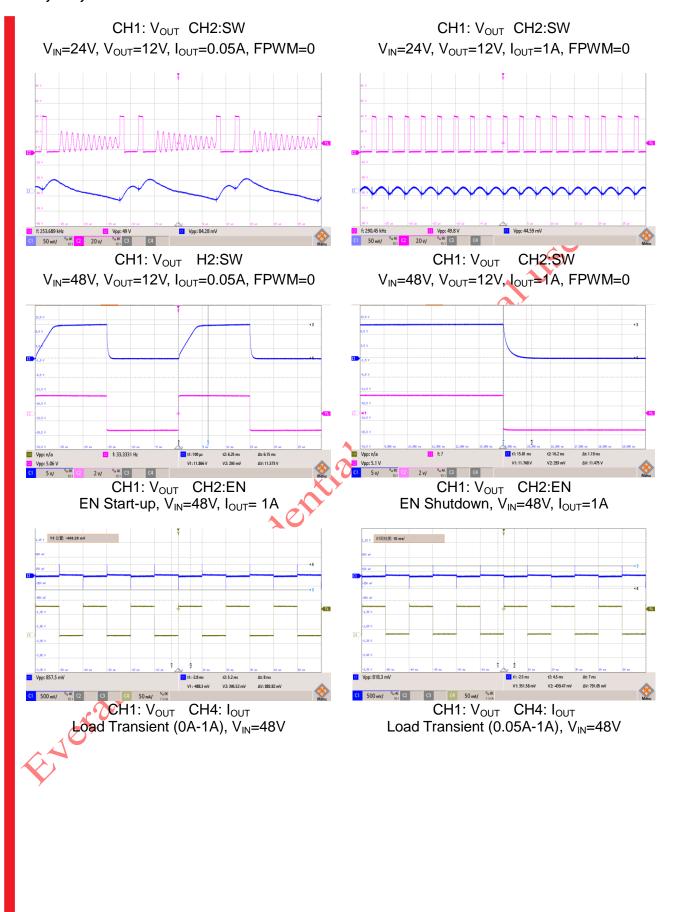

### Typical Operating Characteristics

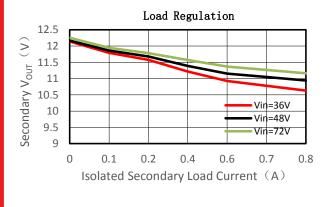

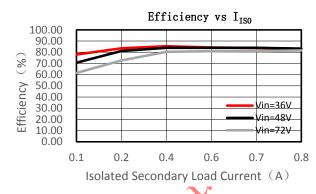

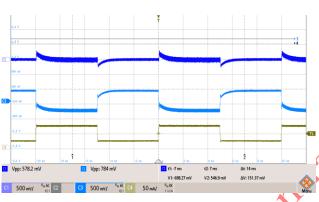

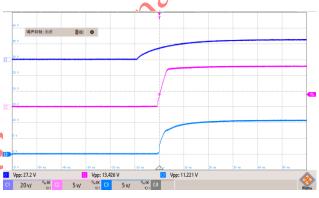

Isolated DC/DC Converter, T<sub>A</sub>=25°C, unless otherwise noted

$\begin{array}{c} \text{CH1:V}_{\text{OUT}} \;,\; \text{CH3:V}_{\text{OUTISO}} \;,\; \text{CH4:I}_{\text{OUTISO}} \\ \text{Secondary LoadTransient (0.25A-0.75A),} \\ \text{$V_{\text{IN}}$=}48V \end{array}$

$$\label{eq:chisquared} \begin{split} \text{CH1:V}_{\text{IN}} &, \text{CH2:V}_{\text{OUT}} &, \text{CH3:V}_{\text{OUTISO}} \\ & \text{VIN Start-up, I}_{\text{ISO}} = 500 \text{mA} \end{split}$$

Everalialog Co

Datasheet

### Functional Description

#### Control Logic

The control structure of EA8961 includes a comparator and a single pulse on-timer generating circuit, which compares the output voltage feedback (FB) with the voltage (VSS) of the soft-start (SS) pin, if the FB voltage is lower than VSS, the internal main switch is turned on, and the turn-on time is determined by the input voltage and the resistance RON. After the on-time, the main switch must remain in the off state, forced to close by the minimum off-time OFF-time, until the FB voltage is lower than VSS again, and the single-pulse on-timer circuit works. During fast start-up or when there is a sudden increase in load current, the regulator operates with a minimum off-time per cycle. When regulating the output in steady state, the off-time is automatically adjusted to produce the duty cycle required for output voltage regulation.

EA8961 works in continuous conduction CCM mode under heavy load. If the FPWM pin is grounded or floating, the system works in discontinuous conduction DCM mode under light load, and it works in continuous conduction mode under sufficient load. If the FPWM pin is connected to VCC, the system works in continuous conduction CCM mode under light load and heavy load. The continuous operating frequency (in Hz) is determined by the RON pin resistance, calculated according to formula as below, and RON is expressed in ohms.

$$F_{\rm SW} = \frac{V_{\rm OUT}}{1.008 \times 10^{-10} \times R_{\rm ON}}$$

Hz.

The output voltage is set by two external resistors  $(R_{FB1}, R_{FB2})$ . Calculate the output voltage according to formula as below, where  $V_{REF}$ =2V is the feedback reference voltage.

$$V_{OUT} = \frac{V_{REF} \times (R_{FB2} + R_{FB1})}{R_{FB1}}V$$

### VCC Power Supply

The EA8961 contains an internal high voltage LDO regulator with a nominal output voltage of 5 V. VCC regulator internal current limit minimum 30mA. This regulator powers internal circuitry, including synchronous Low-side MOSFET gate driver and logic. At the same time, VCC charges the capacitance of the BST pin through an internal diode to provide power for the high-voltage side High-side MOSFET gate driver. The system starts up when the voltage on the VCC pin reaches the undervoltage lockout (VCC UVLO) threshold of 3.85 V.

#### Soft-Start Circuit

The EA8961 reduces current surge through soft-start function. When the EN/UVLO pin is above the EN/UVLO standby threshold 1.24V, and VCC exceeds the undervoltage value 3.85V, an internal 10µA current source switches the external capacitor at the SS pin from 0 V is charged to 2V. Soft-start function ends when the SS capacitor charges to the 2V. A ramp voltage at the SS pin produces a controlled, monotonic output voltage start-up. In all applications, a minimum soft-start capacitor of 1nF must be used.

#### On-Time Generator Circuit

The turn-on time of the main switch High side MOSFET is determined by the resistance of RON, which is inversely proportional to the input voltage (VIN). The system has a nearly constant frequency. The conduction time can be calculated as below, and RON is expressed in ohms.

### 100V, 1A, COT Mode Buck Converter

$$t_{ON} = \frac{1.008 \times 10^{-10} \times R_{ON}}{V_{IN}} s$$

To set the continuous conduction mode switching frequency (FSW in Hz), the RON resistance is determined by equation shown as below:

$$R_{ON} = \frac{V_{OUT}}{1.008 \times 10^{-10} \times F_{SW}} \Omega$$

Select the minimum on-time of RON (when VIN is maximum) must be greater than 150ns to work properly. This minimum on-time requirement limits the maximum switching frequency for applications with higher VIN and lower VOUT.

#### **Current Limit**

The EA8961 provides a current limited off-timer with adjustable off time. If the current peak in the buck switch exceeds 1.6A, the on-timer is immediately terminated and a non-resettable off-timer is started. The length of the off time is determined by the FB voltage and the input voltage VIN. For example, when  $V_{FB}$ =0.1V and VIN=72V, the off time is set to 13us. This can occur if the output is shorted or during the initial stages of start-up. In output overload conditions where FB voltage is greater than 0V, the current limit trip time is shortened. The current limit turn-off time  $t_{OFF}$  is calculated by formula:

$$T_{\text{OFF(CL)}} = \frac{V_{\text{IN}}}{20V_{\text{FB}} + 4.35} \mu \text{s}$$

#### **EN/UVLO Function**

The EA8961 contains a dual-level undervoltage lockout (EN/UVLO) circuit. When the EN/UVLO pin voltage is below 0.35V, the regulator is in low current shutdown mode. When the EN/UVLO pin voltage is greater than 0.35V but less than 1.24V, the system is in standby mode. In standby mode, the VCC regulator operates, but the converter switch remains off. When the voltage at the VCC pin exceeds the VCC rising threshold 3.85V and the EN/UVLO pin voltage is greater than 1.24V, the system switch works. An external resistor divider from VIN to GND can be used to set the minimum operating voltage.

| EN/UVLO Pin Voltage | VCC Regulator  | Mode      | Description                             |

|---------------------|----------------|-----------|-----------------------------------------|

| < 0.35V             | Turn-off       | Shutdown  | VCC regulator turn off, MOSFET turn off |

| 0.35V~1.24V         | Turn-on        | Standby   | VCC regulator turn on, MOSFET turn off  |

| > 1.24V             | VCC < VCC_UVLO | Standby   | VCC regulator turn on, MOSFET turn off  |

| <i>y</i> > 1.24V    | VCC > VCC_UVLO | Operation | VCC regulator turn on, MOSFET turn on   |

If the EN/UVLO set point is not required, the EN/UVLO pin can be driven by a logic signal as an enable input, or connected directly to the VIN pin. If EN/UVLO is directly connected to the VIN pin, the regulator will start operating when VCC voltave over the VCC\_UVLO voltage.

#### **FPWM Function**

Datasheet

By setting the FPWM pin voltage, CCM or DCM operation mode can be selected at light load. When the FPWM pin is grounded or floating, the pulse-skipping PFM mode and the zero-current detection circuit are enabled. When the inductor current drops close to zero, the zero-crossing detector turns off the low-side MOSFET, allowing the EA8961 to operate in DCM mode at light loads. In the DCM state, the switching frequency decreases as the load decreases. At the same time, the internal ripple injection circuit works for a typical buck application circuit. This feature applies over the entire load and input voltage range. Eliminates the need for an external feedback ripple injection circuit.

If the FPWM pin is pulled high, the EA8961 will work in CCM mode under any load condition. CCM operation reduces efficiency at light loads, but improves the output's transient response to step load changes and provides a nearly constant switching frequency. Additionally, the isolation transformer output structure requires continuous conduction mode. The internal ripple injection circuit is disabled in CCM mode. To generate optimal ripple at the FB node, an external ripple injection circuit or an ESR resistor in series with the output capacitor is required.

| FPWM Pin Connecting | Logic | Description                                                                                                                                         |

|---------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| GND or Floating     | 0     | DCM mode at light load. The internal ripple injection circuit is working and eliminates the need for an external feedback ripple injection circuit. |

| VCC                 | 1     | CCM mode at dight load. The internal ripple injection circuit is disabled and an external feedback ripple injection circuit is required.            |

### 100V, 1A, COT Mode Buck Converter

### Application Information

#### Typical Buck Converter

A typical application is a synchronous buck converter, which operates from 15V to 80V and provides a stable 12V output voltage with a maximum output current capability of 1A.

| Parameter            | Design Value |

|----------------------|--------------|

| Input Voltage        | 15V to 80V   |

| Output Voltage       | 12V          |

| Output Loading       | 1A           |

| Typical Frequency    | 300kHz       |

| Light Load Operating | CCM, FWPM≥1  |

### Output Voltage Setting

Set the output voltage by selecting R<sub>FB1</sub> and R<sub>FB2</sub>:

g R<sub>FB1</sub> and R<sub>FB2</sub>:

$$V_{OUT} = \frac{V_{REF} \times (R_{FB2} + R_{FB1})}{R_{FB1}}$$

with the output at the minimum input voltage.

### Switching Frequency Setting

The duty cycle required to maintain the output at the minimum input voltage limits the maximum switching frequency of the EA8961. The maximum value of the minimum forced off time tope limits the duty cycle and therefore the switching frequency. The maximum frequency to avoid output attenuation at minimum input voltage can be calculated.

$$F_{SW,max(@V_{IN.min})} = \frac{V_{IN.min} - V_{OUT}}{V_{IN.min} \times t_{OFF\_min}(ns)}$$

For example, based on the maximum frequency limited by t<sub>OFF\_min</sub> minimum off time, i.e. 170ns calculated as FSW, max(@VIN,min)=1.2MHz. This value is higher than 1MHz, which is the maximum possible operating frequency of EA8961.

At maximum input voltage, the maximum switching frequency of the EA8961 is limited to a minimum time ton, min, thereby limiting the minimum duty cycle of the converter. The maximum frequency at maximum input voltage can be calculated using equation shown as below.

$$F_{SW.max(@V_{IN.min})} = \frac{V_{OUT}}{V_{IN.max} \times t_{ON\_{min}}(ns)}$$

Using above equation and  $T_{ON\_min}(typ)=150ns$ , the maximum achievable switching frequency is FSW, max(@VIN, min)=1000 kHz. Taking this value as the maximum possible operating switching frequency over the input voltage range, the design chooses a nominal switching frequency of FSW=300kHz. The value RON of the resistor sets the nominal switching frequency according to below equation. For the application of FSW=300kHz, RON is calculated as 396k $\Omega$  (taken as 402 k $\Omega$ ).

Datasheet

$$R_{ON} = \frac{V_{OUT}}{1.008 \times 10^{-10} \times F_{SW}} \Omega$$

#### Selecting the inductor

Choose the inductor to limit the inductor ripple current to between 20% and 40% of the maximum load current. The minimum value of inductance required in this application can be calculated according to the equation:

$$L_{min} = \frac{V_O \times (V_{IN.max} - V_O)}{V_{IN.max} \times F_{SW} \times I_{O.max} \times 0.4}$$

According to above equation, at VIN=80V, the minimum value of the inductor is calculated to be 85µH, and the inductor current ripple will be 40% of the maximum load current. Considering the inductance variation and inductance saturation margin, this design chooses L=100µH.

In the design of the chip with a maximum output current of 1A, in addition to the maximum peak current, the saturation current of the inductor also needs to be considered. In an overload or short circuit condition, the peak value of the inductor current will be limited by the high-side FET current limit. According to the high-side MOSFET current limit specification in the electrical characteristics, an inductor with a saturation current rating greater than 1.94 (maximum) should be selected.

### Selecting the Output Capacitor

The output capacitor is chosen to limit the capacitive ripple at the output of the buck converter. The required output capacitance for the ripple voltage  $\Delta VO$  across the capacitor is calculated according to equation:

$$C_{OUT} = \frac{\Delta I_{L.max}}{8 \times F_{SW} \times \Delta V_{0.ripple}}$$

If the  $\triangle$ VO, ripple=10mV, then the  $C_{OUT}$ =15 $\mu$ F. Select 2 standard 10 $\mu$ F ceramic capacitors in parallel and the  $C_{OUT}$  should use X7R type capacitors rated at 25V or higher to limit capacitance reduction due to DC bias.

### Selecting the Serial Ripple Resistor $R_{ESR}$ when FPWM = 1

If FPWM=1, i.e. when connected to VCC, the FPWM pin is pulled high, a resistor  $R_{\rm ESR}$  in series with the output capacitor or an external ripple injection circuit must be selected to ensure sufficient ripple injection at the feedback pin FB (>25mV). The ripple generated by  $R_{\rm ESR}$  is proportional to the inductor current ripple, therefore,  $R_{\rm ESR}$  should be calculated from the minimum inductor current ripple occurring at the minimum input voltage. Calculate RESR according to formula shown as below.

$$R_{ESR} \geq \frac{25 mV \times V_O}{V_{REF} \times \Delta I_{L.min}}$$

When VO=12V,  $V_{REF}$ =2V and  $\Delta$ IL, min=81 mA (at VIN, min=15V), it requires  $R_{ESR}$  to be greater than or equal to 1.87 $\Omega$ . When  $R_{ESR}$ =2 $\Omega$  is selected, the maximum output voltage ripple is about 700 mV at the maximum VIN. However, due to the internal DC error correction loop, load and line regulation will be greatly improved despite adding a larger  $R_{ESR}$  in the circuit.

For applications requiring lower output voltage ripple, a Type 2 or Type 3 ripple injection circuit must

### 100V, 1A, COT Mode Buck Converter

be used, as described in Ripple Configuration. In this design example, when FPWM=1, a  $0\Omega$  ESR resistor is selected and an external Type 3 ripple injection circuit is used.

### Selecting the VCC and Bootstrap Capacitors

The VCC capacitor charges the bootstrap capacitor  $C_{\text{BST}}$  when the high-side switch is turned off, and supplies the internal logic circuits and the low-side MOSFET gate driver. The bootstrap capacitor powers the gate drive of the high-side MOSFET during its on-time. The optimal value of  $C_{\text{VCC}}$  is 1µF. The best value for  $C_{\text{BST}}$  is 10nF. Both capacitors must be high quality X7R ceramic capacitors.

### Selecting the Intput Capacitor

The input capacitor must be large enough to limit the input voltage ripple to acceptable levels. The input capacitance  $C_{IN}$  required for the worst-case input ripple for  $\Delta VIN$  ripple.

$$C_{IN} = \frac{I_{0.max} \times D \times (1 - D)}{\Delta V_{IN.ripple} \times F_{SW}}$$

According to above formula, the value of the input capacitor is calculated to be about 1.68µF when D=0.5. Considering that the capacitance decreases with the applied voltage, two 2.2µF standard value ceramic capacitors are selected. The input capacitors should be rated to withstand the maximum input voltage under all operating and transient conditions. This design selects 100V, X7R ceramic capacitors. A 0.1µF input ceramic capacitor is required as a bypass path for the high frequency components of the input switch current. This bypass capacitor must be placed directly across VIN and PGND (pins 3 and 2) close to the IC. Cin value and location are critical to reducing switching noise and transients.

### Selecting the C<sub>ss</sub> Capacitor

A capacitor connected to the SS pin determines the soft-start time. The capacitance value is determined by equation:

$$C_{SS} = \frac{I_{SS} \times t_{Startup}}{V_{SS}}$$

$C_{SS}$ =22nF and  $V_{SS}$  = 2V,  $I_{SS}$  = 10µÅ, the soft-start time is close to 4ms.

### Selecting the EN/UVLO Pin Resistor

EN/UVLO resistors R3 ( $R_{UV2}$ ) and R9 ( $R_{UV1}$ )set the input undervoltage lockout threshold and hysteresis value according to equations shown as below:

$$V_{IN(HYS)} = I_{UVLO(HYS)} \times R_{UV2}$$

$$V_{IN,UVLO(rising)} = V_{UVLO(TH)} \times \left(1 + \frac{R_{UV2}}{R_{UV1}}\right)$$

Where  $I_{UVLO\_HYS} = 20\mu A$ ,  $V_{UVLO\_TH} = 1.24V$ .

Datasheet

#### Isolated DC/DC Converter

Another typical application example is an isolated DC/DC converter operating from an input voltage range of 36V to 72V. It provides a stable 12V isolated output voltage with an output power capability of 10W. The EA8961 isolated DC/DC application is designed to operate on a nominal 48V DC supply (line variation ranges from 36V to 72V) and can provide a highly efficient 12V isolated output solution with a secondary load current capability of 0A to 0.8A. In applications, the primary coil can be left unloaded. The switching frequency is nominally 300kHz. This design achieves a peak efficiency of over 88%.

| Parameter         | Design Value |

|-------------------|--------------|

| Input Voltage     | 36V to 72V   |

| Output Voltage    | 12V (±10%)   |

| Output Loading    | 0A to 0.8A   |

| Typical Frequency | 300kHz       |

| Peak Efficiency   | ≥ 87%        |

| Operating Mode    | FWPM=1       |

#### **V<sub>OUT</sub> and The Transformer Turns Ratio**

The primary output voltage of an isolated DC/DC converter should not exceed half the minimum input voltage. Therefore, with a minimum VIN of 36V, the primary output voltage (VOUT) should not be higher than 18 V. The isolated output voltage of VOUTISO in Figure 4 is scaled 1:1 by selecting the turns ratio (N1:N2). Using this turns ratio, the primary output voltage, V<sub>OUT</sub>, is calculated as below:

$$V_{OUT} = \frac{V_{OUTISO} + V_{RD1}}{N_2} = \frac{V_{OUTISO} + 0.7V}{1} = 12.7V$$

The  $0.7V(V_{FD1})$  of VOUTISO represents the forward voltage drop of the secondary rectification diode. By choosing the correct feedback resistor, the primary output voltage  $V_{OUT}$  is set to 12.7V and the secondary voltage is regulated to 12V.

# Selecting Secondary Rectifier Diode

The secondary rectifier diode must be able to block the voltage reflected from the maximum input voltage to the secondary switching node. The minimum diode reverse voltage  $V_{RD1}$  rating is given by:

$$V_{RD1} = V_{IN(max)} \times \frac{N_2}{N_1} + V_{OUTISO} = 72V \times 1 + 12V = 84V$$

In this application, a diode with a reverse voltage rating of 100V or higher must be selected considering the worst-case transient input voltage.

#### External Ripple Injection Circuit

The EA8961 FPWM pin must not be grounded or kept open in an isolated DC/DC converter. The ripple injection circuit chooses the third type. See Ripple Configuration for ripple injection design information.

### 100V, 1A, COT Mode Buck Converter

#### Output Capacitor (Cv<sub>iso</sub>)

The output capacitor of an isolated DC/DC converter conducts higher ripple current than the output capacitor of a buck converter. The ripple voltage across the isolated output capacitor is calculated from the time the rectifier diode is off. During this time, the entire output current is supplied by the output capacitor. The required capacitance for the worst-case ripple voltage can be calculated as below, where  $\Delta VISO$  is the expected ripple voltage at the secondary output.

$$C_{VISO} = \frac{I_{ISO}}{\Delta V_{ISO}} \left( \frac{V_{PRI}}{V_{IN(MIN)}} \right) \times \frac{1}{f_{sw}}$$

The equation is an approximation that ignores the ripple components associated with the ESR and ESL of the output capacitor. For  $\Delta V_{ISO}$ =100mV, it requires a minimum  $CV_{ISO}$ =11.12 $\mu$ F. Here we choose two 10 $\mu$ F X7R ceramic capacitors.

#### Ripple Configuration

The EA8961 adopts a constant on-time (COT) control scheme. The turn-on time of the system switch is determined by the on-timer, and the turn-off time of the system switch is obtained by comparing the feedback voltage  $V_{FB}$  with the reference voltage. Therefore, for stable operation, the FB voltage must decrease monotonically and be in phase with the inductor current during the off-time. Additionally, the change in feedback voltage  $V_{FB}$  during the switch off time must be large enough to dominate any noise present at the feedback node.

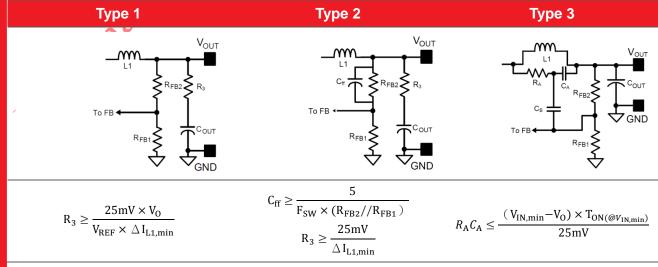

Table 1 shows three different ways to generate the proper voltage ripple at the feedback node. Type 1 and Type 2 ripple circuits couple the converter output ripple to the feedback node FB. The output voltage ripple has two components: (1) The capacitor ripple generated by the inductor current ripple charging or discharging the output capacitor. (2) Resistor ripple caused by inductor current ripple through output capacitor ESR and R3. The capacitor ripple is not synchronous with the inductor current, and the capacitor ripple does not decrease monotonically during the off-time. The resistor ripple is in phase with the inductor current and decreases monotonically during the off time. Therefore, the resistor ripple must exceed the output capacitor ripple (VOUT) for stable operation. If this condition is not met, unstable switching behavior is observed in COT converters, with multiple on-time pulses in succession followed by long off-times.

Type 3 ripple injection is to utilize the ripple injection circuit with RA, CA and switch node (SW) voltages to generate a triangular ramp. This triangular ramp is then AC coupled to feedback node FB using capacitor CB Since this circuit does not use the output voltage ripple, it is suitable for applications requiring low output voltage ripple.

Datasheet

#### Table 1. Ripple Injection Structure

#### **PCB Layout**

Proper layout is critical to the performance of the circuit, and the following layout guidelines are recommended:

- a. There is switching current in the loop composed of the input capacitor C<sub>IN</sub>, VIN pin and PGND pin, therefore, The input capacitor must be close to the IC and directly connected to VIN and PGND pins to minimize the loop area.

- The RON resistor and SS capacitor between the VIN and RON pins should be placed as close

as possible to their respective pins.

- c. VCC and bootstrap (BST) bypass capacitors provide switching current to the high-side and low-side gate drivers, these two capacitors should also be placed as close as possible to the IC, and the connecting wire length and loop area must be kept to a minimum.

- d. Care must be taken in routing the feedback loop to avoid coupling any noise into this pin, in particular the feedback loop must be short and not near magnetics or in parallel with any other switching traces.

- e. In FPWM=1 mode, if a ripple injection circuit is used at the FB pin to generate ripple, the feedback ripple is injected into the DC loop and the VOUT loop, and a differential layout is a better choice to help reduce scope for any noise injection at the FB pin.

- f. The SW node switches rapidly between VIN and GND every cycle and is therefore a source of noise, the SW node area must be kept to a minimum.

Ver. 1.0

## 100V, 1A, COT Mode Buck Converter

## Package Information

#### TSSOP14L-EP

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by Everanalog manufacturer:

Other Similar products are found below:

NCP1218AD65R2G NCP1244BD065R2G NCP1336ADR2G NCP6153MNTWG NCP81101BMNTXG NCP81205MNTXG SJE6600

AZ7500BMTR-E1 SG3845DM NCP1250BP65G NCP4204MNTXG NCP6132AMNR2G NCP81102MNTXG NCP81206MNTXG

NCP1240AD065R2G NCP1240FD065R2G NCP1361BABAYSNT1G NCP1230P100G NX2124CSTR SG2845M NCP1366BABAYDR2G

NCP81101MNTXG NCP81174NMNTXG NCP4308DMTTWG NCP4308AMTTWG NCP1366AABAYDR2G NCP1251FSN65T1G

NCP1246BLD065R2G MB39A136PFT-G-BND-ERE1 NCP1256BSN100T1G LV5768V-A-TLM-E NCP1365BABCYDR2G

NCP1365AABCYDR2G NCP1246ALD065R2G AZ494AP-E1 CR1510-10 NCP4205MNTXG ISL69158IRAZ-T7A XRP6141ELTR-F

RY8017 LP6260SQVF LP6298QVF ISL6121LIB ISL6225CA ISL6244HRZ ISL6268CAZ ISL6315IRZ ISL6420AIAZ-TK ISL6420AIRZ

ISL6420IAZ